Professional Documents

Culture Documents

9a. An Introduction To Interrupts

Uploaded by

MANIKANDANOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

9a. An Introduction To Interrupts

Uploaded by

MANIKANDANCopyright:

Available Formats

7/7/2015

ANINTRODUCTIONTOINTERRUPTS

ANINTRODUCTIONTOINTERRUPTS

INTERRUPTS

There are two main types of interrupt in the 8086 microprocessor, internal and external

hardware interrupts. Hardware interrupts occur when a peripheral device asserts an interrupt

input pin of the microprocessor. Whereas internal interrupts are initiated by the state of the

CPU(e.g.dividebyzeroerror)orbyaninstruction.

Providedtheinterruptispermitted,itwillbeacknowledgedbytheprocessorattheendofthe

current memory cycle. The processor then services the interrupt by branching to a special

service routine written to handle that particular interrupt. Upon servicing the device, the

processoristheninstructedtocontinuewithwhatiswasdoingpreviouslybyuseofthe"return

frominterrupt"instruction.

Thestatusoftheprogrammebeingexecutedmustfirstbesaved.Theprocessorsregisterswill

besavedonthestack,or,atveryleast,theprogrammecounterwillbesaved.Preservingthose

registerswhicharenotsavedwillbetheresponsibilityoftheinterruptserviceroutine.Oncethe

programme counter has been saved, the processor will branch to the address of the service

routine.

EdgeorLevelsensitiveInterrupts

Edgelevelinterruptsarerecognisedonthefallingorrisingedgeoftheinputsignal.Theyare

generallyusedforhighpriorityinterruptsandarelatchedinternallyinsidetheprocessor.Ifthis

latching was not done, the processor could easily miss the falling edge (due to its short

duration)andthusnotrespondtotheinterruptrequest.

Levelsensitiveinterruptsovercometheproblemoflatching,inthattherequestingdeviceholds

theinterruptlineataspecifiedlogicstate(normallylogiczero)tilltheprocessoracknowledges

theinterrupt.Thistypeofinterruptcanbesharedbyotherdevicesinawired'OR'configuration,

whichiscommonlyusedtosupportdaisychainingandothertechniques.

MaskableInterrupts

Theprocessorcaninhibitcertaintypesofinterruptsbyuseofaspecialinterruptmaskbit.This

maskbitispartoftheflags/conditioncoderegister,oraspecialinterruptregister.Inthe8086

microprocessor if this bit is clear, and an interrupt request occurs on the Interrupt Request

input,itisignored.

NonMaskableInterrupts

Therearesomeinterruptswhichcannotbemaskedoutorignoredbytheprocessor.Theseare

associatedwithhighprioritytaskswhichcannotbeignored(likememoryparityorbusfaults).In

general, most processors support the NonMaskable Interrupt (NMI). This interrupt has

absolute priority, and when it occurs, the processor will finish the current memory cycle, then

branchtoaspecialroutinewrittentohandletheinterruptrequest.

http://www.electronics.dit.ie/staff/tscarff/Interrupts/interrupts.htm

1/8

7/7/2015

ANINTRODUCTIONTOINTERRUPTS

AdvantagesofInterrupts

Interruptsareusedtoensureadequateserviceresponsetimesbytheprocessing.Sometimes,

withsoftwarepollingroutines,servicetimesbytheprocessorcannotbeguaranteed,anddata

maybelost.Theuseofinterruptsguaranteesthattheprocessorwillservicetherequestwithin

aspecifiedtimeperiod,reducingthelikelihoodoflostdata.

InterruptLatency

ThetimeintervalfromwhentheinterruptisfirstassertedtothetimetheCPUrecognisesit.This

will depend much upon whether interrupts are disabled, prioritized and what the processor is

currently executing. At times, a processor might ignore requests whilst executing some

indivisible instruction stream (readwritemodify cycle). The figure that matters most is the

longestpossibleinterruptlatencytime.

InterruptResponseTime

The time interval between the CPU recognising the interrupt to the time when the first

instruction of the interrupt service routine is executed. This is determined by the processor

architectureandclockspeed.

TheOperationofanInterruptsequenceonthe8086

Microprocessor:

1.Externalinterfacesendsaninterruptsignal,totheInterruptRequest(INTR)pin,oran

internalinterruptoccurs.

2.TheCPUfinishesthepresentinstruction(forahardwareinterrupt)andsendsInterrupt

Acknowledge(INTA)tohardwareinterface.

3.TheinterrupttypeNissenttotheCentralProcessorUnit(CPU)viatheDatabusfromthe

hardwareinterface.

4.Thecontentsoftheflagregistersarepushedontothestack.

5.Boththeinterrupt(IF)and(TF)flagsarecleared.ThisdisablestheINTRpinandthetrapor

singlestepfeature.

6.Thecontentsofthecodesegmentregister(CS)arepushedontotheStack.

7.Thecontentsoftheinstructionpointer(IP)arepushedontotheStack.

8.Theinterruptvectorcontentsarefetched,from(4xN)andthenplacedintotheIPandfrom

(4xN+2)intotheCSsothatthenextinstructionexecutesattheinterruptserviceprocedure

addressedbytheinterruptvector.

9.WhilereturningfromtheinterruptserviceroutinebytheInterruptReturn(IRET)instruction,

http://www.electronics.dit.ie/staff/tscarff/Interrupts/interrupts.htm

2/8

7/7/2015

ANINTRODUCTIONTOINTERRUPTS

theIP,CSandFlagregistersarepoppedfromtheStackandreturntotheirstatepriortothe

interrupt.

MultipleInterrupts

Ifmorethanonedeviceisconnectedtotheinterruptline,theprocessorneedstoknowtowhich

device service routine it should branch to. The identification of the device requesting service

canbedoneineitherhardwareorsoftware,oracombinationofboth.Thethreemainmethods

are:

1. SoftwarePolling,

2. HardwarePolling,(DaisyChain),

3. HardwareIdentification(VectoredInterrupts).

SoftwarePollingDeterminationoftheRequestingDevice

Asoftwareroutineisusedtoidentifythedevicerequestingservice.Asimplepollingtechnique

isused,eachdeviceischeckedtoseeifitwastheoneneedingservice.

http://www.electronics.dit.ie/staff/tscarff/Interrupts/interrupts.htm

3/8

7/7/2015

ANINTRODUCTIONTOINTERRUPTS

Havingidentifiedthedevice,theprocessorthenbranchestotheappropriateinterrupthandling

routine address for the given device. The order in which the devices appear in the polling

sequencedeterminestheirpriority.

SummaryofSoftwarePolledI/O

PollingisthemostcommonandsimplestmethodofI/Ocontrol.Itrequiresnospecialhardware

and all I/O transfers are controlled by the CPU programme. Polling is a synchronous

mechanism,bywhichdevicesareservicedinsequentialorder.

http://www.electronics.dit.ie/staff/tscarff/Interrupts/interrupts.htm

4/8

7/7/2015

ANINTRODUCTIONTOINTERRUPTS

Thepollingtechnique,however,haslimitations.

1)itiswastefuloftheprocessorstime,asitneedlesslychecksthestatusofalldevicesallthe

time,

2)itisinherentlyslow,asitchecksthestatusofallI/Odevicesbeforeitcomesbacktocheck

anygivenoneagain,

3) when fast devices are connected to a system, polling may simply not be fast enough to

satisfytheminimumservicerequirements,

4) priority of the device is determined by the order in the polling loop, but it is possible to

changeitviasoftware.

Software/HardwareDrivenIdentification(DaisyChain)

Thisissignificantlyfasterthanapuresoftwareapproach.Adaisychainisusedtoidentifythe

devicerequestingservice.

http://www.electronics.dit.ie/staff/tscarff/Interrupts/interrupts.htm

5/8

7/7/2015

ANINTRODUCTIONTOINTERRUPTS

DaisyChainPollingArangement

Daisy chaining is used for level sensitive interrupts, which act like a wired 'OR' gate. Any

requestingdevicecantaketheinterruptlinelow,andkeepitassertedlowuntilitisserviced.

Because more than one device can assert the shared interrupt line simultaneously, some

method must be employed to ensure device priority. This is done using the interrupt

acknowledgesignalgeneratedbytheprocessorinresponsetoaninterruptrequest.

Eachdeviceisconnectedtothesameinterruptrequestline,buttheinterruptacknowledgeline

ispassedthrougheachdevice,fromthehighestprioritydevicefirst,tothelowestprioritydevice

last.

Afterpreservingtherequiredregisters,themicroprocessorgeneratesaninterruptacknowledge

signal. This is gated through each device. If device 1 generated the interrupt, it will place its

identificationsignalonthedatabus,whichisreadbytheprocessor,andusedtogeneratethe

addressoftheinterruptserviceroutine.Ifdevice1didnotrequesttheservicing,itwillpassthe

interrupt acknowledge signal on to the next device in the chain. Device 2 follows the same

procedure,andsoon.

HardwareIdentification(VectoredInterrupts)

Thisisthefastestsystem.Theonusisplacedontherequestingdevicetorequesttheinterrupt,

andidentifyitself.Theidentitycouldbeabranchingaddressforthedesiredinterrupthandling

routine.

If the device just supplies an identification number, this can be used in conjunction with a

lookup table to determine the address of the required service routine. Response time is best

whenthedevicerequestingservicealsosuppliesabranchingaddress.

http://www.electronics.dit.ie/staff/tscarff/Interrupts/interrupts.htm

6/8

7/7/2015

ANINTRODUCTIONTOINTERRUPTS

PriorityInterruptManagementController

Priority Interrupt Controller Chips (PIC's) are hardware chips designed to make the task of a

devicepresentingitsownaddresstotheCPUsimple.ThePICalsoassessesthepriorityofthe

devices connected to it. Modern PIC's can also be programmed to prevent the generation of

interruptswhicharelowerthanadesiredlevel.

Thedecodedlocationisconnectedtotheoutputofapriorityencoder.Theinputofthepriority

encoder is connected to each device. When a device requests service, the priority encoder

presentsaspecialcodecombination(uniqueforeachdevice)tothedecodedmemorylocation.

Theportthusholdsthevalueoraddressassociatedwiththehighestdevicerequestingservice.

The priority encoder arranges all devices in a list, devices given a lower priority are serviced

when no other higher priority devices need servicing. This simplifies the software required to

determinethedevice,resultinginanincreaseinspeed.

Thedisadvantagesare:

http://www.electronics.dit.ie/staff/tscarff/Interrupts/interrupts.htm

7/8

7/7/2015

ANINTRODUCTIONTOINTERRUPTS

1)theextrachiprequired,

2)resultantincreasesincost,

3)moreboardspaceandpowerconsumption,

4)fixedpriorityinhardware.

http://www.electronics.dit.ie/staff/tscarff/Interrupts/interrupts.htm

8/8

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Electronics GuideDocument22 pagesElectronics GuideFernandes KennethNo ratings yet

- Xer Schedule Toolkit Manual PDFDocument33 pagesXer Schedule Toolkit Manual PDFringlove97No ratings yet

- Technology and Livelihood EducationDocument56 pagesTechnology and Livelihood EducationDerick B. PicardoNo ratings yet

- Network Connection Policy SummaryDocument2 pagesNetwork Connection Policy SummaryAmine RachedNo ratings yet

- VHDL TutorialDocument68 pagesVHDL TutorialPedro Pablo Parra AlbaNo ratings yet

- DDAC AssignmentDocument26 pagesDDAC AssignmentHoo Johnny33% (3)

- Extension FunctionsDocument274 pagesExtension FunctionshisureshkNo ratings yet

- DramDocument3 pagesDramMANIKANDANNo ratings yet

- VHDL Implementation of Manchester Encoder and DecoderDocument5 pagesVHDL Implementation of Manchester Encoder and DecoderMANIKANDANNo ratings yet

- Lpc2148 DatasheetDocument38 pagesLpc2148 DatasheetSandeep ThompsonNo ratings yet

- Std10 Science EM 1Document71 pagesStd10 Science EM 1MANIKANDANNo ratings yet

- MicroC2 eCh15L08ARMDevelopmentToolsDocument39 pagesMicroC2 eCh15L08ARMDevelopmentToolsMANIKANDANNo ratings yet

- Analogue To Digital Converters (ADC)Document3 pagesAnalogue To Digital Converters (ADC)MANIKANDANNo ratings yet

- Memory Timing AnalysisDocument3 pagesMemory Timing AnalysisMANIKANDANNo ratings yet

- SubroutinesDocument1 pageSubroutinesMANIKANDANNo ratings yet

- Jump and Branch InstructionsDocument1 pageJump and Branch InstructionsMANIKANDANNo ratings yet

- Program Control InstructionsDocument3 pagesProgram Control InstructionsMANIKANDANNo ratings yet

- Formal Report 1: Arrange 10 Numbers in Ascending OrderDocument2 pagesFormal Report 1: Arrange 10 Numbers in Ascending OrderMANIKANDANNo ratings yet

- 6800 Address ModesDocument1 page6800 Address ModesMANIKANDANNo ratings yet

- 6800 Internal RegistersDocument3 pages6800 Internal RegistersMANIKANDANNo ratings yet

- VHDL FSM Tutorial MY FIRST FSMDocument29 pagesVHDL FSM Tutorial MY FIRST FSMMANIKANDANNo ratings yet

- FT021/3 Computer Systems Summer 2004Document2 pagesFT021/3 Computer Systems Summer 2004MANIKANDANNo ratings yet

- Pic16f8x PDFDocument126 pagesPic16f8x PDFGilberto MataNo ratings yet

- Review QuestionsDocument4 pagesReview QuestionsMANIKANDANNo ratings yet

- Formal Report 1: Arrange 10 Numbers in Ascending OrderDocument2 pagesFormal Report 1: Arrange 10 Numbers in Ascending OrderMANIKANDANNo ratings yet

- FT021/3 Computer Systems Summer 2004Document2 pagesFT021/3 Computer Systems Summer 2004MANIKANDANNo ratings yet

- Memory Timing AnalysisDocument3 pagesMemory Timing AnalysisMANIKANDANNo ratings yet

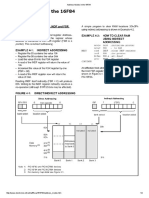

- Address Modes in The 16F84Document2 pagesAddress Modes in The 16F84MANIKANDANNo ratings yet

- Numbering Systems TutorialDocument5 pagesNumbering Systems TutorialMANIKANDANNo ratings yet

- Delay LoopsDocument2 pagesDelay LoopsMANIKANDANNo ratings yet

- Introduction To Parallel PortsDocument5 pagesIntroduction To Parallel PortsMANIKANDANNo ratings yet

- Using EcalDocument4 pagesUsing EcalMANIKANDANNo ratings yet

- Fetch and ExecuteDocument2 pagesFetch and ExecuteMANIKANDANNo ratings yet

- 6800 Internal RegistersDocument3 pages6800 Internal RegistersMANIKANDANNo ratings yet

- Memory Timing AnalysisDocument3 pagesMemory Timing AnalysisMANIKANDANNo ratings yet

- Variables of JavaDocument6 pagesVariables of JavaClanNo ratings yet

- ISA Definition and MIPS ExamplesDocument3 pagesISA Definition and MIPS ExamplesMANAS AGARWALNo ratings yet

- Expl WAN Chapter 1 Intro WANsDocument82 pagesExpl WAN Chapter 1 Intro WANsLeo LaguiNo ratings yet

- SAS NotesDocument57 pagesSAS Notesapi-3853979100% (1)

- C Programming MCQs and QuestionsDocument7 pagesC Programming MCQs and QuestionsAmit sinhaNo ratings yet

- Harmonic Config Man MibDocument16 pagesHarmonic Config Man MibJohn SmithNo ratings yet

- Javascript Extensibility ExampleDocument6 pagesJavascript Extensibility ExampleAxl AxlNo ratings yet

- PHP&SQL ជាភាសាខ្មែរDocument70 pagesPHP&SQL ជាភាសាខ្មែរsovanpanha2003No ratings yet

- Infobright ICE User GuideDocument62 pagesInfobright ICE User Guidepeterpan107No ratings yet

- Database Design TheoryDocument32 pagesDatabase Design TheoryHidayah SanifNo ratings yet

- Software Development and Collaboration: Version Control Systems and Other ApproachesDocument10 pagesSoftware Development and Collaboration: Version Control Systems and Other ApproachesSandraNo ratings yet

- API PRO 9 Installation GuideDocument134 pagesAPI PRO 9 Installation GuideDanielNo ratings yet

- Hadoop Daemons ExplainedDocument3 pagesHadoop Daemons ExplainedSrinivas ReddyNo ratings yet

- CN BlueDocument107 pagesCN BluesadfNo ratings yet

- BDC CALL METHODDocument9 pagesBDC CALL METHODAnonymous 0wXXmp1No ratings yet

- Week 3 Module 3 Graded QuizDocument6 pagesWeek 3 Module 3 Graded QuizFatih FidanNo ratings yet

- Kubernates Kubectl Context and Configuration: Authenticating Across Clusters With KubeconfigDocument9 pagesKubernates Kubectl Context and Configuration: Authenticating Across Clusters With KubeconfigTymon ChikosiNo ratings yet

- P6 Job Services and Why F5 Is Your Friend!Document3 pagesP6 Job Services and Why F5 Is Your Friend!jrojasferrerNo ratings yet

- f5 Arcsight F5BIG-IPsyslogConfigDocument12 pagesf5 Arcsight F5BIG-IPsyslogConfigsachinkoenigNo ratings yet

- TC Log stk1Document6 pagesTC Log stk1JuanoNo ratings yet

- Practice Problems for Bit-oriented Protocols LectureDocument39 pagesPractice Problems for Bit-oriented Protocols LectureRizwan Aslam ButtNo ratings yet

- Data Representation Methods and CPU Data TypesDocument19 pagesData Representation Methods and CPU Data TypesGayle Marie RosalesNo ratings yet

- WsoDocument37 pagesWsozenchuaNo ratings yet

- Suv400s3 UsDocument2 pagesSuv400s3 UsLjubisa PejinNo ratings yet

- IssuesDocument14 pagesIssuessrimkbNo ratings yet