Professional Documents

Culture Documents

Codigo de Colores

Uploaded by

Gefry Andres Castro Jimenez0 ratings0% found this document useful (0 votes)

10 views2 pagesCodigo de Colores

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCodigo de Colores

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views2 pagesCodigo de Colores

Uploaded by

Gefry Andres Castro JimenezCodigo de Colores

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 2

FACULTAD DE INGENIERIA, BIOINGENIERIA I, FEBRERO 2014

Codigo de Colores Para la Posicion de los

Electrodos en un ECG

Gefry A. Castro

ResumenEn este documento se pretende mostrar de manera

breve el codigo de colores utilizado para identificar la posicion

que llevan los electrodos en el cuerpo humano durante un ECG.

Palabras ClavesCodigo de colores, ECG.

I.

I NTRODUCCI ON

STE documento pretende mostrar algunos aspectos

generales en el funcionamiento y configuracion de los

elementos utilizados para la digitalizacion de audio.

En primer lugar, el PsoC cuenta con un conversor Analogico

digital Delta-Sigma que provee medidas de precision para

aplicaciones que requieran bajo ruido. El ADC esta compuesto

por tres bloques: un amplificador de entrada, un modulador

delta-sigma de tercer orden y un decimador como se aprecia en

la figura ??. para mayor informacion sobre el funcionamiento

del ADC se invita al lector dirigirse a [3].

Otro componente de gran importancia en el procesamiento

y reproduccion de senales de audio, es el DAC, que en este

caso es un conversor analogico a digital predefinido de 8 bits,

que cuenta con dos modos de velocidad y resolucion,salida

de voltaje o corriente y que puede ser manejado ya sea por

software, hardware o una combinacion de ambos. En la figura

?? se muestra un diagrama de bloques del componente y en

[4] se encuentra mayor informacion sobre su funcionamiento.

II.

II-A.

D ESARROLLO Y RESULTADOS

Planteamiento del problema

Disenar e implementar un sistema de digitalizacion de

senales de audio, el cual debe tomar una senal de audio,

digitalizarla con el ADC interno del PSoC y reconstruirla con

el DAC interno del PSoC para luego reproducirla.

Se deben incluir todos los elementos necesarios para adaptar

la senal de entrada al PSoC. Para la salida si fuera necesario se

deben implementar filtros, se requiere ademas un amplificador

para la reproduccion del audio, para esto se puede utilizar uno

ya implementado (parlante de un PC, entrada auxiliar de un

reproductor de audio comercial, etc.).

Gefry A. Castro, Estudiante Ingeniera Electronica, Universidad Distrital Francisco Jose de Caldas Codigo: 20092005059, e-mail: gacastroj@correo.udistrital.edu.co

II-B.

Solucion del Problema

El primer paso en el diseno es tener en cuenta los

diferentes aspectos que hacen parte de la configuracion del

ADC y brindan un mejor desempeno, los cuales son de gran

importancia y debido a que son un poco extensos, se invita

al lector a consultar [2] con el fin de revisarlos.

Debido a que la senal de audio que recibe el ADC se

encuentra dentro de unos niveles de tension manejables, no

se hace necesario la amplificacion de la senal por lo cual el

buffer de entrada del ADC sera deshabilitado (Bypass Buffer)

lo que ayudara a reducir el ruido, pero eso no significa que

la senal no deba ser tratada al momento de ingresar al ADC.

Para esto, la senal pasara por un sumador no inversor (ver

figura ??) , el cual permite modificar el nivel DC que se le

este sumando mediante un potenciometro (salida VR de la

placa de desarrollo del PSoC) con el fin de corregir futuras

modificaciones. Esto debido a que el ADC estara trabajando

en modo no diferencial (single ended mode) y el nivel DC

perimite que la lectura de la senal de audio se haga dentro

del rango de entrada del ADC.

Por otra parte, la resolucion sera de ocho bits debido a que el

DAC cuenta con esa misma propiedad, el modo de conversion

sera continuo, ya que en el caso de procesamiento de senales

de audio es lo ideal. La frecuencia de muestreo, la cual debe

cumplir la condicion de Nyquist se escogio a una frecuencia

muy por encima del doble de la frecuencia maxima del rango

audible (20 KHz). Adicionalmente, para la entrada se tiene un

rango de voltajes que van desde cero voltios hasta el doble

del voltaje de referencia (Vref = Vdda/4 = 1.25 V) con el

fin de aprovechar mejor la resolucion y mantener un limite

aceptable en caso del incremento en la amplitud de la senal.

A continuacion se muestra una imagen con la configuracion

del ADC:

El siguiente paso en el diseno es la configuracion del DAC,

cuya resolucion viene fija a ocho bits, y cuyos parametros se

muestran en la figura ??.

Una vez la senal haya salido del DAC, se puede

implementar un filtro pasabajos, pero en este caso debido

a la calidad de audio y a que las frecuencias superiores no

presentan inconvenientes, se opto por usar a la salida un

amplificador operacional en modo buffer como se muestra en

la figura ??. En la figura ?? se muestra el esquema completo.

Una vez realizado el esquema y la configuracion del

circuito, el paso a seguir es escoger los pines que se haran

FACULTAD DE INGENIERIA, BIOINGENIERIA I, FEBRERO 2014

cargo de las diferentes tareas, en la figura ?? se tienen las

entradas Signal y Level, que corresponden a la senal de

audio de entrada y al nivel DC variable respectivamente

que ingresan al sumador, y el pin V L que se conecta a las

resistencias de tierra y realimentacion. Tambien se encuentran

los pines V OUT 1, ADC IN y DAC OUT que se encargan

en ese orden de entregar la senal sumada con el nivel DC,

obtener dicha senal y entregarla al sistema de reproduccion

de audio. Esta distribucion de pines se aprecia en la figura

??.

Como siguiente paso, se escribe el codigo que realizara la

tarea, el cual se muestra a continuacion:

int main()

{

OPAMP_1_Start();

ADC_Start();

ADC_StartConvert();

DAC_Start();

OPAMP_2_Start();

for(;;)

{

DAC_SetValue(ADC_GetResult8());

}

}

El codigo muestra la inicializacion de todos los componentes, y el ciclo infinito donde se estara pasando el valor que lea

el ADC directamente al DAC.

III.

C ONCLUSIONES

En todo proceso de diseno, es conveniente descomponer el

problema en multiples problemas de menor dificultad, esto con

el fin de poder observar en cada etapa las ventajas, desventajas

y limitaciones que puedan tener sobre el comportamiento total

del sistema. En este caso, el acondicionamiento de la senal

de entrada, la configuracion del ADC y la senal de salida se

tuvieron en cuenta para formar la solucion al problema.

El acondicionamiento de la senal de entrada y de salida

es un factor de gran importancia a la hora de realizar la

conversion y reproduccion, ya que estas etapas definen en

gran parte la calidad de la senal de entrada y su posterior

procesamiento, por lo que a la entrada en vez de emplear un

sumador conformado por resistencias, que incrementa en gran

parte el ruido, se opto por implementar un sumador utilizando

los amplificadores operacionales internos del PSoC, y a la

senal de salida un buffer.

R EFERENCIAS

[1] Camargo Julian, Guia de Laboratorio 2, Universidad Distrital, 2013.

[2] Cypress

Application

Note,

Accurate

Measurement

Using

PSoC 3 and PSoC 5LP Delta-Sigma ADCs, AN84783

http://www.cypress.com/?docID=44512

[3] Cypress Component Datasheet, Delta Sigma Analog to Digital Converter

(ADC DelSig) http://www.cypress.com/?rID=48916

[4] Cypress Component Datasheet, 8-Bit Voltage Digital to Analog Converter

(VDAC8) http://www.cypress.com/?rID=49054

You might also like

- Madeleine Mansion - El Estudio Del CantoDocument77 pagesMadeleine Mansion - El Estudio Del CantoGerson Linares Silva92% (12)

- Respiracion CantoDocument13 pagesRespiracion CantoMilton Hernández GarcíaNo ratings yet

- Power Transformer Testing Brochure ESPDocument36 pagesPower Transformer Testing Brochure ESPArturo De Asis Splush100% (1)

- Qué Es La BiologíaDocument28 pagesQué Es La BiologíaGefry Andres Castro JimenezNo ratings yet

- Desarrollo de Un Sistema Vestible de Medición de Variables FisiológicasDocument5 pagesDesarrollo de Un Sistema Vestible de Medición de Variables FisiológicasGefry Andres Castro JimenezNo ratings yet

- AFSPA009Document12 pagesAFSPA009Gefry Andres Castro JimenezNo ratings yet

- Television Practica 1Document5 pagesTelevision Practica 1Gefry Andres Castro JimenezNo ratings yet

- Capitulo 7Document30 pagesCapitulo 7Grober SCNo ratings yet

- Enfermedades Arrecifes de Coral. InvemarDocument36 pagesEnfermedades Arrecifes de Coral. InvemarGefry Andres Castro JimenezNo ratings yet

- Probabilidad y Aplicaciones Estadisticas Paul Meyer PDFDocument191 pagesProbabilidad y Aplicaciones Estadisticas Paul Meyer PDFGefry Andres Castro JimenezNo ratings yet

- Informe Corales MexicoDocument40 pagesInforme Corales MexicoGefry Andres Castro JimenezNo ratings yet

- Documento Simposio Modelación Hábitat y Distribución Mamíferos 2015Document3 pagesDocumento Simposio Modelación Hábitat y Distribución Mamíferos 2015Gefry Andres Castro JimenezNo ratings yet

- Cartilla Cnidaria PDFDocument7 pagesCartilla Cnidaria PDFGefry Andres Castro JimenezNo ratings yet

- NSR-10 Titulo ADocument186 pagesNSR-10 Titulo AAngel De La Torre Coll50% (2)

- Biochemistry 1Document31 pagesBiochemistry 1Léo AyolNo ratings yet

- Integracion y LatinoamericanismoDocument203 pagesIntegracion y LatinoamericanismoIsel Judit TalaveraNo ratings yet

- Estado Del Arte OvaDocument160 pagesEstado Del Arte OvaMichael LewisNo ratings yet

- Enfoques Estratégicos Sobre Las TICs en Educación en América Latina y El CaribeDocument62 pagesEnfoques Estratégicos Sobre Las TICs en Educación en América Latina y El CaribeTICparaEducacion100% (2)

- Citocromo P450Document34 pagesCitocromo P450Miguel Angel Gómez Ramos100% (1)

- RESUMEN Practica 2 de EspectrofotometriaDocument1 pageRESUMEN Practica 2 de EspectrofotometriaGefry Andres Castro JimenezNo ratings yet

- Libro-Metodologia de La Investigacion-TamayoDocument140 pagesLibro-Metodologia de La Investigacion-Tamayowilberthh89% (44)

- Probabilidad y Aplicaciones Estadisticas Paul Meyer PDFDocument191 pagesProbabilidad y Aplicaciones Estadisticas Paul Meyer PDFGefry Andres Castro JimenezNo ratings yet

- Areas Coralinas de ColombiaDocument178 pagesAreas Coralinas de ColombiaGefry Andres Castro JimenezNo ratings yet

- Cinetica QuimicaDocument9 pagesCinetica QuimicaFrancisco Curro PérezNo ratings yet

- Ocean AcidificationDocument2 pagesOcean Acidificationanakarenina1No ratings yet

- Biota 15 RestauracionEcologica-2014 BajaDocument162 pagesBiota 15 RestauracionEcologica-2014 BajaJorge OsorioNo ratings yet

- Relación Entre La Intervención Nutricional y La Calidad de Vida Del Paciente PDFDocument14 pagesRelación Entre La Intervención Nutricional y La Calidad de Vida Del Paciente PDFGefry Andres Castro JimenezNo ratings yet

- Los plásticos: materiales omnipresentes en la vida modernaDocument35 pagesLos plásticos: materiales omnipresentes en la vida modernamarajevas50% (2)

- 10447AtlasSAISeaflower PDFDocument184 pages10447AtlasSAISeaflower PDFGefry Andres Castro JimenezNo ratings yet

- DiversdiversidadDocument204 pagesDiversdiversidadGreissy Campos CabreraNo ratings yet

- Gamoru Fallas ElectronicaDocument12 pagesGamoru Fallas ElectronicaJuan Leonardo SanabriaNo ratings yet

- RT2 Espa Olas Manual PDFDocument48 pagesRT2 Espa Olas Manual PDFJMART29No ratings yet

- Cuánto Sabes de Computación BásicaDocument7 pagesCuánto Sabes de Computación BásicaiirmiithaaNo ratings yet

- ForoDocument2 pagesForoJefry MateusNo ratings yet

- Control Rondas e GuardDocument27 pagesControl Rondas e GuardMauricio Parra BolivarNo ratings yet

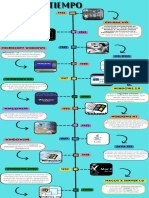

- Línea Del Tiempo ComputaciónDocument5 pagesLínea Del Tiempo Computaciónfrida CastellónNo ratings yet

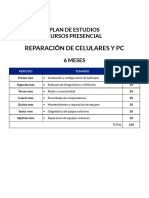

- Reparación de Celulares y PCDocument5 pagesReparación de Celulares y PCAlessandro RafaelNo ratings yet

- Fecha de Creación de WordDocument10 pagesFecha de Creación de WordMarlon ChiyalNo ratings yet

- Selección Mezclador Audio Banda MúsicaDocument3 pagesSelección Mezclador Audio Banda MúsicaVictor Alvarez LopezNo ratings yet

- Algoritmos en PseintDocument5 pagesAlgoritmos en PseintJose Elias Ramos MarchenaNo ratings yet

- Manual de instrucciones HD TV 42 PlasmaDocument40 pagesManual de instrucciones HD TV 42 PlasmachoneroNo ratings yet

- Ejercicios de Paralelismo A Nivel de InstrucciónDocument10 pagesEjercicios de Paralelismo A Nivel de InstrucciónAngel Garcia XdNo ratings yet

- Lista de Cambios W10P DR Lite 2.7 Final 062022Document4 pagesLista de Cambios W10P DR Lite 2.7 Final 062022José Andrés Rivera RománNo ratings yet

- Herencia PDFDocument15 pagesHerencia PDFBrianNo ratings yet

- Respaldo de InformaciónDocument3 pagesRespaldo de InformaciónPamela DanaeNo ratings yet

- PHP Es Un Lenguaje de Programación InterpretadoDocument14 pagesPHP Es Un Lenguaje de Programación InterpretadoKevin Robin Salazar RiosNo ratings yet

- El Lector 2008 05 No 335Document88 pagesEl Lector 2008 05 No 335atom2013xdNo ratings yet

- Infografia Linea Del Tiempo Timeline Historia Cronologia Empresa Profesional MulticolorDocument2 pagesInfografia Linea Del Tiempo Timeline Historia Cronologia Empresa Profesional MulticolorAliison PerezNo ratings yet

- Gestión de Servicios - ProcedimientoDocument16 pagesGestión de Servicios - ProcedimientoJuan SanchezNo ratings yet

- Comandos Impresora BIXOLON SRP-350 SpanishDocument29 pagesComandos Impresora BIXOLON SRP-350 SpanishrafaelcastillohNo ratings yet

- Analogo TM-628HDocument2 pagesAnalogo TM-628Hstickers caserosNo ratings yet

- Configuración del sistema MSCONFIG para optimizar el arranque de WindowsDocument11 pagesConfiguración del sistema MSCONFIG para optimizar el arranque de WindowsFabiola VelozNo ratings yet

- Capt 7 Circuitos Integrados LSI SPLD y Sus AplicacionesDocument16 pagesCapt 7 Circuitos Integrados LSI SPLD y Sus AplicacionesCarlos Carreño Muñoz0% (1)

- Universidad Mariano Galvez de GuatemalaDocument3 pagesUniversidad Mariano Galvez de GuatemalaLuis RamírezNo ratings yet

- CV (2017)Document3 pagesCV (2017)Luis LopzNo ratings yet

- Manual Geovision 6.1 EspañolDocument245 pagesManual Geovision 6.1 EspañolvictorsemifusaNo ratings yet

- El AhorcadoDocument36 pagesEl AhorcadoSamantha Gó GoNo ratings yet

- Que Es HardwareDocument19 pagesQue Es HardwareBenjamin Santos Salinas100% (1)

- Informe Tecnico U2 - Circuitos Electricos y ElectronicosDocument8 pagesInforme Tecnico U2 - Circuitos Electricos y ElectronicosVector SmitNo ratings yet

- Fichas Hemerografica, Internet y BibliográficasDocument4 pagesFichas Hemerografica, Internet y Bibliográficasenriquesito5No ratings yet