Professional Documents

Culture Documents

Leakage Reduction Using Self-Controlled Leakage Transistors

Uploaded by

AkOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Leakage Reduction Using Self-Controlled Leakage Transistors

Uploaded by

AkCopyright:

Available Formats

LEAKAGE POWER REDUCTION IN CMOS CIRCUITS USING

LEAKAGE CONTROL TRANSISTOR TECHNIQUE IN NANOSCALE

TECHNOLOGY

B. DILIP1, P. SURYA PRASAD2 & R. S. G. BHAVANI3

1&2

Dept. of ECE, MVGR college of Engineering, Vizianagaram, AP, India

3

Dept. of ECE, JNTU Kakinada, AP, India

E-mail : dil.bagadi@gmail.com1, suryaprasadp@yahoo.com2, bhavani.rsg@gmail.com3

Abstract In CMOS circuits, as the technology scales down to nanoscale, the sub-threshold leakage current increases with

the decrease in the threshold voltage. LECTOR, a technique to tackle the leakage problem in CMOS circuits, uses two

additional leakage control transistors, which are self-controlled, in a path from supply to ground which provides the

additional resistance thereby reducing the leakage current in the path. The main advantage as compared to other techniques

which involves the sleep transistor is that LECTOR technique does not require any additional control and monitoring

circuitry, thereby limits the area increase and also the power dissipation in active state. Along with this, the other advantage

with LECTOR technique is that it does not affect the dynamic power which is the major limitation with the other leakage

reduction techniques.

Keywords - subthreshold leakage current; transistor stacking; self-controlled LCTs; deep-submicron.

I.

INTRODUCTION

The rapid progresses in semiconductor

technology have leaded the feature sizes to be shrunk

through the use of deep-submicron processes; thereby

the extremely complex functionality is enabled to be

integrated on a single chip. In the growing market of

mobile hand-held devices used all over the world

today, the battery-powered electronic system forms

the backbone. To maximize the battery life, the

tremendous computational capacity of portable

devices such as notebook computers, personal

communication devices (mobile phones, pocket PCs,

PDAs), hearing aids and implantable pacemakers has

to be realized with very low power requirements.

With miniaturization and the growing trend towards

wireless communication, power dissipation has

become a very critical design metric. The longer the

battery lasts, the better is the device.

The power dissipation has not diminished even

with the scaling down of the supply voltage. The

problem of heat removal and power dissipation is

getting worse as the magnitude of power per unit area

has kept growing. For the rapid increase in power

consumption of present day chips, the innovative

cooling and packaging strategies are of little help.

Also, the cost associated with the packaging and the

cooling of such devices is becoming prohibitive. In

addition to cost, the issue of reliability is a major

concern. Component failure rate roughly doubles for

every 10oC increase in operating temperature. With

the on-chip devices doubling every two years,

minimizing the power consumption has became

currently an extremely challenging area of research.

Fig. 1 : Static CMOS leakage sources.

Leakage power of a CMOS transistor depends on

gate length and oxide thickness [4]. To decrease the

dynamic power, the supply voltage is decreased

which leads to the performance degradation. To speed

up the device, the threshold voltage should also be

scaled down along with the supply voltage, which

results in exponential increase in the sub-threshold

leakage current, thereby increase in the static power

dissipation. The main components of leakage current

in a MOS transistor are shown in Figure 1.

Fig. 2 : Reverse current in CMOS inverter

International Journal of Electronics Signals and Systems (IJESS) ISSN: 2231- 5969, Vol-2 Iss-1, 2012

72

Leakage Power Reduction in CMOS Circuits using Leakage Control Transistor Technique in Nanoscale Technology

The leakage power in a CMOS is due to subthreshold leakage current; which is the reverse

current flowing through the OFF transistor, indicated

with arrows in Figure 2. As the technology scales

down which is the shrinking of feature size of

transistor, the channel length decreases, thereby

increasing the amount of leakage power in the total

power dissipated as shown in Figure 3.

and Vdd and pull-down networks and gnd while for

fast switching speeds, low-Vth transistors are used in

logic circuits [8]. Isolating the logic networks, this

technique dramatically reduces leakage power during

sleep mode. However, the area and delay are

increased due to additional sleep transistors. During

the sleep mode, the state will be lost as the pull-up

and pull-down networks will have floating values.

These values impact the wakeup time and energy

significantly due to the requirement to recharge

transistors which lost state during sleep.

C. Forced Stack

In this technique, every transistor in the network

is duplicated with both the transistors bearing half the

original transistor width [6]. Duplicated transistors

cause a slight reverse bias between the gate and

source when both transistors are turned off. Because

sub-threshold current is exponentially dependent on

gate bias, it obtains substantial current reduction. It

overcomes the limitation with sleep technique by

retaining state but it takes more wakeup time.

D. ZIGZAG Technique

Wake-up cost can be reduced in zigzag technique

but still state losing is a limitation. Thus, any

particular state which is needed upon wakeup must be

regenerated somehow. For this, the technique may

need extra circuitry to generate a specific input

vector.

E. SLEEPY STACK Technique

This technique combines the structure of the

forced stack technique and the sleep transistor

technique. In the sleepy stack technique, one sleep

transistor and two half sized transistors replaces each

existing transistor [10]. Although using of W0/2 for

the width of the sleep transistor, changing the sleep

transistor width may provide additional tradeoffs

between delay, power and area. It also requires

additional control and monitory circuit, for the sleep

transistors.

F. LEAKAGE FEEDBACK Technique

This technique is based on the sleep approach.

To maintain logic during sleep mode, the leakage

feedback technique uses two additional transistors

and the two transistors are driven by the output of an

inverter which is driven by output of the circuit

implemented utilizing leakage feedback. Performance

degradation and increase in area are the limitations

along with the limitation of sleep technique.

G. SLEEPY KEEPER Technique

This technique consists of sleep transistors

connected to the circuit with NMOS connected to

Vdd and PMOS to Gnd. This creates virtual power

and ground rails in the circuit, which affects the

switching speed when the circuit is active [9]. The

identification of the idle regions of the circuit and the

generation of the sleep signal need additional

hardware capable of predicting the circuit states

accurately, increasing the area requirement of the

circuit. This additional circuit consumes power

throughout the circuit operation to continuously

Fig. 3 : Technology Vs Leakage Power.

II. LIMITATIONS WITH RELATED WORK

A. MTCMOS

A high-threshold NMOS gating transistor is

connected between the pull-down network and the

ground, and low-threshold voltage transistors are

used in the gate. The reverse conduction paths exist,

which tends the noise margin to reduce or may result

in complete failure of the gate. There also exists a

performance penalty due to the high-threshold

transistors in series with all the switching current

paths.

Dual VT technique is a variation in MTCMOS, in

which the gates in the critical path use low-threshold

transistors and high-threshold transistors for gates in

non-critical path [3], [7]. Both the methods requires

additional mask layers for each value of VT in

fabrication, which is a complicated task depositing

two different oxides thickness, hence making the

fabrication process complex. The techniques also

suffer from turning-on latency i.e., the idle

subsections of circuit cannot be used immediately

after reactivated since some time is needed to return

to normal operating condition. The latency is

typically a few cycles for former method, and for

Dual technology, is much higher. When the circuit is

active, these techniques are not effective in

controlling the leakage power.

B. SLEEP Transistor Technique

This is a State-destructive technique which cuts

off either pull-up or pull-down or both the networks

from supply voltage or ground or both using sleep

transistors. This technique is MTCMOS, which adds

high-Vth sleep transistors between pull-up networks

International Journal of Electronics Signals and Systems (IJESS) ISSN: 2231- 5969, Vol-2 Iss-1, 2012

73

Leakage Power Reduction in CMOS Circuits using Leakage Control Transistor Technique in Nanoscale Technology

monitor the circuit state and control the sleep

transistors even though the circuit is in an idle state.

The topology of a LECTOR CMOS gate is

shown in Figure 5. Two LCTs are introduced

between nodes N1 and N2. The gate terminal of each

LCT is controlled by the source of the other, hence

termed as self-controlled stacked transistors. As

LCTs are self-controlled, no external circuit is

needed; thereby the limitation with the sleep

transistor technique has been overcome. The

introduction of LCTs increases the resistance of the

path from Vdd to Gnd, thus reducing the leakage

current.

Leakage Control TransistOR (LECTOR)

technique is illustrated in detail with the case of an

inverter. A LECTOR INVERTER is shown in Figure

6. A PMOS is introduced as LCT1 and a NMOS as

LCT2 between N1 and N2 nodes of inverter. The

output of inverter is taken from the connected drain

nodes LCT1 and LCT2. The source nodes of LCT1

and LCT2 are the nodes N1 and N2 respectively of

the pull-up and the pull-down logic. The gates of

LCT1 and LCT2 are controlled by the potential at

source terminal of LCT2 and LCT1 respectively. This

connection always keeps one of the two LCTs in its

near cutoff region for any input.

III. LECTOR TECHNIQUE

The effective stacking of transistors in the path

from supply voltage to ground is the basic idea

behind the LECTOR technique for the leakage power

reduction. This is stated based on the observation

from [1], [2] and [5] that a state is far less leaky with

more than one OFF transistor in a path from supply

voltage to ground compared to a state with only one

OFF transistor in the path. The number of OFF

transistors is related to leakage power as shown in

Figure 4.

Fig. 4 : Transistor-stacking Vs Leakage Power.

In this technique, two leakage control transistors

are introduced between pull-up and pull-down

network within the logic gate (one PMOS for pull-up

and one NMOS for pull-down) for which the gate

terminal of each leakage control transistor (LCT) is

controlled by the source of the other. This

arrangement ensures that one of the LCTs always

operates in its near cutoff region.

Fig. 6 : LECTOR based CMOS Inverter

When Vdd = 1V, input A = 0, the voltage at the

node N2 is 800 mV. LCT1 cannot be completely

turned OFF as the voltage is not sufficient. Hence, the

LCT1 resistance will be near to but slightly lesser

than its OFF resistance, allowing conduction. The

resistance provided by LCT1, even though not equal

to the OFF resistance, increases the resistance in the

path of supply voltage to ground, thereby reducing

the sub-threshold leakage current, attaining reduction

in leakage power. Similarly, when input A = 1, the

voltage at the node N1 is 200 mV; hence LCT2 will

be operated in near cutoff state. The states of all the

transistors in the LECTOR inverter for all possible

inputs are tabulated in Table I.

Fig. 5. LECTOR CMOS Gate

International Journal of Electronics Signals and Systems (IJESS) ISSN: 2231- 5969, Vol-2 Iss-1, 2012

74

Leakage Power Reduction in CMOS Circuits using Leakage Control Transistor Technique in Nanoscale Technology

TABLE I.

STATE MATRIX OF LCT INVERTER

Transistor Input Vector (A)

Reference 0

1

ON State

OFF State

M1

OFF State

ON State

M2

Near

Cut-OFF

ON State

LCT1

State

Near

Cut-OFF

ON State

LCT2

State

Along with the resistance in the path, the

propagation delay of the gate also gets increased. The

transistors of LCT inverter are sized such that the

propagation delay is reduced or equal to its base case.

In the sleep related technique, the sleep

transistors have to be able to isolate the power supply

and/or ground from the rest of the transistors of the

gate. Hence, they need to be made bulkier dissipating

more dynamic power. This offsets the savings yielded

when the circuit is idle. Sleep transistor technique

depends on input vector and it needs additional

circuitry to monitor and control the switching of sleep

transistors, consuming power in both active and idle

states. In comparison, LECTOR generates the

required control signals within the gate and is also

vector independent.

Two transistors are added in LECTOR technique

in every path from Vdd to gnd irrespective of number

of transistors in pull-up and pull-down network.

Whereas, forced stacks have 100% area overhead.

The loading requirement with LCTs is a constant

which is much lower. Whereas, the loading

requirements with forced stacks depend on number of

transistors added and are huge. Hence, the

performance degradation is insignificant in the case

of LECTOR, and we overcome the drawback faced

by forced stack technique.

Fig. 8 : Simulation waveforms of LECTOR NAND

The 2-input CMOS NAND gate is shown in

Figure 7 with the two LCTs added to pull-up and

pull-down network between the Vdd and gnd path.

The simulation waveforms of LECTOR NAND from

Figure 8 show that the basic characteristics of NAND

are retained by LECTOR NAND.

B. 4-input AND-OR-Invert

IV. APPLYING LECTOR TO CMOS CIRCUITS

Various circuit applications of the LECTOR

technique are explored in this section. The LECTOR

technique is applied to the following CMOS circuits

and also their respective base case are implemented to

calculate the amount of leakage power reduced in

LECTOR technique.

A. LECTOR based NAND gate

Fig. 9 : Four input AOI

The SCCG (static CMOS complex gate)

implementation of a 4-input AOI is shown in Figure

9, through which the area overhead can be reduced.

The LECTOR implementation here needs only two

additional transistors to be placed between the pull-up

and pull-down network at the node from which the

output is taken.

Fig. 7 : 2-input LCT NAND

International Journal of Electronics Signals and Systems (IJESS) ISSN: 2231- 5969, Vol-2 Iss-1, 2012

75

Leakage Power Reduction in CMOS Circuits using Leakage Control Transistor Technique in Nanoscale Technology

The simulation waveform shown in Figure 12

represents the LECTOR Multiplexer through which it

can be observed that its characteristics resemble that

of the conventional case.

D. Full Adder

Fig. 10 : Simulation waveforms for LECTOR AOI

Fig. 13: A Full Adder

Through the simulation waveforms shown in

Figure 10, the characteristics of LECTOR AOI

resemble the base case.

C. 4:1 Multiplexer

The Gate level schematic of Full Adder is shown

in Figure 13. The LECTOR implementation involves

the addition of two LCTs for each gate. The transistor

level schematic for ex-or gates is similar to that of

And-Or-Invert.

Fig. 14 : Simulation waveforms for LECTOR Full Adder

The simulation waveforms for full adder as

shown in Figure 14, resembles the characteristics of

conventional full adder.

V. EXPERIMENTAL RESULTS

Fig. 11: A 4:1 Multiplexer

The leakage power is measured using the

HSPICE simulator. The results obtained through the

technique for 2-input NAND gate is shown in Table

III. Simulation for the 2-input NAND is performed by

taking four different process parameters Viz. 180nm,

90nm, 65nm and 45nm.

The gate level schematic of 4:1 multiplexer is

shown in Figure 11. The LECTOR implementation

involves the addition of two LCTs in each gate

between the supply and ground path.

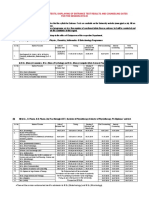

TABLE II. SUPPLY VOLTAGES AND

THRESHOLD VOLTAGE VALUES

Fig. 12: Simulation waveforms for LECTOR MUX

Technology

180nm

90nm

65nm

45nm

Supply

Voltage

1.8V

1.2V

1.1V

1V

NMOS VT

(V)

0.3999

0.2607

0.22

0.1711

PMOS VT

(V)

-0.42

-0.303

-0.22

0.1156

International Journal of Electronics Signals and Systems (IJESS) ISSN: 2231- 5969, Vol-2 Iss-1, 2012

76

Leakage Power Reduction in CMOS Circuits using Leakage Control Transistor Technique in Nanoscale Technology

The supply voltages to be considered for the four

process parameters (technologies) along with the

threshold voltages for NMOS and PMOS in the

respective technologies are as shown in Table II.

threshold voltages in order to achieve high

performance and low dynamic power dissipation,

becomes more with the deep-submicron and

nanometer technologies and thus it becomes a great

challenge to tackle the problem of leakage power.

LECTOR uses two LCTs which are self-controlled

transistors. LECTOR achieves the reduction in

leakage power like other leakage reduction

techniques, such as sleepy stack, sleepy keeper, etc,

along with the advantage of not affecting the dynamic

power, since this technique does not require any

additional control and monitor circuitry and also in

this technique, the exact logic state is maintained.

The LECTOR technique when applied to generic

logic circuits achieves up to 40-45% leakage

reduction over the respective conventional circuits

without affecting the dynamic power. A tradeoff

between Propagation delay and area overhead exists

here as the delay reduction by sizing the transistors

will increase the area overhead.

TABLE III. 2-INPUT NAND RESULTS FOR

VARIOUS TECHNOLOGIES

Leakage power

%age

(nW)

decrease in

Technology

power

Base

LECTO

dissipation

case

R

1.158

0.937

19.035

180nm

2.884

1.647

42.883

90nm

13.977

11.837

15.313

65nm

1503.66

1135.05

24.514

45nm

Table IV gives the results for 4-input AOI for 90nm

and 45nm technologies. Table V gives the results for

4:1 Multiplexer and Full Adder under 90nm process

parameters.

REFERENCES

TABLE IV. RESULTS FOR 4-INPUT AOI

4-input AOI

CONVENTION

AL

LECTOR

Percentage decrease in

Power Dissipation

Leakage

Power(W)

90nm

45nm

3.76E-09

2.13E-06

2.45E-09

1.65E-06

34.914

22.223

TABLE V. RESULTS FOR 4:1 MULTIPLEXER

AND FULL ADDER

4:1

Full

Multiplexer Adder

CONVENTIO

38.558

42.37

Leakage

NAL

Power(nW)

21.354

24.248

LECTOR

Percentage decrease in

44.618

42.771

Power Dissipation

Leakage power dissipation is taken as the

average of power dissipations obtained at all the

possible input vectors of the CMOS circuit. There are

4 possible combinations for 2-input NAND, hence the

average of the four power dissipations gives the

leakage power. In the case of 4-input AOI, power

dissipations corresponding to all the 16 combinations

are averaged. For Multiplexer, the average of 64

power dissipations is considered and for full adder,

the average of 8 power dissipations is considered to

be as the static power dissipated. In each case, the

leakage power is measured by exciting both the

circuits (Conventional and LECTOR) with same set

of input vectors.

[1]

P. Verma, R. A. Mishra, Leakage power and delay

analysis of LECTOR based CMOS circuits, Intl conf. on

computer & communication technology ICCCT 2011.

[2]

H. Narender and R. Nagarajan, LECTOR: A technique

for leakage reduction in CMOS circuits, IEEE trans. on

VLSI systems, vol. 12, no. 2, Feb. 2004.

[3]

L. Wei, Z. Chen, M. Johnson, and K. Roy, Design and

optmization of low voltage high performance dual

threshold CMOS circuits, in Proc. 35th DAC, 1998, pp.

489492.

[4]

John F. Wakerly, Digital Design- Principles and

Practices, fourth edition.

[5]

M. C. Johnson, D. Somasekhar, L. Y. Chiou, and K. Roy,

Leakage control with efficient use of transistor stacks in

single threshold CMOS, IEEE Trans. VLSI Syst., vol. 10,

pp. 15, Feb. 2002.

[6]

B. S. Deepaksubramanyan, A. Nunez, Analysis of

subthreshold leakage reduction in CMOS digital circuits,

in Proc. 13th NASA VLSI Symp.,June 2007.

[7]

Q. Wang and S. Vrudhula, Static power optimization of

deep sub-micron CMOS circuits for dual VT technology,

in Proc. ICCAD, Apr. 1998, pp. 490496.

[8]

M. D. Powell, S. H. Yang, B. Falsafi, K. Roy, and T. N.

Vijaykumar, Gated-Vdd: A ciruit technique to reduce

leakage in deep submicron cache memories, in Proc.

IEEE ISLPED, 2000, pp. 90-95.

[9]

S. H. Kim and V. J. Mooney, Sleepy Keeper: a new

approach to low-leakage power VLSI design, IFIP, pp.

367-372, 2006.

[10]

J. C. Park, Sleepy Stack: A new approach to Low Power

VLSI logic and memory, Ph.D. Dissertation, School of

Electrical and Computer Engineering, Georgia Institute of

Technology, 2005.

VI. CONCLUSION

The increase in leakage power because of the

scaling down of device dimensions, supply and

International Journal of Electronics Signals and Systems (IJESS) ISSN: 2231- 5969, Vol-2 Iss-1, 2012

77

You might also like

- A Literature Review On Leakage and Power Reduction Techniques in CMOS VLSI DesignDocument5 pagesA Literature Review On Leakage and Power Reduction Techniques in CMOS VLSI DesignEditor IJRITCC0% (1)

- deleeppaperDocument7 pagesdeleeppaperDEEPAK PRAJAPATINo ratings yet

- 05682957Document4 pages05682957Praveenkumar ViswanathanNo ratings yet

- Ijesrt: Leakage Current Reduction Techniques For CMOS CircuitsDocument4 pagesIjesrt: Leakage Current Reduction Techniques For CMOS CircuitsShailendra YadavNo ratings yet

- SurajpaperDocument79 pagesSurajpaperSooraj SattirajuNo ratings yet

- Static Power Reduction Techniques For Asynchronous Circuits: Carlos Ortega, Jonathan Tse, and Rajit ManoharDocument10 pagesStatic Power Reduction Techniques For Asynchronous Circuits: Carlos Ortega, Jonathan Tse, and Rajit ManoharK HoneeyNo ratings yet

- Digital CMOS Logic Operation in The Sub-Threshold Region: Hendrawan Soeleman and Kaushik RoyDocument6 pagesDigital CMOS Logic Operation in The Sub-Threshold Region: Hendrawan Soeleman and Kaushik Royphanindra21No ratings yet

- Analysis of Cmos and Mtcmos Circuits Using 250 Nano Meter TechnologyDocument11 pagesAnalysis of Cmos and Mtcmos Circuits Using 250 Nano Meter TechnologyCS & ITNo ratings yet

- Dual-Threshold Voltage Techniques For Low-Power Digital CircuitsDocument10 pagesDual-Threshold Voltage Techniques For Low-Power Digital CircuitsSeizalal SingsonNo ratings yet

- FORTRAN Based ApproachDocument22 pagesFORTRAN Based ApproachGS EKTANo ratings yet

- Ijaerv12n2 02Document6 pagesIjaerv12n2 02Hardik MakwanaNo ratings yet

- FISAC2 200907012 - PrajwalprabhuDocument22 pagesFISAC2 200907012 - PrajwalprabhuPrajwal PrabhuNo ratings yet

- Analysis and Optimization of Active Power and Delay of 10T Full Adder Using Power Gating Technique at 45 NM TechnologyDocument7 pagesAnalysis and Optimization of Active Power and Delay of 10T Full Adder Using Power Gating Technique at 45 NM TechnologyInternational Organization of Scientific Research (IOSR)No ratings yet

- Techniques For Low Power VLSI Design: A Novel Analysis of Leakage Power ReductionDocument4 pagesTechniques For Low Power VLSI Design: A Novel Analysis of Leakage Power ReductionSaranya RamaswamyNo ratings yet

- Design of Modified Low Power CMOS Differential Ring Oscillator Using Sleepy Transistor ConceptDocument19 pagesDesign of Modified Low Power CMOS Differential Ring Oscillator Using Sleepy Transistor ConceptPrajwal GowdaNo ratings yet

- A 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyDocument4 pagesA 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyMuhammad_Swilam_2010No ratings yet

- 279 E317 PDFDocument6 pages279 E317 PDFJubin JainNo ratings yet

- PFFDocument63 pagesPFFsai kiranNo ratings yet

- Power Optimization For Low Power VLSI CircuitsDocument4 pagesPower Optimization For Low Power VLSI CircuitsCHARANNo ratings yet

- Design of ALU Circuits Using Pass Transistor LogicDocument71 pagesDesign of ALU Circuits Using Pass Transistor LogicVivek GuntumuduguNo ratings yet

- Design & Analysis of Different Types of Sleepy Methods For Future TechnologiesDocument6 pagesDesign & Analysis of Different Types of Sleepy Methods For Future TechnologiesseventhsensegroupNo ratings yet

- Icacci 2014 6968238Document6 pagesIcacci 2014 6968238kesavanNo ratings yet

- A Survey On Leakage Power Reduction Techniques by Using Power Gating MethodologyDocument6 pagesA Survey On Leakage Power Reduction Techniques by Using Power Gating MethodologySasi Kiran SNo ratings yet

- LCPMOS TechniqueDocument72 pagesLCPMOS Techniqueadi_gopiNo ratings yet

- Different Sleep MethodsDocument6 pagesDifferent Sleep MethodsSanthoshReddyNo ratings yet

- Efficient Design of 1Document7 pagesEfficient Design of 1sumathiNo ratings yet

- 2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsDocument5 pages2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsKuldeep SinghNo ratings yet

- A Low-Power 8-Read 4-Write Register File DesignDocument4 pagesA Low-Power 8-Read 4-Write Register File DesignEdmund LeongNo ratings yet

- Dual-Output Voltage Reference Circuit Design for Low Power ApplicationsDocument4 pagesDual-Output Voltage Reference Circuit Design for Low Power Applicationsmd istiyakNo ratings yet

- Low-Power VLSI Design Using Dynamic-Threshold LogicDocument6 pagesLow-Power VLSI Design Using Dynamic-Threshold LogicravindarsinghNo ratings yet

- Dheeraj ReportDocument15 pagesDheeraj ReportGirdhar Gopal GautamNo ratings yet

- DC-DC Buck Converter With Reduced Impact: SciencedirectDocument8 pagesDC-DC Buck Converter With Reduced Impact: SciencedirectClaudiu UdrescuNo ratings yet

- Ponencia - Filter - BodyDriven Gonzalez CarvajalDocument4 pagesPonencia - Filter - BodyDriven Gonzalez CarvajalFernando JarixNo ratings yet

- CMOS Based 1-Bit Full Adder Cell For Low-Power Delay ProductDocument6 pagesCMOS Based 1-Bit Full Adder Cell For Low-Power Delay ProductnekuNo ratings yet

- VLSI Interconnect Survey Addressing High-Performance On-Chip TechniquesDocument6 pagesVLSI Interconnect Survey Addressing High-Performance On-Chip TechniquesMohamed YousufNo ratings yet

- Minimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueDocument7 pagesMinimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Design and Simulation of RF Energy Extracting CircuitsDocument28 pagesDesign and Simulation of RF Energy Extracting CircuitsHaresh SinghNo ratings yet

- Nanometer MOSFETDocument12 pagesNanometer MOSFETSibi ManojNo ratings yet

- (Analog) - MS2318 - Design Fundamentals of Implementing An Isolated Half-Bridge Gate DriverDocument4 pages(Analog) - MS2318 - Design Fundamentals of Implementing An Isolated Half-Bridge Gate DriverIgnacio VizzoNo ratings yet

- Design and Analysis of Multi-Threshold Cmos Full Adder Using 90nmDocument8 pagesDesign and Analysis of Multi-Threshold Cmos Full Adder Using 90nmSaravanakumar KalaimaniNo ratings yet

- k1 FCL DigSilentDocument8 pagesk1 FCL DigSilentksg9731No ratings yet

- Leakage Current PaperDocument23 pagesLeakage Current Paperkeshav rocksNo ratings yet

- IJEAS0203039Document6 pagesIJEAS0203039erpublicationNo ratings yet

- 1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002Document16 pages1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002jaigodaraNo ratings yet

- Design and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueDocument7 pagesDesign and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueGRD JournalsNo ratings yet

- Low Power VLSI Unit 2Document14 pagesLow Power VLSI Unit 2JAI ROYALNo ratings yet

- A BIST Scheme For Testing and Repair of Multi-Mode Power SwitchesDocument6 pagesA BIST Scheme For Testing and Repair of Multi-Mode Power SwitchesmohammedNo ratings yet

- Low Voltage Low Power Pipelined ADC For Video Applications: Hameed Zohaib Samad, Patri Sriharirao, K. SarangamDocument5 pagesLow Voltage Low Power Pipelined ADC For Video Applications: Hameed Zohaib Samad, Patri Sriharirao, K. SarangamGayathri SrinivasaNo ratings yet

- Abstract: Ultra-Low Power Phase Locked LoopsDocument4 pagesAbstract: Ultra-Low Power Phase Locked LoopsRizwan Shaik PeerlaNo ratings yet

- Lec14 DTMOSDocument88 pagesLec14 DTMOSSalim SanNo ratings yet

- 2728-Article Text-2331-1-10-20220728Document4 pages2728-Article Text-2331-1-10-20220728Madhu DatarNo ratings yet

- Designing Low-Power CMOS Devices for Minimum EnergyDocument10 pagesDesigning Low-Power CMOS Devices for Minimum EnergySanjay ChNo ratings yet

- VLSI Implementation Of High Speed Low Power Design Using Hybrid Power GatingDocument9 pagesVLSI Implementation Of High Speed Low Power Design Using Hybrid Power Gatingneelima422No ratings yet

- A Body Bias Technique For Low Power Full Adder UsiDocument7 pagesA Body Bias Technique For Low Power Full Adder UsieceaitsrajampetNo ratings yet

- Survey On Power Optimization Techniques For Low Power Vlsi Circuit in Deep Submicron TechnologyDocument15 pagesSurvey On Power Optimization Techniques For Low Power Vlsi Circuit in Deep Submicron TechnologyAnonymous e4UpOQEPNo ratings yet

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsFrom EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsNo ratings yet

- Introduction to Power System ProtectionFrom EverandIntroduction to Power System ProtectionRating: 5 out of 5 stars5/5 (1)

- Introduction-Khelo India Physical Fitness of School Going ChildrenDocument2 pagesIntroduction-Khelo India Physical Fitness of School Going ChildrenAkNo ratings yet

- Public Notice - Postponement of The UGC-NET EnglishDocument1 pagePublic Notice - Postponement of The UGC-NET EnglishAkNo ratings yet

- M SC - SyllabusDocument2 pagesM SC - Syllabusapi-3782519No ratings yet

- Syllabus OlympiadDocument1 pageSyllabus OlympiadAkNo ratings yet

- Viterbi Decoder For CodingDocument6 pagesViterbi Decoder For CodingAkNo ratings yet

- Key Dates - 2019-20 - 300519 PDFDocument6 pagesKey Dates - 2019-20 - 300519 PDFAkNo ratings yet

- PH.D Notification - 1979 - 1983Document52 pagesPH.D Notification - 1979 - 1983AkNo ratings yet

- M.A (Hons) English 5 Y. Int FWD To Acad BR On 24-10-2019Document131 pagesM.A (Hons) English 5 Y. Int FWD To Acad BR On 24-10-2019AkNo ratings yet

- Mphil PHD Urs English2018Document82 pagesMphil PHD Urs English2018AkNo ratings yet

- Domino Ckts Using Dual VTDocument4 pagesDomino Ckts Using Dual VTAkNo ratings yet

- Leakage Current Reduction in VLSI Systems: David Blaauw, Steve Martin, Krisztian Flautner, Trevor MudgeDocument13 pagesLeakage Current Reduction in VLSI Systems: David Blaauw, Steve Martin, Krisztian Flautner, Trevor MudgeAkNo ratings yet

- NVD 13. Design of Efficient Binary Comparators IEEE 2014TDocument11 pagesNVD 13. Design of Efficient Binary Comparators IEEE 2014Tamta1No ratings yet

- Leakage Reduction Using Self-Controlled Leakage TransistorsDocument6 pagesLeakage Reduction Using Self-Controlled Leakage TransistorsAkNo ratings yet

- QDCA For Reversible Logic GateDocument11 pagesQDCA For Reversible Logic Gateamta1No ratings yet

- NET EXAM Paper 1Document27 pagesNET EXAM Paper 1shahid ahmed laskar100% (4)

- Reversible NewDocument3 pagesReversible NewAkNo ratings yet

- Comparator Design Using Full AdderDocument4 pagesComparator Design Using Full AdderInternational Journal of Research in Engineering and TechnologyNo ratings yet

- Ep227 Digital ElectronicsDocument85 pagesEp227 Digital ElectronicsPECMURUGANNo ratings yet

- Sicard SlidesDocument21 pagesSicard SlidesAkNo ratings yet

- Basic ConceptDocument56 pagesBasic ConceptHarish KumarNo ratings yet

- Gonly (A79451700v02)Document1 pageGonly (A79451700v02)Thaw GyiNo ratings yet

- Electrical Equivalent Circuits of Outdoor Insulators Based On Leakage Current Waveforms and Computer SimulationDocument4 pagesElectrical Equivalent Circuits of Outdoor Insulators Based On Leakage Current Waveforms and Computer SimulationFari PratomosiwiNo ratings yet

- Industrial AutomationDocument28 pagesIndustrial Automation4happy12383% (6)

- Flyer SPS2S 245kV DT Breaker USDocument4 pagesFlyer SPS2S 245kV DT Breaker USJuan GaitanNo ratings yet

- MMG 1070/. TS: Eddy Current Displacement SensorDocument2 pagesMMG 1070/. TS: Eddy Current Displacement Sensorimant197812gmail.comNo ratings yet

- PANASONIC FAN - fv-x0vq3 - en - OmDocument8 pagesPANASONIC FAN - fv-x0vq3 - en - OmbbeisslerNo ratings yet

- Feedback and Control Systems: Rezel A. Sto. Tomas, Ece 1Document10 pagesFeedback and Control Systems: Rezel A. Sto. Tomas, Ece 1kujong agacerNo ratings yet

- ParlantesDocument8 pagesParlantesjopsueNo ratings yet

- Verifying Low Power DesignDocument31 pagesVerifying Low Power DesignmjabsNo ratings yet

- V4NCT7 Ar1Document4 pagesV4NCT7 Ar1Andrei DeyuNo ratings yet

- 1303 MBST DiagnosingPowerSeatsDocument5 pages1303 MBST DiagnosingPowerSeatsMarcioMartinhoFerreiraNo ratings yet

- RuleBook Full PDFDocument1,195 pagesRuleBook Full PDFrosostena100% (2)

- Physical Layer 3gpp 38.214Document99 pagesPhysical Layer 3gpp 38.214Saahil MathewsNo ratings yet

- STLD BitsDocument18 pagesSTLD BitsKornepati SureshNo ratings yet

- Manual RM30110 Enatelv1.2Document13 pagesManual RM30110 Enatelv1.2Ricardo100% (1)

- Capacitor PDFDocument21 pagesCapacitor PDFMøñəßh ßîñğh ŁøđhîNo ratings yet

- Parts Manual: Topkat Fuel Management SystemDocument20 pagesParts Manual: Topkat Fuel Management SystemsandyNo ratings yet

- NSN 2G 3G Parameter SettingDocument17 pagesNSN 2G 3G Parameter SettingDikal PebriandaNo ratings yet

- Acquisition System For Smart Home Using LabVIEWDocument5 pagesAcquisition System For Smart Home Using LabVIEWDinh Truong TamNo ratings yet

- Denon AVR-1910Document72 pagesDenon AVR-1910Konstantinos SpiropoulosNo ratings yet

- CM OLTC Operating Instruction-HM0.460.301-EN PDFDocument52 pagesCM OLTC Operating Instruction-HM0.460.301-EN PDFDeegii DeegiiNo ratings yet

- EXPLORER 727 Product Sheet LR PDFDocument2 pagesEXPLORER 727 Product Sheet LR PDFSayyid Zen ShihabNo ratings yet

- Mobile device component diagramDocument35 pagesMobile device component diagramStefanus NgodhuNo ratings yet

- Optical Fibre Diameter-Controlled Manufacturing System Using Cut-Off Feedback TechniqueDocument7 pagesOptical Fibre Diameter-Controlled Manufacturing System Using Cut-Off Feedback TechniquekalyanithallapalliNo ratings yet

- CPD7 - B1 Lecture Notes - 6 SCADA Components and Configuration PDFDocument89 pagesCPD7 - B1 Lecture Notes - 6 SCADA Components and Configuration PDFjjhenNo ratings yet

- BCH Price List W.e.f.05.07.2021Document124 pagesBCH Price List W.e.f.05.07.2021Vrijesh RathodNo ratings yet

- IBM 1312 Serivce Parts Manual PDFDocument244 pagesIBM 1312 Serivce Parts Manual PDFMaria Luz Martinez SanzNo ratings yet

- 26-003 Ventra ControlsDocument2 pages26-003 Ventra ControlsAhver ChaudharyNo ratings yet

- Mi CDocument1 pageMi CArjun SanthoshNo ratings yet