Professional Documents

Culture Documents

Electrónica Digital

Uploaded by

CentipedeWormOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electrónica Digital

Uploaded by

CentipedeWormCopyright:

Available Formats

ltima modificacin: 06-06-2013

220117 - Electrnica Digital

Unidad responsable:

220 - ETSEIAT - Escuela Tcnica Superior de Ingenieras Industrial y Aeronutica de Terrassa

Unidad que imparte:

710 - EEL - Departamento de Ingeniera Electrnica

Curso:

2013

Titulacin:

GRADO EN INGENIERA EN TECNOLOGAS INDUSTRIALES (Plan 2010). (Unidad docente

Obligatoria)

Crditos ECTS:

Idiomas docencia:

Cataln

Profesorado

Responsable:

ANTONIO CALOMARDE PALOMINO

Otros:

GABRIEL JOSE CAPELLA FRAU - DAVID GONZALEZ DIEZ - LEXA DIGNA NESCOLARDE SELVA

Capacidades previas

Es recomendable haber cursado la asignatura Electrnica.

Competencias de la titulacin a las que contribuye la asignatura

Especficas:

1. Conocimiento de los fundamentos y aplicaciones de la electrnica digital y microprocesadores.

Genricas:

2. USO SOLVENTE DE LOS RECURSOS DE INFORMACIN - Nivel 3: Planificar y utilizar la informacin necesaria para

un trabajo acadmico (por ejemplo, para el trabajo de fin de grado) a partir de una reflexin crtica sobre los recursos

de informacin utilizados.

Metodologas docentes

La asignatura se organiza en:

1.- Clases en grupos grandes: En estas clases se desarrollan los conceptos tericos, parte de las clases de problemas, y

las evaluaciones correspondientes al primer y segundo parcial y las pruebas de nivel. Se utilizar el modelo expositivo que

el profesor crea ms conveniente para asimilar los objetivos que se han fijado en la asignatura.

2.- Clases en grupos pequeos: En esta actividad se desarrollan las prcticas de laboratorio.

La plataforma ATENEA se utilizar como herramienta de soporte en los dos tipos de clases que se has descrito. Se

utilizar como transmisor y comunicador con los alumnos.

A) Profesor -> Estudiante/a:

1.- Programacin de actividades e informacin

2.- Material de aprendizaje

3.- Evaluaciones de las actividades

B) Estudiante/a -> Profesor

1.- Entrega de actividades

2.- Preguntas, comentarios i sugerencias respecto al desarrollo de la asignatura y su aprendizaje

C) Estudiante/a -> Estudiante/a

1.- Utilizacin del FORUM como a espacio de informacin y debate.

Objetivos de aprendizaje de la asignatura

1/6

Universitat Politcnica de Catalunya

ltima modificacin: 06-06-2013

220117 - Electrnica Digital

1.

2.

3.

4.

Comprensin y dominio de los conceptos bsicos sobre el anlisis y diseo de sistemas digitales.

Conocimiento de los lenguajes de descripcin hardware, y su aplicacin al diseo de sistemas digitales.

Conocimiento de la estructura de microprocesadores y microcontroladores.

Conocimiento y dominio del diseo de sistemas encastados (System on chip) y su aplicacin en sistemas reales.

Horas totales de dedicacin del estudiantado

Dedicacin total: 150h

Grupo grande/Teora:

46h

30.67%

Grupo pequeo/Laboratorio:

14h

9.33%

Aprendizaje autnomo:

90h

60.00%

2/6

Universitat Politcnica de Catalunya

ltima modificacin: 06-06-2013

220117 - Electrnica Digital

Contenidos

1.-Descripcin de un sistema digital. Del principio Dedicacin: 16h

al final

Clases tericas: 3h

Clases de laboratorio: 2h

Grupo grande/Teora: 3h

Grupo pequeo/Laboratorio: 2h

Aprendizaje autnomo: 6h

Descripcin:

1.1.- Una visin histrica. De donde venimos y donde vamos.

1.2.- Niveles de descripcin.

1.3.- El arte de tratar con complejidad.

1.4.- Sistemas de numeracin.

1.5.- Puertas lgicas.

1.6.- Niveles lgicos.

1.7.- El transistor CMOS.

1.8.- Consumo energtico.

Actividades vinculadas:

Clases de teora, problemas y prcticas de laboratorio.

Prueba individual de conocimientos previos relacionados con el lgebra de Boole (no evaluable). Prctica de

Laboratorio: Introduccin a la utilizacin de sistemas de diseo digital. Proceso de diseo completo.

2.-Diseo con lgica combinacional

Dedicacin: 19h

Grupo grande/Teora: 5h

Grupo pequeo/Laboratorio: 2h

Aprendizaje autnomo: 12h

Descripcin:

2.1.- Introduccin.

2.2.- Ecuaciones booleanas.

2.3.- lgebra de Boole.

2.4.- De la lgica a las puertas.

2.5.- Lgica combinacional multinivel.

2.6.- Alta impedancia i X's

2.7.- Mapas de Karnaugh.

2.8.- Bloques combinacionales.

2.9.- Temporizacin

Actividades vinculadas:

Clases de teora, problemas y prcticas de laboratorio.

Prctica de Laboratorio: Diseo de un sistema digital combinacional. Sumador.

3/6

Universitat Politcnica de Catalunya

ltima modificacin: 06-06-2013

220117 - Electrnica Digital

3.-Diseo de lgica secuencial

Dedicacin: 23h

Grupo grande/Teora: 6h

Grupo pequeo/Laboratorio: 2h

Aprendizaje autnomo: 15h

Descripcin:

3.1.- Introduccin

3.2.- Elementos de memoria: Latches i Flip-Flops

3.3.- Diseo de sistemas sncronos.

3.4.- Maquines de estado finito.

3.5.- Temporizacin en lgica secuencial

3.6.- Paralelismo

Actividades vinculadas:

Clases de teora, problemas y prcticas de laboratorio.

Prctica de laboratorio: Diseo de un sistema secuencial: cronmetro

4.-Lenguajes de descripcin hardware

Dedicacin: 31h

Grupo grande/Teora: 9h

Grupo pequeo/Laboratorio: 2h

Aprendizaje autnomo: 20h

Descripcin:

4.1.- Introduccin

4.2.- Lgica combinacional

4.3.- Descripcin estructural.

4.4.- Lgica secuencial.

4.5.- Ms lgica combinacional

4.6.- Mquinas de estado finito.

4.7.- Mdulos parametrizados

4.8.- Testbenches

Actividades vinculadas:

Clases de teora, problemas y prcticas de laboratorio.

Prctica de laboratorio: Diseo de un circuito complejo.

Examen 1er parcial. Contenidos 1, 2, 3 i 4.

4/6

Universitat Politcnica de Catalunya

ltima modificacin: 06-06-2013

220117 - Electrnica Digital

5.-Arquitectura

Dedicacin: 54h

Clases de laboratorio: 19h

Grupo grande/Teora: 12h

Grupo pequeo/Laboratorio: 4h

Aprendizaje autnomo: 19h

Descripcin:

5.1.- Introduccin

5.2.- Lenguaje ensamblador.

5.3.- Lenguaje mquina

5.4.- Programacin

5.5.- Modos de direccionamiento

5.6.- Luz, cmara y accin: Compilado, ensamblando y cargando

Actividades vinculadas:

Clases de teora, problemas y prcticas de laboratorio.

6.-Microarquitectura

Dedicacin: 31h

Grupo grande/Teora: 11h

Grupo pequeo/Laboratorio: 2h

Aprendizaje autnomo: 18h

Descripcin:

6.1.- Introduccin

6.2.- Anlisis del rendimiento.

6.3.- Procesador de un solo cicle.

6.4.- Procesador multiciclo.

6.5.- Procesador pipeline

6.6.- Representacin HDL.

6.7.- Micro arquitecturas avanzadas.

6.8.- Perspectiva del mundo real: Micro arquitectura ARM

Actividades vinculadas:

Clases de teora, problemas y prcticas de laboratorio.

Sistema de calificacin

- Examen 1er Parcial N1P peso : 35%

- Examen 2o Parcial N2P peso : 35%

-Actividades en ATENEA

peso :

10%

- Practicas de Laboratori

peso : 20%

Todos los que no puedan realizar el examen parcial, o que lo suspendan, tendrn la opcin de recuperarlo

posteriormente.

5/6

Universitat Politcnica de Catalunya

ltima modificacin: 06-06-2013

220117 - Electrnica Digital

Bibliografa

Bsica:

Money Harris, D.; Harris, Sarah L. Digital design and computer architecture. 2nd ed. Amsterdam: Elsevier, 2013. ISBN

9780123944245.

Patterson, David A.; Hennessy, John L. Computer organization and design: the hardware/software interface. 4th ed.

Burlington: Morgan Kaufmann, 2011. ISBN 9780123747501.

Complementaria:

Sloss, A.N.; Symes, D.; Wright, C. ARM system developer's guide: designing and optimizing system software [en lnea]. San

Francisco: Morgan Kaufmann, 2004 [Consulta: 23/05/2013]. Disponible a:

<http://www.sciencedirect.com/science/book/9781558608740>. ISBN 9781558608740.

6/6

Universitat Politcnica de Catalunya

You might also like

- Motivacion Tema 4Document9 pagesMotivacion Tema 4Miriam MartaNo ratings yet

- 7MOTIVACIONDocument7 pages7MOTIVACIONmeriaalexandraNo ratings yet

- Manual Illustrator 10Document479 pagesManual Illustrator 10api-3774955100% (3)

- Motivacion Tema 6Document6 pagesMotivacion Tema 6petinto14No ratings yet

- TEMA3MOTIVACIONDocument10 pagesTEMA3MOTIVACIONElena FNNo ratings yet

- 1MOTIVACIONDocument13 pages1MOTIVACIONUrtzi Arrieta PuñalNo ratings yet

- Psicologia de La Motivacion PDFDocument11 pagesPsicologia de La Motivacion PDFPablo Orellana GuachallaNo ratings yet

- Motivación Tema 2Document7 pagesMotivación Tema 2diananavalNo ratings yet

- Simulacion de Un Proceso Industrial Mediante FlexSimDocument26 pagesSimulacion de Un Proceso Industrial Mediante FlexSimDavid Russo VillarrealNo ratings yet

- File PDFDocument2 pagesFile PDFSTJNo ratings yet

- Que Es AMFEDocument24 pagesQue Es AMFECentipedeWormNo ratings yet

- Mejora Continua de ProcesosDocument49 pagesMejora Continua de ProcesosGabriel DiduNo ratings yet

- Problema Asignacion Investigacion OperacionesDocument10 pagesProblema Asignacion Investigacion OperacionesCentipedeWormNo ratings yet

- Motivacion Tema 4Document6 pagesMotivacion Tema 4petinto14No ratings yet

- Estrategia Oceanos AzulesDocument21 pagesEstrategia Oceanos AzulesCentipedeWormNo ratings yet

- Ejercicios Sketcher PDFDocument2 pagesEjercicios Sketcher PDFCentipedeWormNo ratings yet

- File PDFDocument2 pagesFile PDFCentipedeWormNo ratings yet

- C 1. Conceptos Fundamentales. Teoría de Circuitos: 1.1 Sistemas ElectrónicosDocument21 pagesC 1. Conceptos Fundamentales. Teoría de Circuitos: 1.1 Sistemas ElectrónicosbillymuedasNo ratings yet

- Ejercicios SketcherDocument2 pagesEjercicios SketcherCentipedeWormNo ratings yet

- Problemas Tema 05 01Document2 pagesProblemas Tema 05 01CentipedeWormNo ratings yet

- Tema5 - Diodos para Aplicaciones Especiales PDFDocument32 pagesTema5 - Diodos para Aplicaciones Especiales PDFCentipedeWormNo ratings yet

- FatigaDocument22 pagesFatigaRafael Amaro Palacios SantibañezNo ratings yet

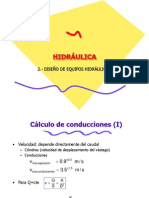

- Hidráulica: 2.-Diseño de Equipos HidráulicosDocument8 pagesHidráulica: 2.-Diseño de Equipos HidráulicosHenry PabonNo ratings yet

- Fracciones Parciales PDFDocument5 pagesFracciones Parciales PDFLuis SegoviaNo ratings yet

- TR Tema 01 Resumen PDFDocument1 pageTR Tema 01 Resumen PDFCentipedeWormNo ratings yet

- Hidraulica - Tema1 Fundamentos Hidraulicos, Dinamica (III)Document10 pagesHidraulica - Tema1 Fundamentos Hidraulicos, Dinamica (III)omar6catNo ratings yet

- Tema8 - Polarización y Estabilización Del Transistor Bipolar PDFDocument30 pagesTema8 - Polarización y Estabilización Del Transistor Bipolar PDFCentipedeWormNo ratings yet

- Tema7 - Fundamentos de Los Transistores Bipolares PDFDocument29 pagesTema7 - Fundamentos de Los Transistores Bipolares PDFCentipedeWormNo ratings yet

- Hidráulica: 2.-Diseño de Equipos HidráulicosDocument8 pagesHidráulica: 2.-Diseño de Equipos HidráulicosHenry PabonNo ratings yet

- Teoria de CircuitosDocument155 pagesTeoria de CircuitosFacundo TerneroNo ratings yet

- GramáticaDocument1 pageGramáticaNicolasNo ratings yet

- Etica y Manejo de Conflictos 1Document3 pagesEtica y Manejo de Conflictos 1Maryory Alayo MontenegroNo ratings yet

- 9 FRAGOSO RevistaChilenaSemiotica 7-3Document17 pages9 FRAGOSO RevistaChilenaSemiotica 7-3Carmen HernándezNo ratings yet

- Mehan, H. Un Estudio de Caso en La Política de La RepresentaciónDocument26 pagesMehan, H. Un Estudio de Caso en La Política de La RepresentaciónandresNo ratings yet

- Marcadores Textuales PDFDocument1 pageMarcadores Textuales PDFVictor JRNo ratings yet

- Examen de suficiencia para estudiantes del Colegio Parroquial San Juan Bautista de la SalleDocument9 pagesExamen de suficiencia para estudiantes del Colegio Parroquial San Juan Bautista de la SalleMari T GuzmánNo ratings yet

- Teorias PsicológicasDocument45 pagesTeorias PsicológicasJasmin Rua encinaNo ratings yet

- Evolución lingüística y fonética históricaDocument11 pagesEvolución lingüística y fonética históricaGarcilaso del SilNo ratings yet

- Resumen Capitulo 9 Desarrollo Humano PapaliaDocument7 pagesResumen Capitulo 9 Desarrollo Humano PapaliaMateo Solarte ArdilaNo ratings yet

- Desintegracion FamiliarDocument15 pagesDesintegracion FamiliarChris ChrisNo ratings yet

- Organizamos la fiesta de bienvenidaDocument8 pagesOrganizamos la fiesta de bienvenidaKati Rojas NietoNo ratings yet

- Formas eficaces para construir la realidad antes de un examen con menos deDocument1 pageFormas eficaces para construir la realidad antes de un examen con menos deMildred AnaconaNo ratings yet

- 6 Ficha Del ColaboradorDocument8 pages6 Ficha Del ColaboradorLuis E ChNo ratings yet

- Clima Organizacional 2021Document27 pagesClima Organizacional 2021GregoryNo ratings yet

- Concepto y DefinicionDocument3 pagesConcepto y DefinicionJoseth CaizaNo ratings yet

- Seminario y Metodologia de InvestigacionDocument19 pagesSeminario y Metodologia de InvestigacionVirginia MedinaNo ratings yet

- Fef-N-04-Ve-22 - Plan Analitico Cii 2021Document10 pagesFef-N-04-Ve-22 - Plan Analitico Cii 2021Sebastián ProañoNo ratings yet

- Argumentación Oral y Escrita, Modulo de Oralidad.Document17 pagesArgumentación Oral y Escrita, Modulo de Oralidad.Lina CeballosNo ratings yet

- Preguntas Psi. CognitivaDocument2 pagesPreguntas Psi. CognitivaGraba CionesNo ratings yet

- PROYECTO ENERO 5A HUMANO Y COMUNITARIO La Feria de Los SentimientosDocument15 pagesPROYECTO ENERO 5A HUMANO Y COMUNITARIO La Feria de Los SentimientosAMON RANo ratings yet

- Prueba de EpistemologíaDocument31 pagesPrueba de EpistemologíabrighittNo ratings yet

- El Aprestamiento y Su ImportanciaDocument7 pagesEl Aprestamiento y Su ImportanciakarolNo ratings yet

- Habilidades SocialesDocument9 pagesHabilidades SocialesDani JcNo ratings yet

- Teoria de La Comunicacion Humana PatologiasDocument3 pagesTeoria de La Comunicacion Humana PatologiasMilagro Martinez LibernalNo ratings yet

- El Poder Esta Dentro de Ti - Louise L. Hay L®Document200 pagesEl Poder Esta Dentro de Ti - Louise L. Hay L®LISBETH CAROLINA PENA ASCANIO100% (7)

- Modelos de PersonalidadDocument4 pagesModelos de PersonalidadLeonardo CortesNo ratings yet

- Diplomado en Salud y HumanizacionDocument7 pagesDiplomado en Salud y HumanizacionLuis Castro MilanoNo ratings yet

- Semana IIIDocument29 pagesSemana IIIFERNANDEZ MONTES STEFANY NATHALINo ratings yet

- TORRETTI - La Geometría en El Pensamiento de KantDocument52 pagesTORRETTI - La Geometría en El Pensamiento de KantJuan Sánchez ZermeñoNo ratings yet

- Psicologia Educativa2 Tarea4Document4 pagesPsicologia Educativa2 Tarea4Gianely Stephanie GomezNo ratings yet