Professional Documents

Culture Documents

Practica 3

Uploaded by

Joan JoseCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Practica 3

Uploaded by

Joan JoseCopyright:

Available Formats

UNIVERSIDAD NACIONAL DE COLOMBIA - SEDE MANIZALES

SUMADOR COMPLETO DE DOS BITS

Docente: Jaime Enrique Arango

Monitor: Jose Miguel Hernandez

Cristian Marcelo Rosero Chingal Cod: 213077

Joan Jose Henriquez Parra Cod: 810562

Gandhy Gabriel Saldana Benavides Cod: 812059

01 de Octubre de 2014

ResumenThis lab implements a one-bit binary adder,using the information given in the guide. Also should

design a two-bit binary adder, four inputs, two outputs and

a carry. These two adders are implemented using only AND

and OR gates with two inputs, and NOT gates.

Index TermsMapas de Karnaugh, Compuertas Logicas,

Sumador Binario, Tabla de Verdad, Acarreo

I.

O BTJETIVOS

Identificar las diferentes fases del proceso general

de diseno e complementacion de un circuito logico

combinacional.

Conocer el funcionamiento de un sumador binario,de

tal forma que se implemente uno de un bit y otro de

dos bits.

Reconocer las diferentes formas de implementar un

sumador binario y con base a este conocimiento

ser capaz de plantear la implementacion de otros

circuitos logicos afines.

Aplicar el metodo de mapa de Karnaugh para la

simplificacion de expresiones booleanas.

II.

I NTRODUCCI ON

Lo que se explicara en este informe es el proceso

mediante el cual fue hecho el analisis de un sumador

binario de dos bits, ademas de como se realizo su diseno,

tambien hablaremos sobre conceptos relacionados con el

desarrollo de este tipo de dispositivos

III.

III-A.

M ARCO TE ORICO

Sumador Binario

En electronica un sumador es un circuito logico que

calcula la operacion suma. En los computadores modernos

se encuentra en lo que se denomina Unidad aritmetico

logica (ALU). Generalmente realizan las operaciones

aritmeticas en codigo binario decimal o BCD exceso

3, por regla general los sumadores emplean el sistema

binario. En los casos en los que se este empleando un

complemento a dos para representar numeros negativos

el sumador se convertira en un sumador-restador (Addersubtracter).

III-B.

sumador Completo

Un sumador completo es un circuito combinacional que

formar la suma aritmetica de tres bits de entrada. Consta

de tres entradas y dos salidas. Dos de las variables de

entrada, que se indican por x y y, representan los dos

bits significativo que van a anadirse. La tercera entrada,

z, representa la cuenta que se lleva de la posicion previa

significativa mas baja. Son necesarias dos salidas debido

a que la suma aritmetica de tres dgitos binarios vara en

valor de 0 a 3 y el 2 o 3 binarios requieren 2 dgito. Las

dos salidas se denotan por los smbolos S para la suma y

C para la cuenta que se lleva. La variable S da el valor

del bit menos significativo de la suma. La variable binaria

C da la cuenta que se lleva de salida.

IV.

PROCEDIMIENTO

La primera parte de la practica consiste en realizar el

montaje de un sumador binario de un bit, cuya tabla de

verdad es proporcionados por la gua (Tabla 1).

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

Cin

0

1

0

1

0

1

0

1

S

0

1

1

0

1

0

0

1

Cout

0

0

0

1

0

1

1

1

Tabla 1. Suma de dos cantidades de un bit.

Una ves generada la tabla de verdad, se procede a sacar

las funciones de cada una de las salidas y a expresarlas

en minterminos, las cuales se simplifican con el metodo

de mapa de Karnaugh.

P

S=

mo (1, 2, 4, 7)

f = (x0 y 0 Cin) + (x0 y Cin0 ) + (x y 0 Cin0 ) + (x y Cin)

S = xy 0 Cin0 + x0 yCin + xyCin + x0 y 0 Cin

S = Cin0 (xy 0 + x0 y) + Cin(AB + x0 y 0 )

S = Cin0 (xy 0 + x0 y) + Cin(x0 x + x0 y 0 + xy + yy 0 )

S = Cin0 (xy 0 + x0 y) + Cin((x0 + y)(x + y 0 ))

S = Cin0 (xy 0 xy) + Cin((xy 0 )0 (x0 y)0 )

S = Cin0 (xy 0 + x0 y) + Cin(xy 0 + x0 y)0

S = (x y) Cin

UNIVERSIDAD NACIONAL DE COLOMBIA - SEDE MANIZALES

Para esto se podra utilizar la dos sumadores de completo

de un bit en cascada para formar un sumador completo

de dos bits como se muestra en la Figura 4, Segun lo

especifica la gua de laboratorio.

Figura 1. Mapa de Karnaugh - Salida S.

Figura 4. Estructura de un Sumador completo de dos bits.

C=

mo (3, 5, 6, 7)

f = (y Cin) + (x Cin) + (xy)

De acuerdo a la configuracion mencionada anteriormente el esquematico de un sumador completo de dos bits

quedara de la siguiente forma (Figura 5).

Figura 2. Mapa de Karnaugh - Salida C.

Este sumador tiene dos entradas, cada una de un bit para

las cantidades que se suman y dos salidas de un bit cada

una para representar la suma y el acarreo(Figura 3).

Figura 5. Esquematico Sumador completo de dos bits en cascada.

Se observa que queda en una configuracion de cascada,

donde hay 5 entradas y tres salidas.

El sumador completo de dos bits mencionado en la

figura 4, se puede simplificar de una forma en la que se

puede ahorrar costo en el diseno. Para esto se volvio a

realizar y a disenar la tabla de verdad teniendo el cuente

el numero de combinaciones(entradas).

Nc = 2n

Nc = 24 = 16

La nueva tabla de verdad va a tener 4 entradas, con 16

combinaciones y tres salidas.

Figura 3. Esquematico Sumador Completo de un bit.

Luego de haber realizado el analisis del diseno, la

implementacion en el simulador ISIS de Proteus y la

verificacion del funcionamiento de este primer circuito.

La segunda parte consiste en realizar el diseno y la

implementacion de un sumador binario completo de dos

bits (cuatro bits de entrada que representan dos sumando

de dos bits cada uno y tres bits de salida, dos para la

suma y uno para el acarreo.

Se procede con la construccion de la tabla de

verdad, de esta tabla se obtienen las expansiones en

minterminos.Como se menciono anteriormente la tabla

de verdad va tener cuatro entradas ( A,B,C,D) y tres

salidas (Cout, S1, S2); donde C = Cin1 y D = Cin2, pero

para metodos de simplificacion lo vamos a mencionar

como C y D. A continuacion se podra observar la tabla

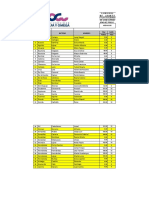

de verdad de un sumador completo de dos bits (Tabla 2).

Una ves generada la tabla de verdad, se procede a

sacar las funciones de cada una de las salidas y a

expresarlas en minterminos, las cuales se simplifican con

el metodo de mapa de Karnaugh.

UNIVERSIDAD NACIONAL DE COLOMBIA - SEDE MANIZALES

Funcion Simplificada de S1

S1 = B 0 (A C) + B(A D C)

Teniendo en forma simplificada la Salida S1 mediante el

mapa de Karnaugh , se realiza la primera parte del circuito

esquematico(Figura. 8).

Figura 8. Circuito Esquematico - Salida S1.

Figura 6. Tabla de verdad - Sumador completo de dos bits.

Salida S2

Salida S1

F = (A, B, C, D)

F = (A, B, C, D)

F =

P

m(1, 3, 4, 6, 9, 11, 12, 14, )

m(2, 3, 5, 6, 8, 9, 12, 15)

0

F = A B CD + A B CD + A BC D + A BCD +

AB 0 C 0 D0 + AB 0 C 0 D + ABC 0 D0 + ABCD

F = A0 B 0 C 0 D + A0 B 0 CD + A0 BC 0 D + A0 BCD0 +

AB 0 C 0 D + AB 0 CD + ABC 0 D0 + ABCD0

Con la Funcion de salida de S1 en terminos de las bases

canonicas se realiza el mapa de Karnaugh.(Figura. 7)

Con la Funcion de salida de S2 en terminos de las bases

canonicas se realiza el mapa de Karnaugh.(Figura. 9)

Figura 7. Mapa de Karnaugh - Salida S1.

Figura 9. Mapa de Karnaugh - Salida S2.

Funcion de Salida segun el mapa de Karnaugh de S1.

S1 = A0 B 0 C + AB 0 C 0 + A0 BC 0 D+

A0 BCD0 + ABC 0 D0 + ABCD

Funcion de Salida segun el mapa de Karnaugh de S2.

S2 = BD0 + B 0 D

Simplificacion con XOR tenemos :

Simplificacion con XOR tenemos :

S1 = B 0 (A C) + A0 B(C D) + AB(C D)

S2 = B D

Teniendo en forma simplificada la Salida S2 mediante

el mapa de Karnaugh , se realiza la primera parte del

esquematico(Figura. 10).

UNIVERSIDAD NACIONAL DE COLOMBIA - SEDE MANIZALES

el esquematico completo en el simulador ISIS de Proteus

(figura 13).

Figura 10. Circuito Esquematico - Salida S2.

Salida Cout

F = (A, B, C, D)

F =

m(7, 10, 11, 13,14, 15)

F = A0 BCD + AB 0 CD0 + AB 0 CD

+ABC 0 D + ABCD0 + ABCD

Con la Funcion de salida de S2 en terminos de las bases

canonicas se realiza el mapa de Karnaugh.(Figura. 11)

Figura 13. Circuito Esquematico - Sumador completo de dos bits..

Por ultimo se realiza el montaje del sumador completo de

dos bits. Todos los montajes de este laboratorio utilizan

u nicamente los CIs de referencia 74LS04 (compuertas

NOT), 74LS08 (compuertas AND), 74LS32 (compuertas

OR) y 74LS86 (compuerta XOR) un dip switch para el

control de las entradas y LEDs a la salida para la visualizacion de los bits de los resultados de las operaciones.

V.

C UESTIONARIO

1. Que es el codigo GRAY y para que se utiliza?

Figura 11. Mapa de Karnaugh - Salida Cout.

Funcion de Salida segun el mapa de Karnaugh de Cout.

Cout = AC + BCD + ABD

Teniendo en forma simplificada la Salida S1 mediante

el mapa de Karnaugh , se realiza la primera parte del

esquematico(Figura. 12).

El codigo GRAY es un sistema de numeracion

binario construido a partir del codigo binario

convencional en el que cambia un solo bit a la

vez en cada transicion. En la actualidad, el codigo

Gray se emplea como parte del algoritmo de diseno

de los mapas de Karnaugh, los cuales son, a su

vez, utilizados como herramienta de diseno. en

la implementacion de circuitos combinacionales

y circuitos secuenciales. La vigencia del codigo

Gray se debe a que un diseno digital eficiente

requerira transiciones mas simples y rapidas entre

estados logicos (0 o 1).

2. Basandose en el conocimiento del sumador

explique que detalladamente lo necesario para

disenar un restador completo?.

Figura 12. Circuito Esquematico - Salida Cout.

Teniendo todas las ecuaciones de las tres salidas , se realiza

Para disenar un restador binario completo de

n bits, primero se debe disenar un restador binario

completo de un bit. Un restador binario completo

de un bit, tiene en las entradas un bit para el

minuendo(x), un bit para el sustraendo (y) y un bit

para el prestamo inicial (Po). A la salida tiene un

bit para la diferencia(R) y un bit para el prestamo

que se realizo (P). Se construye la tabla de verdad

(Figura 13). De la tabla de verdad se encuentra

la expansion en minterminos y posteriormente se

UNIVERSIDAD NACIONAL DE COLOMBIA - SEDE MANIZALES

simplifica algebraica-mente o usando mapas de

karnaugh. Esta simplificacion se implemente y

tenemos el restador binario completo de un bit. Si

necesitamos de N bits, concatenamos n sumadores

binarios completos de un bit. La concatenacion

se realiza a traves de los terminales de prestamos

inicial (Po) y prestamo que se realizo (P)

VI.

C ONCLUSIONES

El proceso general para disenar esta clase de

circuitos logicos consiste en primero determinar las

entradas y salidas del circuito, con esta informacion

generar una tabla de verdad, de la tabla obtener

la expansion en minterminos o maxterminos, esta

expansion se simplifica algebraica-mente o usando

el metodo de mapa de Karnaugh, y finalmente la

expresion booleana resultante se representa con un

diagrama esquematico.

Los circuitos logicos implementados en este

laboratorio, por razones de estudio, se hicieron con

compuertas NOT, AND ,OR y XOR. Con estas

compuerta los circuitos que implementamos en la

practica se pueden simplificar de una manera que

puede reducirse en tamano y costo.

El sumador binario completo de n bits se basa en el

sumador binario completo de 1 bit, donde el Cout

del primer sumador se conecta al Cin del segundo

contador en forma de cascada. De esta forma se

puede formar un sumador de n bits con n conexiones

en cascada.

R EFERENCIAS

[1] http://www.monografias.com/trabajos14/algebra-booleana/algebrabooleana.shtml

[2] http://www.virtual.unal.edu.co/cursos/ingenieria/2000477/lecciones/020102.htm

[3] http://ocw.uv.es/ciencias/1-4/clase54edit.pdf

[4] http://slideplayer.es/slide/167960/

You might also like

- La Isla Del CorderoDocument1 pageLa Isla Del CorderoFrancis Guzman100% (1)

- Reglas de OrtografíaDocument4 pagesReglas de OrtografíaaasdasdNo ratings yet

- Apoc 4Document48 pagesApoc 4Yadira Albelo100% (1)

- Amplificadores: Sistemas de Ecuaciones DiferencialesDocument10 pagesAmplificadores: Sistemas de Ecuaciones DiferencialesJoan JoseNo ratings yet

- Revision de Los Papeles de TrabajoDocument13 pagesRevision de Los Papeles de TrabajoNoemi Rosas50% (2)

- De Los Jeroglíficos Al AlfabetoDocument4 pagesDe Los Jeroglíficos Al AlfabetoMartín LexequíasNo ratings yet

- Anexo 1Document3 pagesAnexo 1Joan JoseNo ratings yet

- Camos EDocument8 pagesCamos EJoan JoseNo ratings yet

- Diseño e Implementación de Un Amplificador Clase DDocument83 pagesDiseño e Implementación de Un Amplificador Clase DNelson RamosNo ratings yet

- Manual Cargue Oficial Archivos Sistema RVCC - Vers 2.0Document11 pagesManual Cargue Oficial Archivos Sistema RVCC - Vers 2.0Joan JoseNo ratings yet

- Sumador de 2 BitsDocument4 pagesSumador de 2 BitsJoan Jose100% (1)

- Lineas de Fuerza y Superficies EquipotencialesDocument15 pagesLineas de Fuerza y Superficies EquipotencialesJoan JoseNo ratings yet

- Trabajo6 NataliaLeyton BrandDocument9 pagesTrabajo6 NataliaLeyton Brandnatalia fabiola leyton tapia100% (1)

- Analisis CombinatorioDocument10 pagesAnalisis CombinatorioAlex Raúl Hidalgo Vega0% (1)

- Contestación A Unas PreguntasDocument109 pagesContestación A Unas Preguntasantoniosantana6No ratings yet

- Derechos Humanos y LiberalismoDocument13 pagesDerechos Humanos y LiberalismoCassandra UribeNo ratings yet

- Autoevaluacion 1 ErparcialDocument4 pagesAutoevaluacion 1 ErparcialGabriela BernedoNo ratings yet

- Organismos Internacionales A Los Que Pertenece VenezuelaDocument5 pagesOrganismos Internacionales A Los Que Pertenece VenezuelaM̦̻̙i͓͙̝t̡͎̺c͔͜h͙̫͎e̻̘͕l͍̝͇l̡͚͉ S͛aͣlaͣzaͣrͬ100% (1)

- 1 Marco TeóricoDocument20 pages1 Marco TeóricoGabriel AvilaNo ratings yet

- Discov Geometry GlossaryinspanishDocument28 pagesDiscov Geometry GlossaryinspanishjordybeltNo ratings yet

- Proyecto Investigación de MercadosDocument40 pagesProyecto Investigación de MercadosMaria Fernanda Cortez100% (2)

- Cdi - U2 - A2 - XxyzDocument7 pagesCdi - U2 - A2 - XxyzKragorGulNo ratings yet

- La Teoría de AtribuciónDocument5 pagesLa Teoría de AtribuciónZFI aduanasNo ratings yet

- Actividad 1 Ensayo Concepto ArchivoDocument8 pagesActividad 1 Ensayo Concepto ArchivoNELLYNo ratings yet

- Tesis Analisis de La Voz Narrativa Gerard GenetteDocument10 pagesTesis Analisis de La Voz Narrativa Gerard Genettevhriverosr2013No ratings yet

- Europa de Entreguerras (1919 - 1945) .Document5 pagesEuropa de Entreguerras (1919 - 1945) .lole_sin_nombreNo ratings yet

- Manual de DepartamentosDocument10 pagesManual de DepartamentosFernandoMagallanesGonzalezNo ratings yet

- Fusion y Refinado de MetalesDocument27 pagesFusion y Refinado de MetalesWilfredoNo ratings yet

- Ensayo JepDocument4 pagesEnsayo JepAmadeus MüllerNo ratings yet

- CV Competencias Laborales OCDocument33 pagesCV Competencias Laborales OCGerardo Javier ContrerasNo ratings yet

- Skidmore T. - Historia Contemporánea de America Latina Cap 2Document13 pagesSkidmore T. - Historia Contemporánea de America Latina Cap 2javiercinta_197037150% (1)

- Lectura La PuyaDocument4 pagesLectura La PuyaAna María Vilchez AlarcónNo ratings yet

- Como Leer Los EvangeliosDocument4 pagesComo Leer Los EvangeliosSalvador GermanNo ratings yet

- 2 Comercio InternacionalDocument4 pages2 Comercio InternacionalLupe GömezNo ratings yet

- Biodisel Por AceiteDocument111 pagesBiodisel Por AceiteLuis Leonardo Llanos EscobarNo ratings yet

- Farabeuf: Escritura Barroca y Novela Mexicana: Margo GlantzDocument10 pagesFarabeuf: Escritura Barroca y Novela Mexicana: Margo GlantzGamaliel Pineda CervantesNo ratings yet

- Caso Clinico NuriaDocument13 pagesCaso Clinico NuriaÉllica StoccoNo ratings yet