Professional Documents

Culture Documents

Implementacion de Una ALU en Verilog Sobre FPGA Spartan3E

Uploaded by

andresteve07Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Implementacion de Una ALU en Verilog Sobre FPGA Spartan3E

Uploaded by

andresteve07Copyright:

Available Formats

Trabajo Pactico

Nro. 1

de una ALU en verilog sobre FPGA Spartan3E

Implementacion

Morales Esteban, Salamandri Santiago, Uboldi Marino

FCEFyN, UNC, Argentina

ABSTRACT

Cargador: Modulo

encargado de inicializar los valores de los registros.

En computacion,

la unidad aritmetico

logica,

tambien

de arithmetic loconocida como ALU (siglas en ingles

gic unit), es un circuito digital que calcula operaciones

etc.) y opearitmeticas

(como suma, resta, multiplicacion,

raciones logicas

(si, y, o, no), entre dos numeros.

ALU: Modulo

encargado de realizar las operaciones

tabuladas en los requerimientos.

DESCRIPCION

CARGADOR

cargador(entrada,boton_a,boton_b,

boton_op,a,b,op);

CONSIGNA IMPLEMENTADA

Implementar una ALU sobre FPGA.

Utilizar las placas de desarrollo Basys II.

La ALU debe ser parametrizable (bus de datos) para

poder ser utilizada posteriormente en el trabajo final.

Validar el desarrollo por medio de Test Bench.

La ALU debera realizar las siguientes operaciones:

Operacion

ADD

SUB

AND

OR

XOR

SRA

SRL

NOR

Codigo

100000

100010

100100

100101

100110

000011

000010

100111

Entradas

entrada: Es el registro de entrada de ancho de bus

parametrizable.

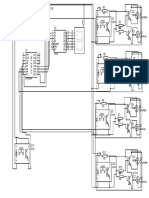

DESARROLLO

boton a: Cuando esta entrada esta en 1 carga el

valor de la entrada en la salida a;

Se implementa una ALU de 8 bits (bus de datos parame

trizable) en FPGA, la cual se divide en 3 modulos:

boton b: Cuando esta entrada esta en 1 carga el

valor de la entrada en la salida b;

boton op: Cuando esta entrada esta en 1 carga el

valor de la entrada en la salida op;

Calculadora: Modulo

encargado de instanciar los

otros modulos.

1

Salidas

CALCULADORA

module calculadora(entrada,boton_a,boton_b,

boton_op,rdo,carry,zero);

a: Este registro de salida sera un operando de la

ALU.

b: Este registro de salida sera un operando de la

ALU.

op: Este registro de salida sera el codigo

de opera

cion de la ALU.

ALU

alu(a,b,op,rdo,carry,zero);

Como la calculadora es el modulo

que instancia a los

iguales a las enotros dos modulos

las entradas seran

iguales a las salidas del

tradas de uno y las salidas seran

otro.

Entradas

a: Este registro de entrada es un operando de la ALU.

b: Este registro de entrada es un operando de la ALU.

op: Este registro de entrada es el codigo

de opera de la ALU.

cion

Variables Internas

wire [BUS_DAT_MSB+1:0] resultado;

Se utiliza una sola variable interna de tipo wirepara

funcion alu

almacenar el resultado de la funcion

Salidas

rdo: Este registro almacena el resultado de la opera de la ALU.

cion

VALIDACION

carry: Este registro de un bit representa el carry de

la operacion.

se muestran los resultados de los testA continuacion

bench realizados sobre todas las operaciones implemen

tadas, el codigo

es el siguiente:

zero: Este registro de un bit es la bandera de zero de

la operacion.

2

module ALU_tb ;

2

3

4

5

6

7

// Inputs

reg [ 7 : 0 ] entrada ;

reg boton_a ;

reg boton_b ;

reg boton_op ;

8

9

10

11

12

// Outputs

wire [ 7 : 0 ] rdo ;

wire carry ;

wire zero ;

13

14

15

16

17

18

19

20

21

22

23

// Instantiate the Unit Under Test (UUT)

calculadora uut (

. entrada ( entrada ) ,

. boton_a ( boton_a ) ,

. boton_b ( boton_b ) ,

. boton_op ( boton_op ) ,

. rdo ( rdo ) ,

. carry ( carry ) ,

. zero ( zero )

);

24

25

26

27

28

29

30

31

32

33

34

35

36

initial begin

// Initialize Inputs

entrada = 7 ;

boton_a = 1 ;

#20

boton_a = 0 ;

entrada = 5 ;

boton_b = 1 ;

#20

boton_b = 0 ;

entrada = 8 ' b00100000 ; // ADD

boton_op = 1 ;

37

// Wait 100 ns for global reset to finish

#20;

38

39

40

// Add stimulus here

41

SUB (binario 100010)

42

43

end

44

45

Variable

a

b

op

resultado

endmodule

Para las pruebas se fueron cambiando los valores de entrada, para cargar los registros con los valores que prueben mejor cada una de las operaciones.

ADD (binario 100000)

Variable

a

b

op

resultado

Valor

250

20

100000

14 + (carry)

Teniendo en cuenta el carry (256 por ser bit 9) mas 14 se

tiene 270.

3

Valor

250

20

100010

230

AND (binario 100100)

Variable

a

b

op

resultado

Valor

10101010

11110000

100100

10100000

XOR (binario 100110)

Variable

a

b

op

resultado

OR (binario 100101)

Variable

a

b

op

resultado

Valor

10101010

11110000

100101

11111010

4

Valor

10101010

11110000

100110

01011010

NOR (binario 100111)

Variable

a

b

op

resultado

Valor

10101010

11110000

100111

01011010

Tener en cuenta que el valor de b no se utiliza en esta

el shift siempre es de un bit. Ademas

obseroperacion,

var que se mantuvo el 1 en el bit mas significativo, en la

proxima

prueba se pone 0 como bit mas significativo de

a para hacer enfasis

en la diferencia.

SRA (binario 000011)

Variable

a

b

op

resultado

Valor

10101010

11110000

000011

11000011

Variable

a

b

op

resultado

5

Valor

00000110

11110000

000011

00000011

Al igual que SRA el valor de b no se tiene en cuenta en

Observar que en este caso se relleno con

la operacion.

cero logico

en vez de mantener el bit mas significativo.

SRL (binario 000010)

Variable

a

b

op

resultado

Valor

10000110

11110000

000010

10100000

You might also like

- 2.1 Convertidores CA CDDocument30 pages2.1 Convertidores CA CDJesus Eduardo Bordek KabralezNo ratings yet

- Evaluación Sumativa 3Document4 pagesEvaluación Sumativa 3tomas espinaNo ratings yet

- Simbología eléctrica y esquemas de controlDocument21 pagesSimbología eléctrica y esquemas de controlRonal Anccare100% (1)

- Disparo Con UJTDocument27 pagesDisparo Con UJTJulio Adrian Alcaraz Valdes100% (3)

- Ejercicios Planeacion AgregadaDocument5 pagesEjercicios Planeacion AgregadaGaryIvánAntonioAjnoNo ratings yet

- Street Fighter EX 2 PlusDocument13 pagesStreet Fighter EX 2 PlusFab FabsNo ratings yet

- Historia y Clasificación de La AutomatizacionDocument11 pagesHistoria y Clasificación de La AutomatizacionGerardo CastanedaNo ratings yet

- Palabras Reservadas Del IDE de ArduinoDocument8 pagesPalabras Reservadas Del IDE de ArduinoGrace LunaNo ratings yet

- Conversor Digital A AnalogoDocument58 pagesConversor Digital A AnalogoCynthia Garcia100% (1)

- Epson PF 220 IIDocument1 pageEpson PF 220 IIImpresoras FiscalesNo ratings yet

- Ejemplo Examen I Parcial 2017Document2 pagesEjemplo Examen I Parcial 2017Rafael MartinezNo ratings yet

- Practica Diagramas de Flujo SABADO 9Document8 pagesPractica Diagramas de Flujo SABADO 9josafat coetezNo ratings yet

- Práctica Calificada Nro 4 2020-I IN 0702 G3Document1 pagePráctica Calificada Nro 4 2020-I IN 0702 G3LeslyBubaNo ratings yet

- Cap2 - Registros de Funciones EspecialesDocument6 pagesCap2 - Registros de Funciones Especialeslgrome73No ratings yet

- Ejemplos de Programas para Microcontrolador PICDocument4 pagesEjemplos de Programas para Microcontrolador PICIvan Velasquez IrineoNo ratings yet

- Fusibles ATmega16Document4 pagesFusibles ATmega16Jhon JairoNo ratings yet

- CEPREUNAC 2007 Economía Semana 11 PDFDocument6 pagesCEPREUNAC 2007 Economía Semana 11 PDFJHON VARGASNo ratings yet

- CFGBNMDocument5 pagesCFGBNMAnonymous SrpvDZo5CNo ratings yet

- Motorola 6800Document2 pagesMotorola 6800Geraldine HernandezNo ratings yet

- Circuito ParqueoDocument1 pageCircuito ParqueoOsvinJokhadesNo ratings yet

- Teorema de Probabilidad Total-Teorema de BayesDocument6 pagesTeorema de Probabilidad Total-Teorema de BayesJuan Sebastian Valbuena GarciaNo ratings yet

- Unidad 1 - Interés Simple PDFDocument13 pagesUnidad 1 - Interés Simple PDFEspruclin AstraprusorroNo ratings yet

- EJERCICIOSDocument6 pagesEJERCICIOSAngel ChirinosNo ratings yet

- Características circuitos CA R-LDocument11 pagesCaracterísticas circuitos CA R-LJose Eduardo Muñoz ZegarraNo ratings yet

- Casos para Salida Computacional PDFDocument11 pagesCasos para Salida Computacional PDFedgar morenoNo ratings yet

- Práctica No. 4 Sobre Costos de ProducciónDocument4 pagesPráctica No. 4 Sobre Costos de ProducciónDiego100% (1)

- GLCD240x128PIC18F4550Document4 pagesGLCD240x128PIC18F4550eeindustrialNo ratings yet

- Programación dinámica para la optimización de recursos en problemas de transporte, producción, contratación y mantenimientoDocument2 pagesProgramación dinámica para la optimización de recursos en problemas de transporte, producción, contratación y mantenimientoJoseMiguelBaezaNo ratings yet

- Domótica Con ArduinoDocument12 pagesDomótica Con ArduinoAnonymous 4yqrYm3No ratings yet

- Análisis Del EntornoDocument11 pagesAnálisis Del EntornoSebastian Zelada ArancibiaNo ratings yet

- LDMicroDocument25 pagesLDMicroLeandro SienraNo ratings yet

- Ejercicios de AlgoritmoDocument9 pagesEjercicios de AlgoritmoRisco Lopez ArnoldNo ratings yet

- Diagrama de GanttDocument3 pagesDiagrama de GanttmarkNo ratings yet

- Caracteristicas Generales de 8085Document34 pagesCaracteristicas Generales de 8085Zabdiel Culebro HIpolitoNo ratings yet

- Digital I - P6 - ContadoresDocument6 pagesDigital I - P6 - ContadoresOliver Gálvez ZavaletaNo ratings yet

- Control de LCD en BASICDocument6 pagesControl de LCD en BASICPollo de la Sexta100% (1)

- Taller 2016Document9 pagesTaller 2016jecalpa27No ratings yet

- Microcontroladores Freescale HC11 HC12 MCF5282 comparativa características usosDocument7 pagesMicrocontroladores Freescale HC11 HC12 MCF5282 comparativa características usosMarthaNo ratings yet

- Cotizacion de ImpresorasDocument1 pageCotizacion de ImpresorasMmerc xDNo ratings yet

- Practica Dirigida Dop y Dap 2016-1Document3 pagesPractica Dirigida Dop y Dap 2016-1Alexis AntonNo ratings yet

- MODULO - ADC Del DsPICDocument24 pagesMODULO - ADC Del DsPICOlesya SergeevaNo ratings yet

- Entrenador PICAXE: programador y circuitos para microcontroladoresDocument9 pagesEntrenador PICAXE: programador y circuitos para microcontroladoresLenin SanNo ratings yet

- Selección de proyectos de inversión con TMAR 15% y presupuesto $20,000Document12 pagesSelección de proyectos de inversión con TMAR 15% y presupuesto $20,000Melany CruzNo ratings yet

- Fundamentos Proton Basic 40Document8 pagesFundamentos Proton Basic 40Kenyo Manuel Miranda QuispeNo ratings yet

- Plan de negocios guía INEI Ministerio ProducciónDocument1 pagePlan de negocios guía INEI Ministerio ProducciónAllison Mancilla DiazNo ratings yet

- Soldeo Por ElectroescoriaDocument24 pagesSoldeo Por Electroescorianagola10No ratings yet

- TUBERÍASDocument56 pagesTUBERÍASEmirEstefanoPandalZavaleta100% (1)

- Ventajas de Multiplexar Display 7 SegmentosDocument12 pagesVentajas de Multiplexar Display 7 SegmentosIsrael MartinNo ratings yet

- Estructura SecuencialDocument4 pagesEstructura SecuencialJuanGabrielMagneNo ratings yet

- Contador Hexadecimal 16F84Document5 pagesContador Hexadecimal 16F84tony_flores_11100% (2)

- Plan de Mantenimiento Preventivo - Extrusora PDFDocument4 pagesPlan de Mantenimiento Preventivo - Extrusora PDFfranksalvatNo ratings yet

- Programacion Lineal Electronica ProblemasDocument17 pagesProgramacion Lineal Electronica ProblemasMonica HuancaNo ratings yet

- Compuertas LogicasDocument4 pagesCompuertas LogicasDtn VilNo ratings yet

- Intel y AMD, La Guerra de Los Procesadores PDFDocument10 pagesIntel y AMD, La Guerra de Los Procesadores PDFjoseave0% (1)

- Suma y Resta de Numeros ComplejosDocument4 pagesSuma y Resta de Numeros ComplejosJimena PiconNo ratings yet

- Capituo II EjerciciosDocument5 pagesCapituo II EjerciciosCristhianMijaelJuárez100% (1)

- Plan de Negocios Pajillas y Vasos ComestiblesDocument5 pagesPlan de Negocios Pajillas y Vasos ComestiblesLuz TejerinaNo ratings yet

- Microcontrolador. TeoríaDocument38 pagesMicrocontrolador. TeoríaAnghel Moreno100% (1)

- Comandos Principales de ArduinoDocument11 pagesComandos Principales de ArduinoCarlos GálvezNo ratings yet

- Kit 1210 Seguidor Linea Velocista ProgramadoDocument11 pagesKit 1210 Seguidor Linea Velocista ProgramadoJulio Ibarra MoedanoNo ratings yet

- Comparador Analógico Pic16f887Document1 pageComparador Analógico Pic16f887Brandon BarriosNo ratings yet

- Calculadora 8 bits ALU MATLABDocument8 pagesCalculadora 8 bits ALU MATLABEdwin Gonzalez MedinaNo ratings yet

- Desarrollo Ejercicios Prácticos Nro.2Document3 pagesDesarrollo Ejercicios Prácticos Nro.2andresteve07No ratings yet

- Contrato Locacion ObraDocument5 pagesContrato Locacion Obraandresteve07No ratings yet

- TP Laboratorio Nro 1Document9 pagesTP Laboratorio Nro 1andresteve07No ratings yet

- Laboratorio Nro1: Sumador 2 BitsDocument8 pagesLaboratorio Nro1: Sumador 2 Bitsandresteve07No ratings yet

- Laboratorio 3Document3 pagesLaboratorio 3andresteve070% (1)

- MonografiaDocument12 pagesMonografiaandresteve07No ratings yet

- Informe TP1 SO1Document12 pagesInforme TP1 SO1andresteve07No ratings yet

- Simulaci Ón de Una Red Fexible de Producci On Mediante Redes de PetriDocument12 pagesSimulaci Ón de Una Red Fexible de Producci On Mediante Redes de Petriandresteve07No ratings yet

- tp6 PDFDocument6 pagestp6 PDFandresteve07No ratings yet

- Contrato Locacion SeriviosDocument3 pagesContrato Locacion Seriviosandresteve07No ratings yet

- Cap1 IntroduccionDocument62 pagesCap1 Introduccionandresteve07No ratings yet

- Laboratorio 1Document3 pagesLaboratorio 1andresteve07No ratings yet

- Cap2 ProcesosDocument47 pagesCap2 Procesosandresteve07No ratings yet

- TP Pericias 13Document10 pagesTP Pericias 13amsabaterNo ratings yet

- SASE2013 Introduccion Practica A Los FPGADocument145 pagesSASE2013 Introduccion Practica A Los FPGAandresteve07No ratings yet

- Laboratorio ReactorDocument7 pagesLaboratorio Reactorandresteve07No ratings yet

- SCDCap5ModDelta PDFDocument12 pagesSCDCap5ModDelta PDFandresteve07No ratings yet

- Libro Comunicacion Digital PDFDocument790 pagesLibro Comunicacion Digital PDFMaxwell MartinezNo ratings yet

- Motores de CC de Iman Permanente y Rotor - v5Document92 pagesMotores de CC de Iman Permanente y Rotor - v5krownsNo ratings yet

- FSKDocument3 pagesFSKCarlos Franco Llapaco AvilaNo ratings yet

- Laboratorio 2Document5 pagesLaboratorio 2andresteve07No ratings yet

- Sistemas Embebidos 2011 2doc Intro LPC1769 RidolfiDocument33 pagesSistemas Embebidos 2011 2doc Intro LPC1769 Ridolfiandresteve07No ratings yet

- Ciclo OttoDocument9 pagesCiclo Ottoandresteve07No ratings yet

- Estructura de DatosDocument40 pagesEstructura de DatosFelipe QuintanaNo ratings yet

- Divisor de Voltaje y CorrienteDocument4 pagesDivisor de Voltaje y CorrienteJuan Carlos MorenoNo ratings yet

- Electrónica AnaliticaDocument71 pagesElectrónica Analiticamakoko2910No ratings yet

- Sum Ad or Rest Ad or 3 BitsDocument6 pagesSum Ad or Rest Ad or 3 Bitsignaci00No ratings yet

- Tr2 - Electronica Industrial (Garcia Nolasco Raúl Luis)Document10 pagesTr2 - Electronica Industrial (Garcia Nolasco Raúl Luis)Raul Luis Garcia NolascoNo ratings yet

- Configuraciones básicas del temporizador integrado 555: comparador, monoestable, biestable y astableDocument7 pagesConfiguraciones básicas del temporizador integrado 555: comparador, monoestable, biestable y astablevannarutoNo ratings yet

- Informe PLLDocument10 pagesInforme PLLRubenCalleSanchezNo ratings yet

- Laboratorio 2 CE3 Verano1Document4 pagesLaboratorio 2 CE3 Verano1Cesar Idvorsky Gutiérrez CachiqueNo ratings yet

- Ep2 Convertidor Elevador P.rectificadorDocument11 pagesEp2 Convertidor Elevador P.rectificadorJair TrellesNo ratings yet

- 3 Clase Ensamblador UC, ALU y DemasDocument9 pages3 Clase Ensamblador UC, ALU y DemasAan LodnarNo ratings yet

- GEK97367C en EsDocument28 pagesGEK97367C en Esivaneduardo14No ratings yet

- Actividad 1 de Informatica 4 Periodo PDFDocument6 pagesActividad 1 de Informatica 4 Periodo PDFSARITA VALENTINA ORDOÑEZ ESPAÑANo ratings yet

- Transmisores DigitalesDocument15 pagesTransmisores DigitalesAguila Real0% (1)

- Laboratorio Electrónica: Emisor ComúnDocument4 pagesLaboratorio Electrónica: Emisor ComúnWilson Amado Miranda MendozaNo ratings yet

- Optoaislador MOC3011 7.5kV 1Canal 10mA Phototriac DIPDocument2 pagesOptoaislador MOC3011 7.5kV 1Canal 10mA Phototriac DIPgreciajgbNo ratings yet

- Soporte y MantenimientoDocument118 pagesSoporte y MantenimientoBere GC100% (1)

- TV Analogica Test PDFDocument8 pagesTV Analogica Test PDFlgbtbtaco46No ratings yet

- CCTV - Marzo - Abril 2015Document14 pagesCCTV - Marzo - Abril 2015Emmanuel Alberto Herrera PobletNo ratings yet

- Comparar Dos Valores EnsemblerDocument5 pagesComparar Dos Valores Ensemblersergio hernan morenoNo ratings yet

- IGBT_PotenciaDocument18 pagesIGBT_PotenciajhonNo ratings yet

- CodewordDocument3 pagesCodewordSandy SureNo ratings yet

- Teorema de SuperposicionDocument15 pagesTeorema de SuperposicionLuis LopezNo ratings yet

- Modelado Convertidores CCDocument56 pagesModelado Convertidores CCPablo García SuárezNo ratings yet

- Informe Laboratorio BJTDocument13 pagesInforme Laboratorio BJTMy Little PatataNo ratings yet

- Practica MicrofonoDocument15 pagesPractica MicrofonoDiiaNiitaRamiirezNo ratings yet

- 2.1.3. Transistores Bipolares (BJT) .Document16 pages2.1.3. Transistores Bipolares (BJT) .Luis Mendoza LopezNo ratings yet

- SDLDocument19 pagesSDLJhonatan Gerardo Soto PuellesNo ratings yet

- Atributos ElectroDocument17 pagesAtributos Electroalimber15No ratings yet

- TecnologiasInalambricas mODULACIONES PDFDocument65 pagesTecnologiasInalambricas mODULACIONES PDFJuan Manuel Hernandez B.No ratings yet

- Grupo 2 Microcontroladores AvrDocument11 pagesGrupo 2 Microcontroladores AvrAlexander Barboza AnayaNo ratings yet

- Topologias de RedesDocument22 pagesTopologias de Redesrigoberto aguilarNo ratings yet