Professional Documents

Culture Documents

Electrical - Ijeeer - Comparison of Various - Vamsi

Uploaded by

TJPRC PublicationsOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electrical - Ijeeer - Comparison of Various - Vamsi

Uploaded by

TJPRC PublicationsCopyright:

Available Formats

International Journal of Electrical and Electronics

Engineering Research (IJEEER)

ISSN(P): 2250-155X; ISSN(E): 2278-943X

Vol. 4, Issue 5, Oct 2014, 1-12

TJPRC Pvt. Ltd.

COMPARISON OF VARIOUS MULTILEVL INVERTER CONFIGURATIONS

FOR SEVEN LEVELS

P. V. NARASIMHARAO1, PRABHAKARA SHARMA. PIDATALA2, B. S. S. G. PARDHU3 & P. ANEELA RANI4

1

Assistant Professor, Department of Electrical and Electronics Engineering, Vishnu Institute of Technology,

Bhimavaram, West Godavari, Andhra Pradesh, India

Assistant Professor, Department of Electrical and Electronics Engineering, Kallam Harnadhareddy Institute of

Technology, Prattipadu, Guntur Andhra Pradesh, India

3

Assistant Professor, Department of Electrical & Electronics Engineering, Aditya Engineering College,

Peddapuram, East Godavari, Andhra Pradesh, India

Assistant Professor, Department of Electrical & Electronics Engineering, Akula Sree Ramulu College of Engineering,

Tanuku, West Godavari, Andhra Pradesh, India

ABSTRACT

This concept mainly deals with the multilevel inverter to increase levels using cascade h-bridge concept.

This paper, dissimilar configuration based on different DC bus voltage for a cascade H-Bridge multilevel inverter have

been existing. Four different type techniques symmetrical, asymmetrical, Number of switches is minimised or reduced, and

multi string actions of a seven-level cascade H-Bridge inverters have been compare, in order to find an optimum bargain

with lower switching losses and optimized output voltage excellence. The similarity results show that an asymmetrical

configuration can obtain more voltage levels in output voltage with same number of component compared with the

conservative seven-level inverter and this will lead to the less number of harmonic content of output voltage.

The compensation of this control method are simplicity and applicability for n-level multilevel inverters, without a major

change in the control circuit.

KEYWORDS: H-Bridge Multilevel Inverter, Total Harmonic Distortion and Switching Losses

INTRODUCTION

In future the power-handling capabilities of static switch devices such as IGBTs with voltage rating up to 4.5 kV

commercially available, has made the use of the voltage source inverters (VSI) possible for high-power applications.

High power and high-voltage changes systems have turn into very important issues for the power electronic manufacturing

handling the huge ac drive and electrical power applications at equally the transmission and sharing levels. For these

reasons, a new family of multilevel inverters has emerged as the solution for working with upper voltage levels.

Multilevel inverters include an array of power semiconductors and capacitor voltage sources, the output of which generate

voltages with stepped waveforms. Capacitor, batteries storage, and RES voltage sources are used as the several dc voltage

sources.

The switching frequency is limited by switching losses are used in the applications of high power and high

voltage applications, multilevel inverters have set up wide acceptance as they can reach low harmonic component with low

www.tjprc.org

editor@tjprc.org

P. V. Narasimharao, Prabhakara Sharma Pidatala, B. S. S. G. Pardhu & P. Aneela Rani

switching frequency. still low blocking voltage the main advantage is switching devices and the above switching device is

the other type of converters and minimum harmonic distortion (THD) and switching losses are increased.

Multilevel inverters are mainly used to produce a required voltage wave shape from so many levels of dc voltages.

Their major advantages are low harmonic distortion percent of the getting output voltage, low electromagnetic emissions,

high efficiency ability to perform at high voltages and modularity. The topology assumed for this concept is the cascaded

H-bridge multilevel inverter which requires so many separate dc sources.

In cascaded multilevel inverter each individual phase requires n dc sources for 2n+1 level. We getting the level

to use that dc sources, for so many applications, multiple dc sources are required difficult lengthy cables and this could

lead to voltage disturb among the dc sources. With an aim to lessen the number of dc sources required for the cascaded

multilevel inverter for a motor drive, in this paper the main concept is sources and focuses on difference between

asymmetric and symmetric cascade multi level inverter that uses same and unequal dc sources in each phase to generate a

seven level equal step multilevel output. It means less switching losses for the equivalent total harmonic distortion. It also

improves the dependability by decreasing the number of dc Sources when comparing symmetrical H-Bridge multi level

inverter.

The MLI modulation technique increases the output voltage and gives a low THD of a relative evaluation between

the VAIS pulse width modulation and the conventional modulation is also existing in terms of output voltage quality,

power circuitry complexity, and total harmonic distortion (THD), Both the MLI circuit topology and its new manage

format are described in detail and their performance is verified based on Matlab/simulation software.

MULTILEVEL INVERTER

Negligible number in multilevel converter topologies is three level voltage levels. Due to the bi-directional

switches, in both rectifier and inverter modes in these two modes the multilevel VSC can work. This is reason most of the

time it is preferred to as a converter instead of an inverter in this dissertation. A multilevel converter can switch either its

input or output nodes (or both) between multiple (more than two) levels of voltage or current. As the number of levels

reach infinity, the output THD reaches to zero. The number of the possible voltage levels, is limited by voltage unbalance

problems, voltage clamping requirements, circuit plan and covering constraints difficulty of the controller, and, of course,

capital and preservation costs. In industrial applications three different major multilevel converter structures have been

applied: cascaded H-bridges converter with different dc sources, diode clamped, and flying capacitors. The multilevel

inverter structures are the main focus of discussion in this chapter; however, the illustrated structures can be implemented

for rectifying operation as well. Although each type of multilevel converters share the advantages of multilevel voltage

source inverters, they may be suitable for specific application due to their structures and drawbacks. Operation and

structure of some important type of multilevel converters are discussed in the following sections.

In a multilevel voltage source inverter, the dc-link voltage Vdc is obtained from any equipment which can yield

stable dc source. Series connected capacitors constitute energy tank for the inverter provided that a few nodes to which

multilevel inverter can be connected. First and foremost, the series connected capacitors will be supposed to be several

voltage sources of the same value. Every one capacitor voltage Vc is given by Vc=Vdc/ (n-1) calculated this formulae,

where n denotes the number of level. The schematic diagram of one phase leg of inverters with dissimilar number of levels,

for which the action of the power semiconductors is represents by a perfect switch with a number of positions.

Impact Factor (JCC): 5.9638

Index Copernicus Value (ICV): 3.0

Comparison of Various Multilevel Inverter Configurations for Seven Levels

The two-level inverter generates an output voltage with two values (levels means +Vdc and -Vdc) with respect to the

negative terminal of the capacitor, while the three-level inverter generates three voltages (means +Vdc, 0 and -Vdc), and so

on.

Figure 1: One Phase Leg of an Inverter with (a) Two Levels, (b) Three Levels, and (c) n Levels

PROPOSED MULTILEVEL INVERTER CONFIGURATIONS FOR SEVEN LEVELS

Symmetrical Configurations

Structure of 7 level single-phase cascade H-Bridge inverter is shown in below. In conventional structure DC link

voltage is shared equally among the three DC voltage sources should be regulated to the equal value at V/3 if DC voltage

across three voltage sources is increases to Vdc. In this all possible switching states with comparative output voltage levels

in conventional arrangement in figure 2. As it is clear seven level output voltage levels can be generated based on

dissimilar switching states. Figure 2 depicted the adjacency of switching states regarding to switching states which shows

all output voltage level of single-phase conservative topology. As it shown, adjacency is accessible between all switching

states as it is likely to move from one level to other one with one switching change.

Figure 2: Structure of Seven-Level Single-Phase Cascade H-Bridge Inverter

Table 1: Output Voltage according to the Switches OnOff Condition

www.tjprc.org

editor@tjprc.org

P. V. Narasimharao, Prabhakara Sharma Pidatala, B. S. S. G. Pardhu & P. Aneela Rani

Table 1 shows the switching combinations that generated the seven output-voltage levels (Vdc, 2Vdc, 3Vdc,

0,-Vdc,-2Vdc,-3Vdc).

Asymmetrical Configurations

The seven - level cascaded multilevel inverter presents two H-Bridges in each bridge 4 switches presents total

8 switches are present. The upper bridge indicates H-Bridge H1consists of a separate DC source Vdc and the second

H-Bridge H2consists of a dc source 2Vdc as shown in below figure. The output of H-Bridge-1 be denoted as V1 and the

output of H-Bridge-2 be denoted as V2 Hence the total output voltage is given by V (t) =V1 +V2 By one another ON and

OFF the switches S1, S4 and S2,S3 of H-Bridge-1 appropriately, output of H1 V1 can be made equal to +Vdc, 0 or -Vdc.

Similarly the output voltage of H-Bridge-2 V2 can be made equal to 2Vdc, 0 or 2Vdc by opening and closing the switches

of H2.

Figure 3: Asymmetric Cascaded Multilevel Inverter

The advantages of the topology are:

Reduced number of dc sources.

High speed capability

Low switching loss

High conversion efficiency.

Table 2: Output Voltage According to the Switches OnOff Condition

Vo

Vdc

2Vdc

3Vdc

0

-Vdc

-2Vdc

-3Vdc

S1

On

On

On

On

Off

On

On

S2

On

Off

On

Off

Off

Off

On

S3

Off

On

Off

On

On

On

Off

S4

Off

Off

Off

Off

On

Off

Off

S5

On

On

On

On

On

On

On

S6

Off

On

On

Off

Off

On

On

S7

On

Off

Off

On

On

Off

Off

S8

Off

Off

Off

Off

Off

Off

Off

Reduced Number of Switches

The main objective is to improve the quality output voltage of the multilevel inverter with reduced number of

switches. An important issue in multilevel inverter design is that to generate nearly sinusoidal output voltage waveform

and to eliminate lower order harmonics. A key concern in the fundamental switching scheme is to determine the switching

angles in order to produce the voltage with fundamental frequency.

Impact Factor (JCC): 5.9638

Index Copernicus Value (ICV): 3.0

Comparison of Various Multilevel Inverter Configurations for Seven Levels

Figure 4: Power Circuit For 7-Level

There are three modes of operation for the proposed 7-level multilevel inverter. These modes are explained as

below.

Powering Mode

This occurs when together the load current and voltage have the same polarity. In the positive half cycle, when the

output voltage is Vdc, the current pass comprises; the below supply, D6, Switch-1, load, Switch-2, and back to the lower

supply. When the output voltage is 2Vdc, current pass is; the lower source, S5, the upper source, Switch-1, load, Switch-2,

and back to the lower source. When the output voltage is 3Vdc, the current pass comprises: top supply, Switch-1, load,

Switch-2, S7, lower supply. In the negative half cycle, Switch-1 and Switch-2 are replaced by Switch-3 and Switch-4

respectively.

Free-Wheeling Mode

This mode exist one of the main switches is turned-off while the load current needs to continue its pass due to

load inductance. This is achieved with the help of the anti-parallel diodes of the switches, and the load circuit is no

connection from the source terminals. In this mode, the positive half cycle current pass comprises; Switch-1, load,

and Diode-2 or Switch-2, load, and Diode-3, while in the negative half cycle the current pass includes Switch-4, load,

and Diode-4 or Switch-3, load, and Diode-1. Regenerating Mode In this mode, part of the energy stored in the load

inductance is return back to the source. This happens during the intervals when the load current is negative during the

positive half cycle and similarly, where the output voltage is zero. The positive current pass comprises; load, Diode-2,

Switch-6, the lower source, and Diode-3, while the negative current pass comprises; load, Diode-1, Switch-6, the lower

source, and Diode-4.

Table 3: Output Voltage According to the Switches OnOff Condition

www.tjprc.org

editor@tjprc.org

P. V. Narasimharao, Prabhakara Sharma Pidatala, B. S. S. G. Pardhu & P. Aneela Rani

Seven Level Multi- String Inverter Topology

The five levels multi-string inverter has so many drawbacks for example big size filter is used, the main drawback

is filter size increases cost of the equipment is increases high harmonics and high electromagnetic interference. This can be

reduced by using seven levels multi-string inverter. The s 7 levels multi-string inverter consists of 2 auxiliary switches

these are separated switches and excited separately. The auxiliary switching of 7 levels multi-string inverter is given below

figure

Figure 5: Auxiliary Switch of the Proposed Multi-String Inverter

Table 4: Output Voltage According to the Switches OnOff Condition

Vo

Vdc

2Vdc

3Vdc

0

-Vdc

-2Vdc

-3vdc

S1

Off

Off

On

Off

Off

Off

Off

S2

On

On

On

On

Off

Off

Off

S3

Off

Off

Off

Off

On

On

On

S4

Off

Off

Off

On

Off

Off

On

S5

Off

On

Off

Off

On

Off

Off

S6

On

Off

Off

Off

Off

On

Off

MATLAB AND SIMULINK RESULTS

Case I: Symmetrical Configurations

Figure 6: Symmetrical Seven Level Configuration

Impact Factor (JCC): 5.9638

Index Copernicus Value (ICV): 3.0

Comparison of Various Multilevel Inverter Configurations for Seven Levels

Figure 7: Symmetrical Seven Level Output Wave Form

Figure 8: Figure Total Harmonic Distortion for Symmetrical

Case 2: Asymmetrical Configurations

Figure 9: Asymmetrical Seven Level Configuration

Figure 10: Asymmetrical Seven Level Output Wave Form

www.tjprc.org

editor@tjprc.org

P. V. Narasimharao, Prabhakara Sharma Pidatala, B. S. S. G. Pardhu & P. Aneela Rani

Figure 11: Total Harmonic Distortion for Asymmetrical

Case 3: Reduced Number of Switches

Figure 12: Matlab Design for Reduced Number of Switches

Figure 13: Output Voltage for Reduced Number of Switches

Impact Factor (JCC): 5.9638

Index Copernicus Value (ICV): 3.0

Comparison of Various Multilevel Inverter Configurations for Seven Levels

Figure 14: Total Harmonic Distortion for Reduced Number of Switches

Case 4: Seven Level Multi- String Inverter

Figure 15: Matlab Design for Seven Level Multi- String Inverter

Figure 16: Output Voltage for Multi String

www.tjprc.org

editor@tjprc.org

10

P. V. Narasimharao, Prabhakara Sharma Pidatala, B. S. S. G. Pardhu & P. Aneela Rani

Figure 17: Total Harmonic Distortion for Multi String

Table 5: Reduction of Switches

CONCLUSIONS

This paper presented a comparison between Symmetrical, Asymmetrical, Reduced number of switches,

Multi String, seven level h-bridge inverter which uses equal dc sources and symmetrical MLI and different DC sources an

asymmetrical MLI, reduced switches reaming techniques.

REFERENCES

1.

Jose Rodriguez, Jih-Sheng Lai, and Fang Zheng Peng, Multilevel Inverters: A Survey of Topologies, Controls,

and Applications, IEEE Transactions on Industrial Electronics, Vol. 49, No. 4, August 2002. pages 724-738.

2.

Zhong Du, Leon M. Tolbert, John N. Chiasson, and Burak Opines, A Cascade Multilevel Inverter Using a Single

DC Source, 0-7803-9547-6/06/$20.00 2006 IEEE pages 426-430.

3.

Remus Teodorescu, Frede Blaabjerg, John. K. Pedersen, Ekrem Cengelci, and Prasad N. Enjeti,

Multilevel Inverter by Cascading Industrial VSI, IEEE Transaction on industrial electronics, Vol.49, No.4,

August 2002. pages 832-838.

4.

Manjrekar, M.D., and LIPO, T.A:A hybrid multilevel inverter topology for drive applications,

Proceedings of the IEEE APEC, pp.523-529, 1998.

5.

Walker, G.R.; Sernia, P. C:Cascaded DC-DC converter connection of photovoltaic modules Power Electronics

Specialists Conference, pesc IEEE 33rd Annual,vol 1,pp. 24 29, 2002.

Impact Factor (JCC): 5.9638

Index Copernicus Value (ICV): 3.0

11

Comparison of Various Multilevel Inverter Configurations for Seven Levels

6.

Fang Zheng Peng; Jih-Sheng Lai; McKeever, J; VanCoevering, J: A multilevel voltage-source inverter with

separate DC sources for static VAr generation, IAS '95., Conference Record of the 1995 IEEE,vol.3.pp.

2541 2548, 1995.

7.

Panagis, P; Stergiopoulos, F; Marabeas, P; Manias, S; Comparison of state of the art multilevel inverters.

IEEE, PESC, pp. 4296 4301,2008.

AUTHORS DETAILS

Mr. P. V. Narasimha Rao obtained his Bachelor of Technology in Electrical and Electronics Engineering from

JNTU Hyderabad, India. He completed his Master of Technology in High Voltage Engineering from University College of

Engineering, JNTU Kakinada, Andhra Pradesh, India. His area of interest includes Multi Level Inverters,

DC-DC Converters and Renewable Energy Sources. He is currently working as an Assistant Professor in Electrical and

Electronics Engineering Department in Vishnu Institute of Technology, Bhimavaram, Andhra Pradesh, India

Mr. Prabhakara Sharma Pidatala obtained his Bachelor of Technology in Electrical and Electronics

Engineering from ANU Numbur, India. He completed his Master of Technology in High voltage Engineering from

University College of Engineering, JNTU-Kakinada, Andhra Pradesh, India. His area of interest includes Renewable

Energy Sources, FACTS Devices, Multi Level Inverters. He is currently working as an Assistant Professor in Electrical

and Electronics Engineering Department in Kallam Haranadhareddy Institute of Technolgy, Chowdavaram,

Andhra Pradesh, India.

Mr. B. S. S. G. Pardhu obtained his Bachelor of Technology in Electrical and Electronics Engineering from

JNTU Hyderabad, India. He completed his Master of Technology in Advanced Power Systems in University College of

Engineering, JNTU-Kakinada, Andhra Pradesh, India. His area of interest includes Multilevel Inverters, Reactive Power

Management. He is currently working as Assistant Professor in Electrical and Electronics Engineering Department in

Aditya Engineering College, Surampalem, Andhra Pradesh, India.

www.tjprc.org

editor@tjprc.org

12

P. V. Narasimharao, Prabhakara Sharma Pidatala, B. S. S. G. Pardhu & P. Aneela Rani

Mrs. P. Aneela Rani obtained her Bachelor of Technology in Electrical and Electronics Engineering from JNTU

Kakinada, Andhra Pradesh, India. She Completed her Master of Technology in Power Electronics, JNTU-Kakinada,

Andhra pradesh, India. Her area of interest includes Multilevel Inverters, Reactive Power Management,

Electrical Machines Control. She is currently working as Assistant Professor in Electrical and Electronics Engineering

Department in Akula Sree Ramulu College of Engineering, Tanuku, Andhra Pradesh, India.

Impact Factor (JCC): 5.9638

Index Copernicus Value (ICV): 3.0

You might also like

- Baluchari As The Cultural Icon of West Bengal: Reminding The Glorious Heritage of IndiaDocument14 pagesBaluchari As The Cultural Icon of West Bengal: Reminding The Glorious Heritage of IndiaTJPRC PublicationsNo ratings yet

- Comparative Study of Original Paithani & Duplicate Paithani: Shubha MahajanDocument8 pagesComparative Study of Original Paithani & Duplicate Paithani: Shubha MahajanTJPRC PublicationsNo ratings yet

- Flame Retardant Textiles For Electric Arc Flash Hazards: A ReviewDocument18 pagesFlame Retardant Textiles For Electric Arc Flash Hazards: A ReviewTJPRC PublicationsNo ratings yet

- 2 52 1649841354 2ijpslirjun20222Document12 pages2 52 1649841354 2ijpslirjun20222TJPRC PublicationsNo ratings yet

- 2 33 1641272961 1ijsmmrdjun20221Document16 pages2 33 1641272961 1ijsmmrdjun20221TJPRC PublicationsNo ratings yet

- Development and Assessment of Appropriate Safety Playground Apparel For School Age Children in Rivers StateDocument10 pagesDevelopment and Assessment of Appropriate Safety Playground Apparel For School Age Children in Rivers StateTJPRC PublicationsNo ratings yet

- 2 29 1645708157 2ijtftjun20222Document8 pages2 29 1645708157 2ijtftjun20222TJPRC PublicationsNo ratings yet

- 2 4 1644229496 Ijrrdjun20221Document10 pages2 4 1644229496 Ijrrdjun20221TJPRC PublicationsNo ratings yet

- 2 51 1656420123 1ijmpsdec20221Document4 pages2 51 1656420123 1ijmpsdec20221TJPRC PublicationsNo ratings yet

- 2 44 1653632649 1ijprjun20221Document20 pages2 44 1653632649 1ijprjun20221TJPRC PublicationsNo ratings yet

- 2 52 1642055366 1ijpslirjun20221Document4 pages2 52 1642055366 1ijpslirjun20221TJPRC PublicationsNo ratings yet

- Using Nanoclay To Manufacture Engineered Wood Products-A ReviewDocument14 pagesUsing Nanoclay To Manufacture Engineered Wood Products-A ReviewTJPRC PublicationsNo ratings yet

- 2 31 1648794068 1ijpptjun20221Document8 pages2 31 1648794068 1ijpptjun20221TJPRC PublicationsNo ratings yet

- The Conundrum of India-China Relationship During Modi - Xi Jinping EraDocument8 pagesThe Conundrum of India-China Relationship During Modi - Xi Jinping EraTJPRC PublicationsNo ratings yet

- 2 51 1651909513 9ijmpsjun202209Document8 pages2 51 1651909513 9ijmpsjun202209TJPRC PublicationsNo ratings yet

- Covid-19: The Indian Healthcare Perspective: Meghna Mishra, Dr. Mamta Bansal & Mandeep NarangDocument8 pagesCovid-19: The Indian Healthcare Perspective: Meghna Mishra, Dr. Mamta Bansal & Mandeep NarangTJPRC PublicationsNo ratings yet

- Analysis of Bolted-Flange Joint Using Finite Element MethodDocument12 pagesAnalysis of Bolted-Flange Joint Using Finite Element MethodTJPRC PublicationsNo ratings yet

- 2 67 1648211383 1ijmperdapr202201Document8 pages2 67 1648211383 1ijmperdapr202201TJPRC PublicationsNo ratings yet

- An Observational Study On-Management of Anemia in CKD Using Erythropoietin AlphaDocument10 pagesAn Observational Study On-Management of Anemia in CKD Using Erythropoietin AlphaTJPRC PublicationsNo ratings yet

- 2 51 1647598330 5ijmpsjun202205Document10 pages2 51 1647598330 5ijmpsjun202205TJPRC PublicationsNo ratings yet

- Numerical Analysis of Intricate Aluminium Tube Al6061T4 Thickness Variation at Different Friction Coefficient and Internal Pressures During BendingDocument18 pagesNumerical Analysis of Intricate Aluminium Tube Al6061T4 Thickness Variation at Different Friction Coefficient and Internal Pressures During BendingTJPRC PublicationsNo ratings yet

- Effectiveness of Reflexology On Post-Operative Outcomes Among Patients Undergoing Cardiac Surgery: A Systematic ReviewDocument14 pagesEffectiveness of Reflexology On Post-Operative Outcomes Among Patients Undergoing Cardiac Surgery: A Systematic ReviewTJPRC PublicationsNo ratings yet

- A Review of "Swarna Tantram"-A Textbook On Alchemy (Lohavedha)Document8 pagesA Review of "Swarna Tantram"-A Textbook On Alchemy (Lohavedha)TJPRC PublicationsNo ratings yet

- Dr. Gollavilli Sirisha, Dr. M. Rajani Cartor & Dr. V. Venkata RamaiahDocument12 pagesDr. Gollavilli Sirisha, Dr. M. Rajani Cartor & Dr. V. Venkata RamaiahTJPRC PublicationsNo ratings yet

- Self-Medication Prevalence and Related Factors Among Baccalaureate Nursing StudentsDocument8 pagesSelf-Medication Prevalence and Related Factors Among Baccalaureate Nursing StudentsTJPRC PublicationsNo ratings yet

- Effect of Degassing Pressure Casting On Hardness, Density and Tear Strength of Silicone Rubber RTV 497 and RTV 00A With 30% Talc ReinforcementDocument8 pagesEffect of Degassing Pressure Casting On Hardness, Density and Tear Strength of Silicone Rubber RTV 497 and RTV 00A With 30% Talc ReinforcementTJPRC PublicationsNo ratings yet

- 2 67 1645871199 9ijmperdfeb202209Document8 pages2 67 1645871199 9ijmperdfeb202209TJPRC PublicationsNo ratings yet

- 2 67 1645017386 8ijmperdfeb202208Document6 pages2 67 1645017386 8ijmperdfeb202208TJPRC PublicationsNo ratings yet

- Vitamin D & Osteocalcin Levels in Children With Type 1 DM in Thi - Qar Province South of Iraq 2019Document16 pagesVitamin D & Osteocalcin Levels in Children With Type 1 DM in Thi - Qar Province South of Iraq 2019TJPRC PublicationsNo ratings yet

- 2 67 1653022679 1ijmperdjun202201Document12 pages2 67 1653022679 1ijmperdjun202201TJPRC PublicationsNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Tutorial 4Document2 pagesTutorial 4Saransh MittalNo ratings yet

- Growatt 1500-US/2000-US/3000-US TL technology datasheetDocument2 pagesGrowatt 1500-US/2000-US/3000-US TL technology datasheetJonathan León100% (1)

- Wa0029. 1Document30 pagesWa0029. 1Angelina BennyNo ratings yet

- MAX 100-150KTL3-X2 LV MV User Manual EN 202312Document83 pagesMAX 100-150KTL3-X2 LV MV User Manual EN 202312JULIO IGLESIASNo ratings yet

- Principles of Electric Circuits, Conventional Flow, 9 EdDocument24 pagesPrinciples of Electric Circuits, Conventional Flow, 9 EdYodel RamírezNo ratings yet

- TL Audio Classic Series 479645Document14 pagesTL Audio Classic Series 479645Nicolas ZuluagaNo ratings yet

- Differential Pressure Switch - Oil ControlDocument6 pagesDifferential Pressure Switch - Oil ControlRakibul HassanNo ratings yet

- Breaker de 608 Sub PDFDocument24 pagesBreaker de 608 Sub PDFGenaro Santiago MartinezNo ratings yet

- Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument17 pagesInsulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodetaynatecNo ratings yet

- UDC2500 Universal Digital Controller Product Manual: 51-52-25-135 August 2005Document222 pagesUDC2500 Universal Digital Controller Product Manual: 51-52-25-135 August 2005kmpoulosNo ratings yet

- Calculate Cable Size and Voltage Drop Electrical Notes Articles PDFDocument10 pagesCalculate Cable Size and Voltage Drop Electrical Notes Articles PDFKamugasha Kagonyera100% (1)

- Contrax Joints Provide Fast, Easy Medium Voltage ConnectionsDocument4 pagesContrax Joints Provide Fast, Easy Medium Voltage ConnectionsAmit BhatiaNo ratings yet

- Bernal Bsar 3B ElectricalDocument16 pagesBernal Bsar 3B ElectricalAidyl Kate BernalNo ratings yet

- Anb Air CondDocument2 pagesAnb Air Condedwin quirozNo ratings yet

- Iso 15257Document34 pagesIso 15257Danilo AmendolaNo ratings yet

- Istar Edge Install Quick Start Guide Ra3 - LT - enDocument26 pagesIstar Edge Install Quick Start Guide Ra3 - LT - enJose ElenilsonNo ratings yet

- Compact Wideband Circularly Polarized Microstrip Antenna Array For 45Ghz ApplicationDocument5 pagesCompact Wideband Circularly Polarized Microstrip Antenna Array For 45Ghz Applicationnguyễn đắc huyNo ratings yet

- Iso 5852 SDocument37 pagesIso 5852 SGhasem A. JavidNo ratings yet

- Mathcad Tutorial: Solving Systems of Equations and Circuit AnalysisDocument6 pagesMathcad Tutorial: Solving Systems of Equations and Circuit AnalysisYadi PermadiNo ratings yet

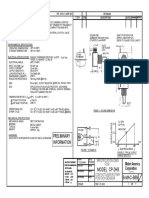

- Preliminary Information: B-MAC-B69 Model Cp-2HbDocument1 pagePreliminary Information: B-MAC-B69 Model Cp-2HbCykhong KhongNo ratings yet

- KAMAL Chapter 12Document38 pagesKAMAL Chapter 12Nida Bagoyboy NatichoNo ratings yet

- Electrical and Electronic Schematic SymbolsDocument16 pagesElectrical and Electronic Schematic SymbolsSanjana Singh100% (1)

- Raychem Kit PDFDocument10 pagesRaychem Kit PDFAdetunji TaiwoNo ratings yet

- 200W Single Output DC-DC Converter SpecificationsDocument3 pages200W Single Output DC-DC Converter SpecificationsAntero CasaniNo ratings yet

- LG Color TV Service ManualDocument26 pagesLG Color TV Service ManualVadakkevalappilNo ratings yet

- POE16S-1AFG Extends PoE Range to 200mDocument3 pagesPOE16S-1AFG Extends PoE Range to 200mSubas ShresthaNo ratings yet

- Panasonic Car Stereo System CQ-CP134U PDFDocument16 pagesPanasonic Car Stereo System CQ-CP134U PDFJuan Carlos SoHeNo ratings yet

- E110B and E120B Excavators Electrical SystemDocument2 pagesE110B and E120B Excavators Electrical Systemedwin quiroz0% (1)

- 128 Coudoint Sliding Rheostats DocumentationDocument20 pages128 Coudoint Sliding Rheostats DocumentationcrestindNo ratings yet

- Electrical Thumb Rules for Motors, Transformers & MoreDocument4 pagesElectrical Thumb Rules for Motors, Transformers & MoreElectrical Radical100% (1)