Professional Documents

Culture Documents

Ee 3002 Prob 5

Uploaded by

dummy1957jOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ee 3002 Prob 5

Uploaded by

dummy1957jCopyright:

Available Formats

EC201-ANALOG CIRCUITS : PROBLEM SET 4

shanthi@ee.iitm.ac.in

Problem 1

The circuit of Fig. 1 shows an amplier.

R

E

=10K

10

(10/1)

(40/1)

(170/1)

(10/1)

5 V

3M

2M

v

i

v

out

M1 M2

M3

M4

V

Tn

=0.7V,

n

C

ox

=200/V

2

|V

Tp

|=0.8V,

p

C

ox

=50/V

2

Figure 1: Problem 1

Determine the operating points of all the devices in the

circuit. For this part, assume = 0 for all devices.

All transistors have nite output impedance, such that

for any transistor, g

m

r

o

= 100. Draw the small signal

equivalent circuit of the amplier. Determine the small

signal gain from v

i

to v

out

and the input and output re-

sistances of the amplier.

Determine the amplitude of the largest sinusoid that can

be applied at the input, so that the output is also a sinu-

soid, devoid of clipping effects. As usual, assume that

the coupling capacitors are innite.

Problem 2

The circuit of Fig. 2 shows a common-drain amplier.

Determine the operating points of all the devices in the

circuit. For this part, assume = 0 for all devices.

All transistors have nite output impedance, such that

for any transistor, g

m

r

o

= 100. Draw the small signal

equivalent circuit of the amplier. Determine the small

signal gain from v

i

to v

out

and the input and output re-

sistances of the amplier.

10

(10/1)

(40/1)

(40/1)

5 V

1.5M

1M

v

i

M1 M2

M3

|V

Tp

|=0.8V,

p

C

ox

=50/V

2

2.5M

v

out

Figure 2: Problem 2

Determine the amplitude of the largest sinusoid that can

be applied at the input, so that the output is also a sinu-

soid, devoid of clipping effects. As usual, assume that

the coupling capacitors are innite.

Problem 3

The circuit of Fig. 3 shows an amplier.

10

(10/1)

(40/1)

(40/1)

5 V

1.5M

1M

v

i

M1 M2

M3

|V

Tp

|=0.8V,

p

C

ox

=50/V

2

v

out

20K

40K

Figure 3: Problem 3

Determine the operating points of all the devices in the

circuit. For this part, assume = 0 for all devices.

1

EE5310/EE3002: Analog Circuits

Tutorial 5

Due on 21st Oct. 2014

All transistors have nite output impedance, such that

for any transistor, g

m

r

o

= 100. Draw the small signal

equivalent circuit of the amplier. Determine the small

signal gain from v

i

to v

out

and the input and output re-

sistances of the amplier.

Determine the amplitude of the largest sinusoid that can

be applied at the input, so that the output is also a sinu-

soid, devoid of clipping effects. As usual, assume that

the coupling capacitors are innite.

Problem 4

In the circuit of Fig. 4, assume that all devices operate in sat-

uration.

R

Vdd

(4W/L) (W/L)

(W/L) (W/L)

M1 M2

Figure 4: Problem 4

Determine the operating points of all the de-

vices in the circuit. Assume = 0 for all

devices. The answers should be in terms of

|V

TP

|, V

TN

,

n

C

ox

,

p

C

ox

, R, V

dd

&(W/L).

What is the transconductance of M1 ? How does it de-

pend on the device thresholds,

n

C

ox

and

p

C

ox

? What

do you think the practical utility of this circuit is ?

Determine the minimum Vdd required to ensure that all

devices are in saturation.

Problem 5

The circuit of Fig. 5 shows an amplier.

Determine the operating points of all the devices in the

circuit. For this part, assume = 0 for all devices.

All transistors have nite output impedance, such that

for any transistor, g

m

r

o

= 100. Draw the small signal

equivalent circuit of the amplier. Determine the input

and output resistances of the amplier. What kind of

controlled source is this ? Determine the relevant trans-

fer parameter of the source.

10

(10/1)

(100/1)

(100/1)

5 V

v

i

M1 M2

M3

|V

Tp

|=0.8V,

p

C

ox

=50/V

2

v

out

(10/1)

20K

(40/1)

(10/1)

40K

R

in

R

out

V

Tn

=0.7V,

n

C

ox

=200/V

2

Figure 5: Problem 5

Determine the amplitude of the largest sinusoid current

at the input, so that the output is also a sinusoid, devoid

of clipping effects. As usual, assume that the coupling

capacitors are innite.

Problem 6

In the circuit of Fig. 6, determine the voltages at Va and Vb.

Neglect . For the transistors, use same the device parame-

ters as in Problem 1.

100

100/1

100/1

5 V

I

D1

I

D2

100/1

100/1

100/1

Vx

Va

Vb

Figure 6: Problem 6

Assume that = 0. Plot I

D1

and I

D2

in the voltage

source Vx is varied in the range 0-to-V

b

+ |V

TP

|.

Repeat the above for = 0.1 V

1

.

2

For the following problems, use the data below:

n

C

ox

= 300 A/V

2

,

p

C

ox

= 75 A/V

2

, V

Tn

= V

Tp

= 0.6 V;

p

=

n

= k

/L, where k

= 0.12/(Vm)

1.8V

R

G

v

s

R

s

R

G

v

d

v

c

-v

d

i

1

i

2

i

1

i

2

v

1

v

2

(a) (b) (c)

(f) (e) (d)

i

s

Figure 1: Circuits for Problems 7 to 13 (All capacitors are large enough to be shorts at the signal frequency.)

7. Design the inverter (determine the transistor widths) in Fig. 1(a) to have a self bias voltage of 0.9 V and a

quiescent current of 54 A when self biased. Use L = 0.18 m for all transistors. Ignore for operating point

calculations. What is the dc gain of this inverter? (Use this inverter for the rest of the problems).

What aspects of the inverter change if the all transistor lengths are quadrupled?

8. What is the constraint on R

G

such that it doesnt affect the gain of the self biased inverter (Fig. 1(b))? Under

this constraint, what are the maximum and minimum output voltages such that both transistors are in saturation?

9. The two inverters in Fig. 1(c) are identical. R

G

satises the constraint above. What is the quiescent output

voltage? What is the amplitude of the input sinusoid such that the output just reaches the swing limits calculated

above?

10. What additions do you need to make to this circuit so that the small sinusoidal input can be converted to a square,

(almost) digital waveform?

11. Assume that the threshold voltage of the nMOS transistor in the second inverter in Fig. 1(b) differs from the

nominal value by V

Tn

. Find the value of V

Tn

for which the quiescent output voltage is half way towards

the output swing limit.

12. Fig. 1(d, e) show a circuit driven by out of phase and in phase (small) signals. Calculate(symbolically) the

small signal currents i

1

and i

2

in in the two cases. Denote the transconductance and output conductance of each

inverter by g

m

and g

o

respectively. Comment on the magnitude of the currents in the two cases.

13. Based on the above results, calculate the small signal voltages v

1

and v

2

in Fig. 1(f). What might be the utility

of this circuit?

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- DC Circuit Basics ExplainedDocument9 pagesDC Circuit Basics ExplainedtekellamerZ aka tekellamerNo ratings yet

- Short Circuit Coordination Study Arc Flash Hazard Analysis PDFDocument9 pagesShort Circuit Coordination Study Arc Flash Hazard Analysis PDFkaushikray06No ratings yet

- BS7671 Formula and TipsDocument32 pagesBS7671 Formula and TipsjeevanNo ratings yet

- SP 1109 1 Earthing and Bonding (ERD 64 10) 2Document45 pagesSP 1109 1 Earthing and Bonding (ERD 64 10) 2RaghuNo ratings yet

- Exam 2 SolDocument6 pagesExam 2 Soldummy1957jNo ratings yet

- PM Speed Adjusting Motor For PSGDocument2 pagesPM Speed Adjusting Motor For PSGFathima Regin100% (2)

- LabManual Chpt2 PDFDocument8 pagesLabManual Chpt2 PDFdummy1957jNo ratings yet

- LabManual Chpt2 PDFDocument8 pagesLabManual Chpt2 PDFdummy1957jNo ratings yet

- LabManual Chpt2 PDFDocument8 pagesLabManual Chpt2 PDFdummy1957jNo ratings yet

- Multistage Amplifiers: Bipolar Junction Transistor: MosfetDocument16 pagesMultistage Amplifiers: Bipolar Junction Transistor: MosfetRomelDianonNo ratings yet

- Lab 11Document3 pagesLab 11dummy1957jNo ratings yet

- Exam 03 SolutionDocument13 pagesExam 03 Solutiondummy1957jNo ratings yet

- ESE 314 Lab Report GuidelinesDocument1 pageESE 314 Lab Report Guidelinesdummy1957jNo ratings yet

- to obtain V = +2 V for the pnp bipolar junction transistor circuit below. (β = 50)Document6 pagesto obtain V = +2 V for the pnp bipolar junction transistor circuit below. (β = 50)dummy1957jNo ratings yet

- F3Document6 pagesF3dummy1957jNo ratings yet

- Basic Electronics Lec 19 by - Dorat El-EslamDocument2 pagesBasic Electronics Lec 19 by - Dorat El-Eslamdummy1957jNo ratings yet

- How To Install A Data Network in Your House - Martin LaurenceDocument24 pagesHow To Install A Data Network in Your House - Martin LaurencefastreturnNo ratings yet

- Basic Electronics Lec 3 by - Dorat El-EslamDocument5 pagesBasic Electronics Lec 3 by - Dorat El-Eslamdummy1957jNo ratings yet

- Voice PDFDocument100 pagesVoice PDFdummy1957jNo ratings yet

- Exam 1 SolDocument6 pagesExam 1 Soldummy1957jNo ratings yet

- EE5310/EE3002: Analog Circuits Tutorial 1 Problems 6, 8, 10, 11 Are OptionalDocument10 pagesEE5310/EE3002: Analog Circuits Tutorial 1 Problems 6, 8, 10, 11 Are Optionaldummy1957jNo ratings yet

- Ee 3002 Prob 3Document6 pagesEe 3002 Prob 3dummy1957jNo ratings yet

- Basic Electronics Lec 2 by - Dorat El-EslamDocument6 pagesBasic Electronics Lec 2 by - Dorat El-Eslamdummy1957jNo ratings yet

- VoiceDocument22 pagesVoiceAravind GaadirajuNo ratings yet

- Ijertv1is4193 Voice PDFDocument12 pagesIjertv1is4193 Voice PDFdummy1957jNo ratings yet

- Ee 3002 Prob 2Document5 pagesEe 3002 Prob 2dummy1957jNo ratings yet

- Blind Transmitter Turns TVs On/Off from PocketDocument11 pagesBlind Transmitter Turns TVs On/Off from Pocketdummy1957jNo ratings yet

- Fall - Final - Report VOICE2 PDFDocument20 pagesFall - Final - Report VOICE2 PDFdummy1957jNo ratings yet

- CALCULATORDocument23 pagesCALCULATORdummy1957jNo ratings yet

- ClassAB - Bandwidth PDFDocument1 pageClassAB - Bandwidth PDFdummy1957jNo ratings yet

- Class B Output: Jeremy HeersinkDocument10 pagesClass B Output: Jeremy Heersinkdummy1957jNo ratings yet

- Overvoltage Types and CausesDocument5 pagesOvervoltage Types and CausesAsanka RodrigoNo ratings yet

- Dr. Ahmed-Alarashi: Availability of High Voltage Semiconductors Made It Possible To Go For HVDCDocument3 pagesDr. Ahmed-Alarashi: Availability of High Voltage Semiconductors Made It Possible To Go For HVDCAhmedNo ratings yet

- Electrical Flashover Hazards and Safety MeasuresDocument6 pagesElectrical Flashover Hazards and Safety MeasuresAhmad YaseenNo ratings yet

- CS-302 Manual (210324 - 1Document18 pagesCS-302 Manual (210324 - 1arnaldomachadoNo ratings yet

- MT121050 (12V105Ah) : Cyclic Charging Voltage (25°C)Document1 pageMT121050 (12V105Ah) : Cyclic Charging Voltage (25°C)Anderson Ferney Rodriguez JimenezNo ratings yet

- Cable Joints Types - Google SearchDocument1 pageCable Joints Types - Google SearchBright NamsongoleNo ratings yet

- How To Select MCB / MCCB (Part:1) : Electrical Notes & ArticlesDocument4 pagesHow To Select MCB / MCCB (Part:1) : Electrical Notes & ArticlesRitesh SharmaNo ratings yet

- Problem Set Circuits 2Document1 pageProblem Set Circuits 2Vien Ysabel JasaNo ratings yet

- Capacitive Discharge GeneratorsDocument6 pagesCapacitive Discharge Generatorsbarnowl999No ratings yet

- Conductivity Supervision DescriptionDocument3 pagesConductivity Supervision DescriptionMauricio Schmidt MunizNo ratings yet

- Buck ConverterDocument2 pagesBuck ConverterBhadreshkumar SharmaNo ratings yet

- ABBs Disconnecting Circuit BreakersDocument8 pagesABBs Disconnecting Circuit BreakersAndrea AtzeniNo ratings yet

- JucomaticDocument4 pagesJucomaticAurelNo ratings yet

- IHP 1C 18 mm feature upgradesDocument2 pagesIHP 1C 18 mm feature upgradesRodolfoAntonioLeónCárdenasNo ratings yet

- 150KHz, 3A Step Down Voltage Switching Regulators DatasheetDocument10 pages150KHz, 3A Step Down Voltage Switching Regulators DatasheetAlfredo Valencia RodriguezNo ratings yet

- Machine-made nonwoven hexagonal pipesDocument41 pagesMachine-made nonwoven hexagonal pipesCGengineering ConsultantNo ratings yet

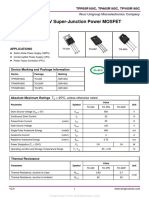

- 650V Super-Junction Power MOSFET: FeaturesDocument9 pages650V Super-Junction Power MOSFET: FeaturesAdalbertoRoque100% (1)

- DDDADDocument1 pageDDDADJevan CalaqueNo ratings yet

- (Final)Document16 pages(Final)saurabhNo ratings yet

- Ec 1 FinalDocument6 pagesEc 1 FinalRaushan RaazNo ratings yet

- ElectronicMechanic (NSQF) 2ndSEMPracticalDocument180 pagesElectronicMechanic (NSQF) 2ndSEMPracticalKhader ManangaNo ratings yet

- Exp 04Document6 pagesExp 04ganga_ch1No ratings yet

- Study of Different Types of Diodes and Their ApplicationsDocument17 pagesStudy of Different Types of Diodes and Their ApplicationsGOVERNMENT POLYTECHNICNo ratings yet

- Banner Fullsize Photo EyesDocument34 pagesBanner Fullsize Photo EyesMemik TylnNo ratings yet

- Tesys Contactors DDocument6 pagesTesys Contactors DJabir QuadriNo ratings yet

- Registered Electrical Workers As at 15th May 2020Document66 pagesRegistered Electrical Workers As at 15th May 2020pius ouna100% (1)