Professional Documents

Culture Documents

Memory Organization

Uploaded by

u110010Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Memory Organization

Uploaded by

u110010Copyright:

Available Formats

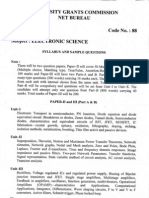

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-1

Chap. 12 Memory Organization

12-1 Memory Hierarchy

Memory hierarchy in a computer system : Fig. 12-1

Main Memory : memory unit that communicates directly with the CPU (RAM)

Auxiliary Memory : device that provide backup storage (Disk Drives)

Cache Memory : special very-high-speed memory to increase the processing

speed (Cache RAM)

Multiprogramming

enable the CPU to process a number of independent program concurrently

Memory Management System : sec. 12-7

supervise the flow of information between auxiliary memory and main memory

Magnetic

tapes

Magnetic

disks

I/O processor

CPU

Main

memory

Cache

memory

Auxiliary memory

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-2

12-2 Main Memory

Bootstrap Loader

A program whose function is to start the computer software operating when

power is turned on

RAM and ROM Chips

Typical RAM chip : Fig. 12-2

128 X 8 RAM : 2

7

=128 (7 bit address lines)

Typical ROM chip : Fig. 12-3

512 X 8 ROM : 2

9

=512 (9 bit address lines)

1288

RAM

CS1

AD7

WR

RD

CS2

Chip select 1

Chip select 2

Read

Write

7 bit address

8 bit data bus

(a) Block diagram

CS1 WR RD CS2 Memory function State of data bus

0

0

0 0

0 0

0 1 1

1

1

1

1

0

1

1

Inhibit

Inhibit

Inhibit

Write

Read

Inhibit

High-impedance

High-impedance

High-impedance

Input data to RAM

Output data from RAM

High-impedance

(b) Function table

5128

ROM

CS1

AD9

CS2

Chip select 1

Chip select 2

9 bit address

8 bit data bus

Power-ON

FFFF:0000

(Reset Point)

POST

System Init.

INT 19

Load Bootstrap Record

(Track 0, Sector 0)

Load Operating System

(IO.SYS, MSDOS.SYS, COMMAND.COM)

Bootstrap Loader

Bootstrap ROM

Boot ROM

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-3

Memory Address Map

Memory Configuration : 512 bytes RAM + 512 bytes ROM

1 x 512 byte ROM + 4 x 128 bytes RAM

Memory Address Map : Tab. 12-1

Address line 9 8

RAM 1 0 0 : 0000 - 007F

RAM 1 0 1 : 0080 - 00FF

RAM 1 1 0 : 0100 - 017F

RAM 1 1 1 : 0180 - 01FF

Address line 10

ROM 1 : 0200 - 03FF

Memory Connection to CPU : Fig. 12-4

2 x 4 Decoder : RAM select (CS1)

Address line 10

RAM select : CS2

ROM select : CS2 Invert

RD : ROM CS1

OE(Output Enable)

1288

RAM 1

CS1

AD7

WR

RD

CS2

1288

RAM 2

CS1

AD7

WR

RD

CS2

1288

RAM 4

CS1

AD7

WR

RD

CS2

1288

RAM 3

CS1

AD7

WR

RD

CS2

1288

ROM

CS1

CS2

AD9

Data

Data

Data

Data

Data

CPU

WR RD 16 - 11 10 9 8 7 - 1

Address bus

Data bus

Decoder

3 2 1 0

1-7

8

9

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-4

12-3 Auxiliary Memory

Magnetic Disk : Fig. 12-5, FDD, HDD

Magnetic Tape : Backup or Program

Optical Disk : CDR, ODD, DVD

12-4 Associative Memory

Content Addressable Memory (CAM)

A memory unit accessed by content

Block Diagram : Fig. 12-6

text text text text

S

e

c

t

o

r

Read/Write

head

Tracks

A Register 101111100

K Register 111000000

Word 1 100 111100 M=0

Word 2 101000011 M=1

Argument register (A)

Key register (K)

Associative memory

array and logic

m words

n bits per word

M

Match

register

Input

Write

Read

Output

Argument

Key (Mask)

Match Logic

Memory

M =1

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-5

mword x n cells per word : Fig. 12-7

Match Logic

One cell of associative memory : Fig. 12-8

Input =1 or 0 Write F/F

A K Match Logic M=1 (MREAD)

Read F/F

A1

C11

An A j

K1 Kn K j

C 1j C1n

C i1 C ij Cin

Cm1 Cmj Cmn

M1

Mm

Mi

Bit 1 Bit n Bit j

Word 1

Word m

Word i

R S

Match

logic

Input

Read

Write

Output

To Mi

K j A i

Fij

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-6

Match Logic : Fig. 12-9

A

j

= Argument, F

ij

= Cell ij bit

j 1 bit match

x

j

= A

j

F

ij

(1 AND 1)+ A

j

F

ij

(0 AND 0)

1 - n n bits match M

i

= x

1

x

2

..x

n

Key bit K

j

: x

j

+K

j

K

j

=0 : A

j

F

ij

no comparison ( K

j

: x

j

+1 =1 )

K

j

=1 : A

j

F

ij

comparison ( K

j

: x

j

+0 = x

j

)

Match Logic for word I :

M

i

= (x

1

+ K

1

) (x

2

+ K

2

). (x

n

+K

n

)

= (x

j

+K

j

)

= (A

j

F

ij

+ A

j

F

ij

+ K

j

)

=

n

j 1

=

n

j 1

F'i1 Fi1

A1 K1

F'i2 Fi2

A2 K2

F'in Fin

An Kn

Mi

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-7

12-5 Cache Memory

Locality of Reference

the references to memory tend to be confined within a few localized areas in

memory

Cache Memory : a fast small memory

keeping the most frequently accessed instructions and data in the fast cache

memory

Cache

cache size : 256 K byte (512 K byte)

mapping method : 1) associative, 2) direct, 3) set-associative

replace algorithm : 1) LRU, 2) LFU, 3) FIFO

write policy : 1) write-through, 2) write-back

Hit Ratio

the ratio of the number of hits divided by the total CPU references (hits + misses)

to memory

hit : the CPU finds the word in the cache (0.9 )

miss : the word is not found in cache (CPU must read main memory)

: cache memory access time = 100 ns, main memory access time = 1000

ns, hit ratio = 0.9

1 miss : 1 x 1000 ns

9 hit : 9 x 100 ns

10

Memory

1900 ns / 10 =190 ns

Cache1000 ns,

5

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-8

Mapping

The transformation of data from main memory to cache memory

1) Associative mapping

2) Direct mapping

3) Set-associative mapping

Example of cache memory : Fig. 12-10

main memory : 32 K x 12 bit word (15 bit address lines)

cache memory : 512 x 12 bit word

CPU sends a 15-bit address to cache

Hit : CPU accepts the 12-bit data from cache

Miss : CPU reads the data from main memory (then data is written to cache)

Associative mapping : Fig. 12-11

Cache memoryassociative memory

Address Data Cache memory

Direct mapping : Fig. 12-12

Cache memorymemory

Tag field (n - k) Index field (k)

2

k

words cache memory + 2

n

words main memory

Tag =6 bit (15 - 9), Index =9 bit

Cache Coherence (Sec. 13-5)

Main memory

32K12

CPU

Cache memory

51212

Argument register

0 1 0 0 0

2 2 3 4 5

0 2 7 7 7

3 4 5 0

1 2 3 4

6 7 1 0

Address Data

CPU address(15 bits)

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-9

Direct mapping cache organization : Fig. 12-13

: 02000

1) Index 000cache

2) Tagcache

3) 000 Indexcache tag00

(02)

4) miss

5) main memorydata read

(address 02000 =5670 read)

32K12

Main memory

Address = 15 bits

Data = 12 bits

Tag Index

6 bits 9 bits

Hex

Address

00 000

3F 1FF

51212

Cache memory

Address = 9 bits

Data = 12 bits

000

1FF

Octal

address

1 2 2 0

2 3 4 0

3 4 5 0

4 5 6 0

5 6 7 0

6 7 1 0

Memory data

Memory

address

000000

02777

02000

01777

01000

00777

00 1 2 2 0

02 6 7 1 0

Tag Data

Index

address

000

777

(a) Main memory

(b) Cache memory

Tag (6 bit)

00 - 63

Index (9 bit)

000 - 511

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-10

Direct mapping cache with block size of 8 words : Fig. 12-14

64 block x 8 word = 512 cache words size

8 word 1block update

Set-associative mapping : Fig. 12-15 (two-way)

Direct mapping ( Fig. 12-13(b))Indextag

( 02777, 01777 )

set.

000

007

010

017

0 1

0 1

770

777

0 2

0 2

3 4 5 0

6 5 7 8

6 7 1 0

Index Tag Data

Block 0

Block 1

Block 63

Tag Block Word

6 3 6

Index

0 1 3 4 5 0 0 2 5 6 7 0

0 2 6 7 1 0 0 0 2 3 4 0

000

777

Index Tag Data Tag Data

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-11

Replacement Algorithm : cache miss or full

1) LRU (Least Recently Used) : block

2) LFU (Least Frequently Used) : block

3) FIFO (First-In First-Out) : block

Writing to Cache : Cache Coherence(Sec. 13-5)

Cache(WRITE) , Cacheblockmain

memoryupdate

1) Write-through : Cache write main memorywrite .

2) Write-back : Cache write flag set

blockflagwrite .

Write-back main memory.

Cache Initialization

Cache is initialized : cache empty invalid data.

1) when power is applied to the computer

2) when main memory is loaded with a complete set of programs from auxiliary memory

valid bit

indicate whether or not the word contains valid data

Main memory Cache memory: ()

Cache READ

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-12

12-6 Virtual Memory

Virtual Memory : Auxiliary memory Main memory

Translate program-generated (Aux. Memory) address into main memory location

Give programmers the illusion that they have a very large memory, even though the

computer actually has a relatively small main memory

: Intel Pentium Processor

Physical Address Lines = A

0

- A

31

: 2

32

= 2

30

X 2

2

=4 Giga

Logical Address = 46 bits address : 2

46

= 2

40

X 2

6

=64 Tera

Address Space & Memory Space

Address Space : Virtual Address

Address used by a programmer

Memory Space : Physical Address(Location)

Address in main memory

: Fig. 12-16

address space (N) = 1024 K = 2

20

Auxiliary Memory

memory space (M) = 32 K = 2

15

main Memory

Program 1

Data 1,1

Data 1,2

Program 2

Data 2,1

Program 1

Data 1,1

Auxiliary memory

Main memory

Address space

N = 1024K =

Memory space

M = 32K = 2

15

2

20

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-13

Memory table for mapping a virtual address : Fig. 12-17

Translate the 20 bits Virtual address into the 15 bits Physical address

Address Mapping Using Pages : Fig. 12-18

Address mapping

Address spacememory spacefixed size

Address space : 1 K page

Memory space : 1 k block

Address space4 page memory space

block.

Virtual

address

register

(20 bits)

Memory

maping

table

Memory table

buffer register

Main memory

address

register

(15 bits)

Main

memory

Main memory

buffer register

Virtual address

Page 0

Page 7

Page 6

Page 5

Page 4

Page 3

Page 2

Page 1

Block 0

Block 3

Block 2

Block 1

Address space

N = 8K = 2

13

Memory space

M = 4K = 2

12

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-14

Memory table in a paged system : Fig. 12-19

1 0 1 0 1 0 1 0 1 0 0 1 1

0

00

11

10

01

1

0

1

10

1

1

10

01 1

000

111

110

101

100

011

010

001

Table

address

Presence

bit

Page no.

Line number

Virtual address

01 0101010011

Block 0

Block 1

Block 2

Block 3

MBR

Main memory

address register

Memory page table

Main memory

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-15

Associative memory page table : Fig. 12-20

Associative memoryblock number(01)

Page(Block) Replacement

Page Fault : the page referenced by the CPU is not in main memory

a new page should be transferred from auxiliary memory to main memory

Replacement algorithm : FIFO LRU

1 0 1 Line number

1 1 1 0 0

0 0 1 1 1

1 1 0 1 0

1 0 1 0 1

0 1 0 0 0

Argument register

Key register

Associative memory

Page no.

Page no. Block no.

Virtual memory

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-16

12-7 Memory Management Hardware

Basic components of a Memory Management Unit

1) Address mapping

2) Common program sharing

3) Program protection

MMU : OS

1) CPU

2) memory controller

Segment

A set of logically related instruction or data elements associated with a given

name

: a subroutine, an array of data, a table of symbol, users program

Logical Address

the address generated by a segmented program

similar to virtual address

Virtual Address : fixed-length page

Logical Address : variable-length segment

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-17

Segmented-page MMU

Fig. 12-21(a) : 2 table(segment, page)

2 table

Fig. 12-21(b) : Associative memory1 table

TLB (Translation Look-a-side Buffer)

associative memorymost recently reference table

Numerical Example

: Logical address & Physical address (Fig. 12-22)

Logical Address :

4 bit segment : 16 segments

8 bit page : 256 pages

8 bit word : 256 address field

Physical Address :

12 bit block : 4096 blocks

8 bit word : 256 address field

(a) Logical address format : 16 segments of 256 pages each,

each page has 256 words

32

Physical memory

2

20

Block Word

12 8

(b) Physical address format : 4096 blocks of 256 word each,

each word has 32 bits

Segment Page Word

4 8 8

Address

or Index

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-18

Page 0

Page 4

Page 3

Page 2

Page 1

Page number

6 00 00

6 00 FF

Hexadecimal

address

Segment Page Block

6

6

6

6

6

00

04

03

02

01

012

A61

053

019

000

(a) Logical address assignment (b) Segment-page versus

memory block assignment

6 01 00

6 01 FF

6 02 00

6 02 FF

6 03 00

6 03 FF

6 04 00

6 04 FF

: Logical & Physical address assignment (Fig. 12-23)

Logical Address

Page Table

Block number 019

Word

Segment

Page

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-19

35

A3

0

6

F

Segment table

012

A61

053

019

000

012

00

35

38

37

36

39

A3

Page table

Block 0

6 02 7E

Logical address (in haxadecimal)

Block 12

32 bit word

Physical memory

000 00

000 FF

012 00

012 FF

019 00

019 FF

019 7E

(a) Segment and page table mapping

6 02 019

6 04 A61

Segment Page Block

(b) Associative memory (TLB)

Segment Page Word

+

Segment table

Page table

Logical address

Block Word

Physical address

(a) Logical to physical address mapping

Segment Page Block

Argument register

(b) Associative memory translation look-aside buffer (TLB)

+

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-20

Memory Protection

Typical segment descriptor : Fig. 12-25

Access Rights : protecting the programs residing in memory

1) Full read and write privileges : no protection

2) Read only : write protection

3) Execute only : program protection

4) System only : operating system protection

Base address Length Protection

segment

Base address

Length

Computer System Architecture

Korea Univ. of Tech. & Edu.

Dept. of Info. & Comm.

Chap. 12 Memory Organization Chap. 12 Memory Organization

12-21

1288

RAM 1

CS1

AD7

WR

RD

CS2

1288

RAM 2

CS1

AD7

WR

RD

CS2

1288

RAM 4

CS1

AD7

WR

RD

CS2

1288

RAM 3

CS1

AD7

WR

RD

CS2

1288

ROM

CS1

CS2

AD9

Data

Data

Data

Data

Data

CPU

WR RD 16 - 11 10 9 8 7 - 1

Address bus

Data bus

Decoder

3 2 1 0

1-7

8

9

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- CSE Digital SyllabusDocument2 pagesCSE Digital Syllabusu110010No ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- ECE Final Upto 4th Year SyllabusDocument42 pagesECE Final Upto 4th Year Syllabusu110010No ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Microprocessor Architecture: Introduction To Microprocessors Chapter 2 1Document47 pagesMicroprocessor Architecture: Introduction To Microprocessors Chapter 2 1harilakNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Ugc Net SyllabusDocument4 pagesUgc Net Syllabus123bala123No ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- FPGADocument4 pagesFPGAu110010No ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Digital ElectronicsDocument51 pagesDigital Electronicsu110010No ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- University of Engineering Management: CE 301 CE 302 CE 303 CH 301Document6 pagesUniversity of Engineering Management: CE 301 CE 302 CE 303 CH 301u110010No ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- IIT/SRIC project proposal letter 2014Document1 pageIIT/SRIC project proposal letter 2014u110010No ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Symo GEN24 Full Backup2Document172 pagesSymo GEN24 Full Backup2Mihai RaduNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- Product Overview: Fully Integrated UWB Transceiver ModuleDocument2 pagesProduct Overview: Fully Integrated UWB Transceiver ModuleHarry LeeNo ratings yet

- Pulsar: Pulse Burst RadarDocument8 pagesPulsar: Pulse Burst RadartungluongNo ratings yet

- Computer ComponetsDocument2 pagesComputer ComponetsIbrahim GullamNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- AU7860A Datasheet: USB Host MP3/WMA Decoder SOCDocument14 pagesAU7860A Datasheet: USB Host MP3/WMA Decoder SOCsdsNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Jntuk M Tech r13 Cad&cam Syllabus PDFDocument60 pagesJntuk M Tech r13 Cad&cam Syllabus PDFLohitha PolisettyNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Wideband Modem ResiliencyDocument18 pagesWideband Modem ResiliencyPanagiotis PapaspyropoulosNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- LG GIS Networking Network Data Admin L2Document4 pagesLG GIS Networking Network Data Admin L2Ashish Kumar JhaNo ratings yet

- Novatek nt96655 Data SheetDocument56 pagesNovatek nt96655 Data Sheetapi-432313169No ratings yet

- 1506706321657Document76 pages1506706321657Aisa HambaliNo ratings yet

- Part I ADocument206 pagesPart I AsenthilkumaranvNo ratings yet

- ABB HMI CP607 Data SheetDocument6 pagesABB HMI CP607 Data SheetRadu BabauNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Digital Telemetry and Automation Solutions For TETRADocument7 pagesDigital Telemetry and Automation Solutions For TETRASyed Fayaz AhmedNo ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- Ac Single PhaseDocument35 pagesAc Single PhaseBerihun EngdaNo ratings yet

- 74 3441Document104 pages74 3441GUZMANNo ratings yet

- CMAX-DM60-CPUSEV53: Electrical SpecificationsDocument3 pagesCMAX-DM60-CPUSEV53: Electrical Specificationsayman sheblNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- System HeghtsDocument54 pagesSystem HeghtsWrEdgarCorderoSzNo ratings yet

- LM5020 100V Current Mode PWM Controller: General Description FeaturesDocument13 pagesLM5020 100V Current Mode PWM Controller: General Description FeaturesAlonso CoradoNo ratings yet

- b8 Digi Anywhereusb Plus DsDocument4 pagesb8 Digi Anywhereusb Plus DsClem CZNo ratings yet

- Biochemistry ES 105Document1 pageBiochemistry ES 105Ko Phyo Wai100% (3)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Argus HR320 PDFDocument2 pagesArgus HR320 PDFfahmi1987No ratings yet

- Input/Line Transformers: Models WMT1A, TL100 & TL600Document2 pagesInput/Line Transformers: Models WMT1A, TL100 & TL600syedhameed uddinNo ratings yet

- Test Data 808nm, Conduction-Cooled Diode Laser Single BarDocument7 pagesTest Data 808nm, Conduction-Cooled Diode Laser Single BarUmar BadshahNo ratings yet

- Footprint Naming Convention - Surface Mount 3749778Document2 pagesFootprint Naming Convention - Surface Mount 3749778jagadees21No ratings yet

- CQY80N/ CQY80NG: Optocoupler, Phototransistor Output, With Base ConnectionDocument11 pagesCQY80N/ CQY80NG: Optocoupler, Phototransistor Output, With Base ConnectionAbdelwhab ElsaftyNo ratings yet

- Fan7382 103101Document17 pagesFan7382 103101Oleksandr ShandurskyiNo ratings yet

- Service Manual: NSX-AJ310 NSX-SZ310 NSX-SZ315 NSX-SZ510Document42 pagesService Manual: NSX-AJ310 NSX-SZ310 NSX-SZ315 NSX-SZ510miguel_olmos_18No ratings yet

- Up Vs Down MEPDocument9 pagesUp Vs Down MEPIngchavaNo ratings yet

- VLSI Interview QuestionsDocument7 pagesVLSI Interview QuestionsVlsi GuruNo ratings yet

- L TDK FerriteDocument54 pagesL TDK FerriteAnonymous vKD3FG6RkNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)