Professional Documents

Culture Documents

Advanced CMOS

Uploaded by

amitgh88Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Advanced CMOS

Uploaded by

amitgh88Copyright:

Available Formats

1

Lecture 1

EE 6346 - Course details

Deleep R. Nair

CSD 318

deleep@ee.iitm.ac.in

Xtn: 4471

2

EE 6346

Advanced CMOS Devices and

Technology

3 credits

E slot

Tuesday 11am

Wednesday 10am

Thursday 10am

Classroom ESB 207B

TA Sarath G.

3

Course objective

To teach the basics of how modern CMOS devices

are designed for better power-performance compared

to previous generation when simple geometric

shrinking no longer works.

Since technology has reached a stage where

assumptions that allowed a total decoupling of circuit

design from process development are no longer

valid, I hope this course would be equally useful for

those who plan to have a career in IC design,

compact modeling or technology development

4

Pre-requisites

[EC 3101 (Solid State Devices) or

EE 5210 (Semiconductor Device

Modeling)] and Consent of Teacher

Knowledge in basic Quantum

mechanics and VLSI technology quite

helpful

5

Student background check

DD(5)/Mtech(4)/MS(1)/PhD(1)

Solid State devices

Semiconductor device modeling

MOS device modeling

VLSI technology

Quantum mechanics/solid state

physics

6

Course content

History of Si technology Review of CMOS scaling. Problems with

traditional geometric scaling Power crisis. Basic quantum mechanics

Mobility enhancement techniques. Review of stress and strain, how it

affects band structure of silicon. Types and realization of stress

elements. Problems with stress elements

Gate oxide scaling trend. Urgency to switch gate dielectric material.

High K material selection. Fermi level pinning Process integration of

high K gate dielectrics and metal gates

Multi-gate transistors. Ways of realization. Fabrication issues and

integration challenges

Ultra shallow junction. Dopant activation methods. Reduction of

parasitic RC

Interconnects

Analog and digital benchmarking of models. Layout dependent effects.

Test structures used for characterization.

Variations and how it can affect scaling.

Basics of sub wavelength lithography. Design for manufacturability

7

Reference Books (No single textbook)

1. Hei Wong , Nano-CMOS Gate Dielectric Engineering, CRC,

2011.

2. J.-P. Colinge, FinFETs and Other Multi-Gate Transistors,

Springer, 2010.

3. S. Deleonibus, Electronic Device Architectures for the Nano-

CMOS Era, Pan Stanford 2009

4. B. Wong, A. Mittal, Y. Cao, G. Starr, Nano-CMOS Circuit and

Physical Design, Wiley Inter-science 2004

5. B. Wong, F. Zach, V. Moroz, A. Mittal, G. Starr, A. Kahng,

Nano-CMOS Design for Manufacturability, Wiley 2009

6. A. Dimoulas, E. Gusev, P. McIntyre, M. Heyns, "Advanced

Gate Stacks for High-Mobility Semiconductors ", Springer 2007

7. Chris Mack, Fundamental Principles of Optical Lithography:

The Science of Microfabrication, Wiley Interscience 2008

8. Review papers provided by me

8

Evaluation pattern

Mid sem (30%)

One seminar/report (15+15%)

End sem (40%)

9

First assignment

Define and distinguish in less than 3 pages

(and 3 page ppt in concise form) what do you

mean/understand

Science, Technology and purpose of education

Return by 13 Aug 2014 (pdf). No weightage will be

carried for final grade.

Plagiarism/copying from peers strictly prohibited

You might also like

- Probability and Random Processes: With Applications to Signal Processing and CommunicationsFrom EverandProbability and Random Processes: With Applications to Signal Processing and CommunicationsRating: 4 out of 5 stars4/5 (1)

- The Finite Element Method: A Practical CourseFrom EverandThe Finite Element Method: A Practical CourseRating: 3.5 out of 5 stars3.5/5 (3)

- Syllabus EXTC Sem 7 Rev. (MU)Document31 pagesSyllabus EXTC Sem 7 Rev. (MU)Anurag RajNo ratings yet

- Silicon On Plastic Full ReportDocument12 pagesSilicon On Plastic Full ReportManjunath Maddy100% (3)

- Microelectronics Group IITBDocument36 pagesMicroelectronics Group IITBkbkkrNo ratings yet

- 01-Intro MEMS History TrendsDocument19 pages01-Intro MEMS History TrendscmosNo ratings yet

- MicroelectronicsDocument39 pagesMicroelectronicsArun Av0% (1)

- Syllabus (ELE 241)Document3 pagesSyllabus (ELE 241)PhoyagerNo ratings yet

- Vlsi CoursefileDocument124 pagesVlsi CoursefileanithaNo ratings yet

- MCESC Structural Engineering and Construction ManagementDocument23 pagesMCESC Structural Engineering and Construction ManagementsonofalexanderNo ratings yet

- Lecture 1 - 4521semiconductor Device Physics Course Outline-2012 SpringDocument17 pagesLecture 1 - 4521semiconductor Device Physics Course Outline-2012 SpringramjidrNo ratings yet

- Vlsi 2014 15 1Document32 pagesVlsi 2014 15 1Rishi JhaNo ratings yet

- Mvlsi 04Document26 pagesMvlsi 04gudiya90_pvNo ratings yet

- EEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Document2 pagesEEE F313 INSTR F313 AnalogandDigitalVLSIDesignFIrstSem 2014 15Harsha DuttaNo ratings yet

- VLSI ModulesDocument28 pagesVLSI Modulessai_karthik89No ratings yet

- Course File - WSNDocument20 pagesCourse File - WSNajaychhotu100% (1)

- Lecture00 UploadDocument13 pagesLecture00 UploadjoeshnaNo ratings yet

- Syllabus EcDocument20 pagesSyllabus Ecrsritusingh23No ratings yet

- Preface: Dr. B. K. SridharaDocument49 pagesPreface: Dr. B. K. SridharaJeevith JeeviNo ratings yet

- 2010 Wang PHDDocument187 pages2010 Wang PHDriturajsrathoreNo ratings yet

- Oster@up EduDocument2 pagesOster@up Edubantids85No ratings yet

- 18-M.Tech (VLSI Design and Embedded System) PDFDocument31 pages18-M.Tech (VLSI Design and Embedded System) PDFAhilan AppathuraiNo ratings yet

- Walling - 463 - Lecture 1Document16 pagesWalling - 463 - Lecture 1Nikunj ShahNo ratings yet

- OutlineDocument1 pageOutlineVarg VikernesNo ratings yet

- Vlsi System DesignDocument29 pagesVlsi System DesignAmar KumarNo ratings yet

- High WayDocument11 pagesHigh Wayمهيمن الابراهيميNo ratings yet

- NIT 1 4 7040 Lecture 1 VLSI EC601Document26 pagesNIT 1 4 7040 Lecture 1 VLSI EC601SANDIP PODDARNo ratings yet

- Bme 354 2014 L1Document21 pagesBme 354 2014 L1Javier Solis0% (1)

- Syllabus 4 Year Ec UPTU 2011-12Document19 pagesSyllabus 4 Year Ec UPTU 2011-12Shubh DixitNo ratings yet

- EE411: Introduction To VLSI Design Course SyllabusDocument9 pagesEE411: Introduction To VLSI Design Course SyllabusSohail MashwaniNo ratings yet

- 453 SyllabusDocument4 pages453 SyllabusPJBNo ratings yet

- ECE 374 TsybeskovDocument2 pagesECE 374 TsybeskovMeryam BakkarNo ratings yet

- CV: Adnan AzizDocument14 pagesCV: Adnan Azizramashankar1hNo ratings yet

- EE 460R - Introduction To VLSIDocument3 pagesEE 460R - Introduction To VLSItrashdnpNo ratings yet

- E&CEDocument143 pagesE&CEkundan1991No ratings yet

- Electrical & Electronic Engineering Program School of Engineering & Information Technology Universiti Malaysia SabahDocument4 pagesElectrical & Electronic Engineering Program School of Engineering & Information Technology Universiti Malaysia Sabahram010No ratings yet

- Bece201l Electronic-Materials-And-Devices TH 1.0 0 Bece201lDocument3 pagesBece201l Electronic-Materials-And-Devices TH 1.0 0 Bece201lkambojnaman2005No ratings yet

- EC NotesDocument2 pagesEC Noteshanumantha12No ratings yet

- EE 360S - Digital Integrated Circuits (Spring 2012, Unique No 16635)Document2 pagesEE 360S - Digital Integrated Circuits (Spring 2012, Unique No 16635)Dildar Khan BhatiNo ratings yet

- CD T Courses 2011Document33 pagesCD T Courses 2011Pranav KalagaNo ratings yet

- Batch-3 First Contact PGMDocument58 pagesBatch-3 First Contact PGMHarold WilsonNo ratings yet

- UG Project Presentation FormatDocument17 pagesUG Project Presentation FormatRajkumar PerumalNo ratings yet

- Mtech Electronics Syllabus VTUDocument48 pagesMtech Electronics Syllabus VTUmuqeetmmaNo ratings yet

- Rajiv Gandhi Technological University, Bhopal (MP) : B.E. (CE) Civil EngineeringDocument15 pagesRajiv Gandhi Technological University, Bhopal (MP) : B.E. (CE) Civil EngineeringpdchaurasiaNo ratings yet

- As A Scientific Pursuit, The Search For A ViableDocument7 pagesAs A Scientific Pursuit, The Search For A ViableWajahat Ali KhanNo ratings yet

- Ementa Elec2104Document5 pagesEmenta Elec2104David AlmeidaNo ratings yet

- Vlsi 2011Document36 pagesVlsi 2011SriramNo ratings yet

- Applied Physics: AUIC-Fall 2020Document10 pagesApplied Physics: AUIC-Fall 2020Its KnowledgeNo ratings yet

- VLSI M.Tech SyllabusDocument14 pagesVLSI M.Tech SyllabusdannycbsNo ratings yet

- Digital Electronics and CommunicationDocument25 pagesDigital Electronics and CommunicationShreyasKamatNo ratings yet

- Course Syllabus 666Document2 pagesCourse Syllabus 666AsraNo ratings yet

- Signature of The Chairman BOS M.E (AE) : KCT-M.E (AE) - I To IV Semester Curriculum and Syllabus R - 2009Document48 pagesSignature of The Chairman BOS M.E (AE) : KCT-M.E (AE) - I To IV Semester Curriculum and Syllabus R - 2009vickyskarthikNo ratings yet

- Ee 310 SyllabusDocument2 pagesEe 310 SyllabusAshwin K ShettyNo ratings yet

- Ulsi DevicesDocument732 pagesUlsi Devicesashutoshsachan80% (5)

- ABET SYLLABUS4 Digital ICDocument3 pagesABET SYLLABUS4 Digital ICHobe NakiNo ratings yet

- EE-112 Solid State Electronics PDFDocument3 pagesEE-112 Solid State Electronics PDFMohammed Ahmad Osama0% (1)

- ResumeDocument3 pagesResumeSaad OmarNo ratings yet

- Semester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)Document19 pagesSemester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)Sneha NargundkarNo ratings yet

- Lec24 Edited PDFDocument13 pagesLec24 Edited PDFamitgh88No ratings yet

- Antennas Course Outline 16aug2016Document24 pagesAntennas Course Outline 16aug2016Ronak05No ratings yet

- Lec37-Edited by Amit GhoshDocument11 pagesLec37-Edited by Amit Ghoshamitgh88No ratings yet

- Lec24 Edited PDFDocument13 pagesLec24 Edited PDFamitgh88No ratings yet

- CP Msa PDFDocument21 pagesCP Msa PDFamitgh88No ratings yet

- Fundamentals of Antennas: Week 1 AssignmentDocument2 pagesFundamentals of Antennas: Week 1 Assignmentayan sahaNo ratings yet

- MSA Array PDFDocument24 pagesMSA Array PDFamitgh88No ratings yet

- The Monte Carlo Methods in Atmospheric OpticsDocument2 pagesThe Monte Carlo Methods in Atmospheric Opticsamitgh88No ratings yet

- Introduction To ResearchDocument158 pagesIntroduction To Researchamitgh88No ratings yet

- Circularly Polarized Microstrip Antennas: Prof. Girish KumarDocument21 pagesCircularly Polarized Microstrip Antennas: Prof. Girish Kumaramitgh88No ratings yet

- Microstrip Antenna Arrays: Prof. Girish KumarDocument24 pagesMicrostrip Antenna Arrays: Prof. Girish Kumaramitgh88No ratings yet

- Tuneable and Dual-Band Msas: Prof. Girish KumarDocument11 pagesTuneable and Dual-Band Msas: Prof. Girish Kumaramitgh88No ratings yet

- Week 10 Horn Antennas Part 2 PDFDocument12 pagesWeek 10 Horn Antennas Part 2 PDFamitgh88No ratings yet

- Mock Test 1 - CBSEDocument2 pagesMock Test 1 - CBSEamitgh88No ratings yet

- Network TopologyDocument30 pagesNetwork Topologyamitgh88No ratings yet

- Introduction To Digital CircuitsDocument1 pageIntroduction To Digital Circuitsamitgh88No ratings yet

- CEM Assignment1Document3 pagesCEM Assignment1amitgh88No ratings yet

- Amit Exp2Document5 pagesAmit Exp2amitgh88No ratings yet

- VlsiDocument30 pagesVlsiJanani MunisamyNo ratings yet

- Vlsi Technology Lec2Document30 pagesVlsi Technology Lec2amitgh88No ratings yet

- Tutorial 1 Intro To PhotonicsDocument4 pagesTutorial 1 Intro To Photonicsamitgh88No ratings yet

- Potential & Potential Energy: Potential of A Charge DistributionDocument9 pagesPotential & Potential Energy: Potential of A Charge Distributionamitgh88No ratings yet

- Frequency Domain Complex Permittivity Measurements at Microwave FrequenciesDocument16 pagesFrequency Domain Complex Permittivity Measurements at Microwave Frequenciesamitgh88No ratings yet

- Free and Confined ElectronsDocument15 pagesFree and Confined Electronsamitgh88No ratings yet

- Quantum Mechanics of ElectronDocument46 pagesQuantum Mechanics of Electronamitgh88No ratings yet

- Equilibrium and Carrier ConcentrationDocument19 pagesEquilibrium and Carrier Concentrationamitgh88No ratings yet

- VlsiDocument30 pagesVlsiJanani MunisamyNo ratings yet

- Optical Characterization of Silica Based Waveguide Prepared by Plasma Enhanced Chemical Vapor DepositionDocument5 pagesOptical Characterization of Silica Based Waveguide Prepared by Plasma Enhanced Chemical Vapor Depositionamitgh88No ratings yet

- Chapter5 Part1 PDFDocument12 pagesChapter5 Part1 PDFamitgh88No ratings yet

- Classical and Quantum ParticlesDocument3 pagesClassical and Quantum Particlesamitgh88No ratings yet

- Assignment Questions ECE VLSI NITTDocument6 pagesAssignment Questions ECE VLSI NITTAkhilGovindNo ratings yet

- L 19 - Mse628a - 30 10 19Document25 pagesL 19 - Mse628a - 30 10 19Dhanishtha SinghNo ratings yet

- U 3Document13 pagesU 3Maheshwar Reddy100% (1)

- VLSI Design Questions and Answers - SanfoundryDocument8 pagesVLSI Design Questions and Answers - SanfoundryJustina FloretNo ratings yet

- IRF MOSFET Power TransistorsDocument1 pageIRF MOSFET Power TransistorsDAVE.A.H. SIGINo ratings yet

- Module 3Document25 pagesModule 3Sushanth M100% (3)

- Footprint Naming Convention - Surface Mount 3749778Document2 pagesFootprint Naming Convention - Surface Mount 3749778jagadees21No ratings yet

- Study The Characteristics of Silicon Controlled Rectifier (SCR)Document8 pagesStudy The Characteristics of Silicon Controlled Rectifier (SCR)Khan ElmeNo ratings yet

- Sp3000udevice PDFDocument475 pagesSp3000udevice PDFElias Herrera gutierrezNo ratings yet

- MikrotikDocument5 pagesMikrotikPrem KumarNo ratings yet

- Toshiba OptocouplersDocument80 pagesToshiba OptocouplersNOEL VELASQUEZNo ratings yet

- Electronic Devices and CircuitsDocument3 pagesElectronic Devices and Circuitsrohitkumar2022rohitkumarNo ratings yet

- Tip 41Document3 pagesTip 41rendy pradanaNo ratings yet

- DICD Tutorial 5Document5 pagesDICD Tutorial 5Pavika Sharma100% (1)

- Gujarat Technological University Bachelor of Engineering Subject Code: 3110016 Basic Electronics 1 YearDocument3 pagesGujarat Technological University Bachelor of Engineering Subject Code: 3110016 Basic Electronics 1 YearGeopolitics PostNo ratings yet

- EdcDocument191 pagesEdcMurugan BalakrishnanNo ratings yet

- Selecting The Best JFET For Your Application: Application Known: Turn To "Choose The Proper FET" andDocument53 pagesSelecting The Best JFET For Your Application: Application Known: Turn To "Choose The Proper FET" andMaciej KlimkiewiczNo ratings yet

- Low Power Bipolar Transistors: BC107 / BC108 SeriesDocument3 pagesLow Power Bipolar Transistors: BC107 / BC108 Seriesioan jeanNo ratings yet

- MosfetDocument4 pagesMosfetKunal SinghNo ratings yet

- CMOS Layout and Design RulesDocument28 pagesCMOS Layout and Design RulesMohamed Mohamed67% (3)

- System Plus Consulting USDocument4 pagesSystem Plus Consulting USRaghu GowdaNo ratings yet

- IXYS ICD ProductCatalog 2019Document48 pagesIXYS ICD ProductCatalog 2019PhilippNo ratings yet

- Mosfet ScalingDocument18 pagesMosfet ScalingRakeshNo ratings yet

- Uln2003d in SMDDocument7 pagesUln2003d in SMDAkylbek KasymovNo ratings yet

- B1132 Sot-89Document4 pagesB1132 Sot-89freddyNo ratings yet

- Datasheet Xl1225Document3 pagesDatasheet Xl1225Nicolae CiuraruNo ratings yet

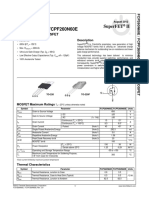

- Superfet Ii Fcp260N60E / Fcpf260N60E: 600V N-Channel MosfetDocument10 pagesSuperfet Ii Fcp260N60E / Fcpf260N60E: 600V N-Channel MosfetAlexandros BobNo ratings yet

- A CMOS-integrated Compute-In-Memory MacroDocument10 pagesA CMOS-integrated Compute-In-Memory MacroMo SongNo ratings yet

- 1.characteristics of SCRDocument6 pages1.characteristics of SCRVenkat Sai ChowdaryNo ratings yet