Professional Documents

Culture Documents

Lab 2 PN JFET Characteristics 2 1112

Uploaded by

Mei Guan0 ratings0% found this document useful (0 votes)

84 views8 pagesJFET

Original Title

Lab 2 Pn JFET Characteristics 2 1112

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentJFET

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

84 views8 pagesLab 2 PN JFET Characteristics 2 1112

Uploaded by

Mei GuanJFET

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 8

COURSE CODE: EXPERIMENT NO: 2

COURSE INSTRUCTOR: DATE:

TITLE: MARKS

OBJECTIVE:

PRELAB :

1 /2

2 /3

/ 5

EXPERIMENT RESULT:

Table 2-1 /4

Table 2-2 /1

/ 5

POST LAB:

1 /3

2 /2

3 /3

4 /1

/ 9

CONCLUSION: / 1

INSTRUCTOR COMMENTS: TOTAL

/ 20

UNIVERSITI TENAGA NASIONAL

Dept of Electronics and Communication Engineering

College of Engineering

EEEB141

pn JFET Characteristics

The objectives of this laboratory experiment is to study the characteristics related to pn JFETs

Semester: 2 Academic Year: 2011 / 2012

TIME:

STUDENT NAME: STUDENT ID:

SECTION:

WORKBENCH NO:

GROUP MEMBER: STUDENT ID:

EEEB141 ELECTRONICS DESIGN LAB, Lab 2

1

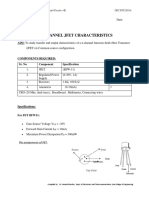

LAB 2 PN JUNCTION FIELD EFFECT TRANSISTOR (JFET)

CHARACTERISTICS

LEARNING OBJECTIVES

By the end of this experiment, you should be able to:

1. Determine the effect of drain-to-source voltage V

DS

on drain current I

D

and reverse

gate-to-source bias voltage V

GS

.

2. Determine and plot the family of drain characteristics of a pn JFET.

3. Determine and plot a pn JFET transfer curve.

MATERIALS

Transistor: 1 2N3819 (JFET)

EQUIPMENT

Tektronix PS280 DC Power Supply

Fluke 45 Dual Display Multimeter

PRE-LAB ASSIGNMENT

1. Draw the cross section area of an n-channel pn JFET. Label

the source, drain, gate,

and depletion regions.

2. Describe the relationship between the drain current, I

D

and the depletion region

(space-charge region) as the gate to source voltage, V

GS

is varied. Draw the

appropriate figures.

EEEB141 ELECTRONICS DESIGN LAB, Lab 2

2

BACKGROUND

There are two principle types of transistors, which are the bipolar junction transistors (BJTs)

and Field Effect Transistors (FETs). In this experiment however, we will limit the study to

FETs (particularly pn JFETs) and BJTs will be discussed in the next experiments.

A FET is a straight forward device. The basic idea of a FET is to control the charge density

of a channel by means of a bias controlled electric field. To minimize the leakage current of

the input signal, the bias voltage is connected to a contact that is isolated from the channel,

named a gate. Two types of FETs are the Metal-Oxide-Semiconductor FET (MOSFET) and

Junction FET (JFET).

Two general categories of JFETs are the pn JFET and the Metal-Semiconductor FET

(MESFET). pn-JFET utilizes a pn-junction for the gate isolation, while MESFET utilizes

Schottky barrier. Typical transistors have three leads, and in case of JFETs, a voltage on one

lead (called the gate) is used to control a current between two other leads (called drain and

source). The figure below illustrated the circuit symbol of n-channel and p-channel JFET

where G, D and S refers to gate, drain and source, respectively.

n-channel p-channel

IN-LAB ACTIVITIES

Gate Short-Circuited To Source

1. Construct the circuit as shown in Figure 3-1.

Figure 2-1: Gate short-circuited to source circuit

D

G

S

I

D

V

DS

+

-

+

V

GS

-

S

G

D

+

V

GS

-

V

SD

+

-

I

D

EEEB141 ELECTRONICS DESIGN LAB, Lab 2

3

2. Set V

DD

= 0.0V. Note that V

DD

= V

DS

. Measure and record the drain current I

D

for

V

DS

= 0V, and V

GS

= 0V.

3. Increase V

DD

to 1.0V. By using the DMM, measure and record I

D

for V

DS

= 1.0V,

and V

GS

= 0V.

4. Repeat for each value of V

DS

as listed in Table 2-1.

5. Reset V

DD

to zero, and POWER OFF.

Gate Is Reverse-Biased

6. Remove the short circuit between the gate and the source and connect voltage source

V

GG

as shown in Figure 2-2.

Figure 2-2: Reverse-biased gate circuit

7. Set V

GG

= -0.2V (note: V

GG

= V

GS

), at V

DD

= V

DS

= 0V. Measure and record the

drain current I

D

.

8. Maintain V

GG

at -0.2V. Repeat step 7, for each value of V

DS

as listed in Table 2-1.

9. Reset all the voltage sources back to zero.

10. Repeat for each value of V

GS

and V

DS

listed in Table 2-1.

11. Reset all the voltage sources back to zero and POWER OFF.

Transfer Characteristic

12. Set V

DD

= 15V, and V

GG

= -2.5V. Measure and record the drain current I

D

.

13. Repeat step 12 for each value of V

GS

listed in Table 2-2, at V

DD

= 15V.

EEEB141 ELECTRONICS DESIGN LAB, Lab 2

4

RESULTS

V

GS

(V)

0 -0.2 -0.5 -0.8 -1.0 -1.2 -1.5 -1.8 -2.0 -2.5

V

DS

(V) I

D

(mA)

0.0

1.0

2.0

3.0

4.0

5.0

6.0

7.0

8.0

9.0

10.0

11.0

12.0

13.0

14.0

15.0

Table 2-1

V

GS

(V) -2.5 -2.0 -1.8 -1.5 -1.2 -1.0 -0.8 -0.5 -0.2 0

I

D

(mA)

Table 2-2

EEEB141 ELECTRONICS DESIGN LAB, Lab 2

5

POST LAB DISCUSSIONS

1. Plot drain characteristics graph (I

D

(mA) versus V

DS

(V)) for this JFET (all V

GS

in one

graph).

2. Describe the characteristic curve by its V

GS

value. Is it what you expected?

3. Plot a transfer characteristic graph (I

D

(mA) versus V

GS

(V)) for this JFET.

4. Identify V

P

(pinch-off voltage) and I

DSS

(saturation current) in the graph of question 3.

(V

P

= V

GS

, when I

D

= 0mA. I

DSS

= I

D

, when V

GS

= 0V)

STUDENTS CONCLUSION

Free Plain Graph Paper from http://incompetech.com/graphpaper/plain/

Free Plain Graph Paper from http://incompetech.com/graphpaper/plain/

You might also like

- EXP10 JFET Transistor CharacteristicsDocument5 pagesEXP10 JFET Transistor CharacteristicsMohammed Dyhia Ali100% (2)

- Implement Dijkstra's AlgorithmDocument4 pagesImplement Dijkstra's AlgorithmSharad KumbharanaNo ratings yet

- Newtons RingsDocument7 pagesNewtons RingsNaziaNo ratings yet

- 0556 Boolean Algebra and Logic SimplificationDocument6 pages0556 Boolean Algebra and Logic SimplificationmasandiganNo ratings yet

- AmmeterDocument28 pagesAmmeterCleider Rey MujeresNo ratings yet

- AmpereDocument28 pagesAmpereJaneth de JuanNo ratings yet

- Interference Theory NotesDocument8 pagesInterference Theory NotessukanyagggNo ratings yet

- Data SourcesDocument3 pagesData SourcesRajeshNo ratings yet

- Communication Skills: - Training TopicsDocument14 pagesCommunication Skills: - Training TopicsHafizan Abdul WahabNo ratings yet

- Boolean AlgebraDocument31 pagesBoolean AlgebraAlee ChauDhriNo ratings yet

- French-English Glossary: Ministry of Territorial Administration and DecentralisationDocument31 pagesFrench-English Glossary: Ministry of Territorial Administration and DecentralisationRaphael RodrigueNo ratings yet

- Machine Learning Types, Applications, and ImportanceDocument19 pagesMachine Learning Types, Applications, and Importancesupriya mishraNo ratings yet

- Emails #10Document3 pagesEmails #10inforumdocsNo ratings yet

- George Boole in 1980 Invented A Different Kind of Algebra Based On Binary Nature at TheDocument26 pagesGeorge Boole in 1980 Invented A Different Kind of Algebra Based On Binary Nature at Theritesh chauhanNo ratings yet

- Lube Oil System in Turbine - Instrumentation BasicsDocument5 pagesLube Oil System in Turbine - Instrumentation BasicsWren DsilvaNo ratings yet

- Franck HertzDocument3 pagesFranck HertzHus-PhycsNo ratings yet

- Business Corrigé Provides BTS Exam SolutionsDocument6 pagesBusiness Corrigé Provides BTS Exam SolutionsmichelNo ratings yet

- Dijkstra's Shortest Path Algorithm Serial and Parallel Execution Performance AnalysisDocument5 pagesDijkstra's Shortest Path Algorithm Serial and Parallel Execution Performance AnalysisMircea TrifanNo ratings yet

- Smart Grid RPDocument61 pagesSmart Grid RPMuhammad HamzaNo ratings yet

- E MailDocument4 pagesE MailSam NickelsonNo ratings yet

- Operating System ReportDocument48 pagesOperating System ReportSyed TahaNo ratings yet

- MGMAT SC SUMMARY Final UnderlinedDocument29 pagesMGMAT SC SUMMARY Final UnderlinedMANOUJ GOELNo ratings yet

- Interview TipsDocument28 pagesInterview TipssuchipatelNo ratings yet

- Lexical Analysis: Risul Islam RaselDocument148 pagesLexical Analysis: Risul Islam RaselRisul Islam RaselNo ratings yet

- About Smart GridDocument38 pagesAbout Smart GridGhayas Ud-din DarNo ratings yet

- Foreign Policy of BangladeshDocument27 pagesForeign Policy of BangladeshTapuNo ratings yet

- BJT Common Base Amplifier: Characteristics & AnalysisDocument7 pagesBJT Common Base Amplifier: Characteristics & AnalysisJules Nikko Dela CruzNo ratings yet

- BD ChinaDocument25 pagesBD ChinaBishawnath RoyNo ratings yet

- Keywords in PythonDocument18 pagesKeywords in PythonAbhinav AnshumanNo ratings yet

- Zener Diode DescriptionDocument9 pagesZener Diode Descriptionshaik jilanNo ratings yet

- Magoosh - SC NotesDocument229 pagesMagoosh - SC Notesjingfeng huangNo ratings yet

- IT Support Engineer - Job DescriptionDocument2 pagesIT Support Engineer - Job DescriptionKhanjee KhanNo ratings yet

- MODULE 2 CommunicationDocument3 pagesMODULE 2 CommunicationShefin KalathilNo ratings yet

- Syntax Analyzer: Features of YACCDocument5 pagesSyntax Analyzer: Features of YACCBaba SravanNo ratings yet

- Report Writing Tip SheetDocument3 pagesReport Writing Tip SheetDr_M_SolimanNo ratings yet

- Data Structures CourseDocument3 pagesData Structures CoursehaseenaNo ratings yet

- Fet Characteristics: ObjectDocument5 pagesFet Characteristics: ObjectpankajmadhuNo ratings yet

- Mosfet Lab 1Document11 pagesMosfet Lab 1Pramod SnkrNo ratings yet

- Center For Advanced Studies in Engineering, Islamabad Electronics LabDocument9 pagesCenter For Advanced Studies in Engineering, Islamabad Electronics LabHussain HadiNo ratings yet

- Basic Electronics PracticalDocument9 pagesBasic Electronics Practicalasfadare100% (2)

- Center For Advanced Studies in Engineering, Islamabad Electronics LabDocument7 pagesCenter For Advanced Studies in Engineering, Islamabad Electronics LabHussain HadiNo ratings yet

- App. Electronics Exp#6Document7 pagesApp. Electronics Exp#6muazam aliNo ratings yet

- Expt 13 - JFET-CharaceristicsDocument8 pagesExpt 13 - JFET-CharaceristicssamarthNo ratings yet

- FET Amplifier: ECE20L-2Document10 pagesFET Amplifier: ECE20L-2Luch ÜNo ratings yet

- L #5: Mosfet C A: Sfsu - E 301 - E L AB Haracteristics and PplicationsDocument14 pagesL #5: Mosfet C A: Sfsu - E 301 - E L AB Haracteristics and PplicationsRudra MishraNo ratings yet

- Expt - 11: JFET CharacteristicsDocument8 pagesExpt - 11: JFET CharacteristicssamarthNo ratings yet

- Design and Analysis of 2N4416 N Channel JFET Single Stage Amplifier For Large Bandwidth and Low Voltage GainDocument9 pagesDesign and Analysis of 2N4416 N Channel JFET Single Stage Amplifier For Large Bandwidth and Low Voltage GainEditor IjasreNo ratings yet

- Lab 3 Clipping and Clamping Circuits 2 1112Document10 pagesLab 3 Clipping and Clamping Circuits 2 1112Mei GuanNo ratings yet

- Eec 234Document45 pagesEec 234Emmanuel100% (1)

- JFET Characteristics Lab GuideDocument22 pagesJFET Characteristics Lab GuideAnsar AnsarNo ratings yet

- Fundamentals of Electrical Engineering 4 Lab 4 - MOSFET AmplifierDocument22 pagesFundamentals of Electrical Engineering 4 Lab 4 - MOSFET AmplifierGerson SantosNo ratings yet

- Lab 2 - Diode CharacteristicsDocument7 pagesLab 2 - Diode CharacteristicsFasil EndalamawNo ratings yet

- Lab Viii. Low Frequency Characteristics of Junction Field Effect TransistorsDocument6 pagesLab Viii. Low Frequency Characteristics of Junction Field Effect Transistorssachinshetty001No ratings yet

- 08ece Ee331 Group 6 Le Van Hai Lab3Document19 pages08ece Ee331 Group 6 Le Van Hai Lab3Quốc HiếuNo ratings yet

- Chapter 4 - JFET PDFDocument13 pagesChapter 4 - JFET PDFnelsonjnelsonjNo ratings yet

- ENGG*3450 Lab Manual MOSFET CharacteristicsDocument12 pagesENGG*3450 Lab Manual MOSFET Characteristicsdlat94No ratings yet

- Lab9 F12Document6 pagesLab9 F12dopesrinathNo ratings yet

- Ef Lab 4Document12 pagesEf Lab 4thevand11No ratings yet

- Analog Electronics Experiment: Field Effect Transistor (FET)Document10 pagesAnalog Electronics Experiment: Field Effect Transistor (FET)Ahmed SalehNo ratings yet

- Periodic Maintenance Schedule Ranger 2.2 AT 4X2Document1 pagePeriodic Maintenance Schedule Ranger 2.2 AT 4X2Mei GuanNo ratings yet

- RRRRDocument1 pageRRRRMei GuanNo ratings yet

- Keep Life Simple2Document5 pagesKeep Life Simple2Mei GuanNo ratings yet

- Numerical Methods Semester ProjectDocument6 pagesNumerical Methods Semester ProjectMei GuanNo ratings yet

- Numeg AssignmentDocument1 pageNumeg AssignmentMei GuanNo ratings yet

- NumecDocument12 pagesNumecMei QiiNo ratings yet

- NumecDocument12 pagesNumecMei QiiNo ratings yet

- FunctionsDocument3 pagesFunctionsMei GuanNo ratings yet

- Every Moment MattersDocument1 pageEvery Moment MattersMei GuanNo ratings yet

- Numeg AssignmentDocument1 pageNumeg AssignmentMei GuanNo ratings yet

- Comparing volumes of two cylinders using calculationsDocument6 pagesComparing volumes of two cylinders using calculationsMei GuanNo ratings yet

- Kelantan Math K2 PDFDocument24 pagesKelantan Math K2 PDFMei GuanNo ratings yet

- MATLAB Code to Calculate Matrix DeterminantDocument2 pagesMATLAB Code to Calculate Matrix DeterminantMei QiiNo ratings yet

- Letter From KPKTDocument1 pageLetter From KPKTMei GuanNo ratings yet

- Numeg AssignmentDocument1 pageNumeg AssignmentMei GuanNo ratings yet

- Project 2Document5 pagesProject 2Mei GuanNo ratings yet

- Lab 3 Clipping and Clamping Circuits 2 1112Document10 pagesLab 3 Clipping and Clamping Circuits 2 1112Mei GuanNo ratings yet

- Travel Itinerary Kuala Lumpur to Bangkok Flight DetailsDocument2 pagesTravel Itinerary Kuala Lumpur to Bangkok Flight DetailsMei GuanNo ratings yet

- Lab 4 BJT-DC Biasing 1 1112Document10 pagesLab 4 BJT-DC Biasing 1 1112Mei GuanNo ratings yet

- Lab6 Function Pt1 CSEB114 Sem2 20112012.Document5 pagesLab6 Function Pt1 CSEB114 Sem2 20112012.Mei GuanNo ratings yet

- Lab 1 Silicone and Zener Diodes Characteristics v2!2!1112Document12 pagesLab 1 Silicone and Zener Diodes Characteristics v2!2!1112Mei GuanNo ratings yet

- Lab 4 BJT-DC Biasing 1 1112Document10 pagesLab 4 BJT-DC Biasing 1 1112Mei GuanNo ratings yet

- Lab4 - CondOp - CSEB114 - Sem2 20112012Document3 pagesLab4 - CondOp - CSEB114 - Sem2 20112012Mei GuanNo ratings yet

- Lab5 RepStruct CSEB114 Sem2 20112012.Document4 pagesLab5 RepStruct CSEB114 Sem2 20112012.Mei GuanNo ratings yet

- Chapter11 FileProcessingDocument22 pagesChapter11 FileProcessingMei GuanNo ratings yet

- Lab 1-Getting Started With VC2005Document13 pagesLab 1-Getting Started With VC2005Mei GuanNo ratings yet

- Lab3 OperatorsExpression CSEB114 Sem2 20112012Document3 pagesLab3 OperatorsExpression CSEB114 Sem2 20112012Mei GuanNo ratings yet

- Lab2 BasicIO CSEB114 Sem2 20112012Document4 pagesLab2 BasicIO CSEB114 Sem2 20112012Mei GuanNo ratings yet

- Chapter10 CharacStringDocument37 pagesChapter10 CharacStringMei GuanNo ratings yet

- Cadence Virtuoso layout of minimum size CMOS inverterDocument11 pagesCadence Virtuoso layout of minimum size CMOS inverterNavid Anjum AaditNo ratings yet

- 2N6034 2N6035 2N6036 PNP 2N6037 2N6038 2N6039 NPN Complementary Silicon Darlington Power Transistors DescriptionDocument4 pages2N6034 2N6035 2N6036 PNP 2N6037 2N6038 2N6039 NPN Complementary Silicon Darlington Power Transistors DescriptionVíctor LaraNo ratings yet

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsDocument132 pagesSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsRAAJ KISHOR R HNo ratings yet

- CHARLIE's Thomas Vox ReplacementsDocument7 pagesCHARLIE's Thomas Vox ReplacementsBDNo ratings yet

- BLDC Motor Controller: V - SupplyDocument7 pagesBLDC Motor Controller: V - SupplyFatihNo ratings yet

- CMOS FabricationDocument38 pagesCMOS FabricationPrajeeth Babu KodruNo ratings yet

- Annex 1 SMD Board 100pDocument9 pagesAnnex 1 SMD Board 100pCatalin BadeaNo ratings yet

- BJT BasicsDocument19 pagesBJT BasicsAman SrivastavNo ratings yet

- TriacDocument13 pagesTriacNaveedNo ratings yet

- Sri Venkateshwara College of Engineering: Usn: 1 V E IA Test-IDocument1 pageSri Venkateshwara College of Engineering: Usn: 1 V E IA Test-Ijaya sreeNo ratings yet

- Type 2N3866A: Geometry Polarity NPN Qual Level: JAN - JANS REF: MIL-PRF-19500/398Document2 pagesType 2N3866A: Geometry Polarity NPN Qual Level: JAN - JANS REF: MIL-PRF-19500/398JavierYancbNo ratings yet

- Chap 3 and 5Document156 pagesChap 3 and 5Richell Mark MiguelNo ratings yet

- BJT Circuit AnalysisDocument24 pagesBJT Circuit AnalysisOssama BohamdNo ratings yet

- Transistor: Robert L. Boylestad and Louis NashelskyDocument23 pagesTransistor: Robert L. Boylestad and Louis NashelskyRafael PeluzioNo ratings yet

- Vlsi Unit-IDocument45 pagesVlsi Unit-Isuneelanubolu7No ratings yet

- Microwave and RF Design V-Amplifiers and Oscillators-SteerDocument209 pagesMicrowave and RF Design V-Amplifiers and Oscillators-SteersystemlocNo ratings yet

- Symbols of Transistors MOSFET and IGFET: Go To WebsiteDocument2 pagesSymbols of Transistors MOSFET and IGFET: Go To Websitemhs madiunNo ratings yet

- tpc8107 26791973Document59 pagestpc8107 26791973Richard BaidooNo ratings yet

- Lists of TransistorsDocument1 pageLists of TransistorsJohn Joshua MontañezNo ratings yet

- Power ElectronicDocument10 pagesPower Electronickalyan mondalNo ratings yet

- Advantages and Disadvantages of BJTs and MOSFETsDocument3 pagesAdvantages and Disadvantages of BJTs and MOSFETscuongspvl2713No ratings yet

- Low Power VLSI Circuits & Systems Complete NotesDocument66 pagesLow Power VLSI Circuits & Systems Complete NotesSai SreejaNo ratings yet

- Cascode Current MirrorDocument19 pagesCascode Current MirrorReshbha Munjal0% (1)

- MultivibratorDocument10 pagesMultivibratorakhilarajNo ratings yet

- Common Base TransistorDocument12 pagesCommon Base TransistorAliza TariqNo ratings yet

- N-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataNixon MaldonadoNo ratings yet

- 5 NMDocument4 pages5 NMPiyush AmbulgekarNo ratings yet

- Field-Effect Transistors: Dr. Talal SkaikDocument18 pagesField-Effect Transistors: Dr. Talal SkaikFrancisNo ratings yet

- 3-PPT MosfetDocument28 pages3-PPT MosfetVaibhavNo ratings yet

- FQP 70 N 10Document8 pagesFQP 70 N 10Rahmat Destia HidayantoNo ratings yet