Professional Documents

Culture Documents

The Digital Logic Level

Uploaded by

sekkozerOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

The Digital Logic Level

Uploaded by

sekkozerCopyright:

Available Formats

1

1

The Digital Logic Level The Digital Logic Level

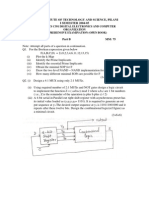

Computer System Organization

Tb. Maulana Kusuma Week 2

Sarjana Magister Program

2

Gates and Boolean Algebra (1)

(a) A transistor inverter.

(b) A NAND gate.

(c) A NOR gate.

2

3

Gates and Boolean Algebra (2)

The symbols and functional behavior for the five basic gates.

4

Boolean Algebra

(a) Truth table for majority function of three variables.

(b) A circuit for (a).

3

5

Circuit Equivalence (1)

Construction of (a) NOT, (b) AND, and (c) OR gates

using only NAND gates or only NOR gates.

6

Circuit Equivalence (2)

Two equivalent functions (a) AB +AC, (b) A(B +C).

4

7

Circuit Equivalence (3)

Some identities of Boolean algebra.

8

Circuit Equivalence (4)

Alternative symbols for some gates:

(a) NAND, (b) NOR, (c) AND, (d) OR

5

9

Circuit Equivalence (5)

(a) The truth table for the XOR function.

(b-d) Three circuits for computing it.

10

Circuit Equivalence (6)

(a) Electrical characteristics of a device.

(b) Positive logic.

(c) Negative logic.

6

11

Integrated Circuits

An SSI chip containing four gates.

12

Multiplexers (1)

An eight-input

multiplexer circuit.

7

13

Multiplexers (2)

(a) An MSI multiplexer.

(b) The same multiplexer wired to compute the majority function.

14

Decoders

A 3-to-8 decoder

circuit.

8

15

Comparators

A simple 4-bit

comparator.

16

Programmable Logic Arrays

A 12-input, 6-output

programmable logic array.

The little squares represent

fuses that can be burned out.

9

17

Shifters

A 1-bit left/right shifter.

18

Adders (1)

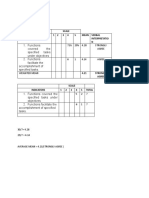

(a) A truth table for 1-bit addition.

(b) A circuit for a half adder.

(a)

(b)

10

19

Adders (2)

(a) Truth table for a full adder.

(b) Circuit for a full adder.

20

Arithmetic Logic Units (1)

A 1-bit ALU.

11

21

Arithmetic Logic Units (2)

Eight 1-bit ALU slices connected to make an 8-bit ALU.

The enables and invert signals are not shown for simplicity.

22

Clocks

(a) A clock.

(b) The timing diagram for the clock.

(c) Generation of an asymmetric clock.

12

23

Latches (1)

(a) NOR latch in state 0.

(b) NOR latch in state 1.

(c) Truth table for NOR.

24

Latches (2)

A clocked SR latch.

13

25

Latches (3)

A clocked D latch.

26

Flip-Flops (1)

(a) A pulse generator.

(b) Timing at four points in the circuit.

14

27

Flip-Flops (2)

A D flip-flop.

28

Flip-Flops (3)

D latches and flip-flops.

15

29

Flip-Flops (4)

Dual D flip-flop.

30

Flip-Flops (5)

Octal flip-flop.

16

31

Memory

Organization (1)

Logic diagram for a

4 x 3 memory.

Each row is one of the

four 3-bit words.

32

Memory Organization (2)

(a) A noninverting buffer.

(b) Effect of (a) when control is high.

(c) Effect of (a) when control is low.

(d) An inverting buffer.

17

33

Memory Chips (1)

Two ways of organizing a 4-Mbit memory chip.

34

Memory Chips (2)

Two ways of organizing a 512 Mbit memory chip.

18

35

Nonvolatile Memory Chips

A comparison of various memory types.

36

CPU Chips

The logical pinout of a generic CPU. The arrows indicate input

signals and output signals. The short diagonal lines indicate

that multiple pins are used. For a specific CPU, a number will

be given to tell how many.

19

37

Computer Buses (1)

A computer system with multiple buses.

38

Computer Buses (2)

Examples of bus masters and slaves.

20

39

Bus Width

Growth of an Address bus over time.

40

Bus Clocking (1)

Read timing on a synchronous bus.

21

41

Bus Clocking (2)

Specification of some critical times.

42

Asynchronous Buses

Operation of an asynchronous bus.

22

43

Bus Arbitration (1)

(a) A centralized one-level bus arbiter using daisy chaining.

(b) The same arbiter, but with two levels.

44

Bus Arbitration (2)

Decentralized bus arbitration.

23

45

Bus Operations (1)

A block transfer.

46

Bus Operations (2)

Use of the 8259A interrupt controller.

24

47

The Pentium 4

The Pentium 4 physical pinout.

48

The Pentium 4s Logical Pinout

Logical pinout of

the Pentium 4.

Names in upper

case are the

office are the

official Intel

names for

individual signals.

Names in mixed

case are groups

of related signals

or signal

descriptions.

25

49

Pipelining on the Pentium 4s Memory Bus

Pipelining requests on the Pentium 4s memory bus.

50

The UltraSPARC III (1)

The UltraSPARC III CPU chip.

26

51

The UltraSPARC III (2)

The main features of the core of an UltraSPARC III system.

52

The 8051 (1)

Physical pinout of the 8051.

27

53

The 8051 (2)

Logical pinout of the 8051.

54

The ISA Bus

The PC/AT bus has two components,

the original PC part and the new part.

28

55

The PCI Bus (1)

Architecture of an early Pentium system. The thicker buses have more

bandwidth than the thinner ones but the figure is not to scale.

56

The PCI Bus (2)

The bus structure of a modern Pentium 4.

29

57

PCI Bus Arbitration

The PCI bus uses a centralized bus arbiter.

58

PCI Bus Signals(1)

Mandatory PCI bus signals.

30

59

PCI Bus Signals(2)

Optional PCI bus signals.

60

PCI Bus Transactions

Examples of 32-bit PCI bus transactions. The first three cycles

are used for a read operation, then an idle cycle, and then

three cycles for a write operation.

31

61

PCI Express

A typical PCI Express system.

62

PCI Express Protocol Stack

(a) The PCI Express protocol stack.

(b) The format of a packet.

32

63

The Universal Serial Bus

The USB root hub sends out frames every 1.00 ms.

64

PIO Chips

An 8255A PIO chip.

33

65

Address Decoding (1)

Location of the EPROM, RAM, and PIO in our 64 KB address

space.

66

Address Decoding (2)

Full address decoding.

34

67

Address Decoding (3)

Partial address decoding.

You might also like

- Digital QuizDocument17 pagesDigital QuizSri MathiNo ratings yet

- Computer System Architecture Set 1Document10 pagesComputer System Architecture Set 1Emilia KullutweNo ratings yet

- Digital Interview QuestionsDocument5 pagesDigital Interview QuestionsAnindra NallapatiNo ratings yet

- MPMC 100 MCQ Set IDocument17 pagesMPMC 100 MCQ Set Ivlsimani9110No ratings yet

- 8051 MCQDocument25 pages8051 MCQRohan Bachhav100% (1)

- Practice Questions To Set 8Document8 pagesPractice Questions To Set 8NiravNo ratings yet

- Ugc Net Merit Entrance Sectional Test No.00Document8 pagesUgc Net Merit Entrance Sectional Test No.00gupta_vkNo ratings yet

- DCSFinal II April21 AssignmenrtDocument45 pagesDCSFinal II April21 AssignmenrtChirantan BiswasNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- Microprocessor AptiDocument7 pagesMicroprocessor AptiprachiumangNo ratings yet

- Quiz Questions On Unit 2 Microcontroller (8051)Document15 pagesQuiz Questions On Unit 2 Microcontroller (8051)Manveen KaurNo ratings yet

- EE6301 DLC Question Bank Rejinpaul 2Document8 pagesEE6301 DLC Question Bank Rejinpaul 2aruljothiNo ratings yet

- DEC Lab Experiments - 2017aDocument5 pagesDEC Lab Experiments - 2017aManjeet SinghNo ratings yet

- QB - Basics of Com - OrganizationDocument11 pagesQB - Basics of Com - OrganizationAarya ShilimkarNo ratings yet

- Compiled MCA-I 2016Document248 pagesCompiled MCA-I 2016rajakishore mohapatraNo ratings yet

- Ec 1202 Digital System DesignDocument8 pagesEc 1202 Digital System DesignworkubNo ratings yet

- UMA VLSI DesignDocument158 pagesUMA VLSI DesignsallyNo ratings yet

- Digital ElectronicsDocument9 pagesDigital ElectronicsmanikantamadetiNo ratings yet

- Digital ElectronicsDocument8 pagesDigital ElectronicsKali HungaNo ratings yet

- MODEL-dlc Eeee RmkcetDocument2 pagesMODEL-dlc Eeee RmkcetreporterrajiniNo ratings yet

- 8085Document14 pages8085diNo ratings yet

- Digital System Objective QuestionsDocument17 pagesDigital System Objective QuestionsRanjeet pratap singh bhadoriyaNo ratings yet

- Microprocessor Assignment (Assignment-2)Document7 pagesMicroprocessor Assignment (Assignment-2)Ajay SahuNo ratings yet

- Ei2353:Digital System Design: Question BankDocument3 pagesEi2353:Digital System Design: Question BanknithyadeceNo ratings yet

- Fundamentals of Microprocessor 8085: Multiple Choice QuestionsDocument21 pagesFundamentals of Microprocessor 8085: Multiple Choice Questionsraghavrocks89No ratings yet

- Computer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GateDocument8 pagesComputer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GatepranavbommiNo ratings yet

- MCS 12Document5 pagesMCS 12Divya KumariNo ratings yet

- Fundamentals of Microcontroller and Its Application: Unit N0.1Document16 pagesFundamentals of Microcontroller and Its Application: Unit N0.1Pankaj KaleNo ratings yet

- Tutorial QuestionxDocument11 pagesTutorial QuestionxkingraajaNo ratings yet

- Question Bank For Mid-2 r13 (Vlsi) .Document6 pagesQuestion Bank For Mid-2 r13 (Vlsi) .rppvchNo ratings yet

- E-1 MCQ SYBCSDocument8 pagesE-1 MCQ SYBCSOMNo ratings yet

- Digital Fundamentals BE SEM 3Document2 pagesDigital Fundamentals BE SEM 3Dhwanil BhattNo ratings yet

- DDCO UPDATED QUESTION BANKttttDocument4 pagesDDCO UPDATED QUESTION BANKttttbrahmareddy.22iseNo ratings yet

- Third Homework AssignmentDocument4 pagesThird Homework AssignmentTara Shankar ChakrabortyNo ratings yet

- QbankDocument3 pagesQbankAnanthi RajkumarNo ratings yet

- COA QuestionBank - 1Document3 pagesCOA QuestionBank - 1itzzsandeshNo ratings yet

- Assignments CSE211Document4 pagesAssignments CSE211Raghav JhanjeeNo ratings yet

- 8051 FAQsDocument5 pages8051 FAQsprashant goreNo ratings yet

- CA 3 MicroprocessorDocument1 pageCA 3 Microprocessornodov66591No ratings yet

- TI ElectronicsDocument6 pagesTI ElectronicsShreeji ExportsNo ratings yet

- BSC (H) CSHT II 204 Mid2012 Ddu Assignment IDocument2 pagesBSC (H) CSHT II 204 Mid2012 Ddu Assignment IRavi RanjanNo ratings yet

- Ec2203 Digital Electronics r8Document3 pagesEc2203 Digital Electronics r8jenifar777No ratings yet

- Multiple Choice QuestionsDocument22 pagesMultiple Choice QuestionsMaari SenjiduveNo ratings yet

- Microprocessor MCQsDocument67 pagesMicroprocessor MCQsHarsimran100% (1)

- Te Oct 2014Document149 pagesTe Oct 2014contrasterNo ratings yet

- Unit IV & V Question BankDocument5 pagesUnit IV & V Question BanknithyasaviNo ratings yet

- Microprocessor (KCS-403) Question BankDocument29 pagesMicroprocessor (KCS-403) Question BankCubic SectionNo ratings yet

- Digital QuestionsDocument3 pagesDigital Questionsmdhuq1No ratings yet

- Coa QaDocument25 pagesCoa QaHimanshu VermaNo ratings yet

- Computer Organization and Architecture-1Document5 pagesComputer Organization and Architecture-1Milan AntonyNo ratings yet

- Microcontroller & Application MCQ Test Papers: State Whether The Following Statements Are True or FalseDocument3 pagesMicrocontroller & Application MCQ Test Papers: State Whether The Following Statements Are True or FalsePrajyotNo ratings yet

- KRL Institute of Technology, Kahuta: CIT-2 Year Subject: Digital & Industrial Electronics Multiple Choice QuestionsDocument7 pagesKRL Institute of Technology, Kahuta: CIT-2 Year Subject: Digital & Industrial Electronics Multiple Choice QuestionsHamza MustafaNo ratings yet

- Preparatory Guidebook For Comprehensive Examination: Question Bank DsdaDocument14 pagesPreparatory Guidebook For Comprehensive Examination: Question Bank DsdaMisbah Sajid ChaudhryNo ratings yet

- Aptitude Technical Group Discussion Technical HR Personal InterviewDocument12 pagesAptitude Technical Group Discussion Technical HR Personal InterviewPrasad NagaNo ratings yet

- Holistic Exam2005-1 PDFDocument6 pagesHolistic Exam2005-1 PDFEnyew100% (1)

- Sample-Question-Paper - Digital Electronics and Microcontroller ApplicationsDocument5 pagesSample-Question-Paper - Digital Electronics and Microcontroller ApplicationsAbhishek ManeNo ratings yet

- Phys 418Document3 pagesPhys 418Joram MuiruriNo ratings yet

- PrasadDocument11 pagesPrasadchandujontyNo ratings yet

- Microprocessor Microcontroller EXAM 2021 MGDocument11 pagesMicroprocessor Microcontroller EXAM 2021 MGRene EBUNLE AKUPANNo ratings yet

- Catalogue of ProductsDocument49 pagesCatalogue of ProductsKuldeep SinghNo ratings yet

- Wistron W37Document51 pagesWistron W37vnenovNo ratings yet

- Notes - Responsive Designs-2533Document10 pagesNotes - Responsive Designs-2533Mannu GavelNo ratings yet

- Mde 4338aDocument160 pagesMde 4338aMiller Alexander Mora VargasNo ratings yet

- Command Line Interface PSS®E 35.3.1: September 2021Document368 pagesCommand Line Interface PSS®E 35.3.1: September 2021Tin RabuzinNo ratings yet

- On Line BloombergDocument21 pagesOn Line BloombergAlexisNo ratings yet

- Java Fundamentals - MidTermDocument6 pagesJava Fundamentals - MidTermMuhammad IqbaalNo ratings yet

- MIP COM2023 - Computer System FundamentalDocument2 pagesMIP COM2023 - Computer System FundamentalmdmmonalissaNo ratings yet

- TB82PH.2.2 AbbDocument8 pagesTB82PH.2.2 AbbZiyaur RahmanNo ratings yet

- Using The Go Programming Language PDFDocument68 pagesUsing The Go Programming Language PDFspywangNo ratings yet

- Alm2 DatasheetDocument5 pagesAlm2 Datasheetjavierdb2012No ratings yet

- Motorola's STARLINE Cable Simulator Are Used in Place of Fixed Forward Equalizer in Systems Where The Amplifiers Are Located Close TogetherDocument2 pagesMotorola's STARLINE Cable Simulator Are Used in Place of Fixed Forward Equalizer in Systems Where The Amplifiers Are Located Close TogetherRodrigo AlonzoNo ratings yet

- T Con Board SchematicsDocument3 pagesT Con Board SchematicsMiftachul Huda75% (4)

- Unit 14 p1Document2 pagesUnit 14 p1api-319906681No ratings yet

- TechNote - A5500 IRF v1.00Document29 pagesTechNote - A5500 IRF v1.00Marduc1No ratings yet

- Android PermissionsDocument11 pagesAndroid Permissionsqaws1234No ratings yet

- PyeconDocument298 pagesPyeconSeungho LeeNo ratings yet

- College Management System ProjectDocument66 pagesCollege Management System ProjectManish RajputNo ratings yet

- SC&T Company Profile-2011.11Document35 pagesSC&T Company Profile-2011.11Luis NascimentoNo ratings yet

- Mode of ExamDocument6 pagesMode of ExamJaspreetNo ratings yet

- Fundamentals of 5g Wireless Communications Sachan Book 82 - CompressDocument171 pagesFundamentals of 5g Wireless Communications Sachan Book 82 - CompressBijoy BanerjeeNo ratings yet

- Lab 1Document8 pagesLab 1Mulugeta AbebawNo ratings yet

- 1 - Xpon Onu 1g1f+catv+wifi+potsDocument5 pages1 - Xpon Onu 1g1f+catv+wifi+potsFernando Calderon100% (2)

- BT 205 BceDocument15 pagesBT 205 BceAnurag JainNo ratings yet

- PWM Control of 3phase VsiDocument65 pagesPWM Control of 3phase VsiOm prakashNo ratings yet

- Thesis SidelineDocument8 pagesThesis SidelineChristian Aries LansanganNo ratings yet

- RF Power Amplifier FundamentalsDocument36 pagesRF Power Amplifier Fundamentalsi_spyder5388100% (1)

- Itr32x XXXX Just Touch Ds220622091eenDocument2 pagesItr32x XXXX Just Touch Ds220622091eenSanjaa ENo ratings yet

- ThinkPad X1 Carbon Gen 10 DatasheetDocument4 pagesThinkPad X1 Carbon Gen 10 DatasheetAlexander MedinaNo ratings yet

- User Manual Gev267, Gev268, Gev269 v3.0Document9 pagesUser Manual Gev267, Gev268, Gev269 v3.0MihaiisvoranuNo ratings yet