Professional Documents

Culture Documents

I2C

Uploaded by

Marco Ulises Ramirez MendozaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

I2C

Uploaded by

Marco Ulises Ramirez MendozaCopyright:

Available Formats

6-6-2014

MARCO ULISES

RAMREZ

MENDOZA

INVESTIGACIN SOBRE DISPOSITIVOS I2C

INGENIERIA EN TELEMATICA 6 A

Introduccin

I2C es un protocolo de comunicacin serie diseado por Philips que se utiliza esencialmente entre dispositivos que pertenecen al mismo

circuito, por ejemplo, sensores con un microcontrolador.

Caractersticas del protocolo:

Velocidad standard de 100Kbit/s (100kbaudios). Se puede cambiar al modo de alta velocidad (400Kbit/s)

Configuracin maestro/esclavo. La direccin del esclavo se configura con software

Solo se necesitan dos lneas:

SDA (Serial Data Line): Lnea de datos.

SCL/CLK (Serial Clock Line): Lnea de reloj, ser el que marque el tiempo de RW (Lectura/Escritura)

La comunicacin siempre tiene la estructura siguiente:

Transmisor: Byte de datos (8 Bits)

Receptor: Bit llamado ACK de confirmacin.

SDA y SCL van a su pin correspondiente en cada dispositivo, de manera que todos quedan en paralelo.

Las lneas SDA y SCL estn independientemente conectadas a dos resistores Pull-Up que se encargaran de que el valor lgico siempre

sea alto a no ser que un dispositivo lo ponga a valor lgico bajo.

Es una comunicacin de tipo half duplex. Comunicacin bidireccional por la misma lnea pero no simultneamente bidireccional.

La estructura de la comunicacin bsica es la siguiente:

1. START condition (Master)

2. 7 Bits de direccin de esclavo (Master)

3. 1 Bit de RW, 0 es Leer y 1 Escribir. (Master)

4. 1 Bit de Acknowledge (Slave)

5. Byte de direccin de memoria (Master)

6. 1 Bit de Acknowledge (Slave)

7. Byte de datos (Master/Slave (Escritura/Lectura))

8. 1 Bit de Acknowledge (Slave/Master (Escritura/Lectura))

9. STOP condition (Master)

I

2

C Esquema Diagrama Caractersticas

EEPROM

alimentacin nica con la

Operacin Abajo de 1.7V

para

24AA256 y 24FC256, 2,5 V

para

Dispositivos 24LC256

Tecnologa CMOS de baja

potencia

-corriente de lectura 400 uA

mx. a 5,5 V, 400 kHz

- Corriente de espera: 1 uA

mx. a 3,6 V, I-temp

2 cables de interface serie,

I2C compatible

en cascada hasta ocho

dispositivos

Disparador Schmitt

Entradas para supresin de

ruido

Control de la pendiente de

salida para eliminar la tierra

de rebote

100 kHz y 400 kHz

Compatibilidad Reloj

Pgina Tiempo de

escritura 5 ms mx.

Auto-Timed Erase / Write

Cycle

64-Byte Pgina Escritura

de Buffer

Hardware de proteccin

contra escritura

Proteccin ESD> 4000V

Ms de un milln de ciclos

de borrado / escritura

Retencin de datos> 200

aos

Programacin de Fbrica

Los paquetes incluyen 8-

lead PDIP, SOIC, SOIJ,

DFN

RTCC

sincronizacin

Salida de alarma / reloj

programable

Amplia gama de regulacin

digital para la exactitud

Timestamp @ VCC Falla y

VCC Restore

memoria de usuario

SRAM respaldada por batera

EEPROM

UNICAS ID / MAC address

pins de salida estandar

DISPLAY

3 1/2

DIGITAL

6,9 mm (0,270 pulgadas) Altura

de carcter

Alta Intensidad luminosa

Requerimientos de baja potencia

Cada Unidad Visualmente

verific la Uniformidad

de los Elementos

Seal, desbordamiento, e

Izquierda o Derecha Decimal

Capacidades

Amplio ngulo de visin

Compatible con la mayora de

TTL y DTL

Circuitos

LCD

I2C hasta 400 kHz

Direccin configurable del usuario

conjunto de comandos simple para

conexin directa al mdulo LCD

Salida de luz posterior

condensador de ajuste de contraste

1,2 y 4 lneas de pantallas

Interfaz de teclado de punto de

cruce de 12 vas

16 buffer de teclado tecla

pin propsito adicional general o

interrumpir cuando la llave est

disponible

Tensin de funcionamiento 2,0 a

5,5 V

corriente <1 mA a 5 V

MULTIPLEXORES

Gestin de recursos rgida y

poco apta para flujos de

trnsito variable.

Requiere duplexor de antena

para transmisin dplex.

Normalmente FDMA se

combina con multiplexing

FDD

Se asignan canales

individuales a cada usuario.

Los canales son asignados

de acuerdo a la demanda.

Tecnologa muy

experimentada y fcil de

implementar.

TECLADOS

Operacin Power-Supply

Voltage Range de 1,65 V a 3,6

V

Compatible con teclado

QWERTY de la Operacin Plus

GPIO Expansin

18 GPIO pueden ser

configurados en ocho entradas y

diez salidas de Apoyo a una

matriz de teclado 8 10 (80

teclas)

La proteccin contra ESD

excede JESD 22 sobre la no-

GPIO pins-2000-V Modelo de

Cuerpo Humano (A114-A) -

1000-V Charged Device Model

(C101)

15kV Modelo del cuerpo

humano alto voltaje ESD (lneas

GPIO)

Espera Baja (Idle) Consumo de

corriente: 3 A

Drenaje de sondeo actual 70 A

para una tecla pulsada

10 Byte FIFO para almacenar

10 pulsa y suelta clave

Soporta 1-MHz Modo Fast Plus

I2C Bus

Open-Drain Active-Low Salida

de interrupciones, afirm cuando

se pulsa la tecla y tecla

ESCAPE

Mnimo tiempo de eliminacin

rebote de 50 s

Accin Schmitt-Disparador

Permite entrada Slow

Transicin y mejor inmunidad al

ruido de conmutacin en los

SCL y SDA Entradas: Tpico V a

1,8 V es 0,18 V

El rendimiento de cierre

excede de 200 mA por

hys JESD 78, Clase II

Muy Pequeo paquete - WCSP

(YFP): 2 mm x 2 mm; 0,4 mm de

paso

DAC

micro fuerza de la

operacin: 125 A @ 3 V

Rpida velocidad de

actualizacin: 188 KSPS

restablecimiento al

encendido a Cero

2.7-V a 5,5 V-Power Supply

especificado Monotnica by

Design

Interfaz I2C hasta 3,4 Mbps

Amplificador de bfer de

salida on-Chip, Carril-a-Carril

Funcionamiento

Doble buffer Registro de

entrada

Soporte de direcciones

para hasta dos DAC5571s

Pequeo 6 Lead Sot 23

Paquete

Funcionamiento De -40 C

a 105 C

You might also like

- How To Install DebianDocument26 pagesHow To Install DebianMarco Ulises Ramirez MendozaNo ratings yet

- HORARIOS 2014-3 - Prototipo 01 - Grupal PDFDocument9 pagesHORARIOS 2014-3 - Prototipo 01 - Grupal PDFMarco Ulises Ramirez MendozaNo ratings yet

- Tipos de SatélitesDocument6 pagesTipos de SatélitesMarco Ulises Ramirez MendozaNo ratings yet

- Sensor EsDocument17 pagesSensor EsMarco Ulises Ramirez MendozaNo ratings yet

- Patrones de RadiaciónDocument6 pagesPatrones de RadiaciónMarco Ulises Ramirez MendozaNo ratings yet

- Pos GreeDocument16 pagesPos GreeMarco Ulises Ramirez MendozaNo ratings yet

- Pensamiento CríticoDocument7 pagesPensamiento CríticoHared MezaNo ratings yet

- Regularización Ui - Compendio TrabajoDocument3 pagesRegularización Ui - Compendio TrabajoMarco Ulises Ramirez MendozaNo ratings yet

- Pensamiento InferencialDocument33 pagesPensamiento InferencialEduardo Pozo MontuyNo ratings yet

- HP 1Document3 pagesHP 1Marco Ulises Ramirez MendozaNo ratings yet

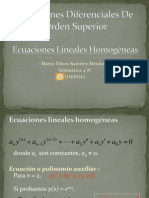

- Ecuaciones Diferenciales Orden SuperiorDocument7 pagesEcuaciones Diferenciales Orden SuperiorMarco Ulises Ramirez MendozaNo ratings yet

- La naturaleza humana y las orientaciones del carácterDocument17 pagesLa naturaleza humana y las orientaciones del carácterMarco Ulises Ramirez MendozaNo ratings yet

- Ecuaciones Diferenciales Orden SuperiorDocument7 pagesEcuaciones Diferenciales Orden SuperiorMarco Ulises Ramirez MendozaNo ratings yet

- 11 Transformada de LaplaceDocument98 pages11 Transformada de LaplaceLeidy YanezNo ratings yet

- Reporte 741Document17 pagesReporte 741Marco Ulises Ramirez MendozaNo ratings yet

- Reporte 741Document17 pagesReporte 741Marco Ulises Ramirez MendozaNo ratings yet

- Reporte 741Document17 pagesReporte 741Marco Ulises Ramirez MendozaNo ratings yet

- Lenguaje de Comandos BatDocument43 pagesLenguaje de Comandos Batkaiser4kNo ratings yet

- Mies-Coordinacion Zonal 2Document26 pagesMies-Coordinacion Zonal 2Ximena SimbañaNo ratings yet

- Ficha de InscripcionDocument1 pageFicha de InscripcionDaniela alexandra Negron estrellaNo ratings yet

- Rol y Función Del Docente Como Mediador en El Proceso de Enseñanza y AprendizajeDocument6 pagesRol y Función Del Docente Como Mediador en El Proceso de Enseñanza y AprendizajethamyunesrNo ratings yet

- Problemas Propuestos de Excavación y TransporteDocument3 pagesProblemas Propuestos de Excavación y TransporteMiguel Andrés100% (1)

- 1.4lista Fric Rot N°004 018 30 07 2018Document38 pages1.4lista Fric Rot N°004 018 30 07 2018locomania2008No ratings yet

- Capitulo2 Tanque OnhoffDocument7 pagesCapitulo2 Tanque OnhoffElizabeth Marleni Gonzales CcantoNo ratings yet

- XtrailDocument3 pagesXtrailMonty MathewsNo ratings yet

- Sierra CaladoraDocument17 pagesSierra CaladoraMario GarciaNo ratings yet

- Programación Ofimatica y Procesos de La InformacionDocument18 pagesProgramación Ofimatica y Procesos de La InformacionCecilia De León GaldonaNo ratings yet

- Metrado de Obras Provisionales - TungulaDocument49 pagesMetrado de Obras Provisionales - TungulaClaudiaBacaCubaNo ratings yet

- g45 X Manual Instructions 1728 enDocument11 pagesg45 X Manual Instructions 1728 enLourdes Barquero GarcíaNo ratings yet

- Petar Trabajos en CalienteDocument1 pagePetar Trabajos en Calientecesar_poma_24No ratings yet

- COMUNIDAD RURAL VS URBANADocument6 pagesCOMUNIDAD RURAL VS URBANAMigdelia AizpruaNo ratings yet

- Secadora UNIMACDocument26 pagesSecadora UNIMACingenieria seguimietos100% (1)

- Estructura Urbana - Alison y Peter SmithsonDocument2 pagesEstructura Urbana - Alison y Peter SmithsonJuan O.100% (4)

- Rubrica de Tecnología e Informática 3 PeríodoDocument1 pageRubrica de Tecnología e Informática 3 PeríodoLuzmaNo ratings yet

- Guia para DiaposDocument2 pagesGuia para DiaposFlakix Lïlï CastilloNo ratings yet

- DIN EN ISO 10628 Fliessbilder EspañolDocument13 pagesDIN EN ISO 10628 Fliessbilder EspañolManu Antonio100% (4)

- Manual de Pedidos y Adquisiciones SIGADocument30 pagesManual de Pedidos y Adquisiciones SIGAfilemon252No ratings yet

- Mantenimiento RCM Tarea 3 UsachDocument7 pagesMantenimiento RCM Tarea 3 UsachAndré FuenzalidaNo ratings yet

- 20190502090542Document33 pages20190502090542Erik QuezadaNo ratings yet

- InyeccionDocument8 pagesInyeccionAndres AriasNo ratings yet

- FICHASDocument5 pagesFICHASJorge ValdezNo ratings yet

- LISTOOOO FORMATO PARA VALIDAR INSTRUMENTO DE INFORMACIÓN Planilla Juicio de ExpertosUU (Reparado)Document6 pagesLISTOOOO FORMATO PARA VALIDAR INSTRUMENTO DE INFORMACIÓN Planilla Juicio de ExpertosUU (Reparado)RAQUEL VALENZUELA JANAMPANo ratings yet

- Que Es La RadiaciónDocument18 pagesQue Es La RadiaciónViviana Molina100% (1)

- Limitantes Estructurales A La Industrialización en BoliviaDocument21 pagesLimitantes Estructurales A La Industrialización en BoliviaFundaciónFriedrichEbertBoliviaNo ratings yet

- Axt 1Document5 pagesAxt 1Diana Figueroa Sierra50% (2)

- Aspectos Ambientales en La Recuperacion SecundariaDocument3 pagesAspectos Ambientales en La Recuperacion SecundariaAlejandro Gabriel MaidanaNo ratings yet

- No Ciempre Es Malo RecordarDocument273 pagesNo Ciempre Es Malo RecordarNancy Luz Marroquín RodríguezNo ratings yet