Professional Documents

Culture Documents

74hc02 PDF

Uploaded by

carlos167020140 ratings0% found this document useful (0 votes)

27 views5 pagesThe 74HC / HCT02 are high-speed Si-gate CMOS devices. They are pin compatible with low power Schottky TTL (LSTTL) They provide the 2-input NOR function.

Original Description:

Original Title

74hc02.pdf

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe 74HC / HCT02 are high-speed Si-gate CMOS devices. They are pin compatible with low power Schottky TTL (LSTTL) They provide the 2-input NOR function.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

27 views5 pages74hc02 PDF

Uploaded by

carlos16702014The 74HC / HCT02 are high-speed Si-gate CMOS devices. They are pin compatible with low power Schottky TTL (LSTTL) They provide the 2-input NOR function.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 5

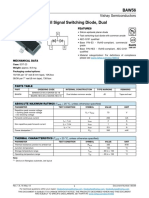

Product specication

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT02

Quad 2-input NOR gate

For a complete data sheet, please also download:

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990 2

Philips Semiconductors Product specication

Quad 2-input NOR gate 74HC/HCT02

FEATURES

Output capability: standard

I

CC

category: SSI

GENERAL DESCRIPTION

The 74HC/HCT02 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL).

They are specified in compliance with JEDEC standard no. 7A.

The 74HC/HCT02 provide the 2-input NOR function.

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25 C; t

r

= t

f

= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (P

D

in W):

P

D

= C

PD

V

CC

2

f

i

+ (C

L

V

CC

2

f

O

) where:

f

i

= input frequency in MHz

f

o

= output frequency in MHz

C

L

= output load capacitance in pF

V

CC

= supply voltage in V

(C

L

V

CC

2

f

o

) = sum of outputs

2. For HC the condition is V

I

= GND to V

CC

For HCT the condition is V

I

= GND to V

CC

1.5 V

ORDERING INFORMATION

See 74HC/HCT/HCU/HCMOS Logic Package Information.

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PHL

/ t

PLH

propagation delay nA, nB to nY C

L

= 15 pF; V

CC

= 5 V 7 9 ns

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per gate notes 1 and 2 22 24 pF

December 1990 3

Philips Semiconductors Product specication

Quad 2-input NOR gate 74HC/HCT02

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 4, 10, 13 1Y to 4Y data outputs

2, 5, 8, 11 1A to 4A data inputs

3, 6, 9, 12 1B to 4B data inputs

7 GND ground (0 V)

14 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

Fig.4 Functional diagram. Fig.5 Logic diagram (one gate).

FUNCTION TABLE

Notes

1. H = HIGH voltage level

L = LOW voltage level

INPUTS OUTPUT

nA nB nY

L

L

H

H

L

H

L

H

H

L

L

L

December 1990 4

Philips Semiconductors Product specication

Quad 2-input NOR gate 74HC/HCT02

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications.

Output capability: standard

I

CC

category: SSI

AC CHARACTERISTICS FOR 74HC

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

SYMBOL PARAMETER

T

amb

(C) TEST CONDITIONS

74HC

UNIT

V

CC

(V)

WAVEFORMS

+25 40 to +85 40 to +125

min. typ. max. min. max. min. max.

t

PHL

/ t

PLH

propagation delay

nA, nB to nY

25

9

7

90

18

15

115

23

20

135

27

23

ns

2.0

4.5

6.0

Fig.6

t

THL

/ t

TLH

output transition time

19

7

6

75

15

13

95

19

16

110

22

19

ns

2.0

4.5

6.0

Fig.6

December 1990 5

Philips Semiconductors Product specication

Quad 2-input NOR gate 74HC/HCT02

DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications.

Output capability: standard

I

CC

category: SSI

Notes to HCT types

The value of additional quiescent supply current (I

CC

) for a unit load of 1 is given in the family specifications.

To determine I

CC

per input, multiply this value by the unit load coefficient shown in the table below.

AC CHARACTERISTICS FOR 74HCT

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

AC WAVEFORMS

PACKAGE OUTLINES

See 74HC/HCT/HCU/HCMOS Logic Package Outlines.

INPUT UNIT LOADCOEFFICIENT

nA, nB 1.50

SYMBOL PARAMETER

T

amb

(C) TEST CONDITIONS

74HCT

UNIT

V

CC

(V)

WAVEFORMS

+25 40 to+85 40 to+125

min. typ. max. min. max. min. max.

t

PHL

/ t

PLH

propagation delay

nA, nB to nY

11 19 24 29 ns 4.5 Fig.6

t

THL

/ t

TLH

output transition time 7 15 19 22 ns 4.5 Fig.6

Fig.6 Waveforms showing the input (nA, nB) to output (nY) propagation delays and the output transition times.

HC: V

M

= 50%; V

I

= GND to V

CC

HCT: V

M

= 1.3 V; V

I

= GND to 3 V.

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- 7749289-TheClandestineChemist 'Snotebook PDFDocument28 pages7749289-TheClandestineChemist 'Snotebook PDFTonNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Fundamentals of The Automotive Cabin Climate Control SystemDocument6 pagesFundamentals of The Automotive Cabin Climate Control SystemSeddik MaarfiNo ratings yet

- SANYO UR18650A 2.2ah SpecificationsDocument18 pagesSANYO UR18650A 2.2ah SpecificationsArpit Agrawal100% (1)

- Charpy Impact Test - STP 1072Document219 pagesCharpy Impact Test - STP 1072biancogallazzi100% (3)

- BN44 00155aDocument2 pagesBN44 00155aEwerton Correia FrançaNo ratings yet

- HF Transceiver PDFDocument13 pagesHF Transceiver PDFlg900df5063No ratings yet

- Design and Build Contract TemplateDocument9 pagesDesign and Build Contract TemplateAlexanderNo ratings yet

- Emergency Off and Rescue From Helicopter: Ground Rescue Booklet Ec130T2Document20 pagesEmergency Off and Rescue From Helicopter: Ground Rescue Booklet Ec130T2robbertmd100% (1)

- BN44 00155aDocument2 pagesBN44 00155aCaptain444100% (1)

- BN44 00155aDocument2 pagesBN44 00155aCaptain444100% (1)

- Idirect Evolution X3 Manual: Read/DownloadDocument2 pagesIdirect Evolution X3 Manual: Read/Downloadcarlos167020140% (1)

- LIFIDocument7 pagesLIFIRajeshNo ratings yet

- SPEC SHEET Uni Ku PLL LNB 0115 2 PDFDocument3 pagesSPEC SHEET Uni Ku PLL LNB 0115 2 PDFcarlos16702014No ratings yet

- SPEC SHEET Uni Ku PLL LNB 0115 2 PDFDocument3 pagesSPEC SHEET Uni Ku PLL LNB 0115 2 PDFcarlos16702014No ratings yet

- Next Generation Cold Corridor - enDocument12 pagesNext Generation Cold Corridor - encarlos16702014No ratings yet

- Universal Ku-Band 2LO PLL LNB (Switchable Local) MODEL No. NJR2841H, NJR2842H, & NJR2843H SeriesDocument6 pagesUniversal Ku-Band 2LO PLL LNB (Switchable Local) MODEL No. NJR2841H, NJR2842H, & NJR2843H Seriescarlos16702014No ratings yet

- Varicondition DX enDocument5 pagesVaricondition DX encarlos16702014No ratings yet

- Airflow Optimisation: RI ON VDocument5 pagesAirflow Optimisation: RI ON Vcarlos16702014No ratings yet

- Universal Ku-Band 2LO PLL LNB (Switchable Local) - MODEL No. NJR2841E/42E/43E SeriesDocument24 pagesUniversal Ku-Band 2LO PLL LNB (Switchable Local) - MODEL No. NJR2841E/42E/43E Seriescarlos16702014No ratings yet

- SPEC SHEET Uni Ku PLL LNB 0115 2 PDFDocument3 pagesSPEC SHEET Uni Ku PLL LNB 0115 2 PDFcarlos16702014No ratings yet

- Manual FSH3 - Operacion - Ingles PDFDocument119 pagesManual FSH3 - Operacion - Ingles PDFcarlos16702014No ratings yet

- Universal Ku-Band 2LO PLL LNB (Switchable Local) MODEL No. NJR2841H, NJR2842H, & NJR2843H SeriesDocument6 pagesUniversal Ku-Band 2LO PLL LNB (Switchable Local) MODEL No. NJR2841H, NJR2842H, & NJR2843H Seriescarlos16702014No ratings yet

- Universal Ku-Band 2LO PLL LNB (Switchable Local) - MODEL No. NJR2841E/42E/43E SeriesDocument24 pagesUniversal Ku-Band 2LO PLL LNB (Switchable Local) - MODEL No. NJR2841E/42E/43E Seriescarlos16702014No ratings yet

- 1259 Dims W FeedDocument2 pages1259 Dims W Feedcarlos16702014No ratings yet

- Assembly, Operation and Maintenance Manual For: Vertexrsi Model 2.4-Meter Series 1259 Quick Deploy Antenna (Qda)Document33 pagesAssembly, Operation and Maintenance Manual For: Vertexrsi Model 2.4-Meter Series 1259 Quick Deploy Antenna (Qda)carlos16702014100% (2)

- Irf3205 PDFDocument9 pagesIrf3205 PDFJuanito Naxito Jebus ArjonaNo ratings yet

- 2SC3063Document3 pages2SC3063carlos16702014No ratings yet

- 7447Document14 pages7447api-3730800100% (1)

- DVD Unlocking CodesDocument56 pagesDVD Unlocking CodesShona96% (26)

- Baw 56Document4 pagesBaw 56carlos16702014No ratings yet

- BN44 00260aDocument2 pagesBN44 00260aJuan VilasNo ratings yet

- PDFDocument7 pagesPDFcarlos16702014No ratings yet

- 2n4400 PDFDocument14 pages2n4400 PDFcarlos16702014No ratings yet

- 74LS393 PDFDocument11 pages74LS393 PDFcarlos16702014No ratings yet

- Ultra ETK20910Document2 pagesUltra ETK20910emil gasimovNo ratings yet

- Definitions of Physical QuantitiesDocument41 pagesDefinitions of Physical QuantitiesAnonymous QiMB2lBCJLNo ratings yet

- Chapter 12 Solutions To ExercisesDocument41 pagesChapter 12 Solutions To ExercisesMuhammad Awais56% (9)

- Security Door InstallationDocument15 pagesSecurity Door InstallationHugo TrindadeNo ratings yet

- Cover Block (8383837083)Document7 pagesCover Block (8383837083)BALAJI ENTERPRISESNo ratings yet

- Advanced Vibration Chapter03Document130 pagesAdvanced Vibration Chapter03Alooy MohamedNo ratings yet

- Dtu-30 09 2019 PDFDocument15 pagesDtu-30 09 2019 PDFRameo majumderNo ratings yet

- Basic Yagi Antenna Design For The ExperimenterDocument9 pagesBasic Yagi Antenna Design For The ExperimenterKrista JacksonNo ratings yet

- Ptu Datesheet 2013Document4 pagesPtu Datesheet 2013Mugume JosephNo ratings yet

- Ludwig Eduard BoltzmannDocument10 pagesLudwig Eduard BoltzmannMarkoNo ratings yet

- ATMega8 UcDocument40 pagesATMega8 UcnrjchopraNo ratings yet

- Ground Water Recharge Techniques 2Document141 pagesGround Water Recharge Techniques 2Ravi Bhushan SharmaNo ratings yet

- DSE7410 MKII DSE7420 MKII Installation Instructions PDFDocument2 pagesDSE7410 MKII DSE7420 MKII Installation Instructions PDFyao nestorNo ratings yet

- Robotic CafeDocument13 pagesRobotic CafeRana SaqlainNo ratings yet

- 1 - ERDAS IMAGINE Viewer PDFDocument20 pages1 - ERDAS IMAGINE Viewer PDFRahmad KurniawanNo ratings yet

- WPT PresentationDocument23 pagesWPT PresentationSyed Safiur RahmanNo ratings yet

- MYG Varistors Data SheetDocument4 pagesMYG Varistors Data SheetPedro Giménez100% (1)

- Electrical Type Flow MetersDocument22 pagesElectrical Type Flow MetersAnuNarayan R0% (1)

- 64K (8Kx8) Parallel EEPROM With Page Write and Software Data Protection AT28C64BDocument18 pages64K (8Kx8) Parallel EEPROM With Page Write and Software Data Protection AT28C64BChu Thi ThuanNo ratings yet

- Analytical Study On The Cornering Behavior of An Articulated Tracked VehicleDocument1 pageAnalytical Study On The Cornering Behavior of An Articulated Tracked VehicleiDEvNo ratings yet

- Motordata Manual en PDFDocument12 pagesMotordata Manual en PDFVut TheaNo ratings yet

- Instrumentation - Aeroplanes: 22.01. Flight InstrumentsDocument27 pagesInstrumentation - Aeroplanes: 22.01. Flight InstrumentsveenadivyakishNo ratings yet