Professional Documents

Culture Documents

80C186 and 80C188 Integrated 16-Bit Microprocessors: Clocking Information Changes Crystal-Driven Clock Source

Uploaded by

Cristian BandilaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

80C186 and 80C188 Integrated 16-Bit Microprocessors: Clocking Information Changes Crystal-Driven Clock Source

Uploaded by

Cristian BandilaCopyright:

Available Formats

AMENDMENT

This document contains information on a product under development at Advanced Micro Devices. The information

is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this product

without notice.

Publication# 16514 Rev: D Amendment/1

Issue Date: October 1998

80C186 and 80C188 Integrated

16-Bit Microprocessors

This document amends the 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book, order #16514D, and

replaces the discontinued 80C186/80C188 CMOS High-Integration 16-Bit Microprocessors Amendment (specifica-

tions for the 20-MHz industrial operating range). This amendment consists of two parts:

n Clock generation information changes for the 80C186 and 80C188 microcontrollers. If the guidelines in this bulletin

are not followed, you may experience problems with clock start-up.

n Industrial operating information at 20 MHz. This is the same information that was published in the discontinued

80C186/80C188 CMOS High-Integration 16-Bit Microprocessors Amendment.

CLOCKING INFORMATION CHANGES

Crystal-Driven Clock Source

The internal oscillator circuit of the microcontroller is

desi gned t o f uncti on wi t h a par al l el resonant

fundamental or third-overtone crystal. The 80C186 and

80C188 microprocessors use a crystal frequency that

is twice the processor frequency. AMD does not

recommend that you replace a crystal with an LC or RC

equivalent for any member of the Am186 family.

The X1 and X2 signals are connected to an internal

inverting amplifier (oscillator) that provides, along with

the external feedback loading, the necessary phase

shift (Figure 1 on page 2). In such a positive feedback

circuit, the inverting amplifier has an output signal (X2)

180 degrees out of phase of the input signal (X1). The

external feedback network provides an additional 180

degree phase shift. In an ideal system, the input to X1

has 360 or zero degrees of phase shift.

The external feedback network is designed to be as

close as possible to ideal. If the feedback network is not

providing necessary phase shift, negative feedback

dampens the output of the amplifier and negatively

affects the operation of the clock generator. Values for

the loading on X1 and X2 must be chosen to provide

the necessary phase shift and crystal operation.

Selecting a Crystal

When selecting a crystal, you should always specify the

load capacitance (C

L

). This value can cause variance in

the oscillation frequency from the desired specified value

(resonance). The load capacitance and the loading of the

feedback network have the following relationship:

C

L

= (( C

1

C

2

)/( C

1

+ C

2

)) + C

S

where C

S

is the stray capacitance of the circuit. Placing

the crystal and C

L

in series across the inverting

amplifier and tuning these values (C

1

, C

2

) allows the

crystal to oscillate at resonance. This relationship is

true for both fundamental and third-overtone operation.

Finally, there is a relationship between C

1

and C

2

. To

enhance the oscillation of the inverting amplifier, these

values must be offset with the larger load on the output

(X2). Equal values of these loads tend to balance the

poles of the inverting amplifier.

The characteristics of the inverting amplifier set limits

on the following parameters for crystals:

ESR (Equivalent Series Resistance) ........... 40 Max

Drive Level .................................................. 1 mW Max

The recommended range of values for C1and C2 are

as follows:

C

1

............................................................. 15 pF 20%

C

2

............................................................. 22 pF 20%

You must determine the specific values for C

1

and C

2

.

The values are dependent on the characteristics of the

chosen crystal and board design. The C

1

and C

2

values include the stray capacitances of the design.

Figure 1 on page 2 shows the correct connection of the

oscillator configurations. Figure 1a shows the inverting

amplifier configuration. This is the equivalent circuitry

with the inverter integrated into the microcontroller.

Figure 1b shows the crystal configuration. The diagram

shows the correct connecti on for third-overtone

crystals. The fundamental mode crystals do not require

the L

1

or the 200-pF capacitor. Figure 1c shows the

recommended crystal mode based on the crystal

frequency. The 80C186 and 80C188 microprocessors

use a crystal twice the CPU frequency and can use

either fundamental or third-overtone mode crystals,

depending on the CPU frequency.

2 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

Figure 1. Oscillator Configurations and Recommended Crystal Modes

Crystal

200 pF

L

11

Notes:

1. Use for third overtone mode crystals. Fundamental mode

crystals do not use L1 or the 200-pF capacitor.

XTAL Frequency L1 Value (Max)

20 MHz 12 H 20%

25 MHz 8.2 H 20%

32 MHz 4.7 H 20%

40 MHz 3.0 H 20%

50 MHz 2.2 H 20%

X1

X2

b. Crystal Configuration

a. Inverting Amplifier Configuration

C

1

C

2

Crystal

C

1

C

2

Microcontroller

20 MHz 25 MHz 32 MHz 40 MHz 50 MHz

Fundamental

Third Overtone

c. Recommended Crystal Mode

80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 3

A M E N D M E N T

SWITCHING CHARACTERISTICS OVER INDUSTRIAL OPERATING RANGE AT 20 MHZ

This section includes the following timings and timing waveforms at 20 MHz:

n Read-Cycle Timings on page 4

n Read-Cycle Waveforms on page 5

n Write-Cycle Timings on page 6

n Write-Cycle Waveforms on page 7

n Interrupt Acknowledge Cycle Timings on page 8

n Interrupt Acknowledge Cycle Waveforms on page 9

n Software Halt Cycle Timings on page 10

n Software Halt Cycle Waveforms on page 11

n Clock Timings on page 12

n Clock Waveforms on page 13

n Ready, Peripheral, and Queue Status Timings on page 14

n Synchronous Read (SRDY) Waveforms on page 14

n Asynchronous Ready (ARDY) Waveforms on page 15

n Peripheral and Queue Status Waveforms on page 15

n RESET and HOLD/HLDA Timings on page 16

n RESET Waveforms on page 16

n HOLD/HLDA Waveforms (Entering HOLD) on page 17

n HOLD/HLDA Waveforms (Leaving HOLD) on page 17

4 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

Read-Cycle Timings

1

T

A-IND

=40C to +85C, V

CC

=5 V 10%

Notes:

1. All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with

C

L

= 50100 pF (1020 MHz). For AC tests, input V

IL

= 0.45 V and V

IH

= 2.4 V, except at X1 where V

IH

= V

CC

0.5 V.

Preliminary

Parameter 20 MHz

# Symbol Description Min Max Unit

General Timing Requirements (listed more than once)

1 t

DVCL

Data in Setup (A/D) 10 ns

2 t

CLDX

Data in Hold (A/D) 3 ns

General Timing Responses (listed more than once)

3 t

CHSV

Status Active Delay 3 29 ns

4 t

CLSH

Status Inactive Delay 3 29 ns

5 t

CLAV

Address Valid Delay 3 25 ns

6 t

CLAX

Address Hold 0 ns

7 t

CLDV

Data Valid Delay 3 25 ns

8 t

CHDX

Status Hold Time 10 ns

9 t

CHLH

ALE Active Delay 20 ns

10 t

LHLL

ALE Width t

CLCL

15 = 35 ns

11 t

CHLL

ALE Inactive Delay 20 ns

12 t

AVLL

Address Valid to ALE Low

2

2. Equal loading.

t

CLCH

10 = 10 ns

13 t

LLAX

Address Hold from ALE Inactive

2

t

CHCL

10 = 10 ns

14 t

AVCH

Address Valid to Clock High 0 ns

15 t

CLAZ

Address Float Delay t

CLAX

= 0 17 ns

16 t

CLCSV

Chip-Select Active Delay 3 25 ns

17 t

CXCSX

Chip-Select Hold from Command Inactive

2

t

CLCH

10 = 10 ns

18 t

CHCSX

Chip-Select Inactive Delay 3 20 ns

19 t

DXDL

DEN Inactive to DT/R Low 0 ns

20 t

CVCTV

Control Active Delay 1

3

3. DEN, INTA, WR.

3 22 ns

21 t

CVDEX

DEN Inactive Delay 3 22 ns

22 t

CHCTV

Control Active Delay 2

3

3 22 ns

23 t

CLLV

LOCK Valid/Invalid Delay 3 22 ns

Timing Responses (Read Cycle)

24 t

AZRL

Address Float to RD Active 0 ns

25 t

CLRL

RD Active Delay 3 27 ns

26 t

RLRH

RD Pulse Width 2t

CLCL

20 = 80 ns

27 t

CLRH

RD Inactive Delay 3 25 ns

28 t

RHLH

RD Inactive to ALE High

2

t

CLCH

10 = 10 ns

29 t

RHAV

RD Inactive to Address Active

2

t

CLCL

15 = 35 ns

80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 5

A M E N D M E N T

Read-Cycle Waveforms

(Note 4)

(Note 5)

(Note 1)

LCS, MCS, UCS, PCS

(Note 2)

Notes:

1. Status inactive in state preceding t

4

.

2. If latched, A1 and A2 are selected instead of PCS5 and PCS6; only t

CLCSV

is applicable.

3. For write cycle followed by read cycle.

4. t

1

of next bus cycle.

5. Changes in t-state preceding next bus cycle if followed by write.

BHE/RFSH

A19A16

BHE/RFSH S6S3

A7A0

Data

(Note 3)

t

1

t

2

t

3

t

4

t

W

Status

1

2

3 4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20 21

22

23

24

23

22

25

26

27

28

29

CLKOUT

S2S0

BHE/RFSH

A19/S6A16/S3

ALE

AD7AD0

(80C188 only)

A15A8

Data

RD

LOCK

DT/R

DEN

AD15AD8

(80C186 only)

AD15A8

(80C188 only)

6 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

Write-Cycle Timings

1

T

A-IND

= 40C to + 85C, V

CC

= 5 V 10%

Notes:

1. All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with

C

L

= 50100 pF (1020 MHz). For AC tests, input V

IL

= 0.45 V and V

IH

= 2.4 V, except at X1 where V

IH

= V

CC

0.5 V.

Preliminary

Parameter 20 MHz

# Symbol Description Min Max Unit

General Timing Responses (listed more than once)

3 t

CHSV

Status Active Delay 3 29 ns

4 t

CLSH

Status Inactive Delay 3 29 ns

5 t

CLAV

Address Valid Delay 3 25 ns

6 t

CLAX

Address Hold 0 ns

7 t

CLDV

Data Valid Delay 3 25 ns

8 t

CHDX

Status Hold Time 10 ns

9 t

CHLH

ALE Active Delay 20 ns

10 t

LHLL

ALE Width t

CLCL

15 = 35 ns

11 t

CHLL

ALE Inactive Delay 20 ns

12 t

AVLL

Address Valid to ALE Low

2

2. Equal loading.

t

CLCH

10 = 10 ns

13 t

LLAX

Address Hold from ALE Inactive

2

t

CHCL

10 = 10 ns

14 t

AVCH

Address Valid to Clock High 0 ns

16 t

CLCSV

Chip-Select Active Delay 3 25 ns

17 t

CXCSX

Chip-Select Hold from Command Inactive

2

t

CLCH

10 = 10 ns

18 t

CHCSX

Chip-Select Inactive Delay 3 20 ns

19 t

DXDL

DEN Inactive to DT/R Low 0 ns

20 t

CVCTV

Control Active Delay 1

3

3. DEN, INTA, WR.

3 22 ns

23 t

CLLV

LOCK Valid/Invalid Delay 3 22 ns

Timing Responses (Write Cycle)

30 t

CLDOX

Data Hold Time 3 ns

31 t

CVCTX

Control Inactive Delay

3

3 22 ns

32 t

WLWH

WR Pulse Width 2t

CLCL

20 = 80 ns

33 t

WHLH

WR Inactive to ALE High

2

t

CLCH

14 = 6 ns

34 t

WHDX

Data Hold after WR

2

t

CLCL

15 = 35 ns

35 t

WHDEX

WR Inactive to DEN Inactive

2

t

CLCH

10 = 10 ns

80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 7

A M E N D M E N T

Write-Cycle Waveforms

(Note 4)

(Note 5)

(Note 1)

CLKOUT

Notes:

1. Status inactive in state preceding t

4

.

2. If latched, A1 and A2 are selected instead of PCS5 and PCS6; only t

CLCSV

is applicable.

3. For write cycle followed by read cycle.

4. t

1

of next bus cycle.

5. Changes in t-state preceding next bus cycle if followed by read, INTA, or halt.

BHE/RFSH

A19A16

BHE/RFSH S6S3

A15A8

D15D8

(Note 3)

t

1

t

2

t

3

t

4

t

W

Status

3

4

5

7

6

8

9

10

11

12

13

33

14

16

20

32

31

30

34

17

35

18

20

19

22

23

23

22

31

LOCK

DT/R

DEN

LCS, MCS, UCS,

PCS (Note 2)

WR

AD15AD8

(80C186 only)

ALE

S2S0

A15A8

(80C188 only)

A7A0

D7D0

AD7AD0

BHE/RFSH

A19/S6A16/S3

A15A8

8 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

Interrupt Acknowledge Cycle Timings

1

T

A

= 40C to +85C, V

CC

= 5 V 10%

Notes:

1. All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with

C

L

= 50200 pF (10 MHz) and C

L

= 50100 pF (12.520 MHz). For AC tests, input V

IL

= 0.45 V and V

IH

= 2.4 V, except at X1

where V

IH

= V

CC

0.5 V.

Preliminary

Parameter 20 MHz

# Symbol Description Min Max Unit

80C186 General Timing Requirements (listed more than once)

1 t

DVCL

Data in Setup (A/D) 10 ns

2 t

CLDX

Data in Hold (A/D) 3 ns

80C186 General Timing Responses (listed more than once)

3 t

CHSV

Status Active Delay 3 29 ns

4 t

CLSH

Status Inactive Delay 3 29 ns

5 t

CLAV

Address Valid Delay 3 25 ns

6 t

CLAX

Address Hold 0 ns

7 t

CLDV

Data Valid Delay 3 25 ns

8 t

CHDX

Status Hold Time 10 ns

9 t

CHLH

ALE Active Delay 20 ns

10 t

LHLL

ALE Width t

CLCL

15 = 35 ns

11 t

CHLL

ALE Inactive Delay 20 ns

12 t

AVLL

Address Valid to ALE Low

2

2. Equal loading.

t

CLCH

10 = 10 ns

13 t

LLAX

Address Hold from ALE Inactive

2

t

CHCL

10 = 10 ns

14 t

AVCH

Address Valid to Clock High 0 ns

15 t

CLAZ

Address Float Delay t

CLAX

= 0 17 ns

19 t

DXDL

DEN Inactive to DT/R Low

2

0 ns

20 t

CVCTV

Control Active Delay 1

3

3. DEN, INTA, WR.

3 22 ns

21 t

CVDEX

DEN Inactive Delay (Non-Write Cycles) 3 22 ns

22 t

CHCTV

Control Active Delay 2

3

3 22 ns

23 t

CLLV

LOCK Valid/Invalid Delay 3 22 ns

31 t

CVCTX

Control Inactive Delay

3

3 22 ns

80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 9

A M E N D M E N T

Interrupt Acknowledge Cycle Waveforms

(Note 6)

(Note 1)

LOCK

Notes:

1. Status inactive in state preceding t

4

.

2. The data hold time lasts only until INTA goes inactive, even if the INTA transition occurs prior to t

CLDX

(min).

3. INTA occurs one clock later in Slave mode.

4. For write cycle followed by interrupt acknowledge cycle.

5. LOCK is active upon t

1

of the first interrupt acknowledge cycle and inactive upon t

2

of the second interrupt acknowledge cycle.

6. Changes in t-state preceding next bus cycle if followed by write.

BHE

A19A16

BHE, S6S3

PTR

(Note 2)

t

1

t

2

t

3

t

4

t

W

Status

(Note 3)

INTA

3 4

8

7

6

5

13

2

1

9

(Note 4)

15

11

12

19

23

22

31

21

20

20

23

22

14

10

CLKOUT

S2S0

BHE (80C186)

A19/S6A16/S3

ALE

DEN

DT/R

A15A8

(80C188)

AD15AD0 (80C186)

AD7AD0 (80C188)

(Note 5)

10 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

Software Halt Cycle Timings

1

T

A

= 40C to 85C, V

CC

= 5 V 10%

Notes:

1. All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with

C

L

= 50200 pF (10 MHz) and C

L

= 50100 pF (12.520 MHz). For AC tests, input V

IL

= 0.45 V and V

IH

= 2.4 V, except at X1

where V

IH

= V

CC

0.5 V.

Preliminary

Parameter 20 MHz

# Symbol Description Min Max Unit

80C186 General Timing Responses (listed more than once)

3 t

CHSV

Status Active Delay 3 29 ns

4 t

CLSH

Status Inactive Delay 3 29 ns

5 t

CLAV

Address Valid Delay 3 25 ns

9 t

CHLH

ALE Active Delay 20 ns

10 t

LHLL

ALE Width t

CLCL

15 = 35 ns

11 t

CHLL

ALE Inactive Delay 20 ns

19 t

DXDL

DEN Inactive to DT/R Low

2

2. Equal loading.

0 ns

22 t

CHCTV

Control Active Delay 2

3

3. DEN, INTA, WR.

3 22 ns

80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 11

A M E N D M E N T

Software Halt Cycle Waveforms

CLKOUT

S2S0

A19/S6A16/S3,

AD15AD8/A15A8,

AD7AD0

ALE

DEN

DT/R

Notes:

1. For write cycle followed by halt cycle.

(Note 1)

t

1

t

2

t

i

t

i

Status

Invalid Address

3

4

5

10

9 11

19

22

12 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

Clock Timings

1

T

A-IND

= 40C to +85C, V

CC

= 5 V 10%

Notes:

1. All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with

C

L

= 50100 pF (1020 MHz). For AC tests, input V

IL

= 0.45 V and V

IH

= 2.4 V, except at X1 where V

IH

= V

CC

0.5 V.

Preliminary

Parameter 20 MHz

# Symbol Description Min Max Unit

CLKIN Requirementsmeasurements taken with external clock input to X1 and X2 not connected (float)

36 t

CKIN

CLKIN Period 25 ns

37 t

CLCK

2

2. t

CLCK

and t

CHCK

(CLKIN Low and High times) should not have a duration less than 40% of t

CKIN

.

CLKIN Low Time 1.5 V

3

3. Tested under worst case conditions: V

CC

= 5.5 V @ 20 MHz, T

A

= 70C.

7 ns

38 t

CHCK

2

CLKIN High Time 1.5 V

3

8 ns

39 t

CKHL

CLKIN Fall Time 3.5 1.0 V 5 ns

40 t

CKLH

CLKIN Rise Time 1.0 3.5 V 5 ns

CLKOUT Timing

41 t

CICO

CLKIN to CLKOUT Skew 17 ns

42 t

CLCL

CLKOUT Period 50 ns

43

t

CLCH

CLKOUT Low Time

C

L

= 50 pF

4

4. Not tested.

0.5 t

CLCL

5 = 20

ns

C

L

= 100 pF

3

0.5 t

CLCL

7 = 18

44

t

CHCL

CLKOUT High Time

C

L

= 50 pF

4

0.5 t

CLCL

5 = 20

ns

C

L

= 100 pF

5

5. Tested under worst case conditions: V

CC

= 4.5 V @ 20 MHz, T

A

= 0C.

0.5 t

CLCL

7 = 18

45

t

CH1CH2

CLKOUT Rise Time

1.03.5 V

8 ns

46

t

CL2CL1

CLKOUT Fall Time

3.5 1.0 V

8 ns

80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 13

A M E N D M E N T

Clock Waveforms

X1

36

37

38

46

44

43

45

42

40 39

41

CLKOUT

14 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

Synchronous Read (SRDY) Waveforms

Ready, Peripheral, and Queue Status Timings

1

T

A-IND

= 40C to +85C, V

CC

= 5 V 10%

Notes:

1. All timings are measured at 1.5 V and 100-pF loading on CLKOUT unless otherwise noted. All output test conditions are with

C

L

= 50100 pF (1020 MHz). For AC tests, input V

IL

= 0.45 V and V

IH

= 2.4 V, except at X1 where V

IH

= V

CC

0.5 V.

Preliminary

Parameter 20 MHz

# Symbol Description Min Max Unit

Ready and Peripheral Timing Requirements

47 t

SRYCL

SRDY Transition Setup Time

2

2. To guarantee proper operation.

15 ns

48 t

CLSRY

SRDY Transition Hold Time

2

10 ns

49 t

ARYCH

ARDY Res. Transition Setup Time

3

3. To guarantee recognition at clock edge.

10 ns

50 t

CLARX

ARDY Active Hold Time

2

10 ns

51 t

ARYCHL

ARDY Inactive Holding Time 10 ns

52 t

ARYLCL

ARDY Setup Time

2

20 ns

53 t

INVCH

Peripheral Setup

3

: INTx, NMI, TMR IN, TEST/BUSY 15 ns

54 t

INVCL

DRQ0, DRQ1 Setup Time

3

15 ns

Peripheral and Queue Status Timing Responses

55 t

CLTMV

Timer Output Delay 22 ns

56 t

CHQSV

Queue Status Delay 23 ns

t

W

or t

2

or t

1

t

W

or t

2

t

W

or t

3

t

4

CLKOUT

SRDY

47

48

80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 15

A M E N D M E N T

Asynchronous Ready (ARDY) Waveforms

Peripheral and Queue Status Waveforms

CLKOUT

ARDY

(Normally Not

Ready System)

ARDY

Normally Ready

System)

t

W

or t

2

or t

1

t

W

or t

2

t

W

or t

3

t

4

49 50

51

49

52

50

CLKOUT

INT3INT0, NMI,

TEST, TMR IN

DRQ0, DRQ1

TMR OUT

QS0, QS1

53

54

55

56

16 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

RESET Waveforms

RESET and HOLD/HLDA Timings

1

T

A-IND

= 40C to +85C, V

CC

= 5 V 10%

Notes:

1. All timings are measured at 1.5 V and 100 pF loading on CLKOUT unless otherwise noted. All output test conditions are with

C

L

= 50100 pF (1020 MHz). For AC tests, input V

IL

= 0.45 V and V

IH

= 2.4 V, except at X1 where V

IH

= V

CC

0.5 V.

Preliminary

Parameter 20 MHz

# Symbol Description Min Max Unit

RESET and HOLD/HLDA Timing Requirements

57 t

RESIN

RES Setup 10 ns

58 t

HVCL

HOLD Setup

2

2. To guarantee recognition at next clock.

10 ns

15 t

CLAZ

Address Float Delay 0 17 ns

5 t

CLAV

Address Valid Delay 3 25 ns

RESET and HOLD/HLDA Timing Requirements

61 t

CLRO

Reset Delay 22 ns

62 t

CLHAV

HLDA Valid Delay 3 22 ns

63 t

CHCZ

Command Lines Float Delay 25 ns

64 t

CHCV

Command Lines Valid Delay (after Float) 25 ns

X1

RES

CLKOUT

RESET

57

61

57

61

80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment 17

A M E N D M E N T

HOLD/HLDA Waveforms (Entering HOLD)

HOLD/HLDA Waveforms (Leaving HOLD)

CLKOUT

HOLD

HLDA

AD15AD8/A15A8,

AD7AD0, DEN

A19/S6A16/S3, RD,

WR, BHE/RFSH,

DT/R, S2S0, LOCK

t

4

or t

i

t

i

t

i

58

62

15

63

HOLD

CLKOUT

HOLD

HLDA

AD15AD8/A15A8,

AD7AD0, DEN

A19/S6A16/S3, RD,

WR, BHE/RFSH, DT/R,

S2S0, LOCK

t

i

t

4

t

i

t

1

t

i

58

62

5

64

18 80C186 and 80C188 Integrated 16-Bit Microprocessors Data Book Amendment

A M E N D M E N T

Trademarks

1998 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Am186, Am188, and E86 are trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

You might also like

- Basic Pic16/17 Oscillator Design: By: Dan MatthewsDocument4 pagesBasic Pic16/17 Oscillator Design: By: Dan Matthewsandi2k9No ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- HCTL 2017Document12 pagesHCTL 2017ivancho1070No ratings yet

- LC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778Document12 pagesLC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778tarpinoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Adc 0804Document41 pagesAdc 0804AndySilvandNo ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- DS1302 Trickle-Charge Timekeeping ChipDocument13 pagesDS1302 Trickle-Charge Timekeeping ChipPravin MevadaNo ratings yet

- Adc12j2700 PDFDocument95 pagesAdc12j2700 PDFmedellin77No ratings yet

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Ca3306 (A, C)Document17 pagesCa3306 (A, C)notaden1849No ratings yet

- Microchip MCP7940M Low Cost I2C Real Time Clock Calendar With SRAMDocument39 pagesMicrochip MCP7940M Low Cost I2C Real Time Clock Calendar With SRAM邱子威No ratings yet

- 24 LC 16Document32 pages24 LC 16Jos RoNo ratings yet

- DS1307 Datasheet FullDocument15 pagesDS1307 Datasheet FulllamanzanadeadanNo ratings yet

- Features: Half-Bridge Gate DriverDocument19 pagesFeatures: Half-Bridge Gate DriverLakshmana Rao VNo ratings yet

- DS12885 Ds12c887aDocument22 pagesDS12885 Ds12c887aopooyoNo ratings yet

- Lvds Signal IntegrityDocument10 pagesLvds Signal IntegritySaipraveen KumarNo ratings yet

- 3-Phase Brushless DC Motor Controller/Driver With Back-Emf SensingDocument12 pages3-Phase Brushless DC Motor Controller/Driver With Back-Emf SensingPero01No ratings yet

- Contactor - SchniderDocument28 pagesContactor - SchniderPramod DixitNo ratings yet

- 24LC02BDocument26 pages24LC02Bjab_arx1No ratings yet

- AN437 Application NoteDocument20 pagesAN437 Application NoteEdgar MuñozNo ratings yet

- Tda 10021 DatasheetDocument17 pagesTda 10021 DatasheetWilly DacoNo ratings yet

- Digital Potentiometer AD8400 8402 8403Document32 pagesDigital Potentiometer AD8400 8402 8403Ozi ---No ratings yet

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocument16 pagesμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKudo ShinichiNo ratings yet

- Simple FSKDocument6 pagesSimple FSKFaten AliNo ratings yet

- LTC 1661Document14 pagesLTC 1661mneagu123No ratings yet

- 24lc08 EepromDocument27 pages24lc08 EepromIsmael Minchola CarhuasNo ratings yet

- DS1307 64 X 8 Serial Real-Time Clock: FeaturesDocument8 pagesDS1307 64 X 8 Serial Real-Time Clock: FeaturesCarlos ArangurenNo ratings yet

- Getting Precise With MSP430 Sigma-Delta ADC Peripherals: Vincent Chan MSP430 Business Development Manager TI AsiaDocument33 pagesGetting Precise With MSP430 Sigma-Delta ADC Peripherals: Vincent Chan MSP430 Business Development Manager TI AsiaStefanGLNo ratings yet

- Real-Time-Clock Selection and Optimization: System ConsiderationsDocument7 pagesReal-Time-Clock Selection and Optimization: System ConsiderationsmadhuvariarNo ratings yet

- Ecodial ReportDocument28 pagesEcodial ReportEngAhmed0% (1)

- Sa PM31P PDFDocument122 pagesSa PM31P PDFJose LuisNo ratings yet

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocument16 pagesμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKasi ChinnaNo ratings yet

- DS1320Document13 pagesDS1320Annelise Grottker de OliveiraNo ratings yet

- 24 LC 16 BDocument12 pages24 LC 16 BAnonymous UxrPsIVNo ratings yet

- TCM29C23, TCM129C23 Variable-Frequency PCM or DSP Interface: DescriptionDocument21 pagesTCM29C23, TCM129C23 Variable-Frequency PCM or DSP Interface: DescriptionmorlockbrNo ratings yet

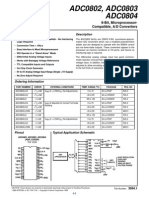

- ADC0802, ADC0803 ADC0804: Features DescriptionDocument17 pagesADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataNo ratings yet

- SN 74 HC 191Document17 pagesSN 74 HC 191Cristobal Silva SanhuezaNo ratings yet

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesAn TrìnhNo ratings yet

- Ns16C552, Pc16552D: Pc16552D Dual Universal Asynchronous Receiver/Transmitter With FifosDocument24 pagesNs16C552, Pc16552D: Pc16552D Dual Universal Asynchronous Receiver/Transmitter With FifosNeimar HahmeierNo ratings yet

- 93lc56 DatasheetDocument36 pages93lc56 DatasheetJose Angel Camara SantosNo ratings yet

- Data SheetDocument14 pagesData SheetChathur Sajeewan BasuruNo ratings yet

- 16Mb H-Die SDRAM Specification: Revision 1.5 August 2004Document12 pages16Mb H-Die SDRAM Specification: Revision 1.5 August 2004AleksandarPetrovicNo ratings yet

- AtoD Converter System S12 NewDocument9 pagesAtoD Converter System S12 NewMina HannaNo ratings yet

- MLX91205 DatasheetDocument14 pagesMLX91205 DatasheetRicardo ReisNo ratings yet

- Installation Calculation Report: New - Project FullDocument28 pagesInstallation Calculation Report: New - Project FullDino MahmutovićNo ratings yet

- 93xx86 Varias VersionesDocument28 pages93xx86 Varias VersionesPosada Burgueño CarlosNo ratings yet

- ADC0809CCNDocument16 pagesADC0809CCNFrancesca Castelar BenalcazarNo ratings yet

- Two-Wire Serial EEPROM: FeaturesDocument28 pagesTwo-Wire Serial EEPROM: FeaturesdobsrdjanNo ratings yet

- Chassis LA6-A LA6A Mono Manual de ServicioDocument26 pagesChassis LA6-A LA6A Mono Manual de Serviciojavier258No ratings yet

- 128 K X 8 Ultimate CMOS SRAM: Block DiagramDocument10 pages128 K X 8 Ultimate CMOS SRAM: Block DiagramDeepa DevarajNo ratings yet

- Panasonic+Ct 36l13g+Ct 32sl13g+Ct 36sc13g+Ct 32sc13g+Ct 3663gDocument187 pagesPanasonic+Ct 36l13g+Ct 32sl13g+Ct 36sc13g+Ct 32sc13g+Ct 3663gwonderboy39No ratings yet

- DS1307Document13 pagesDS1307Ezaú TalamantesNo ratings yet

- Datasheet SN74HC04 - Hex InversorDocument16 pagesDatasheet SN74HC04 - Hex InversorPablo CarvalhoNo ratings yet

- 93C66 Microwire EepromDocument13 pages93C66 Microwire EepromadrianramonNo ratings yet

- SSDAC - MaintainenceDocument16 pagesSSDAC - MaintainenceVikas Srivastav100% (3)

- 1632 CV 100Document22 pages1632 CV 100Bruno FascendiniNo ratings yet

- RouzbehAmini PHD DissertationDocument218 pagesRouzbehAmini PHD DissertationCristian BandilaNo ratings yet

- ArmandMollaGarciaTFG v5Document89 pagesArmandMollaGarciaTFG v5Cristian BandilaNo ratings yet

- ThesisDocument186 pagesThesisCristian BandilaNo ratings yet

- 10 - Barrington-Brown - Air Cored vs. Rod MagnetorquerDocument10 pages10 - Barrington-Brown - Air Cored vs. Rod MagnetorquerCristian BandilaNo ratings yet

- TesiDocument57 pagesTesiCristian BandilaNo ratings yet

- Panasonic Sla Handbook On TransportationDocument5 pagesPanasonic Sla Handbook On TransportationCristian BandilaNo ratings yet

- Celani2021 Article GainSelectionForAttitudeStabilDocument10 pagesCelani2021 Article GainSelectionForAttitudeStabilCristian BandilaNo ratings yet

- Leap Pstart: Handy Pic WriterDocument1 pageLeap Pstart: Handy Pic WriterCristian BandilaNo ratings yet

- Discontinued Product: Chopper-Stabilized Omnipolar Hall-Effect SwitchesDocument13 pagesDiscontinued Product: Chopper-Stabilized Omnipolar Hall-Effect SwitchesCristian BandilaNo ratings yet

- Analysis and Design of Integrated Magnetorquer Coils For AttitudeDocument7 pagesAnalysis and Design of Integrated Magnetorquer Coils For AttitudeCristian BandilaNo ratings yet

- fakhariCES5 8 2010Document10 pagesfakhariCES5 8 2010Cristian BandilaNo ratings yet

- 2iccas2005 Paper 377Document5 pages2iccas2005 Paper 377Cristian BandilaNo ratings yet

- Inverter IR2000 PDFDocument2 pagesInverter IR2000 PDFCristian BandilaNo ratings yet

- D Link DCH Z110 - 120 Manual PDFDocument13 pagesD Link DCH Z110 - 120 Manual PDFCristian BandilaNo ratings yet

- Advanced Li+ Battery-Pack Protectors: General Description FeaturesDocument16 pagesAdvanced Li+ Battery-Pack Protectors: General Description FeaturesCristian BandilaNo ratings yet

- LEAP PSTART Handy PIC WriterDocument1 pageLEAP PSTART Handy PIC WriterCristian BandilaNo ratings yet

- Mil PRF 32383 - 3Document9 pagesMil PRF 32383 - 3Cristian BandilaNo ratings yet

- Ta Di Misura PDFDocument44 pagesTa Di Misura PDFCristian BandilaNo ratings yet

- UHP 2500 Spec PDFDocument7 pagesUHP 2500 Spec PDFCristian BandilaNo ratings yet

- DR Ups40 Spec 1109738 PDFDocument4 pagesDR Ups40 Spec 1109738 PDFCristian BandilaNo ratings yet

- MQ48D Controller Web and SNMP Management Operating Manual PDFDocument14 pagesMQ48D Controller Web and SNMP Management Operating Manual PDFCristian Bandila100% (1)

- MQ48D Controller Web and SNMP Management Operating Manual PDFDocument14 pagesMQ48D Controller Web and SNMP Management Operating Manual PDFCristian Bandila100% (1)

- Ta Di Misura PDFDocument44 pagesTa Di Misura PDFCristian BandilaNo ratings yet

- Tahmid ZCDDocument3 pagesTahmid ZCDCristian BandilaNo ratings yet

- Tahmid's Blog: Ulteriori Informazioni OKDocument8 pagesTahmid's Blog: Ulteriori Informazioni OKCristian BandilaNo ratings yet