Professional Documents

Culture Documents

Tps 54628

Uploaded by

fet_50Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tps 54628

Uploaded by

fet_50Copyright:

Available Formats

Vout( 50mV/div)

Iout( 2A/div)

100us/div

TPS54628

T P S 5 4 6 2 8

www.ti.com SLVSBW5 APRIL 2013

4 .5 V to 1 8 V I n p u t, 6 - A S y n ch r on ou s S te p - D own C on v e r te r with E co- mod e

C h e ck for S amp le s : T P S 5 4 6 2 8

1 FE A T URE S D E S C RI P T I ON

The TPS54628 is an adaptive on-time D-CAP2

2 3 D - C A P 2 Mod e E n able s Fas t T r an s ie n t

mode synchronous buck converter. The TPS54628

Re s p on s e

enables system designers to complete the suite of

Low Ou tp u t Rip p le an d A llows C e r amic Ou tp u t

various end-equipment power bus regulators with a

C ap acitor

cost effective, low component count, low standby

current solution. The main control loop for the Wid e V

I N

I n p u t V oltage Ran ge : 4 .5 V to 1 8 V

TPS54628 uses the D-CAP2 mode control that

Ou tp u t V oltage Ran ge : 0.76 V to 5 .5 V

provides a fast transient response with no external

High ly E fficie n t I n te gr ate d FE T s Op timize d

compensation components. The adaptive on-time

for Lowe r D u ty C y cle A p p lication s

control supports seamless transition between PWM

36 m (High S id e ) an d 2 8 m (Low S id e )

mode at higher load conditions and Eco-mode

operation at light loads. Eco-mode allows the

High E fficie n cy , le s s th an 1 0 A at s h u td own

TPS54628 to maintain high efficiency during lighter

High I n itial Ban d gap Re fe r e n ce A ccu r acy

load conditions. The TPS54628 also has a proprietary

A d ju s table S oft S tar t

circuit that enables the device to adopt to both low

equivalent series resistance (ESR) output capacitors, P r e - Bias e d S oft S tar t

such as POSCAP or SP-CAP, and ultra-low ESR

6 5 0- kHz S witch in g Fr e qu e n cy (f

S W

)

ceramic capacitors. The device operates from 4.5-V

C y cle By C y cle Ov e r C u r r e n t Limit

to 18-V VIN input. The output voltage can be

programmed between 0.76 V and 5.5 V. The device A u to- S kip E co- mod e for High E fficie n cy at

also features an adjustable soft start time. The

Ligh t Load

TPS54628 is available in the 8-pin DDA package,

and designed to operate from 40C to 85C.

A P P LI C A T I ONS

Wid e Ran ge of A p p lication s for Low V oltage

S y s te m

D igital T V P owe r S u p p ly

High D e fin ition Blu - r ay D is c P lay e r s

Ne twor kin g Home T e r min al

D igital S e t T op Box (S T B)

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2D-CAP2, Eco-mode are trademarks of Texas Instruments.

3Blu-ray Disc is a trademark of Blu-ray Disc Association.

PRODUCTION DATA information is current as of publication date.

Copyright 2013, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

T P S 5 4 6 2 8

SLVSBW5 APRIL 2013 www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

ORD E RI NG I NFORMA T I ON

(1 )

T RA NS P ORT

T

A

P A C KA GE

(2 ) (3)

ORD E RA BLE P A RT NUMBE R P I N

ME D I A

TPS54628DDA Tube

40C to 85C DDA 8

TPS54628DDAR Tape and Reel

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(3) All package options have Cu NIPDAU lead/ball finish.

A BS OLUT E MA XI MUM RA T I NGS

over operating free-air temperature range (unless otherwise noted)

(1)

V A LUE

UNI T

MI N MA X

VIN, EN 0.3 20

VBST 0.3 26

VBST (10 ns transient) 0.3 28

Input voltage range VBST (vs SW) 0.3 6.5 V

VFB, SS 0.3 6.5

SW 2 20

SW (10 ns transient) 3 22

VREG5 0.3 6.5

Output voltage range V

GND 0.3 0.3

Voltage from GND to thermal pad, V

diff

0.2 0.2 V

Human Body Model (HBM) 2 kV

Electrostatic discharge

Charged Device Model (CDM) 500 V

Operating junction temperature, T

J

40 150

C

Storage temperature, T

stg

55 150

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

T HE RMA L I NFORMA T I ON

T P S 5 4 6 2 8

T HE RMA L ME T RI C

(1 )

UNI T S

D D A (8 P I NS )

JA

Junction-to-ambient thermal resistance 43.5

JCtop

Junction-to-case (top) thermal resistance 49.4

JB

Junction-to-board thermal resistance 25.6

C/W

JT

Junction-to-top characterization parameter 7.4

JB

Junction-to-board characterization parameter 25.5

JCbot

Junction-to-case (bottom) thermal resistance 5.2

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

2 Copyright 2013, Texas Instruments Incorporated

Product Folder Links :TPS54628

T P S 5 4 6 2 8

www.ti.com SLVSBW5 APRIL 2013

RE C OMME ND E D OP E RA T I NG C OND I T I ONS

over operating free-air temperature range, (unless otherwise noted)

MI N MA X UNI T

V

IN

Supply input voltage range 4.5 18 V

VBST 0.1 24

VBST (10 ns transient) 0.1 27

VBST(vs SW) 0.1 6.0

SS 0.1 5.7

V

I

Input voltage range EN 0.1 18 V

VFB 0.1 5.5

SW 1.8 18

SW (10 ns transient) 3 21

GND 0.1 0.1

V

O

Output voltage range VREG5 0.1 5.7 V

I

O

Output Current range I

VREG5

0 5 mA

T

A

Operating free-air temperature 40 85 C

T

J

Operating junction temperature 40 150 C

E LE C T RI C A L C HA RA C T E RI S T I C S

over operating free-air temperature range, V

IN

= 12 V (unless otherwise noted)

P A RA ME T E R T E S T C OND I T I ONS MI N T YP MA X UNI T

S UP P LY C URRE NT

V

IN

current, T

A

= 25C, EN = 5 V,

I

VIN

Operating - non-switching supply current 950 1400 A

V

FB

= 0.8 V

I

VINSDN

Shutdown supply current V

IN

current, T

A

= 25C, EN = 0 V 3 10 A

LOGI C T HRE S HOLD

EN high-level input voltage EN 1.6 V

V

EN

EN low-level input voltage EN 0.6 V

R

EN

EN pin resistance to GND V

EN

= 12 V 200 400 800 k

V

FB

V OLT A GE A ND D I S C HA RGE RE S I S T A NC E

T

A

= 25C, V

O

= 1.05 V, I

O

= 10 mA, Eco-

772 mV

mode operation

T

A

= 25C, V

O

= 1.05 V, continuous mode

V

FBTH

V

FB

threshold voltage 757 765 773 mV

operation

T

A

= -40 to 85C, V

O

= 1.05 V, continuous

751 765 779 mV

mode operation

(1)

I

VFB

V

FB

input current V

FB

= 0.8 V, T

A

= 25C 0 0.15 A

V

RE G5

OUT P UT

T

A

= 25C, 6 V < V

IN

< 18 V,

V

VREG5

V

REG5

output voltage 5.2 5.5 5.7 V

0 < I

VREG5

< 5 mA

I

VREG5

Output current V

IN

= 6 V, V

REG5

= 4.0 V, T

A

= 25C 20 mA

V

OUT

D I S C HA RGE

R

DISCHG

V

OUT

discharge resistance EN = 0 V, SW = 0.5 V, T

A

= 25C 500 800

MOS FE T

High side switch resistance 25C, V

BST

- SW = 5.5 V 36 m

R

DS(on)

Low side switch resistance 25C 28 m

C URRE NT LI MI T

I

OCL

Current limit L out = 1.5 H

(1)

6.7 7.3 8.9 A

(1) Not production tested.

Copyright 2013, Texas Instruments Incorporated 3

Product Folder Links :TPS54628

T P S 5 4 6 2 8

SLVSBW5 APRIL 2013 www.ti.com

E LE C T RI C A L C HA RA C T E RI S T I C S (con tin u e d )

over operating free-air temperature range, V

IN

= 12 V (unless otherwise noted)

P A RA ME T E R T E S T C OND I T I ONS MI N T YP MA X UNI T

T HE RMA L S HUT D OWN

Shutdown temperature

(2)

165

T

SDN

Thermal shutdown threshold C

Hysteresis

(2)

35

ON- T I ME T I ME R C ONT ROL

t

ON

On time V

IN

= 12 V, V

O

= 1.05 V 150 ns

t

OFF(MIN)

Minimum off time T

A

= 25C, V

FB

= 0.7 V 260 310 ns

S OFT S T A RT

SS charge current V

SS

= 1 V 4.2 6 7.8 A

I

SS

SS discharge current V

SS

= 0.5 V 1.5 3.3 mA

HI C C UP A ND OV E R- V OLT A GE P ROT E C T I ON

V

OVP

Output OVP threshold OVP Detect (L > H) 125%

V

HICCUP

Output Hiccup threshold Hiccup detect (H > L) 65%

T

HICCUPDELAY

Output Hiccup delay To hiccup state 250 sec

T

HICCUPENDELAY

Output Hiccup Enable delay Relative to soft-start time x1.7

UV LO

Wake up V

REG5

voltage 3.45 3.75 4.05

UVLO UVLO threshold V

Hysteresis V

REG5

voltage 0.13 0.32 0.48

(2) Not production tested.

4 Copyright 2013, Texas Instruments Incorporated

Product Folder Links :TPS54628

EXPOSED

THERMAL PAD

TPS54628

DDA

HSOP8

VFB

2

1

EN

3

VREG5

VBST

7

SW

6

GND

5

8

VIN

4

SS

T P S 5 4 6 2 8

www.ti.com SLVSBW5 APRIL 2013

D E V I C E I NFORMA T I ON

D D A P A C KA GE

(T OP V I E W)

P I N FUNC T I ONS

P I N

D E S C RI P T I ON

NA ME NO.

EN 1 Enable input control. EN is active high and must be pulled up to enable the device.

VFB 2 Converter feedback input. Connect to output voltage with feedback resistor divider.

5.5 V power supply output. A capacitor (typical 1 F) should be connected to GND. VREG5 is not active

VREG5 3

when EN is low.

SS 4 Soft-start control. An external capacitor should be connected to GND.

Ground pin. Power ground return for switching circuit. Connect sensitive SS and VFB returns to GND at

GND 5

a single point.

SW 6 Switch node connection between high-side NFET and low-side NFET.

Supply input for the high-side FET gate drive circuit. Connect 0.1 F capacitor between VBST and SW

VBST 7

pins. An internal diode is connected between VREG5 and VBST.

VIN 8 Input voltage supply pin.

Exposed Thermal Thermal pad of the package. Must be soldered to achieve appropriate dissipation. Must be connected to

Back side

Pad GND.

Copyright 2013, Texas Instruments Incorporated 5

Product Folder Links :TPS54628

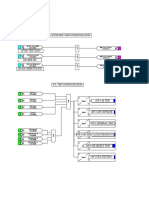

SW

VBST

EN

VFB

GND

VO

4

5

6

2

1

7

VIN

SS

VIN

VREG5

EN

Logic

SW

PGND

Protection

Logic

Ref

SS

UVLO

TSD

Softstart

SS

REF Ref

VREG5

8

VIN

Ceramic

Capacitor

3

SGND

SGND

PGND

PWM +

-

+

OCP

+

-

VREG5

XCON

VREG5

Control Logic

1 shot

ON

SW

PGND

ZC

+

-

+

- +25%

OV

+

-

-35%

HICCUP

UVLO

OV

HICCUP

T P S 5 4 6 2 8

SLVSBW5 APRIL 2013 www.ti.com

FUNC T I ONA L BLOC K D I A GRA M

6 Copyright 2013, Texas Instruments Incorporated

Product Folder Links :TPS54628

SS

FB

SS

t (ms) =

C6(nF) V 1.1 C6(nF) 0.765 1.1

=

I (A) 6

( )

( )

2

IN OUT OUT

OUT LL

IN

V V V

I

L fsw V

-

=

1

T P S 5 4 6 2 8

www.ti.com SLVSBW5 APRIL 2013

OV E RV I E W

The TPS54628 is a 6-A Eco-mode synchronous step-down (buck) converter with two integrated N-channel

MOSFETs. It operates using D-CAP2 mode control. The fast transient response of D-CAP2 control reduces

the output capacitance required to meet a specific level of performance. Proprietary internal circuitry allows the

use of low ESR output capacitors including ceramic and special polymer types.

D E T A I LE D D E S C RI P T I ON

P WM Op e r ation

The main control loop of the TPS54628 is an adaptive on-time pulse width modulation (PWM) controller that

supports a proprietary D-CAP2 mode control. D-CAP2 mode control combines constant on-time control with

an internal compensation circuit for pseudo-fixed frequency and low external component count configuration with

both low ESR and ceramic output capacitors. It is stable even with virtually no ripple at the output.

At the beginning of each cycle, the high-side MOSFET is turned on. This MOSFET is turned off after internal one

shot timer expires. This one shot is set by the converter input voltage, VIN, and the output voltage, VO, to

maintain a pseudo-fixed frequency over the input voltage range, hence it is called adaptive on-time control. The

one-shot timer is reset and the high-side MOSFET is turned on again when the feedback voltage falls below the

reference voltage. An internal ramp is added to reference voltage to simulate output ripple, eliminating the need

for ESR induced output ripple from D-CAP2 mode control.

P WM Fr e qu e n cy an d A d ap tiv e On - T ime C on tr ol

TPS54628 uses an adaptive on-time control scheme and does not have a dedicated on board oscillator. The

TPS54628 runs with a pseudo-constant frequency of 650 kHz by using the input voltage and output voltage to

set the on-time one-shot timer. The on-time is inversely proportional to the input voltage and proportional to the

output voltage; therefore, when the duty ratio is VOUT/VIN, the frequency is constant.

A u to- S kip E co- Mod e C on tr ol

The TPS54628 is designed with Auto-Skip Eco-mode to increase light load efficiency. As the output current

decreases from heavy load condition, the inductor current is also reduced and eventually comes to point that its

rippled valley touches zero level, which is the boundary between continuous conduction and discontinuous

conduction modes. The rectifying MOSFET is turned off when its zero inductor current is detected. As the load

current further decreases the converter run into discontinuous conduction mode. The on-time is kept almost the

same as is was in the continuous conduction mode so that it takes longer time to discharge the output capacitor

with smaller load current to the level of the reference voltage. The transition point to the light load operation

I

OUT(LL)

current can be calculated in Equation 1

(1)

S oft S tar t an d P r e - Bias e d S oft S tar t

The soft start function is adjustable. When the EN pin becomes high, 6A current begins charging the capacitor

which is connected from the SS pin to GND. Smooth control of the output voltage is maintained during start up.

The equation for the slow start time is shown in Equation 2. VFB voltage is 0.765 V and SS pin source current is

6 A.

(2)

The TPS54628 contains a unique circuit to prevent current from being pulled from the output during startup if the

output is pre-biased. When the soft-start commands a voltage higher than the pre-bias level (internal soft start

becomes greater than feedback voltage V

FB

), the controller slowly activates synchronous rectification by starting

the first low side FET gate driver pulses with a narrow on-time. It then increments that on-time on a cycle-by-

cycle basis until it coincides with the time dictated by (1-D), where D is the duty cycle of the converter. This

scheme prevents the initial sinking of the pre-bias output, and ensure that the out voltage (V

O

) starts and ramps

up smoothly into regulation and the control loop is given time to transition from pre-biased start-up to normal

mode operation.

Copyright 2013, Texas Instruments Incorporated 7

Product Folder Links :TPS54628

T P S 5 4 6 2 8

SLVSBW5 APRIL 2013 www.ti.com

Ou tp u t D is ch ar ge C on tr ol

TPS54628 discharges the output when EN is low, or the controller is turned off by the UVLO protection. The

internal low-side MOSFET is not turned on for the output discharge operation to avoid the possibility of causing

negative voltage at the output.

C u r r e n t P r ote ction

The output overcurrent protection (OCP) is implemented using a cycle-by-cycle valley detect control circuit. The

switch current is monitored by measuring the low-side FET switch voltage between the SW pin and GND. This

voltage is proportional to the switch current. To improve accuracy, the voltage sensing is temperature

compensated.

During the on time of the high-side FET switch, the switch current increases at a linear rate determined by V

IN

,

V

OUT

, the on-time and the output inductor value. During the on time of the low-side FET switch, this current

decreases linearly. The average value of the switch current is the load current I

OUT

. The TPS54628 constantly

monitors the low-side FET switch voltage, which is proportional to the switch current, during the low-side on-time.

If the measured voltage is above the voltage proportional to the current limit, an internal counter is incremented

per each SW cycle and the converter maintains the low-side switch on until the measured voltage is below the

voltage corresponding to the current limit at which time the switching cycle is terminated and a new switching

cycle begins. In subsequent switching cycles, the on-time is set to a fixed value and the current is monitored in

the same manner. If the over current condition exists for 7 consecutive switching cycles, the internal OCL

threshold is set to a lower level, reducing the available output current. When a switching cycle occurs where the

switch current is not above the lower OCL threshold, the counter is reset and the OCL limit is returned to the

higher value.

There are some important considerations for this type of over-current protection. The peak current is the average

load current plus one half of the peak-to-peak inductor current. The valley current is the average load current

minus one half of the peak-to-peak inductor current. Since the valley current is used to detect the over-current

threshold, the load current is higher than the over-current threshold. Also, when the current is being limited, the

output voltage tends to fall. When the VFB voltage becomes lower than 65% of the target voltage, the UVP

comparator detects it. If the under-voltage condition persists for 250 s, the device will shut down and re-start in

hiccup mode after 7 times the SS period. When the over current condition is removed, the output voltage will

return to the regulated value. This protection is non-latching.

Ov e r V oltage P r ote ction

TPS54628 detects over and under voltage conditions by monitoring the feedback voltage (VFB). This function is

enabled after approximately 1.7 x times the soft start time. When the feedback voltage becomes higher than

125% of the target voltage, the OVP comparator output goes high and both the high-side MOSFET driver and

the low-side MOSFET driver turn off. This function is non-latch operation.

UV LO P r ote ction

Undervoltage lock out protection (UVLO) monitors the voltage of the V

REG5

pin. When the V

REG5

voltage is lower

than UVLO threshold voltage, the TPS54628 is shut off. This protection is non-latching.

T h e r mal S h u td own

TPS54628 monitors the temperature of itself. If the temperature exceeds the threshold value (typically 165C),

the device is shut off. This is non-latch protection.

8 Copyright 2013, Texas Instruments Incorporated

Product Folder Links :TPS54628

1.020

1.030

1.040

1.050

1.060

1.070

1.080

0 5 10 15 20

V

O

U

T

-

O

u

t

p

u

t

V

o

l

t

a

g

e

(

V

)

V

IN

- Input Voltage (V)

Io=10mA

Io=1A

C005

I

OUT

= 10 mA

I

OUT

= 1 A

Vout( 50mV/div)

Iout( 2A/div)

100us/div

0

10

20

30

40

50

0 5 10 15 20

E

N

I

n

p

u

t

C

u

r

r

e

n

t

(

A

)

EN Input Voltage (V) C003

V

IN

= 18 V

1.000

1.025

1.050

1.075

1.100

0.0 1.0 2.0 3.0 4.0 5.0 6.0

V

O

U

T

-

O

u

t

p

u

t

V

o

l

t

a

g

e

(

V

)

I

OUT

- Output Current (A)

Vin=5V

Vin=12V

Vin=18V

C004

V

IN

= 5 V

V

IN

= 12 V

V

IN

= 18 V

0

200

400

600

800

1,000

1,200

1,400

50 0 50 100 150

I

C

C

-

S

u

p

p

l

y

C

u

r

r

e

n

t

(

A

)

T

J

Junction Temperature (C) C001

0

1

2

3

4

5

6

7

8

9

10

50 0 50 100 150

I

v

c

c

s

d

n

-

S

h

u

t

d

o

w

n

C

u

r

r

e

n

t

(

A

)

T

J

Junction Temperature (C) C002

T P S 5 4 6 2 8

www.ti.com SLVSBW5 APRIL 2013

T YP I C A L C HA RA C T E RI S T I C S

VIN = 12 V, T

A

= 25C (unless otherwise noted).

Figu r e 1 . S UP P LY C URRE NT v s JUNC T I ON T E MP E RA T URE Figu r e 2 . V I N S HUT D OWN C URRE NT v s

JUNC T I ON T E MP E RA T URE

Figu r e 3. E N C URRE NT v s E N V OLT A GE Figu r e 4 . 1 .05 - V OUT P UT V OLT A GE v s OUT P UT C URRE NT

Figu r e 5 . 1 .05 - V OUT P UT V OLT A GE v s I NP UT V OLT A GE Figu r e 6 . 1 .05 - V , LOA D T RA NS I E NT RE S P ONS E

Copyright 2013, Texas Instruments Incorporated 9

Product Folder Links :TPS54628

0

100

200

300

400

500

600

700

800

900

0.0 0.1 1.0 10.0

f

s

w

-

S

w

i

t

c

h

i

n

g

F

r

e

q

u

e

n

c

y

(

k

H

z

)

I

O

- Output Current (A)

Vo=1.05V

Vo=1.8V

Vo=3.3V

C011

V

O

= 1.05 V

V

O

= 1.8 V

V

O

= 3.3 V

0.750

0.755

0.760

0.765

0.770

0.775

0.780

50 0 50 100 150

V

F

B

V

o

l

t

a

g

e

(

V

)

T

J

Junction Temperature (C)

Io=10mA

Io=1A

C012

I

O

= 10 mA

I

O

= 1 A

400

450

500

550

600

650

700

750

800

850

900

0 5 10 15 20

f

s

w

-

S

w

i

t

c

h

i

n

g

F

r

e

q

u

e

n

c

y

(

k

H

z

)

V

IN

- Input Voltage (V)

Vo=1.05V

Vo=1.2V

Vo=1.5V

Vo=1.8V

Vo=2.5V

Vo=3.3V

Vo=5V

C010

V

O

= 1.05 V

V

O

= 1.2 V

V

O

= 1.5 V

V

O

= 1.8 V

V

O

= 2.5 V

V

O

= 3.3 V

V

O

= 5 V

I

OUT

= 1 A

0

10

20

30

40

50

60

70

80

90

100

0.001 0.01 0.1

E

f

f

i

c

i

e

n

c

y

(

%

)

I

OUT

- Output Current (A)

Vo=1.8V

Vo=3.3V

Vo=5V

C009

V

IN

= 12 V

40

50

60

70

80

90

100

0.0 1.0 2.0 3.0 4.0 5.0 6.0

E

f

f

i

c

i

e

n

c

y

(

%

)

I

OUT

- Output Current (A)

Vo=1.8V

Vo=3.3V

Vo=5V

C008

V

IN

= 12 V

Vout(0.5V/div)

EN(10V/div)

1ms/div

VREG5(5V/div)

T P S 5 4 6 2 8

SLVSBW5 APRIL 2013 www.ti.com

T YP I C A L C HA RA C T E RI S T I C S (con tin u e d )

VIN = 12 V, T

A

= 25C (unless otherwise noted).

Figu r e 7. S T A RT - UP WA V E FORM Figu r e 8 . E FFI C I E NC Y v s OUT P UT C URRE NT

Figu r e 9. LI GHT LOA D E FFI C I E NC Y v s OUT P UT C URRE NT Figu r e 1 0. S WI T C HI NG FRE QUE NC Y v s I NP UT V OLT A GE

Figu r e 1 1 . S WI T C HI NG FRE QUE NC Y v s OUT P UT C URRE NT Figu r e 1 2 . V FB V OLT A GE v s JUNC T I ON T E MP E RA T URE

10 Copyright 2013, Texas Instruments Incorporated

Product Folder Links :TPS54628

0.00

1.00

2.00

3.00

4.00

5.00

6.00

7.00

-50 0 50 100

O

u

t

p

u

t

C

u

r

r

e

n

t

(

A

)

T

a

Ambient Temperature (C)

VO=1.05V

VO=1.8V

VO=3.3V

VO=5V

C013

Vo=1.05V VIN(50mV/div)

SW( 5V/div)

400ns/div

SW( 5V/div)

Vo=1.05V Vo(10mV/div)

400ns/div

V = 50 mV / div (-950 mV dc offset)

O

SW = 10 V / div

Time = 1 sec / div

T P S 5 4 6 2 8

www.ti.com SLVSBW5 APRIL 2013

T YP I C A L C HA RA C T E RI S T I C S (con tin u e d )

VIN = 12 V, T

A

= 25C (unless otherwise noted).

Figu r e 1 3. V OLT A GE RI P P LE A T OUT P UT (I

O

= 6 A ) Figu r e 1 4 . D C M V OLT A GE RI P P LE A T

OUT P UT (I

O

= 30 mA )

Figu r e 1 5 . V OLT A GE RI P P LE A T I NP UT (I

O

= 6 A ) Figu r e 1 6 . OUT P UT C URRE NT v s A MBI E NT T E MP E RA T URE

Copyright 2013, Texas Instruments Incorporated 11

Product Folder Links :TPS54628

F =

P

OUT OUT

1

2 L x C p

V = 0.765 x

OUT

R1

1 +

R2

U1

TPS54628DDA

T P S 5 4 6 2 8

SLVSBW5 APRIL 2013 www.ti.com

D E S I GN GUI D E

S te p - By - S te p D e s ign P r oce d u r e

To begin the design process, the user must know a few application parameters:

Input voltage range

Output voltage

Output current

Output voltage ripple

Input voltage ripple

Figu r e 1 7. S h ows th e s ch e matic d iagr am for th is d e s ign e xamp le .

Ou tp u t V oltage Re s is tor s S e le ction

The output voltage is set with a resistor divider from the output node to the VFB pin. It is recommended to use

1% tolerance or better divider resistors. Start by using Equation 3 to calculate V

OUT

.

To improve efficiency at light loads consider using larger value resistors, high resistance is more susceptible to

noise, and the voltage errors from the VFB input current are more noticeable.

(3)

Ou tp u t Filte r S e le ction

The output filter used with the TPS54628 is an LC circuit. This LC filter has double pole at:

(4)

At low frequencies, the overall loop gain is set by the output set-point resistor divider network and the internal

gain of the TPS54628. The low frequency phase is 180 degrees. At the output filter pole frequency, the gain rolls

off at a 40 dB per decade rate and the phase drops rapidly. D-CAP2 introduces a high frequency zero that

reduces the gain roll off to 20 dB per decade and increases the phase to 90 degrees one decade above the

zero frequency. The inductor and capacitor selected for the output filter must be selected so that the double pole

of Equation 4 is located below the high frequency zero but close enough that the phase boost provided be the

high frequency zero provides adequate phase margin for a stable circuit. To meet this requirement use the

values recommended in Table 1

12 Copyright 2013, Texas Instruments Incorporated

Product Folder Links :TPS54628

IN OUT OUT

=

Co(RMS)

IN O SW

V x (V - V )

12 x V x L x

I

f

2 2

=

IPP Lo(RMS) O

1

+

12

I I I

lpp

= +

Ipeak O

2

I

I I

V V

V

IN(max) OUT

OUT

= x

IPP

V L x

IN(max) O SW

-

I

f

T P S 5 4 6 2 8

www.ti.com SLVSBW5 APRIL 2013

T able 1 . Re comme n d e d C omp on e n t V alu e s

Ou tp u t C 4 (p F)

(1 )

L1 (H) C 8 + C 9 (F)

V oltage R1 (k) R2 (k)

MI N T YP MA X MI N T YP MA X MI N MA X

(V )

1 6.81 22.1 5 150 220 1.0 1.5 4.7 22 68

1.05 8.25 22.1 5 150 220 1.0 1.5 4.7 22 68

1.2 12.7 22.1 5 100 1.0 1.5 4.7 22 68

1.5 21.5 22.1 5 68 1.0 1.5 4.7 22 68

1.8 30.1 22.1 5 22 1.2 1.5 4.7 22 68

2.5 49.9 22.1 5 22 1.5 2.2 4.7 22 68

3.3 73.2 22.1 2 22 1.8 2.2 4.7 22 68

5 124 22.1 2 22 2.2 3.3 4.7 22 68

(1) Optional

Since the DC gain is dependent on the output voltage, the required inductor value increases as the output

voltage increases. Additional phase boost can be achieved by adding a feed forward capacitor (C4) in parallel

with R1. The feed forward capacitor is most effective for output voltages at or above 1.8 V.

The inductor peak-to-peak ripple current, peak current and RMS current are calculated using Equation 5,

Equation 6 and Equation 7. The inductor saturation current rating must be greater than the calculated peak

current and the RMS or heating current rating must be greater than the calculated RMS current. Use 700 kHz for

f

SW

.

Use 650 kHz for f

SW

. Make sure the chosen inductor is rated for the peak current of Equation 6 and the RMS

current of Equation 7.

(5)

(6)

(7)

For this design example, the calculated peak current is 6.51 A and the calculated RMS current is 6.01 A. The

inductor used is a TDK SPM6530-1R5M100 with a peak current rating of 11.6 A and an RMS current rating of 11

A.

The capacitor value and ESR determines the amount of output voltage ripple. The TPS54628 is intended for use

with ceramic or other low ESR capacitors. Recommended values range from 22F to 68F. Use Equation 8 to

determine the required RMS current rating for the output capacitor.

(8)

For this design two TDK C3216X5R0J226M 22F output capacitors are used. The typical ESR is 2 m each.

The calculated RMS current is 0.284 A and each output capacitor is rated for 4A.

I n p u t C ap acitor S e le ction

The TPS54628 requires an input decoupling capacitor and a bulk capacitor is needed depending on the

application. A ceramic capacitor over 10 F is recommended for the decoupling capacitor. An additional 0.1 F

capacitor (C3) from pin 8 to ground is optional to provide additional high frequency filtering. The capacitor voltage

rating needs to be greater than the maximum input voltage.

Boots tr ap C ap acitor S e le ction

A 0.1 F. ceramic capacitor must be connected between the VBST to SW pin for proper operation. It is

recommended to use a ceramic capacitor.

Copyright 2013, Texas Instruments Incorporated 13

Product Folder Links :TPS54628

T P S 5 4 6 2 8

SLVSBW5 APRIL 2013 www.ti.com

V RE G5 C ap acitor S e le ction

A 1-F. ceramic capacitor must be connected between the VREG5 to GND pin for proper operation. It is

recommended to use a ceramic capacitor.

T HE RMA L I NFORMA T I ON

This 8-pin DDA package incorporates an exposed thermal pad that is designed to be directly to an external

heartsick. The thermal pad must be soldered directly to the printed board (PCB). After soldering, the PCB can be

used as a heartsick. In addition, through the use of thermal vias, the thermal pad can be attached directly to the

appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a

special heartsick structure designed into the PCB. This design optimizes the heat transfer from the integrated

circuit (IC).

For additional information on the exposed thermal pad and how to use the advantage of its heat dissipating

abilities, see the Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No.

SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Figu r e 1 8 . T h e r mal P ad D ime n s ion s

14 Copyright 2013, Texas Instruments Incorporated

Product Folder Links :TPS54628

VFB

VREG5

SS GND

EN VIN

VBST

SW

EXPOSED

THERMAL PAD

AREA

BOOST

CAPACITOR

VOUT

VIA to Ground Plane

OUTPUT

INDUCTOR

OUTPUT

FILTER

CAPACITOR

SLOW

START

CAP

ANALOG

GROUND

TRACE

VIN

INPUT

BYPASS

CAPACITOR

VIN

FEEDBACK

RESISTORS

TO ENABLE

CONTROL

POWER GROUND

BIAS

CAP

Connection to

POWER GROUND

on internal or

bottom layer

VIN

HIGH FREQENCY

BYPASS

CAPACITOR

T P S 5 4 6 2 8

www.ti.com SLVSBW5 APRIL 2013

LA YOUT C ONS I D E RA T I ONS

1. The TPS54628 can supply large load currents up to 6 A, so heat dissipation may be a concern. The top side

area adjacent to the TPS54628 should be filled with ground as much as possible to dissipate heat.

2. The bottom side area directly below the IC should a dedicated ground area. It should be directly connected

to the thermal pad of the device using vias as shown. The ground area should be as large as practical.

Additional internal layers can be dedicated as ground planes and connected to the vias as well.

3. Keep the input switching current loop as small as possible.

4. Keep the SW node as physically small and short as possible to minimize parasitic capacitance and

inductance and to minimize radiated emissions. Kelvin connections should be brought from the output to the

feedback pin of the device.

5. Keep analog and non-switching components away from switching components.

6. Make a single point connection from the signal ground to power ground.

7. Do not allow switching current to flow under the device.

8. Keep the pattern lines for VIN and PGND broad.

9. Exposed pad of device must be connected to PGND with solder.

10. VREG5 capacitor should be placed near the device, and connected PGND.

11. Output capacitor should be connected to a broad pattern of the PGND.

12. Voltage feedback loop should be as short as possible, and preferably with ground shield.

13. Lower resistor of the voltage divider which is connected to the VFB pin should be tied to SGND.

14. Providing sufficient via is preferable for VIN, SW and PGND connection.

15. PCB pattern for VIN, SW, and PGND should be as broad as possible.

16. VIN Capacitor should be placed as near as possible to the device.

Figu r e 1 9. P C B Lay ou t

Copyright 2013, Texas Instruments Incorporated 15

Product Folder Links :TPS54628

PACKAGE OPTION ADDENDUM

www.ti.com 19-May-2013

Addendum-Page 1

PACKAGING INFORMATION

Orderable Device Status

(1)

Package Type Package

Drawing

Pins Package

Qty

Eco Plan

(2)

Lead/Ball Finish MSL Peak Temp

(3)

Op Temp (C) Device Marking

(4/5)

Samples

TPS54628DDA ACTIVE SO PowerPAD DDA 8 75 Green (RoHS

& no Sb/Br)

CU NIPDAUAG Level-2-260C-1 YEAR -40 to 125 54628

TPS54628DDAR ACTIVE SO PowerPAD DDA 8 2500 Green (RoHS

& no Sb/Br)

CU NIPDAUAG Level-2-260C-1 YEAR -40 to 125 54628

(1)

The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE: TI has discontinued the production of the device.

(2)

Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability

information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that

lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight

in homogeneous material)

(3)

MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4)

There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5)

Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation

of the previous line and the two combined represent the entire Device Marking for that device.

Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information

provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.

TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

TAPE AND REEL INFORMATION

*All dimensions are nominal

Device Package

Type

Package

Drawing

Pins SPQ Reel

Diameter

(mm)

Reel

Width

W1 (mm)

A0

(mm)

B0

(mm)

K0

(mm)

P1

(mm)

W

(mm)

Pin1

Quadrant

TPS54628DDAR SO

Power

PAD

DDA 8 2500 330.0 12.8 6.4 5.2 2.1 8.0 12.0 Q1

PACKAGE MATERIALS INFORMATION

www.ti.com 18-May-2013

Pack Materials-Page 1

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

TPS54628DDAR SO PowerPAD DDA 8 2500 366.0 364.0 50.0

PACKAGE MATERIALS INFORMATION

www.ti.com 18-May-2013

Pack Materials-Page 2

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other

changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest

issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and

complete. All semiconductor products (also referred to herein as components) are sold subject to TIs terms and conditions of sale

supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TIs terms

and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary

to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily

performed.

TI assumes no liability for applications assistance or the design of Buyers products. Buyers are responsible for their products and

applications using TI components. To minimize the risks associated with Buyers products and applications, Buyers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or

other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information

published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or

endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the

third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration

and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered

documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service

voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice.

TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements

concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support

that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which

anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause

harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use

of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TIs goal is to

help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and

requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties

have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or enhanced plastic are designed and intended for use in

military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components

which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and

regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of

non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive

Amplifiers amplifier.ti.com Communications and Telecom www.ti.com/communications

Data Converters dataconverter.ti.com Computers and Peripherals www.ti.com/computers

DLP Products www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP dsp.ti.com Energy and Lighting www.ti.com/energy

Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial

Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright 2013, Texas Instruments Incorporated

You might also like

- Express Luck Group: Specification PhotoDocument1 pageExpress Luck Group: Specification PhotoYesenia Jaime RoaNo ratings yet

- IC For Samsung UE32D4003BW, LED Driver Control ICDocument2 pagesIC For Samsung UE32D4003BW, LED Driver Control ICFrancisco ChaoNo ratings yet

- TPV-InVENTA Nell (Nisene2 LarryBird) 6050A2516301 REV M0C (M0B) - HP Touchsmart Envy 20 All-In-OneDocument41 pagesTPV-InVENTA Nell (Nisene2 LarryBird) 6050A2516301 REV M0C (M0B) - HP Touchsmart Envy 20 All-In-OneLazaro Guajardo Garza50% (2)

- Diagrama Fonte DeltaDocument7 pagesDiagrama Fonte DeltacesarNo ratings yet

- L24D10 MT23-AP Service ManualDocument44 pagesL24D10 MT23-AP Service Manualunexpoyap100% (2)

- Ad82587d PDFDocument45 pagesAd82587d PDFИван Алексиев50% (2)

- (Main 35018086 (3x1) - ICs N501-MSD1306XP - Driv Led N701-OCP8122A OZ9902A-N (24pin) TV Led Konka KDL39-42PS615ATDocument11 pages(Main 35018086 (3x1) - ICs N501-MSD1306XP - Driv Led N701-OCP8122A OZ9902A-N (24pin) TV Led Konka KDL39-42PS615ATJeank Rivadeneyra67% (3)

- SOYEA LCD Service Manual PDFDocument40 pagesSOYEA LCD Service Manual PDFraipedriNo ratings yet

- Current Mode LED Driver: General Description FeaturesDocument1 pageCurrent Mode LED Driver: General Description FeaturesEnrique LandraNo ratings yet

- CC580PV6D Rev.01 20191106 202006163878-1-1Document16 pagesCC580PV6D Rev.01 20191106 202006163878-1-1sabor20212021100% (1)

- Enhancement Mode N-Channel Power MOSFET: OSG65R900xTFDocument10 pagesEnhancement Mode N-Channel Power MOSFET: OSG65R900xTFCube7 Geronimo100% (1)

- Rca RS2656 - RS2657Document27 pagesRca RS2656 - RS2657Ivan Emanuel DonatelloNo ratings yet

- FA + Mainboard TP - MS608.PB831 PDFDocument13 pagesFA + Mainboard TP - MS608.PB831 PDFFernando GuerreroNo ratings yet

- Panel Chimei Innolux v320bj3-p02 0Document30 pagesPanel Chimei Innolux v320bj3-p02 0doniNo ratings yet

- Regulador 001 A5wDocument12 pagesRegulador 001 A5wvladimirNo ratings yet

- 29e50 Ob2273d+ob3362hpDocument1 page29e50 Ob2273d+ob3362hprammerDankov100% (2)

- General Description Product Summary: Bvdss Rdson IDDocument4 pagesGeneral Description Product Summary: Bvdss Rdson IDDavid BarriosNo ratings yet

- Manual Control Remoto GDRC-400T (Ingles)Document9 pagesManual Control Remoto GDRC-400T (Ingles)Alexandro Conde MartínezNo ratings yet

- The Specifications of ISL24835IRZDocument1 pageThe Specifications of ISL24835IRZFadi100% (1)

- Service Manual: Model: APM200Document55 pagesService Manual: Model: APM200VASILIY GRACHEVNo ratings yet

- JVC Service Manual mxgt80 PDFDocument48 pagesJVC Service Manual mxgt80 PDFAlex GuerreroNo ratings yet

- 715t3181 LG Psu Schematic PDFDocument1 page715t3181 LG Psu Schematic PDFSAS WAJINo ratings yet

- Noblex: SERVICE MANUAL Colour TelevisionDocument29 pagesNoblex: SERVICE MANUAL Colour Televisionjose4445No ratings yet

- Datasheet PDFDocument26 pagesDatasheet PDFHoàng Việt HùngNo ratings yet

- Tps 65171Document46 pagesTps 65171deo57ar100% (2)

- OB3372 On BrightDocument13 pagesOB3372 On BrightPedro Leandro SilvaNo ratings yet

- JSK4267-022 Service Manual PDFDocument32 pagesJSK4267-022 Service Manual PDFЕфрушка Мишанов100% (2)

- MT9602 US Service Manual V1.0 2020-3-27-1Document57 pagesMT9602 US Service Manual V1.0 2020-3-27-1Tena y EstebanNo ratings yet

- 29TC679FDocument29 pages29TC679FGustavo ChavezNo ratings yet

- General Description Features: Cost Effective LED ControllerDocument10 pagesGeneral Description Features: Cost Effective LED ControlleranilNo ratings yet

- TCL LD24D50 - Chassis MS09A-LA - (TKLE2413D) - Manual de Servicio PDFDocument41 pagesTCL LD24D50 - Chassis MS09A-LA - (TKLE2413D) - Manual de Servicio PDFFabian OrtuzarNo ratings yet

- Bd9397efv e PDFDocument30 pagesBd9397efv e PDFshafiuddin7326No ratings yet

- PF6000AGDocument1 pagePF6000AGlibre2009No ratings yet

- BGH3299A Manual Servicio PDFDocument36 pagesBGH3299A Manual Servicio PDFaldoNo ratings yet

- FSDM07652R DatasheetDocument16 pagesFSDM07652R Datasheetmarianos67No ratings yet

- Philips AZ 1837 Service Manual PhilipsDocument38 pagesPhilips AZ 1837 Service Manual PhilipsAnom Manela100% (2)

- CDH l32fd10 Service ManualDocument42 pagesCDH l32fd10 Service Manualtravieso112No ratings yet

- JVC DXJ 20 Service ManualDocument101 pagesJVC DXJ 20 Service ManualMuh. Ismail100% (1)

- Sony Vaio VPCEH2N1E MBX-247 Schematic Diagram Quanta HK1Document39 pagesSony Vaio VPCEH2N1E MBX-247 Schematic Diagram Quanta HK1SRG InfoTechNo ratings yet

- Model Name:GA-G41MT-S2: Revision 1.3Document33 pagesModel Name:GA-G41MT-S2: Revision 1.3Đình CườngNo ratings yet

- Diagrama de Modular Philips MCD288Document39 pagesDiagrama de Modular Philips MCD288Antonio Chavez50% (2)

- 32PC5RV Manual de ServiçoDocument38 pages32PC5RV Manual de ServiçoJose Santana100% (1)

- Features: Hybrid Power Boost (HPB) and Narrow VDC (NVDC) Combo Battery Charger With Smbus InterfaceDocument2 pagesFeatures: Hybrid Power Boost (HPB) and Narrow VDC (NVDC) Combo Battery Charger With Smbus InterfaceJ-Pablo Enriquez100% (1)

- Chassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioDocument16 pagesChassis Sanyo Con UOC TMPA8823-5VA4 Manual de ServicioRobert Vicuña100% (1)

- f66fbdd3-58a5-4558-bf4a-ffaeea4fed36Document14 pagesf66fbdd3-58a5-4558-bf4a-ffaeea4fed36Chafik AlbadraouiNo ratings yet

- SLC 7015Document1 pageSLC 7015Дмитрий КопышевNo ratings yet

- Sta 540 SaDocument19 pagesSta 540 Satarzan20140% (1)

- Pioneer Sx-4, 5, 6, 7 SMDocument14 pagesPioneer Sx-4, 5, 6, 7 SMvali dNo ratings yet

- Dap011 DDocument24 pagesDap011 Dsontuyet82No ratings yet

- 1 - Samsung BN44-00705CDocument4 pages1 - Samsung BN44-00705CMurilo FerrazNo ratings yet

- BN44-00554B PD32GV0Document3 pagesBN44-00554B PD32GV0Devorador De PecadosNo ratings yet

- 5A, 28V Input, Step Down Swift™ DC/DC Converter With Eco-Mode™Document27 pages5A, 28V Input, Step Down Swift™ DC/DC Converter With Eco-Mode™thunderer2014No ratings yet

- Tps 51125Document37 pagesTps 51125Naresh Kumar100% (1)

- Low-Noise Fast-Transient-Response 1.5-A Low-Dropout Voltage RegulatorsDocument28 pagesLow-Noise Fast-Transient-Response 1.5-A Low-Dropout Voltage RegulatorssinnlosNo ratings yet

- Bias Power Supply For TV and Monitor TFT LCD Panels: FeaturesDocument30 pagesBias Power Supply For TV and Monitor TFT LCD Panels: Featureseduinggv1829No ratings yet

- Bias Power Supply For TV and Monitor TFT LCD Panels: FeaturesDocument35 pagesBias Power Supply For TV and Monitor TFT LCD Panels: Featureseduinggv1829No ratings yet

- Complete DDR2, DDR3, DDR3L, and LPDDR3 Memory Power Solution Synchronous Buck Controller, 2-A LDO, With Buffered ReferenceDocument30 pagesComplete DDR2, DDR3, DDR3L, and LPDDR3 Memory Power Solution Synchronous Buck Controller, 2-A LDO, With Buffered Referencesalahudeen03No ratings yet

- TLC 5925Document27 pagesTLC 5925zektorNo ratings yet

- PTN 78020 WDocument27 pagesPTN 78020 WabrrielNo ratings yet

- DatasheetDocument58 pagesDatasheetselocaNo ratings yet

- Deloitte IoTDocument54 pagesDeloitte IoTmarkanapier100% (2)

- HighSpeed ElectronicsDocument62 pagesHighSpeed Electronicsfet_50No ratings yet

- IPC Spec TreeDocument1 pageIPC Spec Treefet_50No ratings yet

- Secure Issues in Smart GridDocument11 pagesSecure Issues in Smart Gridfet_50No ratings yet

- DDR SpecDocument219 pagesDDR Specfet_50No ratings yet

- PCB West 2016 New Techniques Address Layout Challenges High Speed Routing CPDocument37 pagesPCB West 2016 New Techniques Address Layout Challenges High Speed Routing CPNguyễn Đình Tiến NamNo ratings yet

- Bitmart Whitepaper enDocument7 pagesBitmart Whitepaper enfet_50No ratings yet

- Hycon Whitepaper V1.21: Infinity ProjectDocument29 pagesHycon Whitepaper V1.21: Infinity Projectfet_50No ratings yet

- Tips Tricks CADDocument37 pagesTips Tricks CADJuan Jose ArmasNo ratings yet

- Pads Tut LogicDocument61 pagesPads Tut Logicardeleanu_842799No ratings yet

- HyperLynx Signal Integrity Analysis Student WorkbookDocument538 pagesHyperLynx Signal Integrity Analysis Student Workbookjagadees2189% (9)

- Challenges and Solutions For Cleaning No-Clean Flux Residues From Surface Mount ComponentsDocument33 pagesChallenges and Solutions For Cleaning No-Clean Flux Residues From Surface Mount Componentsfet_50No ratings yet

- Bitmart Whitepaper enDocument36 pagesBitmart Whitepaper enfet_50No ratings yet

- Bitmart Whitepaper enDocument36 pagesBitmart Whitepaper enfet_50No ratings yet

- Pads Tut LogicDocument61 pagesPads Tut Logicardeleanu_842799No ratings yet

- TN 4614Document16 pagesTN 4614fet_50No ratings yet

- Self Encrypting Drives White PaperDocument15 pagesSelf Encrypting Drives White Paperfet_50No ratings yet

- SI Guidelines PDFDocument36 pagesSI Guidelines PDFfet_50No ratings yet

- PCB Stackup Technology SeriesDocument19 pagesPCB Stackup Technology Seriesfet_50No ratings yet

- (Altium) - TR0116 Design Rules ReferenceDocument73 pages(Altium) - TR0116 Design Rules Referencefet_50No ratings yet

- HW Design CookbookDocument212 pagesHW Design Cookbookfet_50No ratings yet

- IoT An OverviewDocument53 pagesIoT An OverviewHarshaAchyutuni88% (8)

- Hyperlynx A PWB Design ToolDocument42 pagesHyperlynx A PWB Design Toolfet_50No ratings yet

- 2101-0101010302 RJ-45 With Led &transfomerDocument1 page2101-0101010302 RJ-45 With Led &transfomerfet_50No ratings yet

- Acad 2 DDocument269 pagesAcad 2 DPham CongNo ratings yet

- Adaptor 5V2 - 2A STDocument37 pagesAdaptor 5V2 - 2A STfet_50No ratings yet

- Prekidačka NapajanjaDocument48 pagesPrekidačka NapajanjaDamir PranjkovicNo ratings yet

- An 4140Document11 pagesAn 4140ommidbeNo ratings yet

- "KAT" Carriage Power Supply Schematic: DRAWING NUMBER: GK-191-P-029Document12 pages"KAT" Carriage Power Supply Schematic: DRAWING NUMBER: GK-191-P-029Carlos AlexandreNo ratings yet

- Flashtool 430-II Firmware V05.00 Release NotesDocument6 pagesFlashtool 430-II Firmware V05.00 Release NotesGeovanny Cardenas JaimeNo ratings yet

- Conference PaperDocument3 pagesConference PaperAngelica SutharNo ratings yet

- Irfb5620Pbf: Digital Audio MosfetDocument7 pagesIrfb5620Pbf: Digital Audio Mosfettecniloco80No ratings yet

- Psoc BookDocument534 pagesPsoc Bookoss6000100% (1)

- DS - 20210323 - SG6250HV-MV SG6800HV-MV Datasheet - V1.1.2 - ENDocument2 pagesDS - 20210323 - SG6250HV-MV SG6800HV-MV Datasheet - V1.1.2 - ENricardo alonzoNo ratings yet

- PT 51Document33 pagesPT 51Saivamseedhar BojjaNo ratings yet

- Short Questions: (CHAPTER 18) ElectronicsDocument9 pagesShort Questions: (CHAPTER 18) ElectronicsEhtesham Ali KhanNo ratings yet

- Wireless Computer Controlled Robotics Using The Pic16F77 MicrocontrollerDocument45 pagesWireless Computer Controlled Robotics Using The Pic16F77 MicrocontrollerprabhuNo ratings yet

- Radio-Handbook 1977 PDFDocument1,078 pagesRadio-Handbook 1977 PDFpeloton10No ratings yet

- Sangfor HCI White Paper 2016 JuneDocument71 pagesSangfor HCI White Paper 2016 JuneiwakbiruNo ratings yet

- MXL9000 ManualDocument2 pagesMXL9000 ManualbhsoulNo ratings yet

- Micom 87L LogicDocument4 pagesMicom 87L LogictajudeenNo ratings yet

- Data Sheet: BZT03 SeriesDocument9 pagesData Sheet: BZT03 Seriesdrain rainNo ratings yet

- EET301 Tutorial 2-Chapter 2-Session 2017-2018Document4 pagesEET301 Tutorial 2-Chapter 2-Session 2017-2018Nazir AhmedNo ratings yet

- Bass200 ManualDocument12 pagesBass200 ManualTemistocle BNo ratings yet

- Fiber Optics Catalogue Ver2.01 Publish by FirstFiber - CNDocument90 pagesFiber Optics Catalogue Ver2.01 Publish by FirstFiber - CNAnonymous zI6wHoNo ratings yet

- Eng TELE-audiovision 1411Document164 pagesEng TELE-audiovision 1411Alexander WieseNo ratings yet

- HGI 1HC0076376AA EN WebDocument7 pagesHGI 1HC0076376AA EN WebrpshvjuNo ratings yet

- Module Week 10Document2 pagesModule Week 10Maria Christina ManzanoNo ratings yet

- Is 9482 1996 PDFDocument30 pagesIs 9482 1996 PDFabcNo ratings yet

- VSD Training SinamicsDocument22 pagesVSD Training SinamicsClaudio Andres Lagos GuerreroNo ratings yet

- Horn Antenna Design BaitiDocument3 pagesHorn Antenna Design BaitiBetty NurbaitiNo ratings yet

- HP Support Center: Drivers & Software Intel Serial IO DriverDocument1 pageHP Support Center: Drivers & Software Intel Serial IO DriverDodo BabyNo ratings yet

- Introduction To The I/O Buses Technical and Historical Background For The I/O BusesDocument9 pagesIntroduction To The I/O Buses Technical and Historical Background For The I/O BusesshankyguptaNo ratings yet

- A Versatile Monolithic Voltage-to-Frequency ConverterDocument13 pagesA Versatile Monolithic Voltage-to-Frequency ConverterGojko RatkovićNo ratings yet

- Chess Panel ProjectDocument31 pagesChess Panel ProjectMahmoud El-tabeyNo ratings yet

- Cache Coherency SDocument20 pagesCache Coherency Skamal.vlsi7997No ratings yet

- Nju7505a eDocument8 pagesNju7505a eCleber MouraNo ratings yet

- Spintronics ComDocument28 pagesSpintronics Coms_aishwaryaNo ratings yet