Professional Documents

Culture Documents

Displaytech 204A LCD Interface Guide

Uploaded by

Mark VillamorOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Displaytech 204A LCD Interface Guide

Uploaded by

Mark VillamorCopyright:

Available Formats

Interfacing Displaytech 204A

Series LCD to MB90F387S

About the Displaytech 204A

Displaytech Ltd

LCD MODULE 204A SERIES Version : 1.2 P 2 of 17

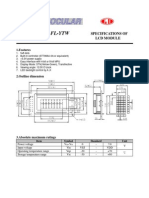

! PHYSICAL DATA

Item Contents Unit

LCD type TN / STN / FSTN ---

LCD duty 1/16 ---

LCD bias 1/5 ---

Viewing direction 6 / 12 oclock

Module size (W!H!T) 98 ! 60 ! 11.0 MAX (14.0 MAX W/LED BACKLIGHT) mm

Viewing area (W!H) 76 ! 25.2 mm

Number of characters (characters!lines) 20 ! 4 ---

Character matrix (W!H) 5 ! 8 dots

Character size (W!H) 2.95 ! 4.75 mm

Dot size (W!H) 0.55 ! 0.55 mm

Dot pitch (W!H) 0.60 ! 0.60 mm

! EXTERNAL DIMENSIONS

! BLOCK DIAGRAM

External Dimensions

Displaytech Ltd

LCD MODULE 204A SERIES Version : 1.2 P 2 of 17

! PHYSICAL DATA

Item Contents Unit

LCD type TN / STN / FSTN ---

LCD duty 1/16 ---

LCD bias 1/5 ---

Viewing direction 6 / 12 oclock

Module size (W!H!T) 98 ! 60 ! 11.0 MAX (14.0 MAX W/LED BACKLIGHT) mm

Viewing area (W!H) 76 ! 25.2 mm

Number of characters (characters!lines) 20 ! 4 ---

Character matrix (W!H) 5 ! 8 dots

Character size (W!H) 2.95 ! 4.75 mm

Dot size (W!H) 0.55 ! 0.55 mm

Dot pitch (W!H) 0.60 ! 0.60 mm

! EXTERNAL DIMENSIONS

! BLOCK DIAGRAM

Actual Picture (Reverse Contrast Type)

Block Diagram

Displaytech Ltd

LCD MODULE 204A SERIES Version : 1.2 P 2 of 17

! PHYSICAL DATA

Item Contents Unit

LCD type TN / STN / FSTN ---

LCD duty 1/16 ---

LCD bias 1/5 ---

Viewing direction 6 / 12 oclock

Module size (W!H!T) 98 ! 60 ! 11.0 MAX (14.0 MAX W/LED BACKLIGHT) mm

Viewing area (W!H) 76 ! 25.2 mm

Number of characters (characters!lines) 20 ! 4 ---

Character matrix (W!H) 5 ! 8 dots

Character size (W!H) 2.95 ! 4.75 mm

Dot size (W!H) 0.55 ! 0.55 mm

Dot pitch (W!H) 0.60 ! 0.60 mm

! EXTERNAL DIMENSIONS

! BLOCK DIAGRAM

Interface Signals

Displaytech Ltd

LCD MODULE 204A SERIES Version : 1.2 P 9 of 17

! INTERFACE PIN CONNECTIONS

Pin NO. Symbol Level Description

1 VSS 0V Ground

2 VDD 5.0V Supply voltage for logic

3 VO --- Input voltage for LCD

4 RS H/L H : Data signal, L : Instruction signal

5 R/W H/L H : Read mode, L : Write mode

6 E H, H ! L Enable signal for KS0076

7 DB0 H/L Data bit 0

8 DB1 H/L Data bit 1

9 DB2 H/L Data bit 2

10 DB3 H/L Data bit 3

11 DB4 H/L Data bit 4

12 DB5 H/L Data bit 5

13 DB6 H/L Data bit 6

14 DB7 H/L Data bit 7

15 A --- Back light anode

16 K --- Back light cathode

Registers

Instruction Register (IR)

stores instruction codes such as clear

display or shift cursor and also stores

address information for the display data

RAM

Data Register

is used for temporarily storing data during

data transactions with the MCU

Registers

Busy Flag (BF)

When the busy flag is set at a logical "1", the

LCD unit is executing an internal operation,

and no instruction will be accepted

Address Counter (AC)

The address counter generates the address

for the display data RAM and character

generator RAM

Registers

Display Data RAM (DD RAM)

This 80 x 8 bit RAM stores up to 80 8-bit

character codes as display data

Busy Flag (BF)

When the busy flag is set at a logical "1", the LCD

unit is executing an internal operation, and no in-

struction will be accepted. The state of the busy flag

is output on data line DB

7

in response to the register

selection signals RS = 0, R/W = 1 as shown in Table

3. The next instruction may be entered after the

busy flag is reset to logical "0".

Address Counter (AC)

The address counter generates the address for

the display data RAM and character generator

RAM. When the address set instruction is written

into the instruction register, the address information

is sent to the address counter. The same instruciton

also determines which of the two RAMs is to be

selected.

After data has been written to or read from the

display data RAM or character generator RAM, the

address counter is automatically incremented or

decremented by one. The contents of the address

counter are output on data lines DB

0

- DB

6

in

response to the register selection signals RS = 0,

R/W = 1 as shown in Table 3.

Display Data RAM (DD RAM)

This 80 x 8 bit RAM stores up to 80 8-bit character

codes as display data. The unused area of the RAM

may be used by the microprocessor as a general

purpose RAM area.

The display data RAM address, set in the address

counter, is expressed in hexadecimal (HEX) num-

bers as follows:

The address of the display data RAM corre-

sponds to the display position on the LCD panel as

follows:

a. Address type a . . . .For dual-line display

When a display shift takes place, the addresses

shift is as follows:

The addresses for the second line are not con-

tinuous to the addresses for the first line. A 40-char-

acter RAM area is assigned to each of the two line

as follows:

line 1: 00

H

- 27

H

line 2: 40

H

- 67

H

For an LCD unit with a display capacity of less

than 40 characters per line, characters equal in

number to the display capacity, as counted from

display position 1, are displayed.

b. Address type b . . . .For single-line display with

logically dual-line addressing

When a display shift takes place, the addresses

shift as follows:

The right-hand eight characters, for the purposes

of addressing and shifting, may be considered to

constitute a second display line. For the address

type of each model, see Table 12.

AC6 AC5 AC4 AC3 AC2 AC1 AC0

HEX

Digit

AC

High-order

Bits

Lower-order

Bits

HEX

Digit

1

Example: DD RAM address '4E'

0 0 1 1 1 0

4 E

9 8 7 6 5 4 3 2 1 39 40

Display Position

DD RAM Address (HEX)

Digit

Line 1

Line 2

00

H

01

H

02

H

03

H

04

H

05

H

06

H

07

H

08

H

26

H

27

H

40

H

41

H

42

H

43

H

44

H

45

H

46

H

47

H

48

H

66

H

67

H

. . .

. . .

Left

Shift

01

H

02

H

03

H

04

H

05

H

06

H

07

H

08

H

09

H

27

H

00

H

41

H

42

H

43

H

44

H

45

H

46

H

47

H

48

H

49

H

67

H

40

H

. . .

. . .

Right

Shift

27

H

00

H

01

H

02

H

03

H

04

H

05

H

06

H

07

H

25

H

26

H

67

H

40

H

41

H

42

H

43

H

44

H

45

H

46

H

47

H

65

H

66

H

. . .

. . .

16 15 14

Display Position Digit

Line

1

DD RAM Address (HEX)

13 12 11 10 9 8 7 6 5 4 3 2 1

00

H

47

H

46

H

45

H

44

H

43

H

42

H

41

H

40

H

07

H

06

H

05

H

04

H

03

H

02

H

01

H

Left

Shift

01

H

48

H

47

H

46

H

45

H

44

H

43

H

42

H

41

H

08

H

07

H

06

H

05

H

04

H

03

H

02

H

Right

Shift

27

H

46

H

45

H

44

H

43

H

42

H

41

H

40

H

67

H

06

H

05

H

04

H

03

H

02

H

01

H

00

H

Dot-Matrix LCD Units

Display Unit Users Manual 5

Registers

Character Generator ROM (CG ROM)

This ROM generates a 5 ! 7 dot-matrix

character pattern for each of 160 different

8-bit character codes

Character Generator RAM (CG RAM)

This RAM stores eight arbitrary 5 x 7 dot-

matrix character patterns, as programmed

by the user

0000

HIGH-ORDER

4 BIT

LOW-

ORDER 4 BIT

0010 0011 0100 0101 0110 0111 1010 1011 1100 1101 1110 1111

xxxx0000

xxxx0001

xxxx0010

xxxx0011

xxxx0100

xxx0101

xxx0110

xxxx0111

xxxx1000

xxxx1001

xxxx1010

xxxx1011

xxxx1100

xxxx1101

xxxx1110

xxxx1111

CG

RAM

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

NOTES:

1. The CG RAM generates character patterns in accordance with the user's program.

2. Shaded areas indicate 5 x 10 dot character patterns.

Table 4. Character Codes

Dot-Matrix LCD Units

8 Display Unit Users Manual

Character Codes

MCU Interface

The LCD unit performs either dual 4-bit or single 8-

bit data transfers, allowing the user to interface with

either a 4-bit or 8-bit microprocessor

4-Bit Microprocessor Interface.

Data lines DB4 - DB7 are used for data transfers.

Data transactions with the external

microprocessor take place in two 4-bit data

transfer operations.

MCU Interface

8-bit Microprocessor Interface

Each 8-bit piece of data is transferred in a single

operation using the entire data bus DB0 - DB7.

Microprocessor Interface

The LCD unit performs either dual 4-bit or single

8-bit data transers, allowing the user to interface with

either a 4-bit or 8-bit microprocessor

4-Bit Microprocessor Interface.

Data lines DB

4

- DB

7

are used for data transfers.

Data transactions with the external microprocessor

take place in two 4-bit data transfer operations.

The high-order 4 bits (corresponding to DB

4

- DB

7

in an 8-bit transfer) are transferred first, followed by

the low-order 4 bits (corresponding to DB

0

- DB

3

in

an 8-bit transfer). The busy flag is to be checked on

completion of the second 4-bit data transfer. Busy

flag and address counter are output in two opera-

tions.

8-bit Microprocessor Interface

Each 8-bit piece of data is transferred in a single opera-

tion using the entire data bus DB0 - DB7.

IR

7

DB

7

DB

6

DB

5

DB

4

RS

R/W

E

IR

3

AC

3

DR

7

DR

3

BF

IR

6

IR

2

AC

2

DR

6

DR

2

AC

6

IR

5

IR

1

AC

1

DR

5

DR

1

AC

5

IR

4

IR

0

AC

0

DR

4

DR

0

AC

4

Write to

Instruction

Register (IR)

Read Busy

Flag (BF) and

Address

Counter (AC)

Read Data

Register (DR)

LCD27-9

Figure 2. 4-Bit Data Transfer

Dot-Matrix LCD Units

Display Unit Users Manual 11

4-bit Data Transfer

Initialization by

Instruction 8-bit

Interface

Initialization by Instructions

If the power conditions for the normal operation

of the internal reset circuit are not satisfied (see

Table 11), then LCD unit must be initialized by

executing a series of instructions. The procedure

for this initialization process is as follows:

Power ON

Wait 15 ms or more

after V

DD

reaches 4.5 V

RS R/W DB

7

DB

6

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

0 0 0 0 1 1

* * * *

Wait 4.1 ms or more

RS R/W DB

7

DB

6

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

0 0 0 0 1 1

* * * *

Wait 100 s or more

End of Initialization

RS R/W DB

7

DB

6

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

0 0 0 0 1 1

* * * *

RS R/W DB

7

DB

6

DB

5

DB

4

DB

3

DB

2

DB

1

DB

0

0 0 0 0 1 1 N F

* *

0 0 0 0 0 0 1 0 0 0

0 0 0 0 0 0 0 0 0 1

0 0 0 0 0 0 0 1 I/D S

Busy flag can't be checked before execution of this

instruction

Function Set (8-Bit Interface)

Busy flag can't be checked before execution of this

instruction

Function Set (8-Bit Interface)

Busy flag can't be checked before execution of this

instruction

Function Set (8-Bit Interface)

(a) Busy flag can be checked after the following instructions

are completed. If the busy flag is not going to be checked,

then a wait time longer than the total execution time of

these instructions is required (See Table 7.)

Function Set

Display Off

Display Clear

Entry Mode Set

8-Bit Interface,

Single/Dual Line

Display, Display Font

Caution: At this point,

the display format

an't be changed.

LCD21-10

Figure 3. 8-Bit Interface

Dot-Matrix LCD Units

Display Unit Users Manual 13

4-Bit Interface

Power ON

Wait 15 ms or more

after V

DD

reaches 4.5 V

RS R/W DB

7

DB

6

DB

5

DB

4

0 0 0 0 1 1

Wait 4.1 ms or more

RS R/W DB

7

DB

6

DB

5

DB

4

0 0 0 0 1 1

RS R/W DB

7

DB

6

DB

5

DB

4

0 0 0 0 1 1

RS R/W DB

7

DB

6

DB

5

DB

4

0 0 0 0 1 0

0 0 0 0 1 0

0 0 N F

* *

Wait 100 s or more

End of Initialization

Busy flag can't be checked before execution of this

instruction

Function Set (8-Bit Interface)

Busy flag can't be checked before execution of this

instruction

Function Set (8-Bit Interface)

Busy flag can't be checked before execution of this

instruction

Function Set (8-Bit Interface)

(a) Busy flag can be checked after the following instructions

are completed. If the busy flag is not going to be checked,

then a wait time longer than the total execution time of

these instructions is required (See Table 7.)

This instruction signals the LCD unit to begin accepting and

sending data in dual 4-bit transfers for all subsequent

transfers for all subsequent transactions. This is the only

4-bit instruction recognized by the LCD unit.

II Function Set

III Display Off

IV Display Clear

V Entry Mode Set

4-Bit Interface,

Single/Dual Line

Display, Display Font

LCD21-11

0 0 0 0 0 0

0 0 1 0 0 0

0 0 0 0 0 O

0 0 0 0 0 1

0 0 0 0 0 0

0 0 0 1 I/D S

I Function Set (4-Bit Interface)

I

II

III

IV

V

Caution: At this point,

the display format

can't be changed.

Figure 4. 4-Bit Interface

Dot-Matrix LCD Units

14 Display Unit Users Manual

Initialization by

Instruction 4-bit

Interface

NOTES:

1.

Symbol "*" signifies a "dont care" bit.

2. Correct input value for "N" is predetermined for each model (see Table 12).

Table 7. Instruction Set

Dot-Matrix LCD Units

18 Display Unit Users Manual

Instruction Set

ELECTRICAL CHARACTERISTICS

Absolue Maximum Ratings

See the device specifications for each LCD unit

model.

Electrical Characteristics

See the device specificiations for each LCD unit

model. Some of the currently available specifica-

tions do not describe the test conditions for the

high-level and low-level output voltages. These

conditions are as follows:

Timing Characteristics

!

!

Table 8.

t

AS

PW

EH

t

DSW

t

cycE

t

AH

t

AH

V

IH

V

IL

DB

0

- DB

7

t

Ef

t

H

t

Er

V

IH

V

IL

E

V

IL

R/W

V

IH

V

IL

RS

VALID DATA

LCD27-24

Figure 5. Write Operation Timing Diagram

(For data sent from the external microprocessor to the LCD unit)

!

!

!

!

!

!

!

Table 9. Write Operation Timing Characteristics

(VDD = 5.0 5%, VSS = 0 V, TA = 0 ~ 50C)

Dot-Matrix LCD Units

Display Unit Users Manual 19

ELECTRICAL CHARACTERISTICS

Absolue Maximum Ratings

See the device specifications for each LCD unit

model.

Electrical Characteristics

See the device specificiations for each LCD unit

model. Some of the currently available specifica-

tions do not describe the test conditions for the

high-level and low-level output voltages. These

conditions are as follows:

Timing Characteristics

!

!

Table 8.

t

AS

PW

EH

t

DSW

t

cycE

t

AH

t

AH

V

IH

V

IL

DB

0

- DB

7

t

Ef

t

H

t

Er

V

IH

V

IL

E

V

IL

R/W

V

IH

V

IL

RS

VALID DATA

LCD27-24

Figure 5. Write Operation Timing Diagram

(For data sent from the external microprocessor to the LCD unit)

!

!

!

!

!

!

!

Table 9. Write Operation Timing Characteristics

(VDD = 5.0 5%, VSS = 0 V, TA = 0 ~ 50C)

Dot-Matrix LCD Units

Display Unit Users Manual 19

Write Operation Timing Characteristics

If the above conditions are not satisfied, the inter-

nal reset circuit will not operate normally. In such a

case, the LCD unit must be initialized by executing

a series of instructions (see the Execution by In-

structions section).

t

AS

PW

EH

t

DDR

t

cycE

t

AH

t

AH

V

OH

V

OL

DB

0

- DB

7

t

Ef

t

DHR

t

Er

V

IH

V

IL

E

V

IH R/W

V

IH

V

IL

RS

VALID DATA

LCD27-25

Figure 6. Read Operation Timing Diagram

(For data sent from the LCD unit to the external microprocessor)

!

!

!

!

!

!

!

Table 10. Read Operation Timing Characteristics

(VDD = 5.0 5%, VSS = 0 V, Ta = 0 ~ 50C)

!

! !

Table 11. Power Conditions for Internal Reset

0.1 ms ! t

rCC

! 10 ms t

OFF

"

1 ms

0.2 V 0.2 V 0.2 V

4.5 V

NOTE: * t

OFF

indicates Power-off Period.

V

DD

LCD27-26

Figure 7.

Dot-Matrix LCD Units

20 Display Unit Users Manual

If the above conditions are not satisfied, the inter-

nal reset circuit will not operate normally. In such a

case, the LCD unit must be initialized by executing

a series of instructions (see the Execution by In-

structions section).

t

AS

PW

EH

t

DDR

t

cycE

t

AH

t

AH

V

OH

V

OL

DB

0

- DB

7

t

Ef

t

DHR

t

Er

V

IH

V

IL

E

V

IH R/W

V

IH

V

IL

RS

VALID DATA

LCD27-25

Figure 6. Read Operation Timing Diagram

(For data sent from the LCD unit to the external microprocessor)

!

!

!

!

!

!

!

Table 10. Read Operation Timing Characteristics

(VDD = 5.0 5%, VSS = 0 V, Ta = 0 ~ 50C)

!

! !

Table 11. Power Conditions for Internal Reset

0.1 ms ! t

rCC

! 10 ms t

OFF

"

1 ms

0.2 V 0.2 V 0.2 V

4.5 V

NOTE: * t

OFF

indicates Power-off Period.

V

DD

LCD27-26

Figure 7.

Dot-Matrix LCD Units

20 Display Unit Users Manual

Read Operation Timing Characteristics

LKS Expansion Board

LCD + Keypad + Stepper Motor

Video Demo

Programming

Step 1: Write a function to send

Instructions to LCD

Step 2: Write a function to Initialize LCD

(initialize once)

Step 3: Write a function to send Data to

LCD

Step 4: Write a function to display a string

to LCD

Demonstration #1

Flowchart for instCtrl() - function to send

instruction to LCD (8-bit)

Flowchart for instCtrl()

function

Sample Code (C)

void instCtrl(unsigned char inst)

{

IO_PDR2.byte = inst; // load 8-bit instruction to 8-bit LCD data lines

IO_PDR5.bit.P50 = 0; // set RS to 0 (instruction register)

IO_PDR5.bit.P51 = 0; // set RW to 0 (write mode)

IO_PDR5.bit.P52 = 1; // set E to 1 (initial state)

delay(1); // base delay is 16 us

IO_PDR5.bit.P52 = 0; // set E to 0 (H-L: final state)

readBF(); // read busy flag;

}

Reading the Busy Flag

Sample Code (C)

void readBF()

{

unsigned char flag;

IO_DDR2.byte = 0x00; // set direction of LCD data lines to input

IO_PDR5.bit.P50 = 0; // set RS to 0 (instruction register)

IO_PDR5.bit.P51 = 1; // set RW to 1 (read mode)

IO_PDR5.bit.P52 = 1; // set E to 1 (initial state)

do {

flag = IO_PDR2.bit.P27; // read bit 7 of Port 2 (busy flag)

} while (flag);

IO_PDR5.bit.P52 = 0; // set E to 0 (H-L: final state)

IO_DDR2.byte = 0xFF; // set direction of LCD data lines back to output

}

Seatwork #1

Flowchart and code for dataCtrl() -

function to send instruction to LCD (8-bit)

Flowchart and code for initLCD() -

function to send initialize the LCD (2-line,

Cursor on, blink off)

Demonstration #2

Flowchart for instCtrl() - function to send

instruction to LCD (4-bit)

Flowchart for

dataCtrl()

function 4-bit interface

(8-bit transfer)

Sample Code (C)

void instCtrl(unsigned char inst)

{

IO_DDR2.byte = inst >> 4; // transfer the upper 4-bit of inst to 4-bit LCD data line

IO_PDR2.bit.P24 = 0; // set RS to 0 (instruction register)

IO_PDR5.bit.P52 = 0; // set RW to 0 (write mode)

IO_PDR5.bit.P53 = 1; // set E to 1 (initial state)

delay(1); // delay for 16 us

IO_PDR5.bit.P53 = 0; // set E to 0 (H-L: final state)

IO_DDR2.byte = inst; // transfer the lower 4-bit of inst to 4-bit LCD data line

IO_PDR5.bit.P53 = 1; // set E to 1 (initial state)

delay(1); // delay for 16 us

IO_PDR5.bit.P53 = 0; // set E to 0 (H-L: final state)

readBF(); // read busy flag

}

Flowchart for instCtrl()

function 4-bit interface

(4-bit transfer for LCD initialization

purposes)

Seatwork #2

Flowchart and code for dataCtrl() -

function to send data to LCD (4-bit)

Demonstration #3

Displaying text to the LCD

displaying Hello! at the center of the 2nd line

Character Display Addresses

Line 1 (0x80 - 0x93)

Line 3 (0x94 - 0xA7)

Line 2 (0xC0 - 0xD3)

Line 4 (0xD4 - 0xE7)

Hello!

Line 1 address continue to Line 3 while Line 2 continues at Line 4.

Sample Code (C)

.

.

instCtrl(0xC6); // move cursor to 2nd line 7th column

dataCtrl(H); // prints H at current cursor position

// then shifts the cursor to the right*

dataCtrl(E); // prints E

dataCtrl(L); // prints L

dataCtrl(L); // prints L

dataCtrl(O); // prints O

dataCtrl(!); // prints !

.

.

* assuming configuration is cursor shift to right

Sources

Sharp HD44870 LCD Datasheet

Displaytech 204A Datasheet

You might also like

- Specification: ModelDocument25 pagesSpecification: ModelMohamed KamalNo ratings yet

- HD61830 PDFDocument43 pagesHD61830 PDFAnonymous x78Ua6JXNo ratings yet

- LCD Interfacing With MicrocontrollersDocument21 pagesLCD Interfacing With Microcontrollerstrinhdieuhvktqs100% (2)

- Interfacing LCD PICDocument33 pagesInterfacing LCD PICKhushal KharadeNo ratings yet

- LCD (Liquid Crystal Display)Document24 pagesLCD (Liquid Crystal Display)Giani Kumar100% (3)

- Lab6 LCDDocument19 pagesLab6 LCDPatipan Jariyapum100% (4)

- 16x2 LCD Display PinoutDocument16 pages16x2 LCD Display PinoutKarthik DmNo ratings yet

- Drive LCD - Ks0066uDocument34 pagesDrive LCD - Ks0066uJose SilvaNo ratings yet

- LCD Programming PDFDocument5 pagesLCD Programming PDFFadli Fatur RahmatNo ratings yet

- LCD Interfacing With Micro Controllers TutorialDocument44 pagesLCD Interfacing With Micro Controllers Tutorialramu497100% (1)

- ST7066UDocument42 pagesST7066UConIntNo ratings yet

- HJ1602A DatasheetDocument11 pagesHJ1602A DatasheetsunthomaNo ratings yet

- LCD 2 X 8Document4 pagesLCD 2 X 8dek_war100% (1)

- Weh002004alpp5n PDFDocument63 pagesWeh002004alpp5n PDFMartin MuszioNo ratings yet

- LCD PPTDocument41 pagesLCD PPTSneh Srijan100% (1)

- Adm1602k Nsa Fbs 3.3vDocument22 pagesAdm1602k Nsa Fbs 3.3vHer ManTokNo ratings yet

- Konfigurasi LCDDocument4 pagesKonfigurasi LCDAndwi Putra NugrahaNo ratings yet

- LCD Interfacing With Micro ControllersDocument4 pagesLCD Interfacing With Micro ControllersMijie Hj Hassan100% (1)

- Interfacing Graphical LCD With 8051: Submitted By: Rohan Dhakad Submitted To: Ambuj PanditDocument24 pagesInterfacing Graphical LCD With 8051: Submitted By: Rohan Dhakad Submitted To: Ambuj PanditRohan DhakadNo ratings yet

- LCD 4 Bit InterfacingDocument6 pagesLCD 4 Bit InterfacingYogesh Hardiya100% (1)

- LCD HD44780U (LCD-II) PC 1601-F + PC 0802-A - DatasheetDocument60 pagesLCD HD44780U (LCD-II) PC 1601-F + PC 0802-A - DatasheetLudwig SchmidtNo ratings yet

- LCD Data SheetDocument2 pagesLCD Data SheetGonzalo BojalilNo ratings yet

- PD 667 Profibus - Slave Configuration Guide.: IndexDocument7 pagesPD 667 Profibus - Slave Configuration Guide.: Indexwer974No ratings yet

- LCD 2 X 16 HD44780 Init CDocument15 pagesLCD 2 X 16 HD44780 Init CtauorusNo ratings yet

- A Presentation On: "16x2 LCD Interfacing With AVR Atmega32 Microcontroller "Document21 pagesA Presentation On: "16x2 LCD Interfacing With AVR Atmega32 Microcontroller "siddharthaNo ratings yet

- Training ReportDocument18 pagesTraining Reportpiyushji125No ratings yet

- Interfacing LCD Module To 8086Document7 pagesInterfacing LCD Module To 8086sreepadaravikumar100% (2)

- HD44780 CommandsDocument3 pagesHD44780 CommandsPhani ChakravarthiNo ratings yet

- Interfacing LCD With PIC Microcontroller - MPLAB XC8Document8 pagesInterfacing LCD With PIC Microcontroller - MPLAB XC8Marian VladianuNo ratings yet

- Gdm0802bflytw 19063127781Document18 pagesGdm0802bflytw 19063127781aristonrafaelNo ratings yet

- How To Control HD44780 DisplayDocument5 pagesHow To Control HD44780 DisplayUngureanu BiankaNo ratings yet

- Char CommDocument8 pagesChar CommfhidipNo ratings yet

- VFD ManualDocument19 pagesVFD Manualjoselazera5923No ratings yet

- Introduction of Moving Message Display Using Liquid Crystal Display and Micro Controller 8051 FamilyDocument13 pagesIntroduction of Moving Message Display Using Liquid Crystal Display and Micro Controller 8051 Familyishu58643No ratings yet

- Anadolu University Department of Electrical & Electronics Engineering EEM 336 Microprocessors 1 CHARACTER LCD INTERFACEDocument32 pagesAnadolu University Department of Electrical & Electronics Engineering EEM 336 Microprocessors 1 CHARACTER LCD INTERFACESĩ Anh NguyễnNo ratings yet

- Understanding the HD44780 LCD controllerDocument3 pagesUnderstanding the HD44780 LCD controllercking88No ratings yet

- Programming Pic Microcontrollers in Picbasic Pro - LCD Lesson 1 Cornerstone Electronics Technology and Robotics IiDocument15 pagesProgramming Pic Microcontrollers in Picbasic Pro - LCD Lesson 1 Cornerstone Electronics Technology and Robotics IiDomDoretoNo ratings yet

- LCD Module 4x20 - 3.73mm Controller KS0073Document4 pagesLCD Module 4x20 - 3.73mm Controller KS0073Narinder Singh100% (2)

- Technical Reference Options and Adapters Volume 2 1of3Document251 pagesTechnical Reference Options and Adapters Volume 2 1of3kgrhoadsNo ratings yet

- LCD - GDM1602BDocument10 pagesLCD - GDM1602BElanio Julio100% (1)

- 1602 LCD Module Instruction ManualDocument7 pages1602 LCD Module Instruction Manualjosman733No ratings yet

- Understanding LCDDocument7 pagesUnderstanding LCDOscar LyeNo ratings yet

- Led Display DriversDocument4 pagesLed Display DriverscybertechnicoNo ratings yet

- Mbe Fix32Document5 pagesMbe Fix32Cristina MonteiroNo ratings yet

- LCD Module User Manual Explains LMB162AFC DisplayDocument11 pagesLCD Module User Manual Explains LMB162AFC DisplayBima Richardo SihombingNo ratings yet

- Over Speed Indication and Automatic Accident Avoiding System For Four WheelerDocument28 pagesOver Speed Indication and Automatic Accident Avoiding System For Four WheelerMayank ChauhanNo ratings yet

- Seven Segment Display Document PDFDocument16 pagesSeven Segment Display Document PDFRekha MudalagiriNo ratings yet

- Submitted By: Aanchal Chaudhary Enrollment No.-Jnu-jpr-2011/00871Document17 pagesSubmitted By: Aanchal Chaudhary Enrollment No.-Jnu-jpr-2011/00871Sonu LovesforuNo ratings yet

- 8085 PRJ Schematic 1Document44 pages8085 PRJ Schematic 1Jani ServiniNo ratings yet

- GDM1602A LCD Module Specifications and Instruction SetDocument11 pagesGDM1602A LCD Module Specifications and Instruction SetAnonymous SFRw7ANo ratings yet

- Embeded PRJDocument7 pagesEmbeded PRJWiz Nati XvNo ratings yet

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3From EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Hilado Vs DavidDocument8 pagesHilado Vs DavidMark VillamorNo ratings yet

- Paguia Vs Office of The PresidentDocument5 pagesPaguia Vs Office of The PresidentMark VillamorNo ratings yet

- Villaflores Vs LimosDocument4 pagesVillaflores Vs LimosMark Villamor100% (1)

- Solatan Vs Inocentes (2005)Document12 pagesSolatan Vs Inocentes (2005)happymabeeNo ratings yet

- Interfacing Numeric Keypad With MB90F387SDocument18 pagesInterfacing Numeric Keypad With MB90F387SMark VillamorNo ratings yet

- 11 Cayetano V Monsod 201 Scra 210 1991Document33 pages11 Cayetano V Monsod 201 Scra 210 1991agy_11No ratings yet

- CprogramDocument56 pagesCprogramMark VillamorNo ratings yet

- NameDocument1 pageNameMark VillamorNo ratings yet

- CandidateHallTicket PDFDocument2 pagesCandidateHallTicket PDFHimanshu GuptaNo ratings yet

- ANSYS CFX-Solver Manager Users Guide PDFDocument192 pagesANSYS CFX-Solver Manager Users Guide PDFaliNo ratings yet

- Configure MATLAB uninstallerDocument3 pagesConfigure MATLAB uninstallerAlfonso PolaNo ratings yet

- DSP Using Matlab® - 4Document40 pagesDSP Using Matlab® - 4api-372116488% (8)

- Mpplus™ V C: Olume OrrectorDocument2 pagesMpplus™ V C: Olume OrrectorPaul Ramos CarcaustoNo ratings yet

- Drawing With Quartz 2 DDocument229 pagesDrawing With Quartz 2 DIma6_No ratings yet

- VirtualBox Windows 7 EngDocument24 pagesVirtualBox Windows 7 EngbvnageshaNo ratings yet

- Guide To Web Application DevelopmentDocument4 pagesGuide To Web Application DevelopmentHaftamu HailuNo ratings yet

- BCA Semester IV Assignments Software Engineering, Data Comms, Business Info SystemsDocument3 pagesBCA Semester IV Assignments Software Engineering, Data Comms, Business Info SystemsLovenueNo ratings yet

- Paperwork Simulation PacketDocument11 pagesPaperwork Simulation PacketHadi P.No ratings yet

- 254 53 680 1 10 20171109Document28 pages254 53 680 1 10 20171109zahruljrulefuadiNo ratings yet

- Cyber LawDocument16 pagesCyber LawAmrit Raz100% (1)

- Simulation With Arena Chapter 2 - Fundamental Simulation Concepts Slide 1 of 46Document24 pagesSimulation With Arena Chapter 2 - Fundamental Simulation Concepts Slide 1 of 46MAMuhammadFikriAkbarNo ratings yet

- Equipment and Controls for Automatic Transfer Systems (ATSDocument7 pagesEquipment and Controls for Automatic Transfer Systems (ATSrajneesh jainNo ratings yet

- ETS Math Misc QuestionsDocument27 pagesETS Math Misc QuestionsAleksandra VoineaNo ratings yet

- Time Domain Based Active Power CalculationDocument12 pagesTime Domain Based Active Power CalculationFrank CifuentesNo ratings yet

- Cfgpro08 PDFDocument64 pagesCfgpro08 PDFSalvador FayssalNo ratings yet

- Design Pattern Mock Test IDocument6 pagesDesign Pattern Mock Test IAhmad RamadanNo ratings yet

- Google Earth y Civil CadDocument3 pagesGoogle Earth y Civil CadRodneyNo ratings yet

- Refrigerator: Samsung Smart Home User ManualDocument3 pagesRefrigerator: Samsung Smart Home User ManualWilliam NoeNo ratings yet

- ADT ListDocument3 pagesADT ListCicio FlaviuNo ratings yet

- EBS122 DevgDocument756 pagesEBS122 Devgzakir_hNo ratings yet

- TCS AssignmentDocument9 pagesTCS AssignmentSupriya Gunthey RanadeNo ratings yet

- Dynamic PricingDocument9 pagesDynamic PricingkoolboyankitNo ratings yet

- Python Railway ReservationDocument41 pagesPython Railway ReservationDiivesh45% (69)

- RSFactoryTalk SE & Microsoft SQL Server - PLCSDocument3 pagesRSFactoryTalk SE & Microsoft SQL Server - PLCSrodriggoguedesNo ratings yet

- Train Ticket NEP04165Document3 pagesTrain Ticket NEP04165PANKAJ GANGWARNo ratings yet

- Hipath 1100 Hipath 1120 Hipath 1150 Hipath 1190: Analog MF Telephones Programming ManualDocument241 pagesHipath 1100 Hipath 1120 Hipath 1150 Hipath 1190: Analog MF Telephones Programming ManualMaria StoicaNo ratings yet

- Java Developer Sadhana GDocument7 pagesJava Developer Sadhana GrecruiterkkNo ratings yet