Professional Documents

Culture Documents

EX-NOR Gates Series Circuit Explained

Uploaded by

Dinesh ReddyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EX-NOR Gates Series Circuit Explained

Uploaded by

Dinesh ReddyCopyright:

Available Formats

Q1. N number of EX-NOR gates is connected in series such that the N inputs (A0, A1, A2......

) are given in

the following way:

A0 and A1 is being given to first EX-NOR gate and A2 and output of first EX-NOR is being given to second

EX-NOR gate and so on. Nth EX-NOR gate's output is final output. How does this circuit work? Explain in

detail?

Q2. A component called "CMPR" with 2 inputs - A and B, and 2 outputs - K and R. If you pass 2 n-bit

numbers to the component CMPR, the component produced the biggest number at the output K and

the smallest number at the output R.

Using minimum numbers of these components "CMPR", Design a component "ARK" with 4 inputs A, B, C

and D and 4 outputs P, Q, R and S in which

'P' is the max (A, B, C, D), 'S' is the min(A, B, C, D). 'Q' is bigger than 'R' but smaller than 'P' and 'R' is

bigger than 'S' and smaller than 'Q'

Q3. In a base-7 number system having the digits 0,1,2, A,B,6 respectively and their place values are -3,-

2,-1,0,+1,+2,+3 respectively, then:

a). What is the maximum decimal value that can be formed?

b). (A0B1) + (1AB0) = ?

Q4. Perform BCD addition and subtraction of following

a). 87 39

b) 18 72

c). 65 12

Q5. Represent following decimal numbers in OCTAL

a). 128

b). 123

c). 8

Q6. Design a state machine, that outputs a '1' one and only when two of the last 3 inputs are '1'. For

example, if the input sequence is 0110_1110 then the output will be 0011_1101. Assume that the input

'Z' is a single bit serial line.

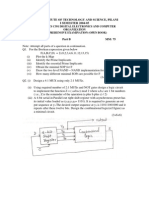

Q7. What is tpd (Propagation delay) for this circuit?

What is tcd (Contamination delay) for this circuit?

What is tpd of the fastest equivalent circuit built using only above 3 components?

Here: tpd - Max. cumulative propagation delay considering all path b/w input and output.

tcd - Min. cumulative contamination delay

Inverter: tcd = 0.5ns, tpd = 1.0ns, tr = tf = 0.7ns

2-input NAND: tcd = 0.5ns, tpd = 2.0ns, tr = tf = 1.2ns

2-input NOR: tcd = 0.5ns, tpd = 2.0ns, tr = tf = 1.2ns

Q8. Construct a synchronous moore state machine with two inputs, A and B, and two outputs, X and Y.

The machine accepts data on two input lines synchronously with the clock. The output X is 1 if and only

if the data on the two input lines have been identical (i.e. A and B are both 1, or A and B are both 0) for

the last three or more consecutive clock cycles. Output Y is 1 if and only if the data on the two input

lines have been complements of each other (i.e. A = 1 and B = 0, or A = 0 and B = 1) for the last three or

more consecutive clock cycles.

Q9. During third world war in the land of Logicia in the year 2099 there is a shortage of XOR gates.

Unfortunately, the only logic gates available are two weird components called X and Y. The truth

table of both components is presented below - Z represents a High-Z value on the output. Could you

help the poor engineers of Logicia to build an XOR gate?

Q10. Construct a 4-bit Johnson counter using 4-bit shift register and inverter cell.

Q11. Construct a 4-bit Johnson counter using a ring counter.

Q12. Write a verilog code for following circuits

a). 1-Bit D-flip flop

b). 1-Bit toggle (T) flip flop

c). Clock divider by 6 with 50 % duty cycle using 1-Bit D & T flip flops

d). Clock divider by 3 with 50 % duty cycle using 1-Bit D & T flip flop

Q13. Write a Verilog code for Factorial N

Q14. A and B are the signed inputs to an arithmetic circuit. A is 8-bit width and B is 5-bit width. Write

Verilog code to generate following outputs,

X = A + B;

Y = A * B

Z = B - A

Q15. Write a Verilog code using function. The inputs to function are A, B, and C, each input is of

n-bit width. Function should return following outputs X, Y, Z,

X = A + B;

Y = X * C;

Z = A*C + B *C;

Q16: Draw the waveforms for the following

reg clk ;

reg q;

always #10 clk = ~clk;

a). always @(clk) q = #5clk;

b). always @(clk) q = #10 clk;

c). always @(clk) q = #15 clk;

Q12: Draw the waveforms for the following

reg clk ;

wire q;

a). assign #5 q = clk;

b). assign #10 q = clk;

c). assign #15 q = clk;

You might also like

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- IES - Electronics Engineering - Digital Electronic CircuitsDocument66 pagesIES - Electronics Engineering - Digital Electronic Circuitsedwinaustine100% (4)

- LTE X2 Handover MessagingDocument13 pagesLTE X2 Handover MessagingManish KumarNo ratings yet

- MSCRM Interview Questions and AnswersDocument11 pagesMSCRM Interview Questions and Answersadikesa100% (1)

- Firewall Audit ChecklistDocument10 pagesFirewall Audit ChecklistChidi OkerekeNo ratings yet

- TurnitinDocument2 pagesTurnitindivya100% (1)

- AlrtrmDocument136 pagesAlrtrmRakesh SharmaNo ratings yet

- Max Clock Frequency D-FF Circuit Buffer Design Latchup Prevention State Machines 2's Complimenter/TITLEDocument27 pagesMax Clock Frequency D-FF Circuit Buffer Design Latchup Prevention State Machines 2's Complimenter/TITLERui ChenNo ratings yet

- Combinatorial Algorithms: For Computers and CalculatorsFrom EverandCombinatorial Algorithms: For Computers and CalculatorsRating: 4 out of 5 stars4/5 (2)

- DCEPFDocument11 pagesDCEPFkanishkhatanaNo ratings yet

- Questions On Digital Electronics and MicroprocessorsDocument12 pagesQuestions On Digital Electronics and MicroprocessorsHarendra KumarNo ratings yet

- Logic GateDocument12 pagesLogic Gateapi-254068557No ratings yet

- VIT University B.Tech ECE Question Paper on VLSI System DesignDocument6 pagesVIT University B.Tech ECE Question Paper on VLSI System DesignvlsisivaNo ratings yet

- United International University (UIU) : Dept. of Computer Science& Engineering (CSE)Document2 pagesUnited International University (UIU) : Dept. of Computer Science& Engineering (CSE)mahbub mitulNo ratings yet

- 2_Tutorial on Convolutional Coding with Viterbi Decoding--Description of the Data Generation, Convolutional Encoding, Channel Mapping and AWGN, and Quantizing Algorithms_2Document6 pages2_Tutorial on Convolutional Coding with Viterbi Decoding--Description of the Data Generation, Convolutional Encoding, Channel Mapping and AWGN, and Quantizing Algorithms_2Darshan Yeshwant MohekarNo ratings yet

- Adder Notes MergedDocument63 pagesAdder Notes MergedPavan SinghNo ratings yet

- Da2 271222Document4 pagesDa2 271222rh457707No ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- UCSB ECE 152a Course ReaderDocument19 pagesUCSB ECE 152a Course Readermuhd220No ratings yet

- 5 - Logic CircuitsDocument32 pages5 - Logic CircuitsPrabath De SilvaNo ratings yet

- 2006Document11 pages2006simplymeashishNo ratings yet

- De FileDocument69 pagesDe FileRanu SharmaNo ratings yet

- E2.11/ISE2.22 - Digital Electronics IIDocument5 pagesE2.11/ISE2.22 - Digital Electronics IIDivya MittalNo ratings yet

- Dig2E 2014 Annotated&CorrectedDocument16 pagesDig2E 2014 Annotated&CorrectedvpsampathNo ratings yet

- Sample CSE370 Final Exam Questions: Logic MinimizationDocument8 pagesSample CSE370 Final Exam Questions: Logic MinimizationQaseem HussainNo ratings yet

- Pipelined Circuits Worksheet: Concept InventoryDocument8 pagesPipelined Circuits Worksheet: Concept InventoryBhargav Vara PrasadNo ratings yet

- Practice Assignment No-4Document8 pagesPractice Assignment No-4Seemab RamzanNo ratings yet

- Sequential CircuitsDocument33 pagesSequential CircuitsPrasun SinghalNo ratings yet

- Workshop Week 4 PDFDocument4 pagesWorkshop Week 4 PDFStevenRNo ratings yet

- LAB MANUAL EXPERIMENTSDocument61 pagesLAB MANUAL EXPERIMENTSKhurshid AlamNo ratings yet

- Diksha, Mannnat CSADocument24 pagesDiksha, Mannnat CSATwinkle SadanaNo ratings yet

- MSQ Session 5 19Document30 pagesMSQ Session 5 19Voleti VnkumarNo ratings yet

- Logic FamiliesDocument9 pagesLogic FamiliesJNo ratings yet

- GATE+ISRO DIGITAL LOGIC AND COMPUTER ORGANIZATION 2015 - Sequential CircuitsDocument35 pagesGATE+ISRO DIGITAL LOGIC AND COMPUTER ORGANIZATION 2015 - Sequential CircuitsRejinRajanNo ratings yet

- University of Edinburgh College of Science and Engineering School of Engineering and ElectronicsDocument15 pagesUniversity of Edinburgh College of Science and Engineering School of Engineering and ElectronicsSyed Fasih Ur RehmanNo ratings yet

- Logic Gates Lab IntroductionDocument6 pagesLogic Gates Lab IntroductionZbiggNo ratings yet

- ECN 252 Lab 6 - Design of D Flip-Flop and CountersDocument2 pagesECN 252 Lab 6 - Design of D Flip-Flop and CountersRUSHIL MOTWANINo ratings yet

- VLSI & ASIC Digital Design Interview QuestionsDocument6 pagesVLSI & ASIC Digital Design Interview QuestionsRupesh Kumar DuttaNo ratings yet

- Combinational Devices and ASM ChartsDocument10 pagesCombinational Devices and ASM ChartsSunny KumarNo ratings yet

- DigitalDocument182 pagesDigitalYeshoda MallikarjunaNo ratings yet

- 2001 Paper E2.1/ISE2.2: Digital Electronics IIDocument12 pages2001 Paper E2.1/ISE2.2: Digital Electronics IIkolkassNo ratings yet

- Assignment 2021-22Document2 pagesAssignment 2021-22Dan Ojwang100% (2)

- VTU Updates: Digital Logic Families, Combinational Circuit Design & SimulationDocument39 pagesVTU Updates: Digital Logic Families, Combinational Circuit Design & SimulationSYED Sahil GhouseNo ratings yet

- Traffic Congestion SolutionsDocument22 pagesTraffic Congestion SolutionsAlexander JereMy SolovovNo ratings yet

- Digital Electronics: An Overview of Key ConceptsDocument14 pagesDigital Electronics: An Overview of Key ConceptsDebbie UzoNo ratings yet

- EC8392-Digital EletronicsDocument2 pagesEC8392-Digital Eletronicssyed1188No ratings yet

- Ec 2007Document11 pagesEc 2007mallanna4blogsNo ratings yet

- Practice Questions For The FinalDocument4 pagesPractice Questions For The FinalTran TinhNo ratings yet

- EC - CE08 - Digital Circuits: Test SummaryDocument16 pagesEC - CE08 - Digital Circuits: Test Summarysaravanababu jayapalNo ratings yet

- Lab Design and Analysis of Active CS and Cascode AmplifierDocument3 pagesLab Design and Analysis of Active CS and Cascode AmplifierAzure HereNo ratings yet

- Digital Logic Design Lab Manual Assignment 1Document13 pagesDigital Logic Design Lab Manual Assignment 1Pirzada SwatiNo ratings yet

- Assignment 5Document3 pagesAssignment 5Anshik BansalNo ratings yet

- Within : Indian Institute of TechnologyDocument2 pagesWithin : Indian Institute of TechnologyIndranilNo ratings yet

- Assignment 6: Transistor/Gate/Logic Due Date: Wednesday 4/02/2020Document5 pagesAssignment 6: Transistor/Gate/Logic Due Date: Wednesday 4/02/2020ZERO TO VARIABLENo ratings yet

- EEE241fİNAL2022 1Document4 pagesEEE241fİNAL2022 1mfp.plt453No ratings yet

- Solutions Mid Ceg3185 2014wDocument6 pagesSolutions Mid Ceg3185 2014wMoe ShantiNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- Electrical, Digital and Industrial Circuits: IT IL IcDocument4 pagesElectrical, Digital and Industrial Circuits: IT IL IcNGOUNENo ratings yet

- 2-Bit Multiplier M B A: Don't Worry About This Question Because This Particular Method Was Not Presented in ClassDocument8 pages2-Bit Multiplier M B A: Don't Worry About This Question Because This Particular Method Was Not Presented in ClassMarlon BoucaudNo ratings yet

- Convolutional (Viterbi) Encoding: Input A Input B OutputDocument14 pagesConvolutional (Viterbi) Encoding: Input A Input B Outputeliezer lopezNo ratings yet

- QuestionDocument80 pagesQuestionRodalie Vale CruzNo ratings yet

- ACM International Collegiate Programming Contest 2009/10 ProblemsDocument15 pagesACM International Collegiate Programming Contest 2009/10 ProblemsHao DoNo ratings yet

- VL2019205005389 Da PDFDocument44 pagesVL2019205005389 Da PDFsimon jordan1005No ratings yet

- T6320 Server ModuleDocument150 pagesT6320 Server ModuleMomin HamidNo ratings yet

- Distributed DatabasesDocument39 pagesDistributed DatabasesKandiga ParandhamanNo ratings yet

- Tutorial Dev C++Document4 pagesTutorial Dev C++Wasdodi Al-AssaNo ratings yet

- Forest Fire Detection Using Sensor NetworksDocument13 pagesForest Fire Detection Using Sensor NetworksMuskan AgarwalNo ratings yet

- Session and State ManagementDocument89 pagesSession and State Managementayush VishwakarmaNo ratings yet

- Mobile Legends Android Crash Log AnalysisDocument76 pagesMobile Legends Android Crash Log Analysisjoshua alejandroNo ratings yet

- Implement Dijkstra's AlgorithmDocument4 pagesImplement Dijkstra's AlgorithmSharad KumbharanaNo ratings yet

- An Introduction' To Computing With Neural Nets: Richard P. LippmannDocument19 pagesAn Introduction' To Computing With Neural Nets: Richard P. LippmannSathish Kumar KarneNo ratings yet

- OS Unit1Document60 pagesOS Unit1Vijay JangidNo ratings yet

- Oracle SQL QueryDocument7 pagesOracle SQL Querybhaskar1234567No ratings yet

- Microprocessor Interfacing - Interfacing ConceptsDocument17 pagesMicroprocessor Interfacing - Interfacing ConceptsMim Fauzi50% (2)

- Bit TwiddlingDocument90 pagesBit TwiddlingKritika Agrawal100% (1)

- Micro Controller Risc ArchitecturesDocument33 pagesMicro Controller Risc ArchitecturesSankar SubramaniamNo ratings yet

- WS5200 Advanced System Management Software Operation Manual 2-13Document98 pagesWS5200 Advanced System Management Software Operation Manual 2-13Mohamed SayedNo ratings yet

- GTest Vs CppUnitDocument2 pagesGTest Vs CppUnitSannayila SahithiNo ratings yet

- Another 5 Questions To Be Added On Fri 15 June. To Date There Are 23 Questions Test Will Be A Selections of About 80% of The TotalDocument7 pagesAnother 5 Questions To Be Added On Fri 15 June. To Date There Are 23 Questions Test Will Be A Selections of About 80% of The TotalAsad NaqviNo ratings yet

- Common Sense Architecture PDFDocument2 pagesCommon Sense Architecture PDFLaurenNo ratings yet

- Exception Handling in CPP PDFDocument2 pagesException Handling in CPP PDFRobertNo ratings yet

- Newos Lab Manual CS2257Document37 pagesNewos Lab Manual CS2257Pavithran ChandarNo ratings yet

- JADMaker for Nokia Java GamesDocument2 pagesJADMaker for Nokia Java GamesIader Camilo Martinez PeinadoNo ratings yet

- Register initiators Unisphere configure VNX VPLEXDocument14 pagesRegister initiators Unisphere configure VNX VPLEXvenubabu_anchaNo ratings yet

- NexentaStor 5.2 CLI Config Guide RevBDocument150 pagesNexentaStor 5.2 CLI Config Guide RevBkieng_canNo ratings yet

- Website Security Report Reveals Multiple VulnerabilitiesDocument17 pagesWebsite Security Report Reveals Multiple Vulnerabilitiesanupprakash36No ratings yet

- CN Lab ManualDocument42 pagesCN Lab Manualnaresh reddyNo ratings yet

- Brute Force Attack With Burp Suite: Adita - Si: Maximize Information System Value For BusinessDocument35 pagesBrute Force Attack With Burp Suite: Adita - Si: Maximize Information System Value For Businessbudi.hw748No ratings yet