Professional Documents

Culture Documents

Simplificacion

Uploaded by

Luis Mamani0%(1)0% found this document useful (1 vote)

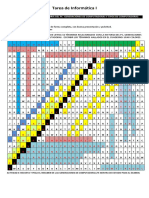

639 views41 pagesEste documento presenta ejercicios sobre simplificación booleana y diseño lógico. Incluye problemas sobre álgebra booleana, tablas de verdad, diagramas de lógica, expresiones booleanas y su implementación con compuertas lógicas. También introduce conceptos de lenguajes de descripción de hardware como Verilog HDL para modelar circuitos digitales.

Original Description:

Original Title

simplificacion

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentEste documento presenta ejercicios sobre simplificación booleana y diseño lógico. Incluye problemas sobre álgebra booleana, tablas de verdad, diagramas de lógica, expresiones booleanas y su implementación con compuertas lógicas. También introduce conceptos de lenguajes de descripción de hardware como Verilog HDL para modelar circuitos digitales.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0%(1)0% found this document useful (1 vote)

639 views41 pagesSimplificacion

Uploaded by

Luis MamaniEste documento presenta ejercicios sobre simplificación booleana y diseño lógico. Incluye problemas sobre álgebra booleana, tablas de verdad, diagramas de lógica, expresiones booleanas y su implementación con compuertas lógicas. También introduce conceptos de lenguajes de descripción de hardware como Verilog HDL para modelar circuitos digitales.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 41

Instituto Tecnolgico de Costa Rica

Escuela de Ingeniera Electrnica

EL 3307 Diseo Lgico

Ejercicios

Tema: Simplificacin

Recopilacin realizada por:

Ing. Jos Alberto Daz Garca

Diciembre 2008

1 of 41

I

mina con la generacin de la base de datos que contiene la mscara fotogrfica empleada pa-

ra fabricar el CI. Se cuenta con diversas opciones para crear la implementacin fsica de un cir-

cuito digital en silicio. El diseador puede escoger entre un circuito integrado para una aplicacin

especfica (ASIC, application-specific integrated circuit), un arreglo de compuertas progra-

mable en el campo (FPGA,field-programmable gate a"ay), un dispositivo de lgica programa-

ble (PLD, programmable logic device) o un CI hecho totalmente a la medida. Cada uno de

estos dispositivos viene acompaado de un surtido de herramientas de CAD que proporciona

el software necesario para facilitar la fabricacin en hardware de la unidad.

Algunos sistemas de CAD incluyen un programa editor para crear y modificar diagramas

esquemticos en la pantalla de una computadora. Este proceso se llama captura de esquemas

o introduccin de esquemas. Con la ayuda de mens, rdenes del teclado y el ratn, el editor

de esquemas puede dibujar diagramas de circuitos digitales en la pantalla de la computadora.

Es posible colocar en la pantalla componentes de una lista tomada de una biblioteca interna y

luego conectarse con lneas que representan alambres. El software para captura de esquemas

crea y administra una base de datos que contiene la informacin creada junto con el esquema.

Las compuertas y bloques funcionales primitivos estn asociados con modelos que permiten

verificar el comportamiento y la temporizacin del circuito. Esta verificacin se efecta apli-

cando entradas al circuitto y utilizando un simulador de lgica para determinar las salidas.

Un adelanto importante en el diseo de sistemas digitales es el uso de un lenguaje de descrip-

cin de hardware (HDL). El HDL se parece a los lenguajes de programacin, pero est orienta-

do especficamente a la descripcin de hardware digital. Representa diagramas de lgica y otra

informacin digital en forma textual. Sirve para simular el sistema antes de construirlo, a fin de

verificar la funcionalidad y la operacin. Una aplicacin importante es su software de sntesis l-

gica, que automatiza el diseo de sistemas digitales. El HDL ha adquirido gran importancia en

aos recientes y es el mejor mtodo con que se cuenta para disear sistemas digitales complejos.

Presentaremos el HDL en la seccin 3-9 y, dada su importancia, se incluyen en todo el libro des-

cripciones de circuitos digitales, componentes y procedimientos de diseo en HDL.

PROBLEMAS

2-1

Demuestre con tablas de verdad la validez de las identidades siguientes:

a) Teorema de DeM<Xgan para b'es variables: (x + y + z)' = x'y'z' y (xyz)' = x' + y' + 1:'

b) La ley distributiva: x + yz = (x + y)(x + z)

Simplifique las expresiones booleanas siguientes de modo que usen el nnimo de literales:

a) xy + xy' b) (x + y)(x + y')

c) xyz + x'y + xyz' d) (A + B)'(A' + B')'

Simplifique las expresiones booleanas siguientes de modo q~ usen el mnimo de literales:

a) ABC + A'B + ABC' b) x'yz + xz

c) (x + y)'(x' + y') d) xy + x(wz + wz')

e) (BC' + A'D)(AB' + CD')

Reduzca las siguientes expresiones booleanas al nmero de literales que se indica:

a) A'C' + ABC + AC' a tres literales

b) (x' y' + z)' + z + xy + wz a tres literales

""'--

c) A'B(D' + C'D) + B(A + A'CD) a una literal

d) (A' + C)(A' + C')(A + B + C'D) -a cuatro literales .

2-2

2-3

2-4

~

Problemas 61

2 of 41

62 Captulo 2 lgebra booleana y compuertas lgicas

2-5 Obtenga el complemento de F = x + y:. luego dem~ q~ FF = O y que F + F - 1.

2-6 Obtenga el complemento de estas expresiones:

a) xy' + x'y , b) (AB' + C)D' + E

c) (x + y' + z)(x' + z')(x + y)

2-7 Dadas las funciones booleanas F, y F2'

a) Demues~ que la funcin booleana E = F. + F2 contiene la suma de los minitnni-

nosdeF,yF2o

b) Demues~ que la funcin booleana G = F,F2 contiene nicamente los mini~rminos

que F, y F2 tienen en comn.

2-8 Muestre la tabla de verdad de la funcin:

F = xy + xy' + y' z

2-9 Podemos realizar operaciones lgicas con cadenas de bits considerando por separado ca-

da par de bits correspondientes (esto se denomina operacin bit por bit). Dadas dos cade-

nas de ocho bitsA = 10101101 Y B = 10001110, evale el resultado de ocho bits despu~s

de las operaciones lgicas siguientes: a) AND, b) OR, c) XOR. d) NffiA, e) Nffi B.

2-10 Dibuje los diagramas de lgica de las expresiones booleanas siguientes:

a) Y=A'B'+B(A+C) b) Y=BC+AC'

c) y = A + CD d) y = (A + B)(C' + D)

2- 11 Dada la funcin booleana:

F = xy + x' y' + y' z

a) implemntela con compuertas AND, OR e inversores,

b ) implem~ntela con compuertas OR e inversores, y

c) implem~ntela con compuertas ANO e inversores.

2- 12 Simplifique las funciones booleanas TI y T 2 al nnimo de literales.

,

2- 13 La suma lgica de todos los minitnninos de una funcin booleana de n variables es 1.

a) Demuestre la afinnacin anterior para n = 3.

b) Sugiera un procedimiento para una demostracin general.

2 -14 Prepare la tabla de verdad de las funciones siguientes y exprese cada funcin como suma

de minitrminos y como producto de maxitnninos:

a) (xy + z)(y + Xl) b) (A' + 8)(8' + C)

c) y'z + wxy' + wxz' + w'x'z

B

T,

A

12

o

o

1

1

O

O

1

1 .

1

1

1

O

O

O

O

O

o

o

o

o

1

1

1

1

o

1

O

1

O

1

O

o

o

o

1

1

1

1

1 1

3 of 41

~

2-15 Dada la funcin booleana

a) Prepare la tabla de verdad de la funcin.

b) Dibuje el diagrama de lgica empleando la expresin booleana original.

c) Simplifique la funcin al mnimo de literales empleando lgebra booleana.

d) Prepare la tabla de verdad de la funcin a panir de la expresin simplificada y de-

muestre que es igual a la de la parte a).

e) Dibuje el diagrama de lgica de la expresin simplificada y compare el nmero total

de compuertas con el diagrama de la parte b).

2-16 Exprese la siguiente funcin como suma de mini trminos y como producto de maxitr-

minas.

2- 17 Exprese el complemento de las siguientes funciones como suma de mini~nninos:

a) F(A,B,C,D)= ~(0,2,6,11,13,14) b) F(x,y,z) = 0(0,3,6,7)

2. 18 Convierta lo siguiente a la otra forma cannica:

a) F(x,y,z)= ~(I,3,7) b) F(A,B,C,D) = 0(0,1,2,3,4.6.12)

2-19 Convierta las expresiones siguientes a suma de productos y producto de sumas:

a) (AB + C)(B + C'D) b) x' + x(x + y')(y + z')

2- 20 Diooje el diagrama de lgica conespondiente a las siguientes expresiOla booleanas sin sim-

plificarlas:

a) BC' + AB + ACD b) (A + B)(C + D)(A' + B + D)

c) (AB + A'B')(CD' + C'D)

2-21 Demuestre que el dual del OR exclusivo es igual.a su complemento.

2- 22 Sustituyendo la expresin booleana equivalente de las operaciones binarias definidas en la

tabla 2-8, demuestre lo siguiente:

a) La operacin de inhibicin no es conmutativa ni asociativa.

b) La operacin de OR exclusivo es conmutativa y asociativa.

2-23 Demuestre que una compuerta NAND de lgica positiva es una compuerta NOR de lgi-

ca negativa, y viceversa.

REFERENCIAS

1. BooLE, G. 1954. An lnvestigation ofthe lllws ofThought. Nueva York: Dover.

2. SHANNON, C. E. A symbolic analysis o relay and switching circuits. Trans. AfEE 57 (1938):

713-723.

3. HUN11NOTON. E. V. Sets o independent postulates or the algebra o logic. Trans. Ana.

Math. Soc.. S (1904): 288-309.

4. MANO, M. M. Y C. R. KIME. 2<XM>. Logic and Computer Design Fundamentals, 2a. ed.

Upper Saddle River, NJ: Prentice-Hall.

5. DIETMEYER. D. L. 1988. Logic Design of Digital Systems. 3a. ed. Boston: AlIyn BKOD.

Referencias 63

F = xy'z + x'y'z + VJ'xy + VJx'y + VJxy

F(A, S, C, D) = B'D +

A'D + BD

4 of 41

106

Captulo 3

Minimizacin en el nivel de compuertas

. Puede haber cualquier nmero de entradas. El orden en que aparecen en la declaracin

input debe ser el mismo en el que se les asigna valores en la tabla que sigue.

. La tabla de verdad se encierra entre las palabras clave table y endtable.

. Los valores de las entradas se dan en orden terminando con un signo de dos puntos (:).

La salida siempre es el ltimo elemento de una fila y va seguida de un punto y coma (;).

. Termina con la palabra clave endprimitive.

Observe que las variables que se pusieron como cabeceras de la tabla forman parte de un co-

mentario y slo se han incluido por claridad. El sistema reconoce las variables por el orden en

que aparecen en la declaracin input. Las primitivas definidas por el usuario se utilizan en la

construccin de otros circuitos digitales igual que las primitivas del sistema. Por ejemplo, la de-

claracin

produce un circuito que implementa

con entradas x, y, z y salida w.

Aunque Verilog HDL utiliza este tipo de descripcin nicamente para las UDP, otros HDL

particulares y sistemas de diseo asistido por computadora (CAD) emplean otros procedimien-

tos para especificar circuitos digitales en forma tabular. El software de CAD puede procesar las

tablas y deducir una estructura eficiente de compuertas para el diseo.

Esta seccin constituye una introduccin a HDL, presentando ejemplos sencillos de mode-

lado estructural. En el captulo que sigue se har una presentacin ms detallada de Verilog HDL.

El lector que ya est familiarizado con los circuitos combinacionales podr pasar directamen-

te a la seccin 4-11 para continuar con este tema.

PROBLEMAS

3- 1 Simplifique las siguientes funciones booleanas empleando mapas de tres variables:

a) F(x, y, z) = ~ (0,2,6,7) b) F(A, B, c) = ~(O, 2, 3,4,6)

c) F(a,b,c) = ~ (O, 1,2,3,7) d) F(x,y,z) = ~S(3,5,6,7)

3-2 Simplifique las siguientes funciones booleanas empleando mapas de tres variables:

a) F(x,y,z) = ~(O,I,5,7) b) F(x,y,z) = ~(1,2,3,6,7)

3 - 3 Simplifique las siguientes expresiones booleanas empleando mapas de tres variables:

a) xy + x'y'z' + x'yz' b) x'y' + yz + x'yz'

c) A'B + BC' + B'C'

3 -4 Simplifique las siguientes funciones booleanas empleando mapas x:

a) F(x,y,z) =~(2,3,6,7) b) F(A,B,C,D) = ~(4,6,7,15)

c) F(A, B, C, D) = ~ (3,7,11,13,14,15) d) F(w, x, y, z) = ~(2, 3,12,13,14,15)

3-5 Simplifique las siguientes funciones booleanas empleando mapas de cuatro variables:

a) F(w, x, y, z) = ~(1, 4, 5, 6,12,14,15)

b) F(A,B,C,D) = ~(O,I,2,4,5,7,ll,15)

c) F( w, x, y, z) = ~(2, 3, 10, 11, 12, 13, 14, 15)

d) F(A, B, C, D) = ~(O, 2, 4, 5, 6, 7, 8,10,13,15)

(W,x,y,z)

5 of 41

3-6 Simplifique las siguientes ex~iones booleanas empleando mapas de cuatro variables:

a) A'B'C'D' + AC'D' + B'CD' + A'BCD + BC'D

b) x'z + w'xy' + w(x'y + xy')

3- 7 Simplifique las siguientes expresiones booleanas empleando mapas de cuatro variables:

a) w'z + xz + x'y + wx'z b) B'D + A'BC' + AB'C + ABC'

c) AB'C + B'C'D' + BCD + ACD' + A'B'C + A'BC'D

d) wxy + yz + xy'z + :x'y

3-8

Encuentre los minitrminos de las siguientes expresiones booleanas graficando primero cada fun-

cin en un mapa:

a) xy + yz + xy'z b) C'D + ABC' + ABD' + A'B'D

c) wxy + x'z' + w'xz

:.

t:;;

~.

""

'S

;~,

3-9 Encuentre todos los implicantes primos de las siguientes

son esenciales:

a) F(w,x,y,z) = ~(O,2,4,5,6,7,8,10,13,15)

b) F(A, S, C, D) = ~(O, 2, 3, 5, 7, 8,10,11,14,15)

c) F(A, S, C, D) - ~(l, 3, 4, S, 10, 11, 12, 13, l., lS)

Problemas 107

deduzca funciones booleanas y cules

6 of 41

Minimizacin en el nivel de compuertas

108 Captulo 3

3- 19 Simplifique las funciones siguientes e implemntelas con circuitos de compuertas NOR de dos

niveles:

a) F =Wx' +y'z' +w'yz' b) F(w,x,y,z) = ~(5,6,9,IO)

3-20 Dibuje el circuito NAND de mltiples niveles para esta expresin:

(AB' + CD')E + BC(A + B)

3-21 Dibuje el circuito NOR de mltiples niveles para esta expresin:

w(x + y + z) + xyz

3-22 Convierta el diagrama lgico del circuito mostrado en la figura 4-4 en un circuito NAND mul-

tinivel.

3-23 Implemente la siguiente funcin booleana F, que tiene las condiciones de indiferencia d, em-

pleando no ms de dos compuertas NOR:

F(A, B, C, D) =

d(A, B, C, D) =

Suponga que cuenta con las entradas normales y con sus complementos.

3-24 Implemente la siguiente funcin booleana F empleando las formas de dos niveles a) NAND-

AND, b) AND-NOR, c) OR-NAND, y d) NOR-OR:

F(A,B,C,D) = ~(O,I,2,3,4,8,9,12)

3-2.5 Enumere las ocho formas degeneradas de dos niveles y demuestre que se reducen a una sola ope-

racin. Explique cmo usar las formas degeneradas de dos niveles para extender el nmero de en-

tradas de una compuerta.

3-26 Con la ayuda de mapas, encuentre la forma de suma de productos ms simple de la funcin

F = fg, donde f y g son, respectivamente,

f = wxy' + y'z + w'yz' + x'yz'

y

g = (w + x + y' + z')(x' + y' + z)(w' + y + z')

Demuestre que el dual del OR exclusivo tambin es su complemento.

Deduzca los circuitos de un generador de paridad de tres bits y un verificador de paridad de cua-

tro bits empleando un bit de paridad impar.

Implemente estas cuatro expresiones booleanas:

D=AeBeC

E = A'BC + AB'C

F = ABC' + (A' + B')C

G = ABC

Implemente esta expresin booleana con compuertas OR exclusivo y AND:

F = AB'CD' + A'BCD' + AB'C'D + A'BC'D

Escriba en HDL la descripcin de estructura de compuertas del circuito de la figura 3-22a).

El circuito OR exclusivo de la figura 3-32a) tiene compuertas con retardo de 10 ns para los in-

versores, 20 ns para las compuertas AND y 30 ns para las compuertas ORo La entrada del circui-

to pasa de xy = OOaxy = 01.

a) Deduzca las seales en la salida de cada compuerta desde t = O hasta t = 50 ns.

3.27

3-28

3-29

3.30

3-31

3-32

~(O, 1,2,9,11)

~(8, 10, 14, lS)

7 of 41

b) Escriba la descripcin HDL del circuito, incluyendo los retardos.

c) Escriba un mdulo de estmulo (similar al ejemplo HDL 3-3) Y simule el circuito para veri-

ficar la respuesta de la parte a).

Escriba la descripcin HDL del circuito de la figura 3-37 empleando dos expresiones booleanas.

Escriba la descripcin HDL del circuito especificado por estas funciones booleanas:

x = A(CD + B) + BC'

)' = (AS' + A'B)(C + D')

z = [(A + B)(C' + D'B)]'

3-33

3-34

~

Utilice enunciados de asignacin continua.

3- 35 Encuentre los errores de sintaxis en las declaraciones siguientes (tome nota de que los nombres

de las compuenas primitivas son

module Exmpl-3(A,B,C,D,F)

inputs A,a,C,

Output D,F;

and gl(A,B,D);

not (D,B,A);

OR (F, B, C) ;

endmodule;

3-36 Dibuje el diagrama lgico del circuito digital especificado por esta descri~in HDL:

module circt (A,B,C,D,F);

input A,B,C,D;

output F;

wire w,x,y,z,a,d;

aDd (x,B,C,d);

an4 (y,a,C);

an4 (w,z,B);

or (z,y,A);

or (F,x,w);

not (a,A);

not (d,D);

eft~--~.lle

3-37 Una funcin lgica de mayora es una funcin booleana que da l si la mayora de las variables

vale 1, y O en caso contrario. Escriba una primitiva definida por el

ci6n de mayora de tres bits.

REFERENCIAS

1. BHASKER, J. 1997. A Vernog HDL Pri~r. Allentown, FA: Star Galaxy Press.

2. HIlL. F. J. y G. R. PETERSON. 1981.1ntroduction to Switching TheoryandLogicalDesign. 3a. ed.

Nueva York: John Wiley.

109 Referencias

opcionales) :

en HDL para una fun- usuano

8 of 41

Problema: Derivar la expresin de suma de productos ms simple para la funcin

f = X2X3X4 + XIX3X4 + XIX2X4

Solucin: La aplicacin de la propiedad de consenso 17a a los primeros dos trminos produce

f = X2X3X4 + XIX3X4 + X2X4XIX4 + XtX2X4

= X2X3X4 + XIX3X4 + XIX2X4 + XtX2X4

Ahora, al aplicar la propiedad de combinacin 14a en los ltimos dos trminos se obtiene

f = X2X3X4 + XIX3X4 + XIx.

Finalmente, con la propiedad de absorcin 13a se llega a

f = X2X3X4 + XIX4

Problema: Derivar la expresin de producto de sumas ms simple para la funcin

f = (XI + X2 + X3)(X1 + X2 + X4)(i1 + X3 + X4)

Solucin: La aplicacin de la propiedad de consenso 17b a los dos primeros tnninos conduce a

f = (il + X2 + X3)(i1 + X2 + X.)(il + X3 + XI + X.)(XI + X3 + X4)

= (XI + X2 + X3)(XI + X2 + X.)(il + X3 + X4)(X1 + X3 + X4)

Ahora, al aplicar la propiedad de combinacin 14b a los dos ltimos tnninos se obtiene

f = (XI + X2 + X3)(X1 + X2 + X4)(X1 + X3)

Finalmente, al aplicar la propiedad de absorcin 13b al primero y al ltimo tnnino resulta

f = (XI + X2 + X4)(X1 + X3)

PROBLEMAS

Al final del libro se encuentran las respuestas a lo~ problemas n18fCaOOs con lDl asterisco.

2.1 Use manipulacin algebraica para comprobar que x + yz = (x + y) . (x + z).

Observe que sta es la propiedad distributiva, como afinna la identidad 1lb de

la seccin 2.5.

2.2 Use manipulacin algebraica para comprobar que (x + y) . (x + y) = x.

2.3 Use manipulacin algebraica para comprobar que xy + yz + xz = xy + .iz.

Observe que sta es la propiedad de consenso 17a de la seccin 2.5.

2.4 Use diagramas de Venn para comprobar la identidad del problema l.

67

Eiemplo 2.12

Eiemplo 2.13

9 of 41

,

CAPiTULO 2 . JNTRODUCCIN A LOS CIRCUITOS LGIC~

68

2.5 Use diagramas de Venn para comprobar el teorema de DeMorgan, segn se da

en las expresiones 15a y 15b de la seccin 2.5.

2.6

*2.7

2.8

2.9

2.10

2.11 Use manipulacin algebraica para demostrar que para las tres variables de

entrada XI' X2 y x)'

nM(O, 1,2,3,4,5,6) = XtX2X3

.2.12 Use manipulacin algebraica para hallar la mnima expresin en suma de pro-

ductos para la funcin/= x.x) + X.X2 + x.xzX) + x.xxi)"

2.13 Use manipulacin algebraica para encontrar la mnima expresin en suma de

productos para la funcin/= XIX;) + X,XzX4 + XIXzX;X4"

2.14 Use manipulacin algebraica para hallar la mnima expresin de producto de

sumas para la funcin/= (XI + x) + xJ. (XI + X2 + x) . (XI + X2 + x) + X4).

.2.1 5 U se manipulacin algebraica para encontrar la mnima expresin de producto

de sumas para la funcin/= (x. + X2 + x) . (XI + X2 + x)) . (XI + X2 + x) "

(XI + X2 + x)"

2.16 a) Muestre la ubicacin de todos los mintrminos en un diagrama de Venn de

2.17

2.18

2.19

Use un diagrama de Venn para comprobar que

(XI + X2 + X3) . (XI + X2 + X3) = XI + X2

Determine si las expresiones siguientes son vlidas, es decir, si los miembros

izquierdo y derecho representan la misma funcin.

a) XIX3 + XIX2X3 + XJX2 + XJX2 = X2X3 + XJX3 + X2X3 + XJX2X3

b) XIX3 + X2X3 + X2X3 = (XI + X2 + X3)(XI + X2 + X3)(i1 + X2 + X3)

c) (XI + X3)(i1 + X2 + X3)(i1 + X2) = (XI + X2)(X2 + X3)(i1 + X3)

Trace un diagrama de tiempo para el circuito de la figura 2.19a. Muestre las

formas de onda que pueden observarse en todos los cables del circuito.

Repita el problema 2.8 para el circuito de la figura 2.19b.

Use manipulacin algebraica para demostrar que para las tres variables de

entrada

X" X2 y X"

m{1,2,3,4,S,6,7} ='x1 +X1+X3

tres

b) Muestre un diagrama de Venn separado por cada tnnino producto en la

funcinf= XIXzX3 + XIX2 + XIX). Use diagramas de Venn para hallar la mnima

forma de suma de producto de.f

Represente la funcin de la figura 2.18 en la forma de diagrama de Venn y

determine su mnima forma de suma de productos.

En la figura P2.1 se muestran dos intentos para trazar un diagrama de Venn

para cuatro variables. Para los incisos a) y b) de la figura, explique por qu el

diagrama no es correcto. (Sugerencia: El diagrama de Venn debe ser capaz de

representar los 16 mintrminos de las cuatro variables.)

En la figura P2.2 se observa la representacin de un diagrama de Venn de cua-

tro variables, as como la ubicacin de los mintrminos mo' mi y mr Muestre

la ubicacin de los otros mintrminos en el diagrama. Represente la funcin

f = x,xzX;X. + x,Xif'X. + XIX, en este diagrama.

de Venn separado por cada

diagrama

f= X.XzXY%4

10 of 41

a)

Dos intentos pora trazar un diagrama de Venn de cuatro variables. Figura P2.1

Figura P2.2 Diagrama de Venn de cuatro variables.

*2.20 Disee el circuito ms simple de suma de productos que implemente la fun-

cinf(xI' X2' X3) = m(3, 4, 6, 7).

2.21 Disee el circuito ms simple de suma de productos que implemente la fun-

cinf(xI' X2' xJ = m(l, 3, 4~ 6~ 7).

2.22 Disee el circuito ms simple de producto de

cinf(xl' X2' X3) = nM(O, 2, S).

.2.23 Disee el circuito ms simple de producto de

~.~.J ulsene el ClrcUI10 mas sImple De prODUCtO De sumas que Implemente la IuD-

cinf(x" X2' X3) = nM(O, 1,5,7),

2.24 Derive la expresin ms simple de suma de productos para la funcinf(x" X2'

x3' x.) = xlxi. + xi~. + X.Xi3'

2.25 Derive la expresin ms simple de suma de productos para la funcinf(x"

X2' X3' x.' xs) = x.x;is + x,x.;x. + x\x;CS + x\i;X~S' (Sugerencia: Aplique la

_~_~aA..A Aa ..,.-~-~,. ,., ~\

X2' X3' X4' XJ = XtX;is + i,i;i4

propiedad de consenso 170).

2.26 Derive la expresin ms simple de producto de sumas para la funcin!(x., X2'

X3' x.) = (x. + X3 + XJ<X2 + X3 + xJ<x. + X2 + X3). (Sugerencia: Aplique la

propiedad de consenso 17b.)

69

b)

sumas que implernente la fun-

sumas

+

XX"xs

+

11 of 41

f

-cAPiTULO 2 70

2.27 Derive la expresin ms simple de producto de sumas para la funcinf(.tl' X2'

X3' x4' xs) = (X2 + x3 + xs)(x, + x3 + XS)(XI + X2 + xs)(x, + x4 + xs). (Sugeren-

cia: Aplique la propiedad de consenso 17b.)

2.28 Disee el circuito ms simple que tenga tres entradas, XI' X2 y X3' que produzca

un valor de salida de 1 siempre que dos o ms de las variables de entrada tenga

el valor 1; de otro modo, la salida debe ser o.

2.29 Disee el circuito ms simple que tenga tres entradas, XI' X2 y X3' que produzca

un valor de salida de 1 siempre que exactamente una o dos de las variables de

entrada tenga el valor de 1; de otro modo, la salida ha de ser O.

2.30 Disee el circuito ms simple que tenga cuatro entradas, x" X2' X3 y X4' que

produzca un valor de salida de 1 siempre que tres o ms de las variables de

entrada tengan el valor de 1; de otro modo, la salida debe ser O.

2.31 Para el diagrama de tiempo de la figura P2.3, sintetice la funcinf{x" X2' X3)

en la forma ms simple de suma de productos.

*2.28

2.29

2.30

I 1 ,11 O

1

O

1

O

1

O

I I I

[.."--I I.."--1 r-..1 -"-lr---l JL -

Figura P2.3 Diagrama de tiempo que

.2.32 Para el diagrama de tiempo de la figura P2.3, sintetice la funcinf(x" X2' xJ

en la forma ms simple de producto de sumas.

.2.33 Para el diagrama de tiempo de la figura P2.4, sintetice la funcinf(x., :X2,:xJ

en la forma ms simple de suma de productos.

2.34 Para el diagrama de tiempo de la figura P2.4, sintetice la funcin!(x" X2' X3)

en la forma ms simple de producto de sumas.

2.35 Disee un circuito con salida f y entradas

. INTRODucCl~ A. 1m CIRCUITOS LGI~

TIempo

una funci6n lgica.

represento

ulsene un CircUitO con saJloa] y entraoas XI' Xo' y. y YO' ~ A. = XI' Xo un nu-

mero, donde los cuatro valores posibles de X (00, 01, 10 Y 11) representan los

cuatro nmeros O, 1, 2 y 3, respectivamente. (La representacin de nmeros se

explicar en el captulo 5.) De manera similar, sea Y = y'yn la representacin

ulsene un ClTCWtO con

mero, donde los cuatro

cuatro nmeros O. 1. 2 ,

los

representan

de otro nmero con los mismos cuatro posibles valores. La salida f debe ser 1 !

los nmeros representados porXy Y son iguales. De otro modo,/debe ser O.

a) Elabore la tabla de verdad para f

b) Sintetice la expresin ms simple posible de Droducto de ~uma~ rutnt (

mismos

posibles

cuatro

12 of 41

I

o

1

O

1

O

1

O

Xl

x2

x3

f

1 1 1

J.'-."l___r l J '-"l._.

~ 1[---

Figura P2.4 Diagrama de tiempo que

2.36 Repita el problema 2.35 para el caso en que f debe ser 1 slo si X ~ Y.

a) Elabore la tabla de verdad paraf.

b) Muestre la expresin de suma cannica de productos paraf.

c) Muestre la expresin ms simple posible de suma de productos paraf.

2.37 Implemente la funcin de la figura 2.26 usando slo compuertas NAND.

2.38 Implemente la funcin de la figura 2.26 usando solamente compuertas NOR.

2.39 Implemente el circuito de la figura 2.35 usando nada ms compuertas NAND

y NOR.

.2.40 Disee el circuito ms simple que implemente la funcinf(x, , X2' X3) = Em(3,

4, 6, 7) usando compuertas NAND.

2.41 Disee el circuito ms simple que implemente la funcin f(x l' x,2' X3) = Em( 1,

3, 4, 6, 7) usando compuertas NAND.

.2.42 Repita el problema 2.40 usando ahora compuertas NOR.

2.43 Repita el problema 2.41 usando ahora compuertas NOR.

2.44 a) Use una herramienta de captura esquemtica para trazar los esquemas de

las funciones siguientes"

ft = X2XJX. + X.X2X4 + XIX2X3 + XtX2X3

/2 = X2X4 + XtX2 + X2X3

b) Use simulacin funcional para comprobar que.l; = h.

2.45 a) Use una herramienta de captura esquemtica para trazar los esquemas de

las funciones siguientes

ft = (XI +X2 +X4)' (X2 +X3 +x.). (Xl +X3 +x.). (XI +X3 +X.)

h = (X2 + X4) . (X3 + X4) . (Xl + x.)

b) Use simulacin funcional para comprobar que.l; = h.

2.46 Escriba cdigo de VHDL para implementar la funcinf(xI' x,2' x,3) = Em(O,

1,3,4,5,6).

71

Tiempo

una funcin lgica,

representa

13 of 41

CAPTULO 2 . INTRODUCCiN A LOS ClRCUIT~ LGIC~

2.47 a) Escriba cdigo de VHDL para describir las funciones siguientes

11 = XIX3 + X2X3 + X3X4 + XIX2 + XIX4

h = (XI +X3). (Xl +X2 +X4). (X2 +X3 +X4)

b) Use simulacin funcional para comprobar que.l; = h.

2.48 Considere las instrucciones siguientes de asignacin en VHDL

72

fl <= xl AND x3) OR (NOT xl AND NOT x3 OR x2 AND x4) OR

(NOTx2ANDNOTx4 ;

f2 <= (xl AND x2 AND NOT x3 AND NOT x4) OR (NOT xl AND NOT x2 AND x3 AND x4)

OR (xl AND NOT x2 AND NOT x3 AND x4) OR

(NOT xl AND x2 ANO x3 ANO NOT x4) ;

BIBLIOGRAFtA

G. Boole, An fnvestigation 01 the Laws olThought, 1854, reimpreso por Dover Publicatio-

ns, Nueva York, 1954.

C. E. Shannon, "A Syrnbolic Analysis of Relay and Switching Circuits", Transactions 01

AfEE 57 (1938), pp. 713-723.

E. V Huntington, "Sets of Independent Postulates for the AIgebra of Logic", Transactions

01 the American Mathematical Society 5 (1904), pp. 288-309.

S. Brown y Z. Vranesic, Fundamentals 01 Digital Logic with Verilog Design (McGraw-

Hill: Nueva York, 2003).

Z. Navabi, VHDL-Analysis and Modeling olDigital Systems, 2a. ed. (McGraw-Hill: Nue-

va York, 1998).

D. L. Perry, VHDL, 3a. ed. (McGraw-Hill: Nueva York, 1998).

J. Bhasker, A VHDL Primer, 3a. ed. (Prentice-Hall: Englewood Cliffs, NJ, 1998).

K. Skahill, VHDLlorProgrammable Logic (Addison-Wesley: Menlo Park, CA, 1996).

A. Dewey, Analysis and Design 01 Digital Systems with VHDL (PWS Publishing Co.: Bos-

ton, 1997).

D. J. Smith, HDL Chip Design (Doone Publications: Madison, AL, 1996).

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

.

a) Escriba cdigo de VHDL completo para implementar f1 y fl.

b) Use simulacin funcional para comprobar que /1 = /2.

14 of 41

304 Capftulo 4 Principios de diseo lgico combinacional

Ejercicios

4.28

4.29

4.30

4.31

4.32

4.33

4.34

4.35

4.36

4.37

4.38

teorema.\' genera/izados de 4.41

expansin de Shannon

4.42

compuerta OR Exclus;va 4.43

(XOR)

4.44

Disee un circuito lgico de aspecto no trivial con un ciclo de retroalimentac

tenga una salida que dependa solamente de su entrada actual.

Demuestre el teorema de combinacin TI O sin utilizar induccin perfecta. pe

do que los teoremas T 1- 1'9 Y TI' - 1'9' son verdaderos.

Muestre que el teorema de combinacin TIO es de hecho un caso especial (

(TII) usado con cobertura ('1'9).

Demuestre que (X + Y') . Y = X . Y sin emplear induccin perfecta. Se puede

los teorema.~ T 1- T 1I Y TI' - T 11' son verdaderos.

Demuestre que (X + Y) . (X' + Z) = X . Z + X'. Y-. sin hacer uso de la inducci

Se puede suponer que los teoremas TI- TII Y TI'- TII' son verdaderos.

Muestre que una compuerta ANO de n entradas puede reemplazarse por (n - I j

ANO de 2 entradas. Puede hacerse la misma instruccin para compuerta.~ No

fique su respuesta.

Cuntas manera.~ fsicamente diferentes existen para realizar. V . W - X . Y . ~

tro compuertas ANO de 2 entradas (4/4 de un 74x08)? Justifique su respuest

Utilice el lgebra de conmutacin para demostrar que al unir dos entrada... en

una compuerta AND u OR de (n + 1) entradas proporciona la funcionalidad '

puerta de n entradas .

Demuestre los teoremas de DeMorgan (T13 y TI3') usando la induccin finit

Cul smbolo lgico se aproxima con mayor exactitud a la realizacin in!

compuerta NOR TTL.la figurd 4-4(c) o (d)? Por qu?

Utilice los teoremas del lgebra de conmutacin para volver a escribir t

siguiente utilizando tan pocas inversiones como sea posible (se permitel

complementados ):

B' . C + A - C . D' + A' . C + E . B' + E . (A + C) . (A' + 0')

Demuestre o rechace las instrucciones siguientes:

(a) Sean A y B variables del lgebra de conmuta

implica que A = B'.

(b) Sean X y Y expresiones del lgebra de conmutacin. Entonces X . Y = O

implica que X = Y'.

Demuestre los teoremas de expansin de Shannon. (Sugerrnc;a: No se vay

es fcil.)

Los teoremas de expansin de Shannon pueden generalizarse para "extraer. n

una sino; variables de modo que una funcin lgica pueda ser expresad

suma o producto de i trminos. Establezca los teoremas de expansin ge

de Shannon.

Demuestre cmo los teoremas de expansin generalizados de Shannon condu

presentaciones de suma cannica y producto cannico de funciones lgicas.

Una compuerta OR Exclusiva ( XOR) es una compuerta de 2 entradas cuya!

y slo si exactamente una de sus entradas es l. ~riba una tabla de verdad.

suma de productos y el correspondiente circuito ANO-OA para la funcin OF

Desde el punto de vista del lgebra de conmutacin, cul es la funcin de un

XOA de 2 entradas cuyas entradas se encuentran unidas? Cmo puede diferi

tamiento de salida de una compuerta XOA real?

15 of 41

Despus de completar el diseo y fabricacin de un sistema digital basado en SSI. un

diseador encuentra que se requiere de un inversor ms. Sin embargo. las nicas com-

puertas de sobra en el sistema son una OA de 3 entradas, una ANO de 2 entradas y una

XOA de 2 entradas. Cmo debera realizar el diseador la funcin del inversor sin

agregar otro CI?

Cualquier conjunto de tipos de compuerta lgica que puede realizar cualquier funcin

lgica se conoce como un conjunto completo de compuertas lgicas. Por ejemplo, com-

puertas ANO de 2 entradas. compuertas OR de 2 entradas e inversores son un conjunto

completo. porque cualquier funcin lgica puede expresarse como un producto de sumas

d~ variables y sus complementos, y las compuertas ANO y OR con cualquier nmero de

entradas pueden hacerse a partir de compuertas de 2 entradas. Las compuertas NANO

de 2 entradas fonnan un conjunto completo de compuertas lgicas? Demuestre su res-

puesta.

Las compuertas NOA de 2 entrada.~ forman un conjunto completo de compuertas lgi-

cas? Demuestre su respuesta.

Las compuenas XOA de 2 entradas forman un conjunto completo de compuertas lgicas?

Demuestre su respuesta.

Defina una compuerta de dos entradas. aparte de NANO. NOA o XOA. que forme un

conjunto completo de compuertas lgicas si se permiten las entradas constantes O y l.

Demuestre su respuesta.

Algunas personas piensan que existen cuatro funciones lgicas bsicas. ANO. DR. NOT

y SUr: La figura X4.50 es un smbolo posible para una compuerta BUT de 4 entradas y 2

salidas. Invente una funcin til y no trivial para que la compuerta BUT la realice. La fun-

cin tendra algo que ver con el nombre (BUT. "pero"). Tenga en cuenta que. debido a la

simetra de] smbolo, la funcin debera ser simtrica con respecto a las entradas A y B de

cada seccin y con respecto a las secciones I y 2. Detalle su funcin de BUT y escriba su

tabla de verdad.

Escriba expresiones lgicas para las salidas Z I y Z2 de la compuerta BUT que usted dise

en el ejercicio anterior. y dibuje un diagrama lgico correspondiente utilizando compuer-

tas ANO. compuertas OA e inversores.

La mayora de los estudiantes no tienen problema al emplear el teorema T8 para "expandir"

la multiplicacin en expresiones lgicas. pero muchos desarrollan un bloqueo mental si

intentan utilizar el teorema T8' para "expandir" la suma de una expresin lgica. Cmo

puede usarse la dualidad para superar este problema?

Cuntas funciones lgicas diferentes de n variables existen?

Cuntas funciones lgicas diferentes de 2 variables F(X. V) existen? Escriba una expresin

algebraica simplificada para cada una de ellas.

Una funcin lgica autodual es una funcin F tal que F = FD. Cules de las siguientes

funciones son autoduales? (El smbolo e denota la operacin OA Exclusiva (XOA).)

(a) F=X (b) F=I.x.y.z<0.3.5.6)

(c) F=X.V'+X'.V (d) F=W.(XeVeZ)+w'.(XeVEBZ)'

(e) Una funcin F de 7 variables tal (f) Una funcin F de lO variables tal que

que F = 1 si y slo si 4 o ms de F = 1 si y slo si 5 o ms de las

las variables son I variables son 1

4.46

4.47

4.48

4.49

..50

4.51

4.52

4.53

4.54

4.55

,

4.56

Cuntas funciones lgicas autoduales de n variables de entrada existen? (Sugerencia:

Considere la estructura de la tabla de verdad de una funcin autodual.)

~

Ejercicios 305

conjunto completo

BUT

compuerta sur

A1

~ Z1 81

A2 Z2

B2

Figura X4.50

(uncin lgica autodua/

$

16 of 41

306 Captulo 4 Principios de diseo lgico combinacional

4.57 Demuestre que cualquier funcin lgica de n entradas F(X),...,Xn) que pueda I

en la forma F=X,oG(X2,...,Xn)+X1'oGD(Xc...,Xn)esautodual.

4.58 Suponiendo que una compuerta de inversin tiene retardo de propagacin de 5 ns,

compuerta no inversora tiene un retardo de propagacin de 8 ns, compare las ve

de los circuitos en la figura 4-24 (a), (c) y (d).

4.59 Encuentre las expresiones de producto de sumas mnimo para las funciones lgi,

figuras 4-27 y 4-29.

4.60 Utilice el lgebra de conmutacin para demostrar que las funciones lgicas I

en el ejercicio 4.59 son iguales a las funciones ANO-DA obtenidas en las figl

y 4-29.

4.62 Demuestre que la regla para combinar i celdas 1 en un mapa de Karnaugh es ,

suma no redundante 4.63 Una suma no redundante para una funcin lgica F es una suma de implicantes p

F de tal modo que si cualquier implicante primo se elimina. la suma ya no es

Esto suena bastante parecido a una suma mnima. pero una suma no redundante n.

sariamente mnima. Por ejemplo. la suma mnima de la funcin en la figura 4-35

4.64

4.65

4.66

4.67

4.68

mas en la figura 4-27 y la 4-29 son mnimas.

lgebra

de conmutacin. utilizando los axiomas y teoremas del

tres trminos de producto, pero hay una suma no redundante con cuatro trmin(

ducto. Encuentre la suma no redundante y diooje un mapa de la funcin, encel

crculos solamente los implicantes primos en la suma no redundante.

Encuentre otra funcin lgica en la seccin 4.3 que tenga una o ms sumas no rec

no mnimas, y dibuje su mapa, encerrando en crculos nicamente los implicantl

en la suma no redundante.

Dibuje un mapa de Kamaugh y asigne variables a las entradas del circuito ANO

la figura X4.65 de modo que su salida sea F = 1:w.x. v,z<6, 7, 12, I 3). Advierta qu

puerta de salida es una XOR de 2 entradas en lugar de una ORo

F

Figura X4.65

Un circuito "comparador" de 3 bits recibe dos nmeros de 3 bits, P = P 2P 1 Po Y O =

Disee un circuito de suma de productos mnimo que produzca una salida l s

P>O.

Erx:oontre exp'eS~ ~ xOOucto ~ sumas ~ salida mltiple mnimas ~ F = Ix

G = Ix.v.z<I,4,6), y H = Ix,v.z<, l ,2,4,6),

Demuestre si la expresin siguiente es una suma mnima o no lo es. Haga esto de

ms sencilla posible (algebraicamente, sin usar mapas).

F = T'.U.V.W.X+T'.U.V'.X.Z+T'.U.W.X.Y'.z

17 of 41

W

r I

wx

v z '" 00 01 r-;~~

00 o . 12 8

01 1 5 13 9

f [ 11 3 7 15 11

10 2 6 ,. 10

]z

v[

v=O

9 El texto establece que una tabla de verdad o equivalente es el punto de partida para los

mtodos de minimizacin combinacionales tradicionales. Un mapa de Karnaugh contiene

por s mismo la misma infonnacin que una tabla de verdad. Dada una expresin de suma

de productos, es posible escribir los unos correspondientes a cada tnnino de producto

directamente en el mapa sin desarrollar una tabla de verdad explcita o lista de minitr-

minos, y luego proceder con el procedimiento de minimizacin de mapa. De esta fonDa,

encuentre una expresin de producto de sumas mnimas para cada una de las siguientes

funciones lgicas:

F=X'.Z+X.V+X.V'.Z (b) F=A'.C'.D+B'.C.D+A.C'.D+B.C.D

F = W . x . Z' + W . X' . V . Z + X . Z (d) F = (X' + V') . (W' + X' + V) . (W. X . Z)

F=A. B. C'. D'. A'. B. C'.A. B. D.A'. C. D+ B. C. D'

(a)

(c)

(e)

Repita el ejercicio 4.69. encontrando una expresin de producto de sumas mnima para

cada funcin lgica.

Derive la expresin de producto de sumas mnima para la funcin del detector de nmeros

BCD primos de la figura 4-37. Determine si la expresin es o no algebraicamente igual a

la expresin de producto de sumas mnima y explique su respuesta.

Un mapa de Karnaugh para una funcin de 5 variables puede dibujarse como se muestra

en la figura X4.72. En un mapa as. las celdas que ocupan la misma posicin relativa en

los submapas V = O y V = l se consideran adyacentes. (Muchos ejemplos trabajados de

mapas de Karnaugh de 5 variables aparecen en las secciones 7.4.4 Y 7.4.5). Encuentre una

expresin de producto de sumas mnima para cada una de las siguientes funciones utili-

zando un mapa de 5 variables:

F = Iv.w.x.v,z(5, 7,13,15,16,20,25,27,29,31)

F = Iv.w.x. v.z{O, 7,8,9,12,13,15,16,22,23,30.31)

(a)

(b)

(c)

(d)

(e)

(1)

F = Iv,w,x. y.z<0.1.2.3.4.5, 10.11.14.20.21.24.25.26.27.28.29.30)

F = Iv,w,x. y.z<0.2,4,6, 7.8.10,11.12,13.14,16,18,19.29,30)

F = nv,w.x,y.z<4,5.10, 12, 13, 16.17.21.25,26.27,29)

F = tv,W.x.y.z<4.6. 7.9,11.12,13.14.15.20.22,25.27.28.30) + d(l. 5.29.31)

Ejercicios

307

wx w

y z" 00 01 ,.~~--~

00 18 20 a 24

01 11 21 28 25

Y [ 11 11 2S 31 27

10 11 a ~ .

Figura X4.72

]z

V=1

mapa di' Karnaugh

de 5 variables

18 of 41

308 Captulo 4 Principios de diseo lgico combinacional

wx "

Figura X4.74 y Z" 00 01 11 10

oo~. 44 40

01 33 37 45 41

Y [ 11 35 . 47 48

10 34 . 46 41-

. .

U,V-1.0 X

~. 73 Repita el ejercicio 4.72, hallando una expresin de producto de sumas mnima p

funcin lgica.

~. 74 Un mapa de Kamaugh para una funcin de 6 variables puede dibujarse como sc

en la figura X4.74. En un mapa as, las celdas que ocupan la misma posicin rel

submapas adyacentes se consideran como adyacentes. Minimice las funciones si

con la ayuda de los mapas de 6 variables:

(a) F = Iu.v.w.x.v,z(I,5,9, 13,21,23,29,31,37,4S,S3,61)

(b) F = Iu.v.w.x.v,z(0,4,8, 16,24,32,34,36,37,39,40,48,50,56)

(c) F = Iu.v.w.x.v,z(2,4.5,6, 12-21.28-31.34.38,50.51.60-63)

~. 75 Existen 2n subcubos m de un cubo n para el valor m = n-l. Muestre sus represenl

de texto y los correspondientes trminos de producto. (Se pueden emplear elipse!; a

que se requieran, por ejemplo. 1.2. ..., n.)

~. 76 Hay slo un subcubo m de un cubo n para el valor m = n; su representacin de

xx...XX. Escriba el trmino de producto corl'espondiente a este cubo.

..77 El programa en C de la tabla 4-9 utiliza la memoria de manera ineficiente porque a

memoria para un nmero mximo de cubos en cada nivel, incluso si nunca se hact

este mximo. Vuelva a disear el programa de manera que los arreglos cubes y us

arreglos de una dimensin. y cada nivel utilice solamente tantas entradas de arregl

sean necesarias. (Sugerencia: se pueden 3signar todava cubos de manera secuenci

mantngase al tanto del punto de partida en el arreglo para cada nivel.)

mapa de Karnaugh

de 6 variables

4.75

4.76

4.77

]z

v[ v[

~J

X

u. v = 0,1

w

, ,

YZ

]z

v[ v[

u, v = 1,0 u. v = 1,1

19 of 41

Como una funcin de m, cuntas veces se redescubre un cubo m diferente en la tabla

4-9, pero el cubo se encuentra en el ciclo interno y se descarta? Sugiera algunas maneras

para eliminar esta deficiencia.

El tercer ciclo for en la tabla 4-9 intenta combinar todos los cubos m a un nivel dado con

todos los otros cubos m en ese nivel. De hecho, solamente se pueden combinar los cubos

m con las x's en las mismas posiciones, de modo que es posible reducir el nmero de itera-

ciones del ciclo mediante el uso de una estructura de datos ms sofisticada. Disee una

estrUctura de datos que segregue los cubos para un nivel dado de acuerdo a la posicin de

sus x 's, y determine el tamao mximo requerido para diversos elementos de la estructura

de datos. Vuelva a escribir la tabla 4-9 de acuerdo a esto.

Haga una estimacin de si los ahorros en la.~ iteraciones del ciclo interno conseguidas en

el ejercicio 4.80 superan el gasto general de mantener una estructura de datos ms com-

pleja. Intente hacer suposiciones razonables acerca de cuntos cubos se distribuyen en

cada nivel, e indique cmo sus resultados son afectados por estas suposiciones.

Optimice la funcin Oneone en la tabla 4-8. Una optimizacin obvia es abandonar el ciclo

pronto, pero existen otras optimizaciones que eliminan completamente el ciclo foro Una

est basada en consulta de tablas y otra utiliza un clculo delicado que involucra comple-

mentacin, aplicacin de OR Exclusivo y adicin.

Extienda el programa C en la tabla 4-9 para manipular condiciones "sin importancia". Pro-

porcione otra estructura de datos, dc[MAX_VARS+l] [MAX_CUBES] , que indiquen si un

cubo dado contiene solamente elementos "sin importancia", y actualcela a medida que

los cubos se leen y generan.

(Circuito Hamlet.) Complete el diagrama de temporizacin y explique la funcin del cir-

cuito en la figura X4.83. De dnde obtiene ~u nombre el circuito?

4.81

~~

Demuestre que un circuito AND-OR de dos niveles correspondiente a la suma completa

de una funcin lgica siempre est libre de riesgos.

Encuentre una funcin lgica de cuatro variables cuya realizacin de suma de productos

mnima no esl libre de riesgos, pero para la cual exista una realizacin de ~uma de pro-

ductos libre de riesgos con menores tnninos de producto que la suma completa.

Comenzando con las instrucciones WHEN en el programa ABEL de la tabla 4-14, elabore

las ecuaciones lgicas para las variables X4 a Xl O en el programa. Explique cualquier dis-

crepancia entre sus resultados y las ecuaciones en la tabla 4-15.

Dibuje un diagrama de circuito correspondiente a las ecuaciones de suma de productos de

dos niveles mnima para el circuito de alanna, como se dan en la tabla 4-12. En cada entra-

da y salida de inversor, compuerta AND y compuerta ORo escriba un par de nmeros (tO,

tI), donde tO es el nmero de prueba de la tabla 4-25 que detecta un bloqueo en falla O en

esa lnea. y ti es el nmero de prueba que detecta un bloqueo en falla l.

4.87

Ejercicios 309

28

Figura X4.83

F

20 of 41

310 Capitulo 4 Principios de diseo lgico combinacional

4.88 Escriba un programa VHDL en estilo de flujo de datos (entidad y arquitectura)

diente al circuito sumador completo en la figura 5-86.

4.89 Utilizando la entidad que usted dise en el ejercicio 4.88, escriba un progra

estructural para un sumador cclico de 4 bits empleando la estructura de la figu

4.90 Empleando la entidad que usted defini en el ejercicio 4.88. escriba un progra

estructural para un sumador cclico de 16 bits a lo largo de las lneas de la ti

Utilice una instruccin genera te para crear los 16 sumadores completos y su

nes de seal.

4.91 Vuelva a escribir la arquitectura del detector de nmeros primos de la tabla 4-63

una instruccin while.

4.88

4.89

4.90

21 of 41

98

(~apl 1110

-1 1 I .

-1_J--LJL Ji .

LJL

RESUMEN

El lgebra booleana es una hen-amienta matemtica que se usa en el anlisis y

diseo de circuitos digitales.

Las operaciones booleanas bsicas son las operaciones OR, AND y NOT.

Una compuerta OR produce una salida ALTA cuando cualquier entrada es AL-

TA. Una compuerta AND produce una salida ALTA slo cuando todas las entra-

das son ALTAS. Un circuito NOT (INVERSOR) produce una salida que es el ni-

vellgico opuesto que la entrada.

Una compuerta NOR es la misma que una OR con su salida conectada a un IN-

VERSOR. Una compuerta NAND es la misma que una compuerta AND con su

salida conectada a un INVERSOR.

Los teoremas y reglas booleanas se pueden usar para simplificar la operacin

de un circuito lgico y pueden conducir a una forma ms sencilla de imple-

mentar el circuito.

Las compuertas NAND se pueden usar para implementar cualquiera de las ope-

rciciones booleanas bsicas. Las compuertas NOR se pueden usar de igual for-

ma.

Los smbolos estndar o los altemos se pueden usar para cada compuerta lgi-

ca, dependiendo de si la salida ser activa en ALTO o activa en BAJO.

En la norma IEEE/ ANSI para smbolos lgicos se usan smbolos rectangulares

para cada dispositivo lgico, con notaciones especiales dentro de los rectngu-

los, para mostrar cmo dependen las salidas de las entradas.

l.

2.

3.

4.

5.

6:

,.

8.

,

TERMINOS CLAVE*

--- ,

activo en ALTO compuerta NOR operacin NOT

activo en BAJO compuerta OR operacin OR

lgebra booleana inversin-complememacin smbolos IEEE! ANSI

asegurado o declarado nivel lgico smbolos lgicos alIemos

circuito NOT (INVERSOR) niveles lgicos activos tabla de verdad

compuerta ANO no asegurado o no declarado teoremas booleanos

compuena NAND operacin ANO teoremas de OeMorgan

PROBLEMAS

Las letras en negritas que preceden a algunos de los problemas se usan paf2 indi-

car su naturaleza. o de qu tipo son:

8

T

D

N

problema bsico C problema difci:

problema de deteccin de fallas

problema de diseo o modificacin del circuito

concepto o tcnica nueva no analizada en el texto

Estos trminos se destacan con negritas en el captulo y se definen en el Glosario al final dellihro.

lgebra

3 / Compuertas lgicas y

booleana 22 of 41

Itrobl"lna~

SECCiN 3-3

B ~1. Dibuje la forma de onda de salida para la compuerta OR de la figura 3-42.

FIGURA 3-42

Suponga que la entrada A de la figura 3-42 se cortocircuita involuntariamen-

te a tierra (es decir, A = O). Dibuje la forma de onda resultante.

Suponga que la entrada A de la figura 3-42 se cortocircuita involuntariamen-

te a la lnea de alimentacin de + S V (es decir, A = 1). Dibuje la forma de

onda resultante.

Lea los siguientes enunciados respecto a una compuerta ORo A primera vista

parecen vlidos, pero despus de algn razonamiento se dar cuenta que

ninguno es siempre vlido. Demuestre esto dando un ejemplo especfico pa-

ra refutar cada enunciado.

(a) Si la forma de onda de salida de una compuerta OR es la misma que la

forma de onda en una de sus entradas, la otra entrada se mantiene per-

manentemente en BAJA.

(b) Si la forma de onda de salida de una compuerta OR es siempre ALTA,

una de sus entradas se mantiene permanentemente en ALTA.

Cuntos conjuntos de condiciones de entrada producir una salida en ALTA

de una compuerta OR de cinco entradas?

~

3-4.

~

3-5.

SECCiN 3-4

B 3-6. Cambie la compuerta OR de la figura 3-42 a una compuerta ANDo

(a) Dibuje la forma de onda de salida.

(b) Dibuje la forma de onda de salida si la entrada A se conocircuita perma-

nentemente a tierra.

(c) Dibuje la forma de onda de salida si A se cortocircuita permanentemente

a +5 V.

D 3-7. Refirase a la figura 3-40 Modifique el circuito de manera que la alarma slo

se active cuando la presin y la temperatura excedan sus lmites mximos al

mismo tiempo.

B 3-8. Cambie la compuerta OR de la figura 3-6 a una compuerta AND y dibuje la

forma de onda de salida.

3-9. Suponga que se tiene una compuerta desconocida de dos entradas que pue-

de ser una compuerta OR o una AND. Qu combinacin de niveles de en-

trada se debe aplicar a las entradas de la compuerta para determinar el tipo

de compuerta?

3-10. Cter1o ofalso: no importa cuntas ent~das tenga una compuerta AND, pro-

ducir una salida en ALTA para una sola combinacin de niveles de ent~da.

~~

SECCIONES 3-5 A 3-7

3-11. Aplique la forma de onda A de la figura 3-23 a la entrada de un INVERSOR.

Dibuje la forma de onda de salida. Repita para la forma de onda B.

99

-_.J-.-l.._f-l___r-.-l-

I I I

._fL_f1lrLJ~J-ullI"L

I I I

1 J 1_-

A

~~~~)- x

B

C

23 of 41

100

Captulo 3 / Compuertas

(a) Escriba la expresin booleana para la salida x de la figura 3-43(a). Deter-

mine el valor de x para todas las condiciones de entrada posibles y liste

los valores en una tabla de verdad.

(b) Repita la operacin para el circuito de la figura 3-43(b).

B 3-12.

FIGURA 3-43

A

B x

C

3-13. Determine la tabla de verdad completa para el circuito de la figura 3-15(b)

encontrando los niveles lgicos presentes en cada salida de compuerta para

cada una de las 32 combinaciones de entrada posibles.

3-14. Cambie cada compuerta OR a una ANO, y cada AND a una OR en la figura

3-15(b). Luego escriba la expresin para la salida.

3-15. Determine la tabla de verdad completa para el circuito de la figura 3-16 y

encuentre los niveles lgicos presentes en cada salida de las compuertas pa-

ra cada una de las 16 combinaciones posibles de niveles de entrada.

SECCiN 3-8

B 3-16. Para cada una de las siguientes expresiones, construya el circuito lgico co-

rrespondiente usando compuertas ANO y OR e INVERSORES.

(a) x = AB(C + D)

- - --

(b) z= (A + B+ CDE) + BCD

(c) y= (M+ N + PQ)

-

(d) x= W+ PQ

(e) z = MN(P + N)

(t) x = (A + B)(A + B)

y lgebra booleana

(a)

(b)

24 of 41

1~I'obl('ma...

SECCiN 3-9

3-17. (a) Aplique las formas de onda de entrada de la figura 3-44 a una compuer-

ta NOR y dibuje la forma de onda de salida.

(b) Repita con C mantenida permanentemente en BAJA.

(c) Repita con Cmantenida en ALTA.

B

FIGURA 3-44

8 3-18. Repita el problema 3-17 para una compuerta NAND.

C 3-19. Escriba la expresin para la salida de la figura 3-45 y ~la para detenninar la

tabla de verdad completa; luego aplique las formas de onda de la figura 3-44

a las entradas del drcuito, y dibuje la fonna de onda de salida resultante.

FIGURA 3-45 A

B

C

T'!i

;.'ii

(~~~ .

"

, ...,.:;. -

~ ~~T~

...,.",

,_.

~.

3-20. Determine la tabla de verdad para el circuito de la figura 3-24.

3-21. Modifique los circuitos que se trazaron en el problema 3-16, de manera que

las compuertas NANO y NOR se usen siempre que sea adecuado.

,;:fi:;::

.=,

';'."

..

;~

..;j;.;...

;..,;:;c

;.::~

SECCiN 3-10

3-22. PREGUNTAS DE EjERCIOO

Complete cada expresin

(a) A + 1 =

(b) A. A =

(c) B. B -

(d) C+ C-

(e) x. O =

B

3-23. Demuestre los teoremas 15a y 15b ensayando todos los casos posibles.

C 3-24. (a) Simplifique la siguiente expresin usando los teoremas (13b), (3) y (4):

(b) Simplifique la

101

I11 I m

--J! ! LJ I

A 11 I I I

B 111 :rt- ~

~ ! I ; I i j I

I I I 1 II 1 I

-11 . !r1t-'L__1 I I1I

I ., 1 I

C I II

(O D. 1 z

(g)D+O= I

(h) C + C =

(1) G+ GF= -

(j) y + wy =

x = (M + NXM + PX + P)

siguiente expresin usando los teoremas (13a), (8) y (6):

z = ABC + ABC + BCD

25 of 41

1 102

Ctplulo 3 I Compuertas lgicas y

SECCIONES 3-11 Y 3-12

3-25. Demuestre los teoremas de DeMorgan ensayando todos los casos posibles.

B 3-26. Simplifique cada una de las siguientes expresiones usando los teoremas de

DeMorgan.

-

(a) ABC

- -

(b) + BC

- - - - ---

(c) ABCD (O A + C + D (i) ABCD

Use los teoremas de DeMorgan para simplificar la expresin para la salida

de la figura 3-45.

Convierta el circuito de la figura 3-43(b) a uno que use slo compuertas

NANO. Luego escriba la expresin de salida para el nuevo circuito; simplif-

quelo usando los teoremas de DeMorgan y comprelo con la expresin del

circuito original.

Convierta el circuito de la figura 3-43(a) a uno que slo use compuertas

NOR. Luego escriba la expresin para el nuevo circuito; simplifquelo usan-

do los teoremas de DeMorgan y comprelo con la expresin del circuito ori-

ginal.

Demuestre cmo una compuerta NANO de dos entradas se puede construir

a partir de compuertas NOR de dos entradas.

Demuestre cmo una compuerta NOR de dos entradas se puede construir a

partir de compuertas NANO de dos entrada.-;.

En un avin jet se emplea un sistema para monitorear los valores de rpm,

presin y temperatura de sus motores usando sensores que operan como si-

gue:

Salida del sensor RPM = O slo cuando la velocidad < 4800 rpm

Salida del sensor P = O slo cuando la presin < 220 psi

Salida del sensor T = O slo cuando la temperatura < 200F

En la figura 3-46 se muestra el circuito lgico que controla una luz de adver-

tencia en la cabina para dertas combinadones de condiciones en los moto-

res. Suponga que un ALTO en la salida Wactiva la luz de advertencia.

(a) Determine qu condiciones de los motores advertirn al piloto.

(b) Cambie este circuito a uno que use compuertas NANO.

3-27.

C 3-28.

3-29.

B 3-30.

B 3-31.

3-32.

FIGURA 3-46 T

p

SECCIONES 3-13 y 3-14

3-33. Dibuje las representaciones estndar para cada una de las compuertas lgi-

cas bsicas. Luego dibuje las representaciones alternas.

3-34. Para cada uno de los siguientes enunciados dibuje el smbolo de compuerta

lgica apropiado, estndar o alterno, para la operacin determinada.

(a) Una salida ALTA ocurre slo cuando las tres entradas son BAJAS.

(b) Una salida BAJA ocurre cuando cualquiera de las cuatro entradas es BA-

JA.

(c) Una salida BAJA ocurre slo cuando las ocho entradas son ALTAS.

B

lgebra

booleana

-

(g) A(B + C)D

- -

(h) (M + NXM + N)

-

(d) A+ B

--

(c) AB

w

Luz de

advertencia

R

26 of 41

Problt'nJtN

Se supone que el circuito de la figura 3-45 es un candado simple de combi-

nacin digital, cuya salida generar una seal activa en BAJO UNLOCK slo

para una combinacin de entradas.

(a) Modifique el diagrama del circuito de manera que represente ms eficaz-

mente la operacin del circuito.

(b) Use el nuevo diagrama del circuito para determinar la combinacin de

entrada que activar la salida. Haga esto trabajando hacia atrs, partiendo

de la salida y usando la informacin que proporcionan I~ smbol~ de

la compuerta, como se hizo en los ejemplos 3-22 y 3-23. Compare l~

resultados con la tabla de verdad obtenida en el problema 3-19.

(a) Determine las condiciones de entrada necesarias para activar la salida Z

de la figura 3-37(b). Haga esto trabajando hacia atrs partiendo de la sa-

lida, como se hizo en I~ ejemplos 3-22 y 3-23.

(b) Suponga que este es el estado BAJO de Z que activar la alarn1a. Cam-

bie el diagrama del circuito para reflejar lo anterior y luego use el dia-

grama revisado para determinar las condiciones de entrada necesarias

para activar la alarma.

Modifique el circuito de la figura 3-40 de manera que Al = O se necesite pa-

ra producir DRlVE = 1 en vez de Al = l.

Determine las condidones de entrada necesarias para causar que la salida

de la figura 3-47 pase a su estado activo.

3-35.

3-36.

D 3-37.

3-38.

FIGURA 3-47

3-39. Use los resultados del problema 3-38 con el fin de obtener la tabla de ver-

dad completa para el circuito de la figura 3-47.

3-40. Cul es el estado asegurado para la salida de la figura 3-47? Para la salida

de la figura 3-36<c)?

3-41. En la figura 3-48 se muestra una aplicacin de compuenas lgicas que simu-

la un intemJp(or de dos tiros, similar a los que usamos en nuestra casa para

encender o apagar la luz con dos intemJptores diferentes. Aqu, la luz es un

LEO que estar en ON (conductor) cuando la salida de la compuena NOR

sea BAJO. Note que esta salida est etiquetada UGln" para indicar que es

activa en BAJO. Determine las condiciones de entrada necesarias para acti-

var el LED. Luego verifique que el circuito opere como un interruptor de

dos tiros usando los intemlptores 14 y B. En el captulo 4 usted aprender

cmo disear circuitos como ste para producir una relacin determinada

ent~ entradas y salidas.

8

SECCIN 3-15

3-42. Dibuje nuevamente los ,circuitos de (a) la figura 3-47 y (b) de la figura 3-48

usando los smbolos IEEE! ANSI.

103

A x

B

C

D

E

27 of 41

Captulo 3 I Compuertas lgicas y lgebra booleana

104

FIGURA ~

+5V

A

+5V

B

APLICACiN PARA MICROCOMPUfADORA

3-43. Refirase a la figura 3-40 del ejemplo 3-23. Las entradas A7-Ao son entrada,~

de direcciones que se proporcionan a este drcuito a partir de salidas del

chip del microprocesador en una microcomputadora. El cdigo de direccio-

nes de ocho bits AT~) selecciona el dispositivo que el microprocesador de-

sea activar. En el ejemplo 3-23 el cdigo de direcciones requerido para acti-

var la unidad de disco fue At.-1o = 111111102 = FE16'

Modifique el circuito de manera que el microprocesador deba suminis-

trar un cdigo de direcciones de 4A16 para activar la unidad de disco.

c

EJERCICIOS DlFfclLES

3-44. Demuestre cmo x = ABC se puede implementar con una compuerta NOR

de dos entradas y una compuena NAND de dos entradas.

3-45. Implemente y = ABCD usando slo compuertas de dos entradas.

c

c

RESPUESTAS A LAS PREGUNTAS DE REPASO

SECCiN 3-2

1. .X' - 1 X 8 O 3. 32

2.

SECCiN 3-3

1. Todas las entradas en BAJO. 2. x = A + B +

C + D + E + F 3. Constante en ALTO.

SECCiN 3-4

1. Las cinco entradas - 1.

mantendr la salida en BAJO.

de verdad de cada compuena.

2. Una entrada en BAJO

3. Falso; vase la tabla

SECCiN 3-5

1. La salida del segundo INVERSOR se~ la misma que

la entJ3da A 2. yse~ BAJA slo para A = B = 1.

SECCiN 3-6

1. x = A + B + C + AD 2. x = D(AB + C) + E

SECCiN 3-7

1. x - 1 2. x ~ 3. x - 1 para ambas.

1

~

LUZ

SECCiN 3-8

1. Vase la figura 3-15(a).

3. Vase la figura 3-15(b).

2. Vase la figura 3-17(b).

SECCiN 3-9

1. Todas las entradas en BAJO

3. x = A + B + CD

2. x=O

SECCiN 3-10

l. Y - AC 2. y = ABD 3. y - AD + BD

SECCiN 3-11

1. z = AS + C 2. y = ( + S + T)Q 3. Igual

que la figura 3-28, ex~o que NANO es reemplazada

por NOR. 4. y = AB(C+ [)

SECCiN 3-12

1. T~ 2. El circuito NOR es ms eficiente porque se

puede implementar con un CI 74LSO2.

- -

3. x = (::iBXCD) = (AB+ ("CD) = AB + CD

28 of 41

R('~pu..~1 a~ a ll~ pr"Aunta., dt' r"pl~o dt' seccin

SECCiN 3-13

l. La salida pasa a BAJA cuando cualquier entrada sea

ALTA. 2. La salida pasa a ALTA slo cuando todas

..185 entradas sean BAJAS. 3. La salida pasa a BAJA

cuando cualquier entrada sea BAJA. 4. La salida pa-

. a ALTA slo cuando t<Xias las entradas sean ALTAS.

~~~~

105

2. Z pasad a BAJO cuando .A - B = O, E - 1 Y C o D, o

ambas, sean O. 3. Dos 4. Dos 5. BAJA 6.

.A = B ~ O, C = D - 1 7. ...

SECCiN 3-15

1. Vase la figura 3-41.

y tringuJ~ en las salidas.

2. Reajngulo con &: dentro,

29 of 41

258 . AlGEBRA DE BOOlE y SIMPLIFICACiN lGICA

11. La expresin booleana X = A.B + CD representa

(a) dos operaciones OR multiplicadas (ANO). (b) Una puerta AND de 4 entradas

(c) dos operaciones ANO sumadas (OR) (d) una operacin OR-exclusiva

11. Un ejemplo de una expresin suma de productos es

(8) A+B(C+D) (b) AB+AC+ABC

(c) (A+B+C)(A+B+C) (d) LasI'eSpuestas(a)y(b)

13. Un ejemplo de una expresin producto de sumas es

(a) A(B+C)+AC (b) (A+B)(A+B+C)

(c) A+B+BC (d) Lasrespuesw(a)y(b)

14. Un ejemplo de una expresin suma de productos estndar es

(a) AB + ABC) + ABO (b) ABC + ACD

(c) AB+AB+AB (d) ABCO+AB+A

15. Un mapa de KamaUgh de 3 variables tiene

(a) ocho celdas (b) b'es celdas (c) diecisis celdas (d) cuatro celdas

16. En un mapa de Karnaugh de 4 variables, un tnnino producto de dos variables se obtiene de

un

(a) grupo de 2 celdas de Is (b) grupo de 8 celdas de ls

(c) grupo de 4 celdas de l s (d) grupo de 4 celdas de Os

17. En un mapa de Kamaugh, la agrupacin de Os produce

(a) una expresin producto de sumas (b) una expresin suma de productos

(c) una condicin "indiferente" (d) un circuito lgico AND-OR

18. Un mapa de Kamaugh de 5 variables tiene

(a) diecisis celdas (b) treinta y dos celdas (c) sesenta y cuatro celdas

19. Un SPLD que tiene una matriz AND programable y una matriz OR fija es una

(a) PROM (b) PLA (c) PAL (d) GAL

10. VHDL es un tipo de

(a) circuito lgico prograrnable (b) lenguaje de descripcin hardware

(c) matriz programable (d) matemticas lgicas

21. En VHDL, un puerto es

(a) un tipo de entidad (b) un tipo de arquitectura

(c) una entrada o una salida (d) un tipo de variable

SECCIN 4.1 Opera~ioDes y eIpresioDes booleana.

1. Utilizando la notacin booleana, escribir una expresin que sea 1 siempre que una o ms de

sus variables (.4, B. C y D) sean l.

2. Escribir una expresin que sea l slo si todas sus variables (.4, B, C, D y E) son l.

3. 1!.sCribir una expresin que sea l cuando una o ms variables (.4, B y C) son O.

30 of 41

4. Evaluar las siguientes operaciones:

(a) O + 0+1 (b) 1 + 1 + 1 (e) 1 . O. O

(d)I.I.1 (e)I.0.1 (1)1.1+0.1.1

5. Hallar los valores de las variables que hacen que cada tnnino producto sea 1 y que cada suma

sea O.

(8) AB (b) ABC (c) A+B (d) A+B+C

(e) A+B+C (f) A+B (&) ASC

6. Hallar los valores de X para todos los posibles valores de las variables.

(a) X=(A+B)C+B

(e) X=(A+B)(A+B)

SECCiN 4.2 Leyes y reglas del lgebra booleana

7. Identificar la ley del

dades.

(a) AB + CD + ACD + B = B + AB + ACD + CD

(b) ABCD + ABC = DEBA + CBA

(c) AB(CD + EF + GH) = ABCD + ABEF + ABGH

Identificar la regla o reglas del lgebra de Boole en que est basada cada una de las siguientes

igualdades.

- -

(a) AB+CD+EF=AB+CD+EF (b) AAB+ABC+ABB=ABC

(c) A(BC + BC) + AC = A(BC) + AC (d) AB(C + C) + AC = AB + AC

(e) AB+ABC=AB (f) ABC+AB+ABCD=ABC+AB+D

8.

SECCIN 4.3 Teoremas de DeMorgaD

9. Aplicar los teoremas de DeMorgan a cada expresin:

- -

(8) A+B (b) AB (c) A+B+C (d) ABC

--

(e) A(B+C) (1) AB+CD <&> AB+CD (h) (A+B)(C+D)

10. Aplicar los teoremas de DeMorgan a cada expresin:

-

(a) AB(c+l5) (b) AB(CD+EF)

- -

(c) (A + B + C + D) + ABCD (d) (.4 + B + C + D)(ABCD)

-- --

(e) AB(CD + EF)(AB + CD)

11. Aplicar los teoremas de DeMorgan a las siguientes expresiones:

-- --

(a) (ABC)(EFG) + (H/J)(KLM)

-==--

(c) (A + B)(C + D)(E + F)(G + H)

SECCIN 4.4 Anlisis booleano de los circuitos lgicos

12. Escribir la expresin booleana para cada puerta lgica de la Figura 4.55.

13. Escribir la expresin booleana para cada uno de los circuitos lgicos de la Figura 4.56.

PROBLEMAS. 259

(b) X=(A+B)C

(1) x = (A + BC)(B + C)

(c) X=ABC+AB

de Boole en que est basada cada una

lgebra de las siguientes igual-

- -

(b) (A+BC+CD)+SC

31 of 41

260 . ALGEBRA DE BOOLE y SIMPLIFICACiN LGICA

==1~~~~)- x

B

(a)

~ ~~~3:=)"- x

D

14. Dibujar el circuito lgico representado por cada una de las siguientes expresiones.

(a) A + B + C (b) ABC (c) AB + C (d) AB + CD

15. Dibujar el circuito lgico repRSentado por cada una de las siguientes expresiones.

(a) AS + As (b) AB + AS + ABC

() AB(C+D) (d) A+(B(C+D(B+C)]

16. Construir una tabla de verdad para cada una de las siguientes expresiones booleanas.

(a) A + B (b) AB () AB + BC

(d) (A + B)C (e) (A + B)(S + C)

SECCiN 4.5 Simplificacin mediante el 'Icebra de Boole

17. Mediante las tcnicas del lgebra de Boole, simplificar las siguientes expresiones lo mximo

posible:

(a) A(A + B) (b) A(A + AB) (c) BC + BC

(d) A(A + As) (e) ABC + ABC + ABC

18. Mediante las tcnicas del lgebra de Boole, simplificar las siguientes expresiones:

(a) (A + B)(A + C) (b) As + ABE + ABCD + ABEDE

(c) AB + ~ + A (d) (A + A)(AB + ABE)

(e) AB+(A+B)C+AB

19. Mediante las tcnicas del lgebra de Boole, simplificar las siguientes expresiones:

(a) BD+ B(D+E)+i5(D+ F) (b) ABC+(A+ B+E)+ABED

- -

(c) (B + BC)(B + BC)(B + D) (d) ABCD + AB(CD) + (AB)CD

(e) ABqAB+E(BC+AC)]

20. Determinar cules de los circuitos lgicos de la Figura 4.57 son equivalentes.

; ==1=:)- x ~ =::r~~~)- x

(c) (d)

A --C>o-- x

(b)

FIGURA 4.55

A

: =:~~!=D- x

(b)

FIGURA 4.56

(d)

32 of 41

C

D

B X

(a)

(c)

SECCIN 4.6 Formas estndar de las expresiones booleanas

21. Convertir las siguientes expresiones en sumas de productos:

(a) (A + B)(C + B) (b) (A + BC)C (c) (A + C)(AB + AC)

22. Convertir las siguientes expresiones en sumas de productos:

(a) AB + CD(AB + CD) (b) AB(BC + BD) (c) A + B[AC + (B + C)D]

23. Defmir el dominio de cada suma de productos del Problema 21 y convertir la expresin a su

forma estndar.

24. Convertir cada suma de productos del Problema 22 a su forma estndar.

25. Determinar el valor binario de cada trmino en las expresiones suma de productos del

Problema 23.

26. Determinar el valor binario de cada trmino en las expresiones suma de productos del

Problema 24.

27. Convertir cada una de las expresiones suma de productos estndar del Problema 23 a su forma

producto de sumas estndar.

28. Convertir cada una de las expresiones suma de productos estndar del Problema 24 a su forma

producto de sumas estndar.

SECCIN 4.7 Expresiones booleanas y tablas de verdad

29. Desarrollar la tabla de verdad de cada una de las siguientes expresiones suma de productos

estndar:

(a) ABC + ARC + ABC (b) XYZ + XYz + xrZ + XYz + XYZ

30. Desarrollar la tabla de verdad de cada una de las siguientes expresiones suma de productos

estndar:

(a) ABCD + ABCD + ABCD + ABCD

(b) WXYZ + wxrZ + WxYZ + wiYZ + wxfz

PROBLEMAS. 261

X

D

8

(b)

~:~~;=~=1=>- j X

.4-

C

D

(d)

FIGURA 4.57

33 of 41

262 . ALGEBRA DE BOOLE y SIMPLIFICACiN LGICA

Desarrollar

estDdar:

31.

(a) AB+ABC+AC+ABC (b) X+rZ+WZ+XYz

31. Deaanollar la tabla de verdad de cada una de las siguientes ex~iones producto de sumas

estndar:

(a) (A + B + C)(A + B + C)(A + B + C)

(b) (A + B + C + D)(A + B + C + D)(A + B + E + D)(A + B + C + D)

33. Deaanollar la tabla de verdad de cada una de lu siguientes ex~iones producto de sumas

estndar:

(a) (A + B)(A + C)(A + B + C)

(b) (A + B)(A+ B+C)(B+C+D)(A + B+C +D)

34. Para cada tabla de verdad de la Figura 4.58, obtener una expresin suma de productos estn-

dar y un producto de sumas estndar.

(a)

SECCiN 4.8 Mapas de Karnaugh

35. Dibujar un mapa de Kamaugh de 3 variables y etiquetar cada celda segn su valor binario.

36. Dibujar un mapa de Kamaugh de 4 variables y etiquetar cada celda segn su valor binario.

37. Escribir los trntinos producto estndar correspondientes a cada celda de un mapa de

Kamaugh de 3 variables.

MinimizaciD de una suma de productos mediante el mapa de Karnaugb

38. Utilizar UD mapa de Kamaugh para hallar la suma de productos minima para cada una de las

expresiones siguientes.

(a) Aje + ABC + ABC (b) AC(B + C)

SECCIN 4.9

(d) (b) (c)

34 of 41

~

(c) A(BC + BC) + A(BC + BC) (d) ARC + ARC + ABC + ASC

~

(a) ME + ABC + ABC + ABE

~

(c) DEF + DEF + DEF

40. Expandir las expresiones siguientes a su fonDa suma de productos estndar.

(8) AB + ABC + ABC (b) A + BC

(c) ABCD + ACD + BCD + ABCD (d) AB + ABCD + CD + BCD + ABCD

41. Minimizar las expresiones del Problema 40 utilizando un mapa de Kamaugh.

42. Utilizar un mapa de Karnaugh para reducir las expresiones siguientes a su fonDa suma de pro-

ductos mnima.

(8) A+BC+CD

(b) ABCD + ABCD + ABCD + ABCD

(c) AB(CD + CD) + AB(CD + CD) + ABCD

(d) (AB + AB)(CD + CD)

(e) AB + AB + CD + CD

43. Reducir la funcin especificada en la tabla de verdad de la Figura 4.59 a su fonDa suma de

productos mnima mediante un mapa de Karnaugh.

44. Utilizar el mapa de Karnaugh para implementar la fonDa suma de productos mnima de la fun-

cin lgica especificada en la tabla de verdad de la Figura 4.60.

45. Resolver el Problema 44 para una situacin en que las seis ltimas combinaciones binarias no

estn penoitidas.

~~~

FIGURA 4.59

PROBLEMAS. 263

(b) AC(B + B(B + E)]

FIGURA 4.60

35 of 41

264 . ALGEBRA DE BOOLE y SIMPLIFICACiN LGICA

SECCIN 4.10 Minimizacin de un producto de sumas mediante el mapa de Karnaugh

46. Utilizar un mapa de Karnaugh para hallar la suma de productos mnima de las siguientes

expresiones:

(a) (A + B + C)(A + B + C)(A + B + C)

(b) (X + y)(X +Z)(X + Y + Z)(X+ y +Z)

(c) A(B + C)(A + C)(A + B + C)(A + B + C)

47. Utilizar un mapa de Karnaugh para simplificar las siguientes expresiones a su forma produc-

to de sumas mnima:

(a) (A + B + C + D)(A + B + C + D)(A + B + C + D)

(b) (X+ Y)(W +Z)(X+Y +Z)(W+X+ Y+Z)

48. Para la funcin especificada en la tabla de verdad de la Figura 4.59, determinar el producto de

sumas mnimo mediante el mapa de Kamaugh.

49. Determinar el producto de sumas mnimo para la funcin de la tabla de verdad de la Figura

4.60.

so. Convertir cada una de las siguientes expresiones producto de sumas mnimo a la forma de

suma de productos minima utilizando un mapa de Karnaugh.

(8) (A + B)(A + C)(A + B + C)

(b) (A+B)(A+S+C)(B+C+D)(A+B+C+D)

SECCIN 4.11 Mapa de Karnaugh de cinco variables

51. Minimizar la siguiente suma de productos utilizando un mapa de Karnaugh.

X = ABCDE + ABCDE + ABCDE + ABCDE + ABCDE + ABCDE

+ ABCDE + ABCDE + ABCDE + ABCDE

52. Aplicar el mapa de Karnaugh para minimizar la siguiente suma de productos.

A=~n+~n+~n+~+~+woca+~+~n+~n

SECCIN 4.12 VHDL (opcional)

53. Escribir un programa VHDL para el circuito lgico de la Figura 4.61.

A

B

C

D

E X

F

G

H

J FIGURA 4.61

54. Escribir un programa VHDL para la expresin

y = ARC + ARC + ARE + ABC

Aplicacin a los sistemas digitales

ss. Si es necesario elegir un tipo de display para trabajar bajo condiciones de baja luminosidad,

cul se seleccionara, un display de 7 segmentos de diodos LEO o de cristal lquido? Por

qu?

36 of 41

56. Explicar por qu los cdigos 1010, 1011, 1100, 1101, 1110 Y 1111 pertenecen a la categora de

condiciones "indiferentes.' en las aplicaciones con displays de 7 segmentos.

57. Para el segmento b, cuntas puertas e inversores menos se necesitan para implementar la

suma de productos mnima con respecto a la suma de productos estndar?

58. Repetir el Problema 57 para la lgica de los segmentos c hasta g.

Problemas especiales de diseno

59. La lgica del segmento a de la Figura 4.52 produce una salida a nivel ALTO para activar el

segmento, ocurriendo lo mismo para el resto de los segmentos. Si se utiliza un display de 7-

segmentos que requiere un nivel BAJO para activar cada segmento, modificar adecuadamen-

te la lgica del segmento.

60. Redisear la lgica del segmento a utilizando un producto de sumas mnimo Cul es ms sen-