Professional Documents

Culture Documents

Lattice WP Flash Corruption

Uploaded by

marquitos550b0 ratings0% found this document useful (0 votes)

37 views8 pagesFlash memory is commonly used to store firmware in embedded systems. Occasionally, the firmware stored in The Flash memory is accidentally corrupted. This article examines Flash corruption and its causes beyond a software bug.

Original Description:

Original Title

Lattice Wp Flash Corruption

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentFlash memory is commonly used to store firmware in embedded systems. Occasionally, the firmware stored in The Flash memory is accidentally corrupted. This article examines Flash corruption and its causes beyond a software bug.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

37 views8 pagesLattice WP Flash Corruption

Uploaded by

marquitos550bFlash memory is commonly used to store firmware in embedded systems. Occasionally, the firmware stored in The Flash memory is accidentally corrupted. This article examines Flash corruption and its causes beyond a software bug.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 8

1 Flash Corruption: Software Bug or Supply Voltage Fault?

Flash Corruption: Software Bug or Supply Voltage Fault?

Shyam Chandra, Lattice Semiconductor

Answer: Both! Flash memory is commonly used to store firmware in embedded

systems. Occasionally, the firmware stored in the Flash memory in some systems is

accidentally corrupted, preventing the system from booting up after power-on. Flash

corruption is commonly associated with a software bug. However, it is also commonly

understood that the probability of Flash corruption increases either during power cycling

tests or during margining tests. The Flash corruption problem tends to be more severe

when the number of complex ASICs or SOCs used on the board increases. This article

examines Flash corruption and its causes beyond a software bug, and suggests

methods to minimize the corruption.

How Do The Flash Memory Contents Become Corrupted?

Figure 1 illustrates a typical circuit boards CPU circuitry. When the power is turned on,

the reset generator first activates the CPU reset signal. It then waits until the power to

the CPU, Flash memory and the DDR memory each reaches its correct operation level,

waits for an additional extended period of time (about 150ms) and then deactivates the

CPU reset signal. When the reset signal is deactivated, the CPU begins to execute the

initialization routine in the Flash memory, transfers the contents of the firmware stored

in the Flash memory into the DDR memory and then executes the program from the

DDR memory.

2 Flash Corruption: Software Bug or Supply Voltage Fault?

Flash

CPU

DDR

Mem

Initialization

Routine

Main Routine

Flash Update

Routine

Firmware

Memory Map

1

V

-

C

o

r

e

3

V

3

-

I

/

O

1

V

5

-

D

D

R

3

0

V

7

5

-

V

t

t

1

V

5

-

D

D

R

3

0

V

7

5

-

V

t

t

3V3 -I/O

Reset

Generator

CPU

Reset

Write

Disable

Which

Supply Rails

to Monitor?

Figure 1 Typical CPU Section and Firmware Memory Map

The procedure to load firmware into the Flash memory is:

- Firmware is downloaded into the DDR memory through a communication

interface.

- Jump to the Flash Update Routine to reprogram the Flash with the new firmware.

- Power to the processor is recycled and the new firmware takes effect.

The Flash memory contents can become corrupted if the code execution jumps to the

Flash Update Routine inadvertently. When the board power is cycled, the corrupt

version of the code is loaded into the DDR and the board does not function as

expected.

The code execution could jump to this Flash Update Routine inadvertently due either to

a software bug or to a faulty supply voltage rail (during the power-off event, for

example). A software bug can be detected using normal debugging methods.

However, a faulty power supply voltage is hard to detect, as the supply voltage error

can occur anywhere.

How Does A Supply Voltage Fault Cause The Program To Jump To The Flash

Update Routine?

All ICs have both minimum and maximum operating voltage specifications. If the

maximum voltage specification is exceeded, the device is damaged, and if the supply

drops below the minimum supply level, the device no longer operates as specified. For

example, the core voltage specification of the CPU in Figure 1 is 1.2V +/- 5%. If the

3 Flash Corruption: Software Bug or Supply Voltage Fault?

voltage drops below this level, the ability of the CPUs internal instruction execution

pipeline to reliably transfer instructions and data is compromised, and (depending on

the CPUs process and operating temperature) the instruction can be incorrectly

executed. For example, a Move instruction can be interpreted as a Pop instruction,

and the code execution then jumps to a random memory location (determined by the

contents of the stack). Depending on the contents of that memory location and the error

in execution, the processor can either hang or jump to the Flash Update Routine,

corrupting the Flash memory and overwriting the Flash memory contents.

A droop in DDR memory voltage or threshold voltage also introduces errors in the

instructions and data transferred between the memory and CPU. This erroneous code

execution can cause a jump to the Flash Update Routine, corrupting Flash memory.

When does the supply voltage droop?

The power supply voltage droop can occur for the following reasons:

- Card power down When the power to the board is turned off, not all supplies

on the board turn off at the same time, because the turn off rate depends on the

supply capacity, load, output capacitor, etc. Because the power supply turn-off

slew rate is very slow compared to the processors instruction execution speed,

the processor can experience a supply fault, causing it to mis-execute

instructions before the supply is fully turned off or before its reset signal is

activated.

- Momentary ground voltage rise The power consumption of some processors

can fluctuate dynamically, depending on the executed instructions. When such

changes occur, the device draws large amounts of current for brief periods from

the power source, and dumps these into the ground. As a result, the supply

voltage can momentarily droop and the ground voltage may increase. The

duration of such a condition depends on the inductance of the supply path.

How can Flash corruption due to supply voltage faults be minimized?

The probability of Flash corruption can be minimized by activating the CPU reset when

any supply rail drops below its threshold level. This prevents code execution under

faulty power supply conditions. The reset generator activates both the CPU reset signal

as well as the write protection signal to the Flash memory. In some cases, the reset

generator output is not directly used to reset the CPU. Instead, it is connected to a

CPLD, which executes a reset distribution algorithm. In such cases, the write protection

signal for the Flash should be activated because the CPU may not be reset as soon as

the power supply voltage becomes faulty. The reset generator IC in Figure 1 monitors

all CPU rails 1.0V, 3.3V, 1.5V and 0.75V and activates the reset signal and Flash

write protect signals when any one of them drops below their operating threshold levels.

4 Flash Corruption: Software Bug or Supply Voltage Fault?

Selecting a Reset Generator IC

The criteria for selecting a reset IC include the number of voltage monitoring inputs,

glitch filtering, hysteresis, fault detection accuracy (across operating temperature and

voltage) and fault detection speed.

Number of voltage monitoring inputs: The reset generator IC must monitor all

voltage rails related to the CPU for faults (voltage excursions below corresponding

operating threshold levels). In the case of Figure 1, four inputs are required with

thresholds set at 5% below the nominal operating voltage levels. For example, Lattice

power management ICs support 6 to 12 voltage rail monitoring inputs, and the reset

generation threshold levels can be programmed from -.5% to -20%.

Errors to avoid: Some designs use a single rail reset generator that usually monitors

only, for example, 3.3V. This will not be sufficient, because the 3.3V rail may turn off at

a different rate than the core voltage or the DDR voltage. This arrangement could work

only if all supplies used the 3.3V as their input supply. In most circuit boards, however,

the power supply for the core and DDR use different input voltage sources (due to

power dissipation), and so reset generation using only 3.3V cannot avoid Flash

corruption. The same argument is true if the reset generator monitors only the core

supply rail.

Glitch filtering When the reset generator has single ended sensing (as opposed to

differential sensing) of voltage rails, differences in the ground voltage between the reset

IC and the CPU memory can generate false reset signals. To make sure that the reset

is actually generated by a fault in the supply voltage, and not by a momentary ground

voltage difference, glitch filters are used within the reset ICs. For example, when their

input glitch filters are enabled, Lattice power management ICs ensure that the fault

persists for 64 microseconds before activating the reset signal.

Errors to avoid: Reset generators using ADC and microcontrollers to monitor voltages

implement an ADC sample-averaging algorithm to eliminate the effects of glitches,

resulting in false reset activation. The averaging algorithm derives the actual ADC

voltage by calculating the average of four ADC voltage samples.

Hysteresis Most voltage rails are sourced from switched mode power supplies. The

output of these supplies usually contain ripple. This ripple can cause a reset signal

glitch when the supply level is close to the reset threshold. To avoid this, reset

generators must have hysteresis voltage levels ranging from 0.5% to 1% (of the voltage

monitored). For example, the hysteresis of Lattice power management ICs is 1% of the

monitored voltage. This means that to achieve 1% hysteresis at 3.3V, the hysteresis

step size is 30mV, while the hysteresis step size for a monitoring threshold of 1V is

10mV.

5 Flash Corruption: Software Bug or Supply Voltage Fault?

Errors to avoid: Reset generators using ADC and microcontrollers to monitor voltages

should implement hysteresis in software to prevent glitches in the reset output.

Fault detection Accuracy: Assumptions: The lowest operating voltage of the CPU is

V

NOM

-5%, where V

NOM

is the nominal core voltage. When the supply is turned off, V

NOM

reduces linearly at a rate of 2% per millisecond.

The accuracy of a reset generator is a measure of uncertainty in its ability to detect a

given voltage threshold. For example, a reset generator monitoring Vnom-5% threshold

with an error of 2% can activate the reset output anywhere between Vnom-3% (=-

5%+2%) to Vnom-7% (=-5%-2%). The processor continues to execute instructions until

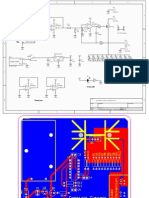

the reset signal is activated. Figure 2 shows two reset generators (zero propagation

delay assumed): one with an accuracy of 2% accuracy (Figure 2a) and the other with

0.7% (Figure 2b). As can be seen, the supervisor with 2% error has a much wider

uncertainty range than that of the reset generator with 0.7% accuracy. While the reset

output activation within the orange zone prevents the processor from executing even

though the supply is healthy (an irritant), the activation in the red zone is its inability to

prevent the processor from corrupting the Flash memory. Clearly, the narrower the

uncertainty, the less probability of Flash corruption. The accuracy of Lattice power

management devices is 0.7%.

6 Flash Corruption: Software Bug or Supply Voltage Fault?

VcoreNOM

VcoreNOM-5%

VcoreNOM-3%

VcoreNOM-7%

CPU Core Rail

Voltage

R

e

s

e

t

N

o

t

R

e

q

u

i

r

e

d

F

l

a

s

h

C

o

r

r

u

p

t

i

o

n

Z

o

n

e

Reset Out

Reset Activation

Uncertainty

(VNOM - 3% to

VNOM - 7% )

Time

(2a) Reset Generator with 2% Error

VcoreNOM

VcoreNOM-5%

VcoreNOM-4.3%

VcoreNOM-5.7%

CPU Core Rail

Voltage

Reset Out

Reset Activation

Uncertainty

(VNOM 4.3% to

VNOM 5.7%)

Time

(2b) Reset Generator with 0.7% Error

Reset Not

Required

Flash Corruption

Zone

Flash Corruption

Probability: HIGHER

Flash Corruption

Probability: LOWER

Reset Generator

VcoreNOM-5%

VioNOM-5%

Vddr3NOM-5%

VttNOM-5%

Reset Out

VcoreNOM

VioNOM

Vddr3NOM

VttNOM

Reset

Thresholds

Figure 2 Flash Corruption Probability vs. Reset Generator Accuracy

Errors to avoid: Some designs use the Power Good from DC-DC converters to

determine the health of supplies and use a CPLD to generate reset signals. This

method does not reduce the probability of Flash corruption because the accuracy of the

Power Good signals of DC-DC converters ranges from 4% to 20%.

Also, some designs use low cost comparators to monitor the voltages. In this case, one

has to pay attention to voltage reference, resistor accuracy and comparator offset

errors. For example, for a 1% accuracy voltage monitoring a circuit across voltage and

temperature, one has to use a comparator with <1mV offset error, Vref with an accuracy

<0.5% and use 0.1% resistors to set the fault detection threshold.

7 Flash Corruption: Software Bug or Supply Voltage Fault?

Fault Detection Speed (Tpd): Assumption: the voltage monitoring accuracy of the

reset generator is 0%.

Fault detection speed is a measure of the time required for the reset generator to

activate the reset output signal from the time the voltage crosses the fault threshold or

the reset generators fault propagation time delay. In Figure 3a, the reset generator

requires 1ms to activate the reset signal. The voltage continues to droop and, by the

time the reset signal is active, the supply voltage at the CPU is 7% below its nominal

operating voltage. This allows about 1ms for the CPU to corrupt the Flash. When the

fault detection speed is less than 100us, the voltage at the CPU is V

NOM

-0.2%, and the

probability of Flash corruption is exponentially reduced. Lattice power management

devices are able to activate the reset signal in about 64us with the glitch filter turned on,

or 16us with the glitch filter turned off.

VcoreNOM

VcoreNOM -5%

VcoreNOM-7%

CPU Core Rail

Voltage

F

l

a

s

h

C

o

r

r

u

p

t

i

o

n

Z

o

n

e

Reset Out

Tpd = 1ms

Time

(3a) Reset Generator with 1ms Tpd

VcoreNOM

VcoreNOM-5%

CPU Core Rail

Voltage

Reset Out

Tpd <100s

Time

(3b) Reset Generator with Tpd<100s

Flash Corruption

Zone

Flash Corruption

Probability: HIGHER

Flash Corruption

Probability: LOWER

VcoreNOM-5.2%

Reset

Generator

VcoreNOM-5%

VioNOM-5%

Vddr3NOM-5%

VttNOM-5%

Reset Out

VcoreNOM

VioNOM

Vddr3NOM

VttNOM

Reset

Thresholds

Figure 3 Flash Corruption Probability vs.

Reset Generator Fault Detection Speed

8 Flash Corruption: Software Bug or Supply Voltage Fault?

Errors to avoid: Some designs use a microcontroller with an ADC as a reset generator.

The reset is activated by its voltage monitoring routine, which is activated by a 10ms to

50ms real time clock Interrupt. Consequently, the reset can be activated with a delay of

10ms to 50ms. Because of this long delay, this method will not be able to prevent Flash

corruption. Note that the voltage monitoring accuracy of an ADC is determined by its

errors and the error of the on-chip ADC voltage reference. The number of ADC bits is

not a measure of its accuracy.

Summary

The conventional thinking that Flash corruption is due only to a software bug results in

engineers wasting time looking for one that does not exist. Flash corruption can occur

after the power input to the board is disconnected. The only way to minimize the

chances of Flash corruption is by holding the processor in reset when there is a supply

voltage fault. The probability of Flash corruption can be significantly reduced by using a

more accurate (<1% voltage fault detection error) and faster (Fault detection speed

<100us) reset generator.

You might also like

- Flash Corruption ReasonsDocument8 pagesFlash Corruption ReasonsNachiket KshirsagarNo ratings yet

- Over Flux Protection TransformerDocument73 pagesOver Flux Protection TransformerArief HusshanNo ratings yet

- Ablerax Ms - SeriesDocument47 pagesAblerax Ms - SeriesPramote RodbonNo ratings yet

- Microprocessors and Microcontrollers DesignDocument8 pagesMicroprocessors and Microcontrollers DesignBittu VermaNo ratings yet

- Analyses Procedure No Post Problem On Laptop Motherboard Circuit PDFDocument3 pagesAnalyses Procedure No Post Problem On Laptop Motherboard Circuit PDFDelwar HossainNo ratings yet

- Soft-Start Controller For Switching Power Supplies: ImplementationDocument6 pagesSoft-Start Controller For Switching Power Supplies: ImplementationMuhammad Umair JavedNo ratings yet

- Stellariserrata: Stellaris Lm3S9790 Revb1 ErrataDocument21 pagesStellariserrata: Stellaris Lm3S9790 Revb1 ErrataNgô Văn ThiệnNo ratings yet

- Precor Error CodesDocument29 pagesPrecor Error Codesfgwood100% (1)

- InterruptDocument7 pagesInterruptJoseph JohnNo ratings yet

- ETAP FAQ Arc Flash Calculations PDFDocument7 pagesETAP FAQ Arc Flash Calculations PDFgilbertomjcNo ratings yet

- ETAP FAQ Arc Flash CalculationsDocument7 pagesETAP FAQ Arc Flash CalculationsmomarqasmiNo ratings yet

- 3 Phase Motor DriverDocument6 pages3 Phase Motor DriverIon MoldoveanuNo ratings yet

- How Does a Logic Board Power UpDocument4 pagesHow Does a Logic Board Power UpBartłomiej DolataNo ratings yet

- 3.working Principal. 4.circuit Diagram. 5.conclusionDocument9 pages3.working Principal. 4.circuit Diagram. 5.conclusionSumit JoshiNo ratings yet

- Chapter 2Document92 pagesChapter 2arati bhavsarNo ratings yet

- Components of A PLCDocument7 pagesComponents of A PLCJCABRACHY ABNo ratings yet

- Answers For QuestionnsDocument101 pagesAnswers For QuestionnsfitzgeraldNo ratings yet

- Upgrading A P - SupplyDocument7 pagesUpgrading A P - SupplyDrift GeeNo ratings yet

- Wild Thumper Controller InstructionsDocument5 pagesWild Thumper Controller InstructionsReza NaderiNo ratings yet

- Chapter 7 Troubleshooting and Fault InformationDocument3 pagesChapter 7 Troubleshooting and Fault Informationtricky777100% (1)

- Vdocuments - MX Etap Faq Arc Flash CalculationsDocument7 pagesVdocuments - MX Etap Faq Arc Flash CalculationsEmmanuel EntzanaNo ratings yet

- Daata 7Document49 pagesDaata 7Govindaraju HSNo ratings yet

- Reset Generation For TI DSP ProcessorDocument8 pagesReset Generation For TI DSP Processorsansm20083184No ratings yet

- Potential Transformer: FaultDocument8 pagesPotential Transformer: FaulttdhinakaranNo ratings yet

- PLC 2Document31 pagesPLC 2Biniam HaddisNo ratings yet

- SMPSDocument7 pagesSMPSDebashish RoyNo ratings yet

- First Revzcn, Zxiew Project ReportDocument11 pagesFirst Revzcn, Zxiew Project ReportamkrishnakumarNo ratings yet

- Failsafe system designDocument3 pagesFailsafe system designSyed Hassan TariqNo ratings yet

- ATX PC Computer Power Supply TroubleshootingDocument23 pagesATX PC Computer Power Supply TroubleshootingCharleneNo ratings yet

- Pmc20-E 10Document4 pagesPmc20-E 10Juan FresnedaNo ratings yet

- Octagon 5025A User ManualDocument126 pagesOctagon 5025A User ManualGregor MaximoffNo ratings yet

- Taming The Variable Speed MotorDocument3 pagesTaming The Variable Speed MotorBalasundaramSrinivasaRajkumarNo ratings yet

- Eye Blink DocumentDocument38 pagesEye Blink Documentpavani13No ratings yet

- FrostBYTE V3Document16 pagesFrostBYTE V3apple.baxterNo ratings yet

- Automatic Grid Failure Detection and ControlDocument26 pagesAutomatic Grid Failure Detection and ControlAnuj TripathiNo ratings yet

- Lec 8Document17 pagesLec 8deemo1354210No ratings yet

- The ANSI/IEEE Code For Phase Sequence Relay Is 47 and of Phase Failure Relay Is 58Document9 pagesThe ANSI/IEEE Code For Phase Sequence Relay Is 47 and of Phase Failure Relay Is 58ax33m144No ratings yet

- Vehicle Speed Control System Using RF CommunicationDocument80 pagesVehicle Speed Control System Using RF CommunicationSaheb Amrinder100% (6)

- Secure Design Using A Microcontroller (I)Document4 pagesSecure Design Using A Microcontroller (I)Ionela100% (4)

- Embedded FirmwareDocument7 pagesEmbedded FirmwareSatya SinhaNo ratings yet

- Self Internet NotesDocument9 pagesSelf Internet NotesFarhan AzizNo ratings yet

- PLC QnaDocument8 pagesPLC QnaMoses MberwaNo ratings yet

- Laptop 3Document2 pagesLaptop 3أحمد الأمينNo ratings yet

- e-PG PATHSHALA-Computer Science Computer ArchitectureDocument9 pagese-PG PATHSHALA-Computer Science Computer Architecturebiswajit biswalNo ratings yet

- Class Notes - Computer Relay ArchitectureDocument10 pagesClass Notes - Computer Relay ArchitecturebiswajitsahooNo ratings yet

- Microcontroller Based Power Supply: Corresponding AuthorDocument5 pagesMicrocontroller Based Power Supply: Corresponding AuthorPrasad LoharNo ratings yet

- Lab manual 2Document5 pagesLab manual 2Muhammad AnsNo ratings yet

- Dual Output Power Supply Sequencing For High Performance ProcessorsDocument10 pagesDual Output Power Supply Sequencing For High Performance ProcessorsXuejun ZhuNo ratings yet

- Vector Surge Relay - MRG20000Document20 pagesVector Surge Relay - MRG20000t_syamprasadNo ratings yet

- Smart Battery White PaperDocument10 pagesSmart Battery White PaperKranthi KumarNo ratings yet

- Motherboard Repair InformationDocument33 pagesMotherboard Repair Informationabhilashvaman5542100% (1)

- APSP - Lecture Notes 2Document7 pagesAPSP - Lecture Notes 2Manjula sNo ratings yet

- Computer Architecture: 1. Draw A Diagram Single Bus Organization of The Data Path Inside A ProcessorDocument8 pagesComputer Architecture: 1. Draw A Diagram Single Bus Organization of The Data Path Inside A Processormd sayemNo ratings yet

- High-Tech Generator Protection RelayDocument20 pagesHigh-Tech Generator Protection RelayLuka YannamNo ratings yet

- Power Good Signals ExplainedDocument18 pagesPower Good Signals ExplainedGaurav Kumar SinghNo ratings yet

- Unbalance CurrentDocument8 pagesUnbalance CurrentRudi AlfadliNo ratings yet

- Introduction to Power System ProtectionFrom EverandIntroduction to Power System ProtectionRating: 5 out of 5 stars5/5 (1)

- Illustrated Assembly Manual k8015 Rev2Document16 pagesIllustrated Assembly Manual k8015 Rev2marquitos550bNo ratings yet

- AKZ 431 Service ManualDocument5 pagesAKZ 431 Service Manualmarquitos550bNo ratings yet

- Currentload Rev2Document2 pagesCurrentload Rev2nvkjayanthNo ratings yet

- Aotf11s60 PDFDocument6 pagesAotf11s60 PDFmarquitos550bNo ratings yet

- UbifsDocument47 pagesUbifsSanel KoncarNo ratings yet

- 60W 18 1Document20 pages60W 18 1marquitos550bNo ratings yet

- Memoria de Samsung K9GAG08U0EDocument55 pagesMemoria de Samsung K9GAG08U0ERodrigo CiezaNo ratings yet

- Ups Lyonn RackeableDocument2 pagesUps Lyonn RackeableMijael MontañoNo ratings yet

- Samsung Un32 40d5500rfDocument80 pagesSamsung Un32 40d5500rfmarquitos550bNo ratings yet

- SN75176 RS-485 CommunicationDocument7 pagesSN75176 RS-485 Communicationmarquitos550bNo ratings yet

- 13 NM 60 NDocument21 pages13 NM 60 Nmarquitos550bNo ratings yet

- Sony HBD Tz130Document28 pagesSony HBD Tz130marquitos550bNo ratings yet

- 30V Dual N-Channel MOSFET with Schottky Diode CharacteristicsDocument9 pages30V Dual N-Channel MOSFET with Schottky Diode CharacteristicsRafael HurtadoNo ratings yet

- 20097841222Document2 pages20097841222marquitos550bNo ratings yet

- Power MOSFET BasicsDocument10 pagesPower MOSFET BasicsBob ProebstelNo ratings yet

- LG Flat TV 32LG40 Manual de EntrenamientoDocument87 pagesLG Flat TV 32LG40 Manual de EntrenamientoMiguel Gabriel TunNo ratings yet

- SCR Guide PDFDocument16 pagesSCR Guide PDFmarquitos550bNo ratings yet

- Planos Tableta Cpu Rk2928 Puerto Usb Pequeno Board Tr738 SCH v10 Moveontechnology ComDocument6 pagesPlanos Tableta Cpu Rk2928 Puerto Usb Pequeno Board Tr738 SCH v10 Moveontechnology Comoryad100% (1)

- SCR Guide PDFDocument16 pagesSCR Guide PDFmarquitos550bNo ratings yet

- Carga Inductiva Con TriacDocument11 pagesCarga Inductiva Con Triacanon_274509247No ratings yet

- 13dBm Metering Node Module APC220N Technical DocumentationDocument6 pages13dBm Metering Node Module APC220N Technical Documentationmarquitos550bNo ratings yet

- Carga Inductiva Con TriacDocument11 pagesCarga Inductiva Con Triacanon_274509247No ratings yet

- Ohaus TS200sDocument77 pagesOhaus TS200smarquitos550bNo ratings yet

- D13N03LTDocument12 pagesD13N03LTmarquitos550bNo ratings yet

- Nand 01 GW 3 B 2 N 6Document64 pagesNand 01 GW 3 B 2 N 6marquitos550bNo ratings yet

- Max 4614Document12 pagesMax 4614marquitos550bNo ratings yet

- AN2492 Application Note: Wide Range 400W L6599-Based HB LLC Resonant Converter For PDP ApplicationDocument35 pagesAN2492 Application Note: Wide Range 400W L6599-Based HB LLC Resonant Converter For PDP Applicationmarquitos550bNo ratings yet

- Trimble Lassen SQDocument196 pagesTrimble Lassen SQmarquitos550bNo ratings yet

- An 133 FDocument12 pagesAn 133 Fmarquitos550bNo ratings yet

- Upgrade Database Using OEM 12C Cloud Control DBACLASSDocument9 pagesUpgrade Database Using OEM 12C Cloud Control DBACLASSVinod KumarNo ratings yet

- HCIA-Data Center V1.5 Training Materials PDFDocument980 pagesHCIA-Data Center V1.5 Training Materials PDFGyamfi Calaquei Sylvester100% (1)

- OptiX OSN 8800 6800 3800 Troubleshooting (V100R007)Document342 pagesOptiX OSN 8800 6800 3800 Troubleshooting (V100R007)Claudio Saez100% (1)

- Prestige XT-W Installation InstructionsDocument2 pagesPrestige XT-W Installation Instructionstatiana_370273750No ratings yet

- TC-610620 Service Manual 00 (RoHS)Document95 pagesTC-610620 Service Manual 00 (RoHS)cjNo ratings yet

- Designing Finite State Machines (FSM) Using VerilogDocument8 pagesDesigning Finite State Machines (FSM) Using VerilogusaravanakumarNo ratings yet

- AEV JK HEMI Harness InstallationDocument10 pagesAEV JK HEMI Harness InstallationBryanNo ratings yet

- C Interview Questions and AnswersDocument9 pagesC Interview Questions and AnswersShazia KhaliqNo ratings yet

- Mercedes Pass Through GuideDocument30 pagesMercedes Pass Through Guiderobert doddsNo ratings yet

- Qualcomm Robotics RB5 Development Kit User Guide: 80-88500-5 Rev. AE December 7, 2023Document89 pagesQualcomm Robotics RB5 Development Kit User Guide: 80-88500-5 Rev. AE December 7, 2023Priya NynaruNo ratings yet

- SELinux For DummiesDocument38 pagesSELinux For DummiesdbahanyNo ratings yet

- Example Risk Assessment For A Motor Vehicle ShowroomDocument4 pagesExample Risk Assessment For A Motor Vehicle Showroomdogankku100% (1)

- Multi Band Ceiling Mount Omni Antenna 790-960 1710-2700 MHzDocument1 pageMulti Band Ceiling Mount Omni Antenna 790-960 1710-2700 MHzJohannita AlvaradoNo ratings yet

- Altivar 61/71: Devicenet™ Card User'S ManualDocument72 pagesAltivar 61/71: Devicenet™ Card User'S ManualMarcelo Alexis Pacheco CastroNo ratings yet

- (2013) Package Relaimpo PDFDocument36 pages(2013) Package Relaimpo PDFLyly MagnanNo ratings yet

- Caracteristicas Router NetGear AC779SDocument2 pagesCaracteristicas Router NetGear AC779SLuis BrizuelaNo ratings yet

- MeSH ConceptDocument29 pagesMeSH ConceptRAMAKRISHNANNo ratings yet

- Introduction To Robotics Lab Manual: The Islamia University of Bahawalpur Department of Computer Systems EngineeringDocument62 pagesIntroduction To Robotics Lab Manual: The Islamia University of Bahawalpur Department of Computer Systems EngineeringEngrFawwadHassanJaskani100% (1)

- Optergy Proton Datasheet Rev5Document2 pagesOptergy Proton Datasheet Rev5taha amjadNo ratings yet

- "... Stopped Working" Error When Opening Product: ProblemDocument7 pages"... Stopped Working" Error When Opening Product: Problemkendy chavez ccahuanaNo ratings yet

- Infrared Sensor Detects Obstacles Using 555 Timer CircuitDocument5 pagesInfrared Sensor Detects Obstacles Using 555 Timer CircuitGirijaKaushikNo ratings yet

- How To Create A Custom Startup Winpe 2.X CDDocument13 pagesHow To Create A Custom Startup Winpe 2.X CDmmarrioNo ratings yet

- Content Server Schema and Report Fundamentals 10.5Document9 pagesContent Server Schema and Report Fundamentals 10.5dustinbrNo ratings yet

- Tigear 2Document154 pagesTigear 2Alberto Roca MNo ratings yet

- A Presentation On Home Automation System Using Atmega328 Chip and GSM Module For Long Distance ControlDocument12 pagesA Presentation On Home Automation System Using Atmega328 Chip and GSM Module For Long Distance ControlKola SarakiNo ratings yet

- Activit y Description Duration PredecessorDocument5 pagesActivit y Description Duration PredecessorJanaka Wijeyesinghe0% (1)

- Magic GlovesDocument9 pagesMagic GlovesyrikkiNo ratings yet

- Monitoring LDOMSDocument49 pagesMonitoring LDOMSAhmed EidNo ratings yet

- Canon Ip5200 Service ManualDocument64 pagesCanon Ip5200 Service ManualCharles Doud100% (1)

- Scientech 71: Best Choice For Your PCB LabDocument2 pagesScientech 71: Best Choice For Your PCB LabSourabh HajraNo ratings yet