Professional Documents

Culture Documents

SEC10

Uploaded by

Arvind BaroniaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SEC10

Uploaded by

Arvind BaroniaCopyright:

Available Formats

10

FLASH MEMORY TECHNOLOGY

OVERVIEW

Flash memory technology is a mix of EPROM and EEPROM technologies. The term flash was

chosen because a large chunk of memory could be erased at one time. The name, therefore, distinguishes flash devices from EEPROMs, where each byte is erased individually.

Flash memory technology is today a mature technology. It is a strong competitor to other nonvolatile memories such as EPROMs and EEPROMs, and to some DRAM applications.

HOW THE DEVICE WORKS

The more common elementary

flash cell consists of one transistor

POLY 2 WORD/SELECT

ONO DIELECTRIC

with a floating gate, similar to an

POLY 1 FLOATING

GATE

EPROM cell. However, technology

and geometry differences between

flash devices and EPROMs exist. In

N+ S/D

N+ S/D

particular, the gate oxide between

the silicon and the floating gate is

EPROM MEMORY CELL

thinner for flash technology.

Source and drain diffusions are also

different. These differences allow

the flash device to be programmed

POLYCIDE

and erased electrically. Figures 10ONO

1 and 10-2 show a comparison

OXIDE ON N+

between a flash memory cell and an

POLY 1

EPROM cell from a same manufacN+ S/D

turer (AMD) with the same technolGATE OXIDE 1

ogy complexity. The cells look

similar since the gate oxide thickFLASH MEMORY CELL

Photos by ICE, Memory 1997

22482

ness and the source/drain diffusion

differences are not visible in the

Figure 10-1. AMD EPROM Versus AMD Flash Memory Cells

photographs.

INTEGRATED CIRCUIT ENGINEERING CORPORATION

10-1

Flash Memory Technology

Type

Density

Date Code

Cell Size

Cell Gate

Length

Flash

4Mbit

9406

6m2

0.7m

9634

5.52m2

0.7m

EPROM

1Mbit

Source: ICE, "Memory 1997"

22483

Figure 10-2. EPROM Versus Flash Cell (AMD)

Other flash cell concepts are based upon EEPROM technology. Figure 10-3 shows a split-gate cell

and Figure 10-4 shows a transistor with the tunnel oxide in only a part of the oxide under the floating gate. These cells are larger than the conventional one-transistor cell, but are far smaller than

the conventional two-transistor EEPROM cell.

Photo by ICE, Memory 1997

22480

Figure 10-3. Split Gate Flash Cell

Photo by ICE, Memory 1997

22481

Figure 10-4. Tunnel Window Flash Cell

10-2

INTEGRATED CIRCUIT ENGINEERING CORPORATION

Flash Memory Technology

The electrical functionality of the flash memory cell is similar to that of an EPROM or EEPROM.

Electrons are trapped onto the floating gate (see a detailed description in Section 9). These electrons modify the threshold voltage of the storage transistor. Electrons are trapped in the floating

gate using Fowler-Nordheim tunneling (as with the EEPROM) or hot electron injection (as with

the EPROM). Electrons are removed from the floating gate using Fowler-Nordheim tunneling as

with the EEPROM. Figure 10-5 summarizes the different modes of flash programming.

Electron Trapping

Electron Removal

VCG

Bi-polarity FN-t

Write / Erase

technology

Fowler-Nordheim tunneling

Vsub

VCG

Hot-Electron

injection and FN-t

technology

VD

Fowler-Nordheim tunneling

Hot-Electron Injection

Source: ICE, "Memory 1997"

20840

Figure 10-5. Comparison Between the Different Types of Flash Programming

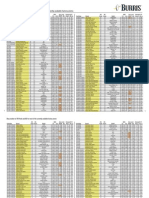

Figure 10-6 summarizes chip and cell sizes of some of the flash memories analyzed by ICEs laboratory. Most of these are date coded 1994 but give a good idea of what is widely used in 1997.

All these memories use the NOR flash architecture. A photo of SanDisks 32Mbit flash cell (used

on its CompactFlash cards) featuring a cell size of 1.8m2 is shown Figure 10-7.

ARCHITECTURE

As with other semiconductors, the flash memory chip size is the major contributor to the cost of

the device. For this reason, designers have developed alternative memory array architectures,

yielding a trade-off between die size and speed. NOR, NAND, DINOR, and AND are the main

architectures developed for flash memories.

INTEGRATED CIRCUIT ENGINEERING CORPORATION

10-3

Flash Memory Technology

Density

Date Code

Cell Size

(m2)

Cell Type

Gate

Length (m)

Die Size

(mm2)

SST

1Mbit

9417

10.2

Split Gate

0.95

29.0

AMD

2Mbit

9325

8.0

1T

0.80

51.2

AMD

4Mbit

9406

6.0

1T

0.70

49.8

ATMEL

4Mbit

9411

16.6

Tunnel Window

N/A

107.0

INTEL

16Mbit

1993

3.3

1T

0.75

123.6

AMD/FUJITSU

16Mbit

9436

2.7

1T

0.60

87.0

Source: ICE, "Memory 1997"

22479

Figure 10-6. Flash Chip and Cell Size Comparison

METAL BIT LINE

POLY 3

POLY 2

POLY 1

W

PLUG

DIFFUSED BIT LINE

Control Word Control

(Poly 2) (Poly 3) (Poly 2)

Q1

Q3

Q2

Q4

Photo by ICE, Memory 1997

22478

Figure 10-7. SanDisk Flash Cell

NOR Cell

The NOR architecture is currently the most popular flash architecture. It is commonly used in

EPROM and EEPROM designs. Aside from active transistors, the largest contributor to area in the

cell array is the metal to diffusion contacts. NOR architecture requires one contact per two cells,

which consumes the most area of all the flash architecture alternatives. Electron trapping in the

floating gate is done by hot-electron injection. Electrons are removed by Fowler-Nordheim tunneling. The worlds leading manufacturers of flash devices (Intel, AMD) use NOR cell configurations.

10-4

INTEGRATED CIRCUIT ENGINEERING CORPORATION

Flash Memory Technology

NAND Cell

To reduce cell area, the NAND configuration was developed. Figure 10-8 shows the layouts of

NOR and NAND configurations for the same feature size. The NAND structure is considerably

more compact.

NOR-CELL

,,, ,,

,,, ,,

,,, ,,

,,, ,,

,,,

,,,

,,,

,,,

,,,

,,,

,,,

,,,

,,

,,

,,

,,

,,,

,,,

,,,

,,,

,,

,,

,,

,,

,,

,,

,,

,,

,,,,,,,, ,,,,,,,,,

,,,

,,,,,,,, ,,,,,,,,,

,,,

,,,,,,,, ,,,,,,,,,

,,,

,,,,,,,, ,,,,,,,,,

,,,

NAND-CELL

Floating Gate

Control Gate

,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,

Select Gate

Select Gate

Bit Line (Aluminum)

P-Well

N+

Source: ICE, "Memory 1997"

19960

Figure 10-8. Comparison of NOR and NAND Architectures

A drawback to the NAND configuration is that when a cell is read, the sense amplifier sees a

weaker signal than that on a NOR configuration since several transistors are in series. Figures 109 and 10-10 describe the NAND architecture from Toshiba. The weak signal slows down the speed

of the read circuitry, which can be overcome by operating in serial access mode. This memory will

not be competitive for random access applications. Figure 10-11 shows a speed comparison of

NOR and NAND devices.

DINOR Cell

DINOR (divided bit-line NOR) and AND architectures are two other flash architectures that

attempt to reduce die area compared to the conventional NOR configuration. Both architectures

were co-developed by Hitachi and Mitsubishi.

INTEGRATED CIRCUIT ENGINEERING CORPORATION

10-5

Flash Memory Technology

EMBEDDING

COMPOUND

POLY 3

METAL

POLY 2

N+

EDGE CELLS

POLY 1

Photo by ICE, Memory 1997

EDGE CELLS

22476

Figure 10-9. Toshiba Flash NAND Cell

Architecture

NAND

Date Code

9528

Cell Size

1.3m2

Die Size

103mm2

Min Feature

Size (Gate)

Cell: 0.25m

Periphery: 0.5m

Source: ICE, "Memory 1997"

22475

Figure 10-10. Toshibas 32Mbit Flash Characteristcs

Architecture

NOR

NAND

Random Access Time

80ns

20s

Serial Access Time

80ns

Source: ICE, "Memory 1997"

19961

Figure 10-11. NOR Versus NAND Access Times

The DINOR design uses sub-bit lines in polysilicon. Mitsubishi states that its device shows low

power dissipation, sector erase, fast access time, high data transfer rate, and 3V operation. Its

device uses a complex manufacturing process involving a 0.5m CMOS triple well, triple-level

polysilicon, tungsten plugs, and two layers of metal. Figure 10-12 shows the DINOR architecture.

AND Cell

With AND architecture, the metal bit line is replaced by an embedded diffusion line. This provides a reduction in cell size. The 32Mbit AND-based flash memory device proposed by Hitachi

needs a single 3V power supply. In random access mode, the device is slower than a NOR-based

device. Hitachis device is specified to operate with a 50ns high-speed serial access time.

10-6

INTEGRATED CIRCUIT ENGINEERING CORPORATION

Flash Memory Technology

,,,,,,,

,

Second Al

Main Bit Line (First Al)

Sub-Bit Line (Polysilicon)

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,,, ,,, ,,, ,,,, ,,,,, ,,,, ,,,, ,,

,

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,,,, ,,, ,,, ,,,, ,,,,, ,,,, ,,,,

,

12.7m (1.6m/Cell)

Select Transistor

Source: Mitsubishi/ICE, "Memory 1997"

19962A

Figure 10-12. DINOR Architecture

Figure 10-13 presents a review of the different flash architectures. Figure 10-14 shows a cell size

comparison between DRAM, NAND, and NOR flash architectures. The NOR flash one-transistor

cell has roughly the same size as a DRAM cell for the same process generation.

NAND ARCHITECTURE

NOR ARCHITECTURE

Bit 1

Bit 2

Bit 1

Bit 3

Word 1

Bit 2

Select Gate 1

Word 1

Word 2

Word 2

Word 3

Word 3

Word 8

Select Gate 2

Source

For One

Block

AND ARCHITECTURE

Bit 1

Bit 2

Select Gate 1

DINOR ARCHITECTURE

Main Bit Line

(Metal)

Word 1

Select Tr2 Select Tr1

Sub Bit Line (Polysilicon)

Word 1

Word 2

Word 8

Word 3

Source Line

Word 8

Select Gate 2

19963

Source: ICE, "Memory 1997"

Figure 10-13. Flash Architectures

INTEGRATED CIRCUIT ENGINEERING CORPORATION

10-7

Flash Memory Technology

Technology

(Gate Length)

NAND Flash

Cell

NOR Flash

Cell

DRAM Cell

0.6m

3m2

6m2

6m2

0.4m

1.3m2

2.5m2

2.5m2

Source: ICE, "Memory 1997"

22474

Figure 10-14. Flash and DRAM Cell Size Comparison

Several companies strongly support one type of flash architecture. However, to hedge their bets

and to offer products for several different end uses, many firms have elected to build flash devices

using more than one type of architecture. Figure 10-15 shows vendors support of flash memory

architectures.

NOR

NAND

AND

DINOR

Intel

National

Hitachi

Mitsubishi

AMD

Samsung

Mitsubishi

Hitachi

Atmel

Toshiba

Fujitsu

Fujitsu

TI

AMD

Motorola

Micron

SGS-Thomson

Macronix

UMC

Mitsubishi

Samsung

Toshiba

Winbond uses its proprietary "split-gate" architecture.

Source: ICE, "Memory 1997"

20080C

Figure 10-15. Vendors Support of Flash Memory Architectures

Audio NAND Flash

Toshiba, Samsung, and National Semiconductor each introduced 4Mbit serial audio NAND flash

devices. Their devices used the NAND cell configuration. These parts, used for telephone

answering machines or other audio data storage, have started to replace audio DRAMs. Based on

the small NAND cell, audio NAND flash uses serial access to face speed problems. Moreover,

audio NAND devices are cheaper than standard NAND flash since they contain fewer functions.

Sometimes audio flash devices may contain some bad cells. Even though those faulty cells would

not affect the audio applications, the product would sell for less money.

10-8

INTEGRATED CIRCUIT ENGINEERING CORPORATION

Flash Memory Technology

MULTI-LEVEL STORAGE CELL (MLC)

Four-Level Storage Cell

Most of the major flash companies are working to develop their version of a multi-level cell flash

device. The goal of this device is to store information in several different levels inside the same

memory cell. The most common developments are those that store information on four different

levels in the same cell.

In multi-level cell, there are two difficult issues that must be addressed by manufacturers. The

first is to tightly control the program cycle that gives four different levels of charge. The second

difficulty is to accurately recognize, during the read cycle, the four different threshold voltages of

the programmed transistor.

Flash devices must be reliable even in worst case conditions. External parameters (power supplies, temperatures, etc.) may vary from the time the flash device is programmed to the time it is

read. Figure 10-16 shows an example of threshold voltage distribution for four stages stored on

the same transistor.

Cell Distribution

"11"

"10"

"01"

"00"

VT

Source: ICE, "Memory 1997"

20805

Figure 10-16. Threshold Voltage Distribution for Four States

Different companies are working intensively on this issue. During each of the past several years,

papers were presented by most of the major flash manufacturers regarding multi-level cell technology. Intel presented a paper on its four-level storage work at the 1995 ISSCC conference. At

the 1996 ISSCC conference, two papers were presented on this concept. Samsung presented a

128Mbit four-level NAND flash cell and NEC presented a 64Mbit four-level NOR flash cell. At

the 1995 Symposium on VLSI Circuits, Toshiba presented a development for future high density

INTEGRATED CIRCUIT ENGINEERING CORPORATION

10-9

Flash Memory Technology

MLC NAND flash memories. At the December 1996 IEDM Conference, SGS-Thomson presented

a study on MLC for the different flash architectures and their trade-offs. Highlights of this study

are presented in Figure 10-17.

Array Architecture

Cell Size*

Advantage as

Single-Bit Concept

Disadvantage as

Single-Bit Concept

Advantage as

Multi-Bit Concept

Disadvantage as

Multi-Bit Concept

Common Ground

9-11F2

1. General purpose

applications and most

understood array and

technology

DINOR

7.5F2

1. Reduced cell size while 1. Requires triple poly

preserving the common

ground array

1. Reduction in BL-BL

coupling

1. Tunneling during

programming

2. Source resistance

1. Relatively large

cell size

1. Minimum interaction

1. Closely coupled

between neighbors

metal bitline

2. CHEI for programming 2. Vt distribution affected

by neighbor data

AND

8F2

1. Good combination of

CG and DINOR

2. Drain contact every

32-128 cells

1. Reduction in BL-BL

coupling

1. Tunneling during

programming

2. Source resistance

NOR Virtual Ground AMG

6F2

1. Small cell size

2. Low current

programming

1. CHE programming

2. Reduction in BL-BL

coupling

1. Resistive diffusion

bitlines

2. Neighbor interaction

affecting Vt distribution

1. CHEI programming

2. Disturb reduction due

to poly-poly erase

1. Neighbor interaction

affecting Vt distribution

2. Low read current and

high erase voltages

1. Programming by tunneling in the channel

NOR Virtual Ground Split Gate Poly-Poly Erase

7.5F2

6F2

NAND

1. Overerase not an issue

1. Requires triple poly

1. Small cell size

1. Read thru stack of

15 cells

2. High read and programming voltages

*F is the technology feature size

Source: SGS-Thomson/ICE, "Memory 1997"

22595

Figure 10-17. Trade-Off of MLC Using Different Flash Architectures

During the first half of 1997, Intel announced that it sampled 64Mbit MLC parts. SanDisk, along

with manufacturing partner Matsushita, used the technology to boost single-chip capacity to

64Mbit. It refers to its multi-level cell technology as Double Density or D2. SanDisk claims

that the 64Mbit die is only 10 percent larger than the companys 32Mbit die. Meanwhile, the company is also working on a 256Mbit Double Density flash device.

Multi-Level Storage Cell for Audio Applications

Development of MLC cell takes considerable time because digital storage needs to be reliable. The

data needs to stay valid in worst-case conditions. For audio applications, however, tolerances

allow for some error. For this reason, Information Storage Devices (ISD) proposed non-volatile

memories that are able to store 256 different levels on the same transistor. ISDs product family is

called ChipCorder and enables a single chip solution for voice recording and playback. It currently has a chip with up to four minutes of voice storage capacity.

10-10

INTEGRATED CIRCUIT ENGINEERING CORPORATION

Flash Memory Technology

POWER SUPPLY

Currently, flash power supplies range from 5V/12V down to 2V. Flash memory power supplies

vary widely from vendor to vendor. There are two main reasons for this variation. First, flash

cells need high voltage for programming. With different types of flash architectures and designs,

different program/erase techniques (Fowler-Nordheim tunneling or hot-electron injection) exist.

These architectures do not share the same voltage requirements. For example, high voltage with

no current can be generated internally with a voltage pump. However the source/drain current

of hot-electron injection requires an external power supply.

The second reason for wide power supply variation is that there are many applications that currently require different power supply levels. Some applications may require low-voltage flash

devices while others operate well using flash device with high-voltage characteristics.

Manufacturers can propose different types of power supplies that best fit a specific application.

SmartVoltage

SmartVoltage is an Intel concept. However, other manufacturers including Sharp and Micron

have signed on to license the technology. SmartVoltage parts can be used for several power supplies. Read voltage may be 2.7V, 3.3V or 5.5V and programming voltage may be 3.3V, 5V or 12V.

Flash memories are used in a wide variety of applications as illustrated Figure 10-18. All these applications allow vendors to offer several flash solutions. Using the NAND flash architecture for serial

access applications is one example. Figure 10-19 shows the diversity of the flash memory types.

Focus Segment

Application

Auto

Engine Control

PC

BIOS

HDD

Disc Control

Wireless

Analog/SSM

Networking

Hub Control

Source: TI/ICE, "Memory 1997"

22596

Figure 10-18. Flash Target Segments

INTEGRATED CIRCUIT ENGINEERING CORPORATION

10-11

Flash Memory Technology

Core Architecture

NOR, NAND, DiNOR, AND

Cell Architecture

1 Transistor, Split Gate, Others

Storage

1 Level, Multi-Level Cell (MLC)

Voltage (Read/Program)

5V/12V, 5V/5V, 3V/5V, 3V/3V, 2.7V/2.7V,

2.2V/2.2V, Smart Voltage

Configurations

Random Access, Serial Access, Others

Applications

Audio, PC, Wireless

Source: ICE, "Memory 1997"

22473

Figure 10-19. Flash Diversity

RELIABILITY CONCERNS

There are three primary reliability concerns of a flash memory IC. They are data retention, thin

oxide stress, and over or under erasing/programming.

Regarding erase/program, flash ICs that use hot electron injection for trapping electrons in the

floating gate are programmed (data equal to 0) by capturing electrons in the floating gate, as with

an EPROM.

Flash ICs that use Folwer-Nordheim tunneling for trapping electrons in the floating gate will be

programmed (data equal to 0) by removing the electrons from the floating gate, as with an

EEPROM. The reliability concern is to either over program or over erase as shown in Figure 10-20.

12V

0V

0V

0V

N+

N+

12V

F

N+

N+

VT SHIFT HIGH

VT SHIFT LOW

FN tunneling for program

Low program/erase current

Over program problem

Hot electron injection to program

Lower program disturb

Over erase problem

Slow program time

Fast program time

Source: Motorola/ICE, "Memory 1997"

20841

Figure 10-20. Erased Threshold Voltage Shift for Flash Memory Cell

10-12

INTEGRATED CIRCUIT ENGINEERING CORPORATION

Flash Memory Technology

PCMCIA

Magnetic memory storage and flash memory devices will co-exist. Magnetic memory will continue to dominate in ultra-high capacity, low cost/Mbyte applications where power, weight/size,

and mechanical ruggedness are not a consideration. Flash-based mass storage will become pervasive in small, low power, portable electronic platforms, providing low power, small size, and

unparalleled ruggedness/reliability and offering lowest entry cost of any mass storage. PCMCIA

(Personal Computer Memory Card International Association) cards were developed for this flash

mass storage application.

Hitachi proposed a 75Mbyte ATA PC Card using a mostly good memory (MGM) production technique. The chip must have a minimum of 98 percent of its memory cell sectors free of defect and

have all logic circuits 100 percent functional. Figure 10-21 illustrates an ATA Card using the MGM

technology.

C +

Logic

Logic

Flash

Flash

Flash

with MGM

Flash

with MGM

Flash

Flash

Flash

with MGM

Flash

with MGM

Flash

Flash

with MGM

Flash

with MGM

Aux Byte

512Byte Sector

Aux Byte

512Byte Sector

Aux Byte

512Byte Sector

Aux Byte

512Byte Sector

Aux Byte

512Byte Sector

Address Decode

512Byte Sector

Aux Byte

Data Register

MGM Memory

Good Sector

Flash

First Generation

Bad Sector

Second Generation

Source: Hitachi/ICE, "Memory 1997"

22597

Figure 10-21. ATA Card Evolution

SMALL FLASH-MEMORY MODULES

Small flash-memory modules were developed for applications where PCMCIA storage cards will

not physically fit. The main applications are for equipment needing small-size storage such as

PDAs, cameras, and digital audio recorders.

Three developmentsCompactFlash, Miniature Card and Solid State Floppy Disk Card

(SSFDC)are similar in size but employ substantially different electrical interface schemes.

Figure 10-22 presents the three miniature flash card solutions.

INTEGRATED CIRCUIT ENGINEERING CORPORATION

10-13

Flash Memory Technology

CompactFlash

Miniature Card

SSFDC

SanDisk

Intel/AMD

Toshiba

CampactFlash

Association

Miniature Card

Implementers Forum

SSFDC Forum

43 x 36 x 3.3mm

38 x 33 x 3.5mm

45 x 37 x 0.76mm

NOR Flash

NOR Flash, DRAM,

SRAM, OTP, ROM

NAND Flash

Capacity

2 to 15Mbytes

2, 4Mbytes

2, 4Mbytes

Connector Type

50-Pin subset

of PCMCIA

40-Pad Elastomeric

68-Pin PCMCIA

With Adapter

Number of Contacts

Circular Pins

Flat-Edge Contacts

Flat-Surface Contacts

Software Interface

ATA

FTL (Flash

Translation Layer)

Host-Based

Controller

Built-In Controller?

Yes

No

No

Original Developers

Industry Alliance

Module Dimensions

Memory Type

Source: ICE, "Memory 1997"

22598

Figure 10-22. Standards for Small Flash-Memory Modules

CompactFlash

CompactFlash was developed by SanDisk Corporation, Sunnyvale, California, in 1994. The

CompactFlash Association (CFA) was established in October, 1995, to promote and encourage the

worldwide adoption of CompactFash technology as an open industry standard. More than 40

companies have joined the CFA.

The CompactFlash design incorporates the ATA (AT-Attachment) interface standard, that uses the

same electrical signals as PCMCIA/ATA flash cards. The first product that employed

CompactFlash technology was IBMs Palm Top PC110, which was introduced in September, 1995.

Miniature Card

The Miniature Card, originally developed by Intel, is supported by the Miniature Card

Implementers Forum (MCIF). The Miniature Card incorporates a linear-addressed format like

PCMCIA flash cards. This card needs host-based software to be read. This software is called Flash

Translation Layer (FTL) and was developed by M Systems. Miniature Cards are cheaper than

CompactFlash cards but need that additional software. Figure 10-23 shows the ATA configuration

versus the linear configuration. Intel developed its Miniature Card for high-volume consumer

applications and will not support CompactFlash.

10-14

INTEGRATED CIRCUIT ENGINEERING CORPORATION

Flash Memory Technology

ATA Flash Cards

Card

System

Host

CPU

ATA

Intelligent

Controller

Flash

Linear Non-ATA Flash Cards

Card

System

Host

CPU

Flash File

System Software

Flash Memory

Source: ICE, "Memory 1997"

20807

Figure 10-23. ATA Versus Linear Flash Card

Solid State Floppy Disk Card (SSFDC)

Toshibas Solid State Floppy Disk Card is based on its flash NAND cell technology. This card was

announced in late 1995. With its small die size, the NAND technology is more cost effective. Like

the CompactCard this card includes an adapter to be compatible with the PCMCIA Type II cards.

An SSFDC Forum was held in April 1996 in Japan to agree on an industry standard for a supersmall data storage medium. More than 40 companies, including Samsung Electronics, have joined

the SSFDC Forum.

The SSFDC is the size of a credit card, and is much thinner than any of the other small-form factor

memory cards. Used with an ATA PC card adapter, SSFDC can be used as a standard PC card.

INTEGRATED CIRCUIT ENGINEERING CORPORATION

10-15

Flash Memory Technology

10-16

INTEGRATED CIRCUIT ENGINEERING CORPORATION

You might also like

- Cartridge List EliminatorIIIDocument12 pagesCartridge List EliminatorIIIArvind BaroniaNo ratings yet

- Digital Signal Processing Approach to InterpolationDocument11 pagesDigital Signal Processing Approach to InterpolationArvind BaroniaNo ratings yet

- Scan 0001Document9 pagesScan 0001Arvind BaroniaNo ratings yet

- ParthDocument5 pagesParthArvind BaroniaNo ratings yet

- Calibrating The Microscope: IBIS Data Acquisition Training GuideDocument3 pagesCalibrating The Microscope: IBIS Data Acquisition Training GuideArvind BaroniaNo ratings yet

- 303 British Pages 282 and 283Document2 pages303 British Pages 282 and 283dragoon119No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Toshiba FAB EMMC-1511507Document3 pagesToshiba FAB EMMC-1511507Wagner WagrilloNo ratings yet

- Dos and Don'Ts of Deploying NVMe Over Fabrics BRKDCN-3812 2022Document226 pagesDos and Don'Ts of Deploying NVMe Over Fabrics BRKDCN-3812 2022James ZhangNo ratings yet

- A Comparative Study of Flash StorageDocument20 pagesA Comparative Study of Flash Storagepeteco carabajalNo ratings yet

- Reed Solomon CodesDocument13 pagesReed Solomon CodesGaneshVenkatachalamNo ratings yet

- 15 DifferentiatorsDocument48 pages15 Differentiatorsjagdish joshiNo ratings yet

- Vision Sensor With Built-In AI: Simple and Impressive Detection StabilityDocument32 pagesVision Sensor With Built-In AI: Simple and Impressive Detection Stabilitymarius100% (1)

- FLASH TYPE AND USE CASESDocument6 pagesFLASH TYPE AND USE CASESseanNo ratings yet

- 5210 SSD Vs HDD Endurance White Paper PDFDocument9 pages5210 SSD Vs HDD Endurance White Paper PDFSonam RaiNo ratings yet

- Working With Embedded Multimediacard (Emmc)Document15 pagesWorking With Embedded Multimediacard (Emmc)britto100% (1)

- OpenScape Xpert V6 System Manager Online Help Administrator Documentation Issue 2Document188 pagesOpenScape Xpert V6 System Manager Online Help Administrator Documentation Issue 2Dinesh SangamNo ratings yet

- Nor Nand Flash Guide PDFDocument9 pagesNor Nand Flash Guide PDFZhenhai WeiNo ratings yet

- SMI Confidential: SM3267 Test Program and ISP Release NoteDocument3 pagesSMI Confidential: SM3267 Test Program and ISP Release NoteRaul Trujillo PNo ratings yet

- Analyzing Real Time Behaviour of Flash MemoriesDocument56 pagesAnalyzing Real Time Behaviour of Flash Memoriesapi-3802214100% (2)

- Curdso PDFDocument18 pagesCurdso PDFJose LopezNo ratings yet

- A Deep Dive Into 3D-NAND Silicon Linkage To Storage System Performance & ReliabilityDocument15 pagesA Deep Dive Into 3D-NAND Silicon Linkage To Storage System Performance & ReliabilityHeekwan SonNo ratings yet

- Flash Memories: Detlev RichterDocument287 pagesFlash Memories: Detlev RichterdarNo ratings yet

- LG 55lw5700-Ue Chassis La12c SCHDocument27 pagesLG 55lw5700-Ue Chassis La12c SCHGustavoNo ratings yet

- USBest UT165Document27 pagesUSBest UT165Wise ManNo ratings yet

- Hardware and IT Infrastructure Guide PDFDocument42 pagesHardware and IT Infrastructure Guide PDFcoroner4No ratings yet

- 128-Megabit 2.7-Volt Dual-Interface Dataflash At45Db1282 PreliminaryDocument35 pages128-Megabit 2.7-Volt Dual-Interface Dataflash At45Db1282 PreliminarymhasansharifiNo ratings yet

- 6500 Ion Nvme SSD Product Brief-3223536Document4 pages6500 Ion Nvme SSD Product Brief-3223536ManunoghiNo ratings yet

- Ocz Deneva2 Msata Product BriefDocument2 pagesOcz Deneva2 Msata Product BriefFlavio BraboNo ratings yet

- Romelos Siwalette - SAN and Storage Foundations TestDocument19 pagesRomelos Siwalette - SAN and Storage Foundations TestFIboy SEnNo ratings yet

- 2.1.1 Flash Memory: 2.1.2 Comparison Between Floating 2.1 High-K Gate Stacks 2.1 High-K Gate StacksDocument4 pages2.1.1 Flash Memory: 2.1.2 Comparison Between Floating 2.1 High-K Gate Stacks 2.1 High-K Gate Stackstanuj_sharma1991No ratings yet

- DieSortingTool User Manual V4.18 20190116Document19 pagesDieSortingTool User Manual V4.18 20190116Douglas LeonNo ratings yet

- SN 936 NotesDocument20 pagesSN 936 Noteszeus balagtasNo ratings yet

- SSD Buying GuideDocument16 pagesSSD Buying Guidemob3No ratings yet

- Challenges of SSD Forensic Analysis: by Digital AssemblyDocument44 pagesChallenges of SSD Forensic Analysis: by Digital AssemblyMohd Asri XSxNo ratings yet

- Introducing Intel® QLC 3D NAND Technology: Solution BriefDocument4 pagesIntroducing Intel® QLC 3D NAND Technology: Solution BriefKRNo ratings yet

- MOSFET Chapter - 6Document51 pagesMOSFET Chapter - 6田佳生No ratings yet