Professional Documents

Culture Documents

Optimization of Power Consumption in VLSI Circuit

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Optimization of Power Consumption in VLSI Circuit

Copyright:

Available Formats

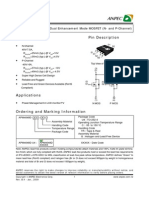

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE)

e-ISSN: 2278-1676,p-ISSN: 2320-3331, Volume 9, Issue 2 Ver. III (Mar Apr. 2014), PP 62-66

www.iosrjournals.org

www.iosrjournals.org 62 | Page

Optimization of Power Consumption in VLSI Circuit

Mr. Praveen Kumar Gupta

1

, Jagdeep Kaliraman

2

1

Associate Professor CSE Deptt. LU (Faridabad)

2

A P, ECE Deptt. ACEM (Faridabad)

Abstract: Increasing speed and complexity of design gives a significant increase in power consumption in VLSI

chips. Speed, power consumption and space are major issues in VLSI circuit. To meet these challenges there are

certain design techniques which are used to reduce power. Optimization of power can be done by considering

various components such as transistor sizing, voltage scaling, variable V

DD

, multiple threshold voltages, voltage

islands, power gating, long channel transistor, stacking & parking states and logic styles etc. Power

consumption in VLSI circuit is data dependent. In this paper different design methods are tested to optimize the

power. It is found that algorithm based design reduces gate switching activity that results reduction of power in

multiplier circuit.

Keyword: Transistor sizing, voltage scaling, variable V

DD

, multiple threshold voltages, voltage islands, long

channel transistor, stacking & parking states, logic styles, Genetic algorithm, Booth multiplication

I. Introduction

Reduction in power dissipation is an important design issue in VLSI circuits. The design parameters

have major effect on the overall performance of the system. On the basis of component used and their function

different optimization techniques can be used. For example in case of multiplier power consumption depends

upon data. This is because switching contributes to more power consumption. This can be optimized by using

various gate combinations. Gate switching can be reduced by using algoritms. For example of in case of

multiplier design method Booth algorithm as well as modified Booth algorithm can be used for efficient

multiplication. In this paper various approaches are used for power consumption eg. transistor sizing, voltage

scaling, variable V

DD

, multiple threshold voltages, voltage islands, long channel transistor, stacking& parking

states, logic styles, Genetic algorithm, Booth multiplication etc.

This paper is divided into five sections. First section is of introduction. Second section is about

preliminary studies. Third section includes different design methods and their testing. Fourth section is of

comparison with discussion. Finally, fifth section is conclusion of the work reported here.

II. Preliminaries

2.1 Power Dissipation

In case of VLSI circuits power dissipation is of two types i.e. static power dissipation and dynamic

power dissipation. This is shown as under:-

1. Static Power Dissipation

2. Dynamic Power Dissipiation

Static power dissipation is due to three major factors as leakage current, sub threshold current of

transistors and tunnelling effect of current. So optimization can be achieved by concentrating all these design

issues. As we know that MOS transistor has two P-N junctions: one is between source and drain and other is

between drain and source. When source substrate junction or drain substrate junction is reversed biased. The

leakage current flows through reverse biased P-N junctions. Generally this leakage current is very small in

magnitude so we ignore this current.

Leakage current is temperature dependent. This is because leakage current is caused by thermally

generated carriers. With increase in temperature, leakage current increases. According to a survey it is found

that it becomes double for every 10

0

C rise in temperature. From this it is clear that temperature of a circuit must

be controlled at any cost.

1.1 Sub threshold current of transistors

At VGS = V

T

surface is said to be inverted. In this condition there is strong inversion and conduction

takes place afterwards. But practically V

GS

< V

T

. MOS transistor is under sub threshold or weak inversion

conduction. This current is equally small in magnitude and rises exponentially. This current flows from drain to

source. It is observed at V

GS

=0.

Optimization of Power Consumption in VLSI Circuit

www.iosrjournals.org 63 | Page

If V

T

is nearly zero volt. Then threshold leakage current will be more. From this it is clear that if

threshold voltage is less leakage current will be more. Hence (PD)

static

will also be more. The threshold voltage

has to keep high.

As ( P

D

)

static

=P(t) = i

DD

(t) V

DD

Here i

DD

(t) is the leakage current or static current and V

DD

is supply voltage. From this it is clear that if leakage

current increases, then static power increases. Hence threshold voltage represents a trade off between

performance and static power dissipiation.

2.2 Tunnelling Current Effect

As gate oxide material is SiO

2

and SiO

2

is very good dielectric. The leakage current through this good

dielectric is very low. But if the thickness of dielectric is very less. Then electrons can tunnel through this

dielectric. If the thickness of dielectric decreases tunnelling effect increases.

2.3 Dynamic Power Dissipiation

Dynamic power dissipiation occurs in charging and discharging of capacitive loads. Let C

L

is the

capacitive load. If this capacitive load is switched between ground and V

DD

and switching frequency is taken as

(f)

switching

then charging of load taken takes place for T (f)

switching

time and discharging also takes place for same

time, T being the time interval.

During charging current flows from V

DD

to C

L

and during discharging current flows from C

L

to V

DD

.

Total charge transferred from positive supply rail (V

DD

) to negative supply rail (ground) during charging and

discharging cycle will be:-

Q= C

L

V

DD

So (P

D

)

Dynamic

=

DD

(t) V

DD

dt =

DD

(t) dt

=

V

DD

[ T(f)

switching

C

L

V

DD

]

= C

L

(f)

switching

(P

D

)

Total

= (PD)

switching

+ (P

D

)

dynamic

Usually (PD)

Total

can be ignored but high sub threshold current if exist, then it cannot be ignored. But (P

D

)

dynamic

is far greater than (PD)

static

hence it cannot be ignored.

At this short span of time, rail to rail current flows and causes power dissipiation which can not be avoided.

Table 1

Dynamic power dissipiation affects the battery when the device is in active mode but static power

battery life even when the device is in sleep mode.

Power Dissipation Estimation

In all logic circuits power consumption is related to information transfer and each circuit have inherent

requirement of information transfer. Let R is transfer rate requirement for a given architecture. The lower bound

of this rate may be determined which can be used for power dissipiation estimation. The different architecture

can perform same function but may have different information transfer rate and channel capacity. The channel

capacity can be given as under:-

Here SNR stands for signal to noise ratio. For any transfer, capacity should be greater than or equal to

R. The overall power in digital circuit is a function of signal power, temperature and semiconducting property

etc. However power dissipiation is mainly due to ground bounce. The lower bound of power dissipiation can be

calculated using information transfer capacity of channel. Let R be the required information transfer rate, W is

the channel bandwidth & C is the channel capacity. Lower bound of power dissipiation can be given as:-

III. Design methods for optimisation

3.1 Power Optimization as Data dependent

Complexity of data contributes to switching activity in the circuit. With the use of efficient algorithm

design component of circuit can be reduced. By the application of simulation to standard design and comparing

Sources to bear power dissipiation

Air cooled system

Heat sinks

Liquid cooling

Optimization of Power Consumption in VLSI Circuit

www.iosrjournals.org 64 | Page

it with optimization better design component can be found. Gate switching for all initial states and all inputs can

be simulated to analyse power consumption. Data dependency is helpful in gate design complexity. Ordering of

gate inputs affect both power and delay. Prasad [1] has described methods to optimize the power and/or delay of

logic gates based on transistor reordering. So, considerable improvements in power and delay can be obtained

by proper ordering of transistors. For instance, late arriving signals can be placed closer to the output to

minimize gate propagation delay. Another approach to reduce power is to consider the size of gate, which has

significant impact on circuit delay and power dissipation. By increasing the size of transistors in a given gate,

delay of the gate can be decreased but in contrast, power dissipated in the gate and fabrication space increases.

Therefore, an optimum balance can be achieved by sizing of transistors appropriately. A method is to compute

the slack at each gate in the circuit, where the slack of a gate corresponds to how much the gate can be slowed

down without affecting the critical delay of the circuit. Alternatively, in different sub circuits, where slack is

greater than zero are utilized and the size of the transistors is reduced until the slack becomes zero, or the

transistors attain a minimum size.

Combinational Gate Level Design

In gate level design of circuit, different combination of logical gates may different combination of

logical gates may produce same circuit output but different value of power consumption. Path balancing,

factorization and dont care optimization may be utilized to optimize power consumption. Path balancing can be

achieved by avoiding delay at each input gate. Genetic Algorithm can be used to determine different

combination of gates and power consumption can be formulated by devising Fitness Function. Coello [3] has

proposed design of combinational logic circuit based on Genetic Algorithm.

By defining chromosome development schemes of various combinations of logic circuit can be

developed using cross over and mutation. This approach is more efficient than human designer as various

constraint of design circuit can be devised subject to fitness function. Genetic Algorithm can reduce number of

gates, which consequently reduce power consumption; as the work of Coello [2], shows on 2-bit adder and 2-bit

multiplier with a particular cardinality that 56% reduction in number of gates for the circuit can be achieved.

IV. Comparison and discussion

Number of Gates versus power saving in CMOS based on ISCAS-89 benchmark circuits. [8]

Table 2. Power reduction versus Speed Loss

Optimization of Power Consumption in VLSI Circuit

www.iosrjournals.org 65 | Page

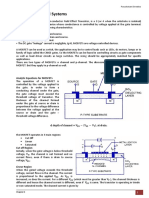

For instance, a modular approach as shown below in Fig. 1 is proposed to adopt appropriate optimization

technique considering different possibilities in multiplier design.

Figure1. Modular approach for multiplier design

V. Conclusion

It is found that data complexity and various combination of gate level digital circuit has considerable

impact in power dissipiation. Besides, this physical design can be optimized by using Genetic algorithm by

analysing the placement option. This is subjected to optimum space allocation. Similarly selection of Booth

algorithm may reduce power consumption of data complexity. It is found that in multiplier circuit Modified

Booth Algorithm reduces power consumption as compared to other methods of multiplication.

References

[1] S. C. Prasad and K. Roy, Circuit Optimization for Minimization of Power Consumption Under Delay Constraint. In Proceedings

of the Intl Workshop on Low Power Design, pages 1520, April 1994.

[2] Coello, Carlos A., Christiansen, Alan D. & Hernndez Aguirre, Using Genetic Algorithms to Design Combinational Logic

Circuits. ANNIE'96. Intelligent Engineering through Artificial Neural Networks, Volume 6. Smart Engineering Systems: Neural

Networks, Fuzzy Logic and Evolutionary Programming. Edited by Cihan H. Dagli, Metin Akay, C. L. Philip Chen, Benito R.

Fernandez and Joydeep Ghosh. pp 391-396. November, 1996.

[3] Coello, Carlos Artemio Coello. An Empirical Study of Evolutionary Techniques for Multi-objective Optimization in Engineering

Design. Ph.D. Dissertation, Department of Computer Science, Tulane University, New Orleans, LA, 1996.

[4] H. J. M. Veendrick, Short-circuit dissipation of static CMOS circuit and its impact on the design of buffer circuits, IEEE J. Solid-

State Circuits, Vol. 19, Aug 1984, pp. 468-473.

[5] Charles H. Bennett, Notes on Landauers Principle, Reversible Computation and Maxwells Demon, Studies in History and

Philosophy of Modern Physics, v. 34, pp. 501-510, 2003

[6] C.H. Bennett, The Thermodynamics of Computation a Review Internat. J. Theoret. Phys. 21, pp. 905-940 (1982).

[7] L. Benini, M. Favalli, and B. Ricco, Analysis of hazard contribution to power dissipation in CMOS ICs. In Proceedings of the

1994 International Workshop on Low Power Design, pp 27-32, April 1994.

Optimization of Power Consumption in VLSI Circuit

www.iosrjournals.org 66 | Page

[8] Vaughn Betz and Jonathan Rose, Circuit Design, Transistor Sizing and Wire Layout of FPGA Interconnect, IEEE Custom

Integrated Circuits Conference, 1999

[9] Boemo, E., Gonzalez de Rivera, G., Lopez-Buedo, S., Meneses, J., Some R.W. Allen. Addison-Wesley, 1996.

[10] Alain Guyot and Slim Abou-Samra, Low Power CMOS Digital Design, In proc. Of International Conference on

Microelectronics 1998 (ICM98), Monastir, Tunisia, December 1998

[11] R. Landauer, Irreversibility and Heat Generation in the Computing Process, IBM Journal of Research and Development, Vol 5,

pp. 261-269, 1961

[12] P. Landman, Low-Power Architectural Design Methodologies, Ph. D. Thesis, Electronic Research Laboratory, university of

California, Berkeley, August 1994

[13] Fei Li, Deming Chen, Lei He, Jason Cong: Architecture evaluation for power efficient FPGAs, Proc. Of Int. Symp on Field

Programmable Gate Arrays, 2003, pp. 175184

[14] F. N. Najm and M. G. Xakellis, Statistical estimation of the switching activity in VLSI circuits, VLSI Design, vol. 7, no. 3, pp.

243-254, 1998.

[15] M. Pedram, "Power estimation and optimization at the logic level," Int'l Journal of High Speed Electronics and Systems, Vol. 5, No.

2 (1994), pp. 179-202.

[16] Andrs David Garca Garca, Etude sur lEstimation et lOptimisation de la Consommation de puissance, PhD Thesis, lEcole

Nationale Suprieure des Tlcommunications, Paris, 2000.

[17] Alain Guyot and Slim Abou-Samra, Low Power CMOS Digital Design, In proc. Of International Conference on

Microelectronics 1998 (ICM98), Monastir, Tunisia, December 1998.

[18] P. Schneider and S. Krishnamoorthy. Effects of correlations on accuracy of power analysis - an experimental study, International

Symposium on Low Power Electronics and Design, Monterey, California, United States, 1996, pp. 113-116.

[19] Jan M. Rabaey and Massoud Pedram. Low power design methodologies. Boston, Kluwer Academic, 1996.

[20] Kara K.W. Poon, Steven J.E. Wilton, and A. Yan, A Detailed Power Model for Field-Programmable Gate Arrays, ACM

Transactions on Design Automation of Electronic Systems (TODAES), vol. 10, issue 2, pp. 279-302, April 2005.

[21] M. Pedram, Design technologies for Low Power VLSI, In Encyclopedia of Computer Science and Technology, Vo. 36, Marcel

Dekker, Inc., 1997, pp. 73- 96.

[22] F. N. Najm and M. G. Xakellis, Statistical estimation of the switching activity in VLSI circuits, VLSI Design, vol. 7, no. 3, pp.

243-254, 1998.

[23] Fei Li, Deming Chen, Lei He, Jason Cong: Architecture evaluation for power efficient FPGAs, Proc. Of Int. Symp on Field

Programmable Gate Arrays, 2003, pp. 175184

[24] P. Landman, Low-Power Architectural Design Methodologies, Ph. D. Thesis, Electronic Research Laboratory, University of

California, Berkeley, 1994.

[25] R. Landauer, Irreversibility and Heat Generation in the Computing Process, IBM Journal of Research and Development, Vol 5, N

3, pp. 261-269, 1961.

[26] James Kao, Siva Narendra, Anantha Chandrakasan, Sub threshold leakage modeling and reduction techniques, In proc. of the

2002 IEEE/ACM international conference on Computer-Aided Design, pp. 141-148, 2002.

[27] Vaughn Betz and Jonathan Rose, Circuit Design, Transistor Sizing and Wire Layout of FPGA Interconnect, IEEE Custom

Integrated Circuits Conf., 1999.

[28] Charles H. Bennett, Notes on Landauers Principle, Reversible Computation and Maxwells Demon, Studies in History and

Philosophy of Modern Physics, v. 34, pp. 501-510, 2003.

[29] Boemo, E., Gonzalez de Rivera, G., Lopez-Buedo, S., Meneses, J., Some Notes on Power Management on FPGAs, LNCS, No.

975, Springer-Verlag, Berlin, pp 149-157, 1995.

You might also like

- Project Based Learning Tools Development On Salt Hydrolysis Materials Through Scientific ApproachDocument5 pagesProject Based Learning Tools Development On Salt Hydrolysis Materials Through Scientific ApproachInternational Organization of Scientific Research (IOSR)No ratings yet

- Effects of Formative Assessment On Mathematics Test Anxiety and Performance of Senior Secondary School Students in Jos, NigeriaDocument10 pagesEffects of Formative Assessment On Mathematics Test Anxiety and Performance of Senior Secondary School Students in Jos, NigeriaInternational Organization of Scientific Research (IOSR)100% (1)

- Philosophical Analysis of The Theories of Punishment in The Context of Nigerian Educational SystemDocument6 pagesPhilosophical Analysis of The Theories of Punishment in The Context of Nigerian Educational SystemInternational Organization of Scientific Research (IOSR)No ratings yet

- The Effect of Instructional Methods and Locus of Control On Students' Speaking Ability (An Experimental Study in State Senior High School 01, Cibinong Bogor, West Java)Document11 pagesThe Effect of Instructional Methods and Locus of Control On Students' Speaking Ability (An Experimental Study in State Senior High School 01, Cibinong Bogor, West Java)International Organization of Scientific Research (IOSR)No ratings yet

- Necessary Evils of Private Tuition: A Case StudyDocument6 pagesNecessary Evils of Private Tuition: A Case StudyInternational Organization of Scientific Research (IOSR)No ratings yet

- Study The Changes in Al-Ahwaz Marshal Using Principal Component Analysis and Classification TechniqueDocument9 pagesStudy The Changes in Al-Ahwaz Marshal Using Principal Component Analysis and Classification TechniqueInternational Organization of Scientific Research (IOSR)No ratings yet

- Geohydrological Study of Weathered Basement Aquifers in Oban Massif and Environs Southeastern Nigeria: Using Remote Sensing and Geographic Information System TechniquesDocument14 pagesGeohydrological Study of Weathered Basement Aquifers in Oban Massif and Environs Southeastern Nigeria: Using Remote Sensing and Geographic Information System TechniquesInternational Organization of Scientific Research (IOSR)No ratings yet

- Youth Entrepreneurship: Opportunities and Challenges in IndiaDocument5 pagesYouth Entrepreneurship: Opportunities and Challenges in IndiaInternational Organization of Scientific Research (IOSR)100% (1)

- Students' Perceptions of Grammar Teaching and Learning in English Language Classrooms in LibyaDocument6 pagesStudents' Perceptions of Grammar Teaching and Learning in English Language Classrooms in LibyaInternational Organization of Scientific Research (IOSR)No ratings yet

- Development of Dacum As Identification Technique On Job Competence Based-Curriculum in High Vocational EducationDocument5 pagesDevelopment of Dacum As Identification Technique On Job Competence Based-Curriculum in High Vocational EducationInternational Organization of Scientific Research (IOSR)No ratings yet

- Child Mortality Among Teenage Mothers in OJU MetropolisDocument6 pagesChild Mortality Among Teenage Mothers in OJU MetropolisInternational Organization of Scientific Research (IOSR)No ratings yet

- Factors Affecting Success of Construction ProjectDocument10 pagesFactors Affecting Success of Construction ProjectInternational Organization of Scientific Research (IOSR)No ratings yet

- Enhancing Pupils' Knowledge of Mathematical Concepts Through Game and PoemDocument7 pagesEnhancing Pupils' Knowledge of Mathematical Concepts Through Game and PoemInternational Organization of Scientific Research (IOSR)No ratings yet

- Need of Non - Technical Content in Engineering EducationDocument3 pagesNeed of Non - Technical Content in Engineering EducationInternational Organization of Scientific Research (IOSR)No ratings yet

- Lipoproteins and Lipid Peroxidation in Thyroid DisordersDocument6 pagesLipoproteins and Lipid Peroxidation in Thyroid DisordersInternational Organization of Scientific Research (IOSR)No ratings yet

- Comparison of Psychological Variables Within Different Positions of Players of The State Junior Boys Ball Badminton Players of ManipurDocument4 pagesComparison of Psychological Variables Within Different Positions of Players of The State Junior Boys Ball Badminton Players of ManipurInternational Organization of Scientific Research (IOSR)No ratings yet

- Comparison of Selected Anthropometric and Physical Fitness Variables Between Offencive and Defencive Players of Kho-KhoDocument2 pagesComparison of Selected Anthropometric and Physical Fitness Variables Between Offencive and Defencive Players of Kho-KhoInternational Organization of Scientific Research (IOSR)No ratings yet

- Advancing Statistical Education Using Technology and Mobile DevicesDocument9 pagesAdvancing Statistical Education Using Technology and Mobile DevicesInternational Organization of Scientific Research (IOSR)No ratings yet

- Study of Effect of Rotor Speed, Combing-Roll Speed and Type of Recycled Waste On Rotor Yarn Quality Using Response Surface MethodologyDocument9 pagesStudy of Effect of Rotor Speed, Combing-Roll Speed and Type of Recycled Waste On Rotor Yarn Quality Using Response Surface MethodologyInternational Organization of Scientific Research (IOSR)No ratings yet

- Microencapsulation For Textile FinishingDocument4 pagesMicroencapsulation For Textile FinishingInternational Organization of Scientific Research (IOSR)No ratings yet

- Comparative Effect of Daily Administration of Allium Sativum and Allium Cepa Extracts On Alloxan Induced Diabetic RatsDocument6 pagesComparative Effect of Daily Administration of Allium Sativum and Allium Cepa Extracts On Alloxan Induced Diabetic RatsInternational Organization of Scientific Research (IOSR)No ratings yet

- Auxin Induced Germination and Plantlet Regeneration Via Rhizome Section Culture in Spiranthes Sinensis (Pers.) Ames: A Vulnerable Medicinal Orchid of Kashmir HimalayaDocument4 pagesAuxin Induced Germination and Plantlet Regeneration Via Rhizome Section Culture in Spiranthes Sinensis (Pers.) Ames: A Vulnerable Medicinal Orchid of Kashmir HimalayaInternational Organization of Scientific Research (IOSR)No ratings yet

- Core Components of The Metabolic Syndrome in Nonalcohlic Fatty Liver DiseaseDocument5 pagesCore Components of The Metabolic Syndrome in Nonalcohlic Fatty Liver DiseaseInternational Organization of Scientific Research (IOSR)No ratings yet

- Comparison of Explosive Strength Between Football and Volley Ball Players of Jamboni BlockDocument2 pagesComparison of Explosive Strength Between Football and Volley Ball Players of Jamboni BlockInternational Organization of Scientific Research (IOSR)No ratings yet

- Application of Xylanase Produced by Bacillus Megaterium in Saccharification, Juice Clarification and Oil Extraction From Jatropha Seed KernelDocument8 pagesApplication of Xylanase Produced by Bacillus Megaterium in Saccharification, Juice Clarification and Oil Extraction From Jatropha Seed KernelInternational Organization of Scientific Research (IOSR)No ratings yet

- A Review On Refrigerants, and Effects On Global Warming For Making Green EnvironmentDocument4 pagesA Review On Refrigerants, and Effects On Global Warming For Making Green EnvironmentInternational Organization of Scientific Research (IOSR)No ratings yet

- Investigation of Wear Loss in Aluminium Silicon Carbide Mica Hybrid Metal Matrix CompositeDocument5 pagesInvestigation of Wear Loss in Aluminium Silicon Carbide Mica Hybrid Metal Matrix CompositeInternational Organization of Scientific Research (IOSR)No ratings yet

- Parametric Optimization of Single Cylinder Diesel Engine For Specific Fuel Consumption Using Palm Seed Oil As A BlendDocument6 pagesParametric Optimization of Single Cylinder Diesel Engine For Specific Fuel Consumption Using Palm Seed Oil As A BlendInternational Organization of Scientific Research (IOSR)No ratings yet

- Research Analysis On Sustainability Opportunities and Challenges of Bio-Fuels Industry in IndiaDocument7 pagesResearch Analysis On Sustainability Opportunities and Challenges of Bio-Fuels Industry in IndiaInternational Organization of Scientific Research (IOSR)No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- EI2403 - VLSI Design 2 Marks With AnswersDocument23 pagesEI2403 - VLSI Design 2 Marks With AnswersAnand GvphNo ratings yet

- a拉扎维模拟CMOS集成电路第二版最新答案Document1,603 pagesa拉扎维模拟CMOS集成电路第二版最新答案就爱吃饭团No ratings yet

- Research Article: 9T Full Adder Design in Subthreshold RegionDocument5 pagesResearch Article: 9T Full Adder Design in Subthreshold Regiondeepa_sinha_3No ratings yet

- Pedot Pss Hall EffectDocument9 pagesPedot Pss Hall EffectMengfang Li100% (1)

- Ald 8100 XX FamilyDocument17 pagesAld 8100 XX FamilyNor MenaNo ratings yet

- CmosDocument207 pagesCmossuneeldvNo ratings yet

- FDS6930 PDFDocument5 pagesFDS6930 PDFTut MorisNo ratings yet

- EE477L HW1 Sp24Document4 pagesEE477L HW1 Sp24Archit SethiNo ratings yet

- SMD 357Document6 pagesSMD 357Marcoantonio AntonioNo ratings yet

- Lectures Chpter 4 MOSFET of Sedra Semith Micro Electronic CircuitsDocument164 pagesLectures Chpter 4 MOSFET of Sedra Semith Micro Electronic CircuitsShafiul Huda ErazNo ratings yet

- Wearable Technologies PDFDocument162 pagesWearable Technologies PDFManu Weird100% (1)

- Unit 3: MOS Electrostatics: The Mobile Charge vs. Gate VoltageDocument22 pagesUnit 3: MOS Electrostatics: The Mobile Charge vs. Gate VoltagealNo ratings yet

- Temperature Effects in SemiconductorsDocument20 pagesTemperature Effects in Semiconductorsohenri100No ratings yet

- Martin Held DissertationDocument252 pagesMartin Held DissertationJaimeNo ratings yet

- Apm 4048 DDocument13 pagesApm 4048 DJuan CoronelNo ratings yet

- ECE315 / ECE515: - MOSFET - Second Order Effect (Contd.) - Steps For DC Analysis of MOSFET CircuitsDocument27 pagesECE315 / ECE515: - MOSFET - Second Order Effect (Contd.) - Steps For DC Analysis of MOSFET CircuitsChánh NguyễnNo ratings yet

- MosfetbasicsDocument94 pagesMosfetbasicsBhargav GoudNo ratings yet

- 0.18um Modular Triple Self-Aligned Embedded Split-Gate Flash MemoryDocument2 pages0.18um Modular Triple Self-Aligned Embedded Split-Gate Flash MemoryYohanes ErwinNo ratings yet

- Vijay BTP Report EndSemDocument46 pagesVijay BTP Report EndSemVijay AjayNo ratings yet

- Unit 3Document82 pagesUnit 3gauravlodhi983No ratings yet

- LPVLSI Unit 3 NotesDocument49 pagesLPVLSI Unit 3 NotesSai Sreeja100% (1)

- Homework 2Document12 pagesHomework 2janifer lucyNo ratings yet

- Dang 2019 Jpn. J. Appl. Phys. 58 090606Document11 pagesDang 2019 Jpn. J. Appl. Phys. 58 090606nhalder1No ratings yet

- Unit 2 - Fabrication - VinayDocument37 pagesUnit 2 - Fabrication - VinayApoorvaNo ratings yet

- A Novel TFET StructureDocument23 pagesA Novel TFET StructureRohith ChowdaryNo ratings yet

- Chapter 6 Control SystemsDocument7 pagesChapter 6 Control SystemspurushresthaNo ratings yet

- Fabrication and Characterization of Organic Field-Effect TransistorsDocument11 pagesFabrication and Characterization of Organic Field-Effect TransistorsEbru CoşkunNo ratings yet

- Microwind3.1 Design Rules For 45NM Cmos TechnologyDocument44 pagesMicrowind3.1 Design Rules For 45NM Cmos TechnologyOkta_BSD100% (1)

- 1st PaperDocument11 pages1st Paperaruna kumariNo ratings yet

- Development of Algan/Gan High Electron Mobility Transistors (Hemts) On Diamond SubstratesDocument76 pagesDevelopment of Algan/Gan High Electron Mobility Transistors (Hemts) On Diamond Substrateszinouu113113No ratings yet