Professional Documents

Culture Documents

Libro Principios Digitales Roger L Tokheim 1p PDF

Uploaded by

jkl012Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Libro Principios Digitales Roger L Tokheim 1p PDF

Uploaded by

jkl012Copyright:

Available Formats

SERIE DE COMPENDIOS SCHA UM

TEOR~A Y PROBLEMAS

de

PRINCIPIOS DIGITALES

ROGER L. TOKHEIM, M. S.

Jefe del Departomento de Educocibn Industrial,

Henry Sibley High School ,

Mendoto Heights, Minnesota

Traduccibn:

Ra61 Varela G.

Quimico

Profesor de Computaci6n y ProgromacMn

en la U. N.A.M.

Maria Pozzi de del Conde

Matemdtica

hvestigadora del Coiegio de Mkxico

Revisibn Ttcnica:

Jose Cen Zubieta

hgeniero Mednico Electricista, U.N.A.M.

Maestro en Ciencios de Operaciones

New York University

Jefe de lo Unidad de C6mputo del Colegio de Mixico

M~ X I CO ROC~ T A RUENOS AlRES <;UATEMAI,A I.ISBOA MADRID

\lJF.VA YOHK PANAMA SAh JUAN SANTIA<;O s ~ O PAUI,O AUCKI,ANI)

HAMAUR(;O .IOHANNESBURGO 1.ONDRES MONTREAL NUEVA DEI.HI

I ' , AR~T TAN FRANCISCO SINGAPUR ST. 1,OUIS SIDNEY TOKlO TORONTO .

?, -

PRINCIPIOS DIGITALES

Prohibida la reproduccl6n total o parcial de esta obra,

por cualquier medio, sln autorizaci6n escrlta del editor.

DERECHOS RESERVADOS @I 1982, respecto a la primera edlcldn en espanoi por

LIBROS McGRAW.HILL DE MEXICO, S. A, de C. V.

Atlacomulco 499.501, Fracc. Industrial San Andres Atoto

53500 Naucalpan de JuArez, Edo. de Mexico

Miembro de la Cdmara Naclonal de l a lndustria Editorlal, Reg. Num. 465

ISBN 968-451.287-2

Traducido de la primera edici6n en ingl6s de

DIGITAL PRINCIPLES

Copyright C 1960, by McGraw-HIII Book Co., U. S. A.

ISBN 0.07-064928-6

2345678901 P.E.-82 8012356794

lmpreso en Mexico Printed In Mexlco

Esta obra ee termin6 en febrero de 1984

en LltogrOfica Ingramex, S, A.,

Centeno 162,

Col. GranJas Eemeralda

Delegacldn lztapalapa

09610 MBxico, D. F.

Se tiraron 3 000 ejemplares

Prefacio

La electrbnica digital es una tecnologia en desarrollo. Los circuitos digitales se

emplean ahora en todo tipo de productos; desde juguetes para niflos hasta computa-

doras, desde sistemas de telemetria en satklites hasta calculadoras manuales. Debido

principalmente al desarrollo de 10s circuitos integrados (CI) de bajo costo, 10s cir-

cuitos digitales aparecen actualmente en casi todos 10s productos electrbnicos y se es-

pera que esta tendencia continue.

Principios digitales de la serie Schaum facilita la informacibn necesaria para

ayudar al lector a resolver aquellos problemas digitales con 10s que uno puede en-

contrarse como estudiante, tecnico, ingeniero o aficionado. Debido a que son nece-

sarios 10s principios del tema, la filosofia Schaum's se dedica a mostrar al estudiante

cbmo aplicar 10s principios de la electrbnica digital. Este libro contiene mas de 700

problemas prhcticos, muchos de ellos con soluciones detalladas.

Los temas tratados en este libro fueron seleccionados cuidadosamente para que

coincidieran con 10s cursos que se imparten a nivel preparatoria, vocational o es-

cuela ttrcnica*. Se analizaron ocho de 10s libros de texto y manuales de laboratorio

que se utilizan mhs en el campo de la electr6nica digital. Los temas y problemas que

se incluyen en este libro son similares a 10s que se encuentran con mas frecuencia en

10s libros comunes.

Principios digitales de la Serie Schaum, empieza con sistemas numericos y cd-

digos digitales y continha con compuertas 16gicas y circuitos de Ibgica combinatoria.

Luego trata basculadores y 16gica secuencial siguiendo con contadores, registros de

corrimiento, circuitos aritmdticos y, finalmente, dispositivos de interfase. El libro

hace hincapie en el uso de C1 estandar en la industria para que el lector se familiari-

ce con 10s aspectos de hardware de la electrbnica digital.

Afortunadamente, si se comprenden'algunos principios, la electrbnica digital

no es diflcil. La electrbnica digital es interesante por las fantasticas tareas que estos

circuitos pueden realizar. Usando sblo unos cuantos Cl digitales, pueden diseaarse

y construirse proyectos que contengan el equivalente de miles de transistores.

Deseo agradecer a mis alumnos de la Henry Sibley High School por su aliento.

TambiCn quisiera expresar mi aprecio a mi familia, Dan, Marshall y Caroline, por su

apoyo y paciencia.

'N. del T. En el sistema educational de E.U.A.

ROGER L. TOKHEIM tiene el grado en Educacibn de Artes In-

dustriales del St. Cloud State College y de la Universidad de Wisconsin. Es

autor del libro Digital Electronics (McGraw-Hill, 1979) y de abundante ma-

terial educacional de ciencias e industria. Como un experimentado educa-

dor en 10s niveles adulto y secundario, es actualmente el jefe de Educacibn

Industrial de Henry Sibley High School, Mendota Heights, Minnesota.

Numeros u tilizados en electronics digital

Todos conocemos el sistema de numeros decirnales, que utiliza 10s simbolos 0, 1, 2, 3, 4, 5, 6, 7, 8, y 9.

El sistema decimal tambiCn tiene un valor de posicibn, caracteristico. ConsidCrese el numero decimal

- 238. El 8 esth en la posici6n o lugar de las unidades, el 3 en el de las decenas, por lo tanto, las tres dece-

nas denotan 30 unidades; el 2 est4 en el de las centenas, o sea, 200 unidades. Sumando 200 + 30 + 8, el

numero decimal total que se obtiene es 238. El sistema decimal tambikn se llama sistema de base 10, ya

que tiene diez simbolos diferentes. Asimismo se dice que este sistema tiene rddix 10. Los tCrminos base y

rhdix significan exactamente lo mismo.

Los ntimeros binarios (base 2) se usan ampliamente en circuitos digitales, 10s nhmeros octales (base

8) y hexadecimales (base 16), aunque en menor grado, tarnbikn se utilizan en sistemas digitales.

Todos estos sistemas mencionados (decimal, binario, octal y hexadecimal) pueden usarse para con-

tar, y todos tienen el valor de posici6n caracteristico.

El sistema de nhmeros binarios s6lo utiliza dos simbolos

_ (0,l); se dice que tiene radix 2 y comunmente se llama

sistema de numeros de base 2. Cada dlgito binario se de-

nomina bit.

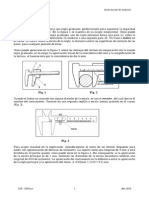

La forma de contar en binario se muestra en la

figura 1-1. El ndmero binario se indica a la derecha, con

su decimal equivalente a la izquierda. N6tese que el bit

menos signifcativo (bms) estA en el lugar de las unida-

des; en otras palabras, si el 1 aparece en la columna de-

recha, se suma un 1 a la cuenta binaria; el segundo lugar

de derecha a izquierda es el lugar de 10s 2(doses); el 1

que aparece en esta columna (como en el renglbn del 2

decimal) significa que se suma un 2 a la cuenta. La figu-

ra 1-1 es otro ejemplo de tres valores de posici6n bina-

rios (el de 10s 4 (cuatros), 10s 8 (ochos) y 10s 16 (dieci-

kises)). Notese que cada valor de posicion es una potencia

de 2 mayor que el de la derecha. De hecho, el lugar de las

unidades es 2O, el de 10s 2 (doses) 2l, el de 10s 4 (cuatros)

22, el de 10s 8 (ochos) 2' y el de 10s 16 (dieciseises) 24. En

electrbnica digital se acostumbra memorizar por lo me-

nos la zucesibn de la cuenta binaria del0000 al 11 11 (se

dice uno, uno, uno, uno), o sea, hasta el 15 decimal.

ConsidCrese el ntimero de la figura 1-20, donde se

enseAa cbmo convertir el 1001 1 (se dice uno, cero, cero,

uno, uno) a su decimal equivalente. Nbtese que para ca-

da bit del ntimero binario, el decimal equivalente para

I

1 CO"lC0

binario

I I

Flg 1-1 Conteo binario y decimal

conteo

decimal

0

I

7

-

3

4

5

6

7

8

9

10

I I

12

13

14

15

16

17

18

19

I

16 8 4 2 1

0

I

I

I 0

1 I

1 0 0

1 0 1

1 1 0

I l l

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

l I 0 0

1 1 0 1

1 1 1 0

1 1 1 1

1 0 0 0 0

1 0 0 0 1

1 0 0 1 0

1 0 0 1 1

Z N~IMEROS UTILIZAEQS EN ELECTR~NI CA DIGITAL [CAP. I -

ese valor de posic~bn, esth escrito abajo. Para obtener este decimal, se suman 10s ndmeros decimales (16

-

+ 2 + 1 = 19) y se concluye entonces que el 10011 binario es igual a1 I9 decimal.

Considkrese el ndmero binario 101 110 de la figura 1-2b. Siguiendo el mismo procedimiento, cada

bit del ndmero binario genera un decimal equivalente para ese valor de posicibn. El bit mcis signifcativo

(EMS) del ndmero binario es igual a 32, y si a tste le sumamos 8 + 4 + 2, da como resultado un total de

-

46, por lo que el 101 110 binario es equivalente a1 46 decimal. La figura 1-2b identifica tambien a1 punto

binario (similar a1 punto decimal en ndmeros decimales). Generalmente se omite el punto binario a1 tra-

bajar con binarios enteros.

Binario

Decimal

Polencias de 2

Valor de posicibn

1 0 0 I I . -Punto binario

16 + 2 + I = I 9

a) Conversibn de binario a decimal

2' 7 3 2' 2 1 2O

16 8 4 2 1

Binario I 0 1 1 I 0 . t- Punto binario

Potencias de 2

Valor de posicibn

Decimal 32 + 8 + 4 + 2 = 46

b) Conversibn de binario a decimal

2 24 2" 2> 2 ' 2O

32 16 8 4 2 I

c) Resumen de conversiones y uso de subindices para indicar la base del nbmero

Fig 1-2

i Cbmo convertir numeros fraccionarios? La figura 1-3 es un ejemplo de la conversi6n del ndmero

binario 11 10.101 a su decimal equivalente. Los valores de posici6n se indican en la parte superior; hay

que notar el valor de cada lugar a la derecha del punto binario. El procedimiento para efectuar esta con-

versi6n es el mismo que se emplea para con 10s ndmeros enteros: se suma el valor de posici6n de cada bit

para obtener el ndmero decimal. En este problema 8 + 4 + 2 + 0.5 + 0.125 = 14.625 decimal.

Binario 1 I I 0 . I 0 1

Decimal 8 + 4 + 2 + 0.5 + 0.125 = 14.625

Potencias de 2

Valor de posicibn

Fig 1-3 Conversi6n de binario a decimal

2' 2' 2 ' 2O 1!2l 112'. 1/2=

8 4 2 1 0.5 0.25 0.125

iCuhl es el valor del ndmero 1 I l ? Podria ser ciento once en decimal, o bien uno, uno, uno en bina-

rio. Algunos libros utilizan el sistema que se muestra en la figura 1-2c para designar la base o radix de

una cantidad. En este caso, 1001 1 es de base 2 como lo indica el subindice 2. El ndmero 19 esth en base

10 coma lo indica el subindice 10. La figura I-2c es un resumen de las conversiones binarias a decimales

de las figuras 1-2a y b.

- CAP.]] NilMEROSUTlLIZADOS EN ELEcTR~NI CA DIGITAL 3

Convitrtase el numero decimal 87 a nCmero binario. La figura 1-4 nos muestra un mttodo ade-

-

cuado para llevar a cab0 esta conversi6n: se divide el numero 87 entre 2 y se obtiene el cociente 43 y de

residuo I; este es importante y se escribe a la derecha, ademas es el bit menos significativo (bms), nume-

ro binario. El cociente (43) se transfiere como lo indica la flecha y pasa a ser el dividendo. De esta for-

-

ma, todos 10s cocientes se dividen entre 2, hasta que el ultimo sea 0 y el residuo sea 1, como en la dltima

linea de la figura 1-4. Casi a1 final de la figura se indica que el 87 decimal es igual al 10101 11 binario.

bmt

y con residuo I ----------

1

y con residuo 1

1 I

) con residuo

I ) ! 1

). con residuo ( : -------?

l ~ ~ l

y con residuo : -

y con residuo 0 - -- 1

BMS 1

y con residua I

1 I 1 I

<' , ( , = 1 0 I 0 I I I ,

- Fig 1-4 Conversibn de decimal a binario

Convitrtase el 0.375 decimal a numero binario. La figura I-5a ilustra un metodo de llevar a cab0

-

esta operaci6n. Hay que notar que el numero decimal (0.375) se multiplica por 2, dando como resulta-

do 0.75. El 0 del lugar de 10s enteros (lugar de las unidades) serB el siguiente bital punto binario. Enton-

ces el 0.75 se multiplica por 2, resultando 1.50. El acarreo del 1 a 10s enteros (lugar de las,unidades), sera

el siguiente bit a la derecha del.anterior, se multiplica entonces el 0.50 por 2 obteniendo como resultado

1.00. El acarreo del I al lugar de 10s enteros es el 1 final del numero binario, ya que el proceso de conver-

si6n termina cuando 'el producto es 1.00. En la figura 1-50 vemos c6mo convertir el 0.375 decimal a su

correspondiente 0.01 1 binario.

Fig 1-5 Conversiones de decimal fraccionario a binario

La figura I-5b muestra la conversi6n de10.84375 decimal a binario. Una vez mils hay que hacer hin-

capit en que 0.84375 se multiplica por 2. El entero de cada producto se escribe abajo, generando asi el

nhmero binario, y cuando el producto es igual a 1.00, se termina la conversi6n. En este problema se in-

-

dica c6mo convertir el 0.84375 decimal a1 0.1101 1 binario.

4 N~ MEROS UTILIZADOS EN ELECTR~NICA DIGITAL [CAP. I

Considerese el nurnero decimal 5.625. Para convertir este nhmero a binario se necesitan dos proce-

sos diferentes: la parte entera del nhmero (5) se procesa por divisi6n repetida como se ilustra en la parte

-

superior de la figura 1-6. De esta forma el 5 decimal se convierte en el 101 binario. La parte fraccionaria

del numero decimal (.625) se convierte a1 .I01 binario como se indica en la parte inferior de la figura 1-6.

Esta parte se convierte al binario .I01 mediante un proceso de multiplicaci6n repetida. En seguida se

combinan las 60s secciones entera y fraccionaria, resultando que el 5.625 decimal es igual a1 101.101

binario.

5 i 2 = 2 y con rcsiduo I

I 1

r--

2 t 2 = 1 y con residuo 0

I 1

1

1 i 2 = 0 y con residuo 1

I I

Fig 1-6 Conversibn de decimal a binario

PROBLEMAS RESUELTOS

1.1 El sistema binario de numeros es el sistema de base - y tiene rtidix .

Soluci6n:

El sisterna binario de numeros es el sistema de base 2 y tiene rhdix 2.

1.2 Al trabajar con numeros binarios, el termino bit significa

Soluci6n:

Bit significa dlgito binario.

1.3 ~ C b mo diria el numero 1001 en a) binario y b) decimal?

Soluci6n:

El numero 1001 se dice de la siguiente manera: a) uno, cero, cero, uno. b) mil uno.

1.4 El numero 1 1OI0 es un nhmero de base .

Soluci6n:

El numero 1 lolo es un numero de base 10, como lo indica el sublndice 10.

1.5 Escribir el numero de base 2, uno, uno, cero, cero, uno.

Solucibn:

11001,

1.6 Convertir 10s siguientes nlimeros binarios a sus decimales equivalentes:

a) 001100 c) 011100 e) 101010 g) 100001

b) OO~OI I 4 111100 n 111111 h) 111000

NOMEROS UTILIZADOS EN ELECTR~NICA DIGITAL

Solucibn:

Siguiendo el procedimiento de la figura 1-2 10s decimales equivalentes a 10s numeros binarios son:

a) 001 100,= 12,, c) 011100,=2810 e) 101010,=42,, g) 100a01,=3310

b) m1 1 , = 3 , , 4 1 1 1 i ~ , = a 0 , ~ n l i l i 1l , =a3, , h) 1ilooo, =56, ~

-

Solucihn:

Siguiendo el procedimiento de la figura 1-2, 11 11000.1 11 1, = 1935,,.

1.8 11100.0112 = - 10

-

Soluci6n:

Siguiendo el procedimiento de la figura 1-3, 11 100.01 1, = 28.375,,.

SoluclBn:

-

Siguiendo el procedimiento de la figura 1-3. 11001 1.1001 1, = 51.59375,,

-

Solucl6n:

Siguiendo el procedimiento de la figura 1-3, 1010101010.1, = 682.5,,

-

1.11 Convertir 10s siguientes numeros decimales a sus binarios equivalentes:

a) 64, b) 100, c) 111, 4 145, e) 255, 8 500

Solucibn:

-

Siguiendo el procedimiento de la figura 1-4, 10s binarios equivalentes a 10s numeros decimales son:

a) 64,, = 1000000, c) l l l l o=l l O1l l l , e) 255,, = 11111111,

b) 1001o= 11001W2 d) 145,,= 100100012 n 50010 = 1111101002

Solucibn:

-

Siguiendo el procedimienro de la figura 1-6. 34.75,, = 100010.11,

Siguiendo el procedimiento de la figura 1-6, 25.25,, = 11001.01,

-

1.14 27.1875,o = 2

Soluci6n:

Siguiendo el procedimiento de la figura 1-6, 27.1875,, = 1101 1.001 1,

- 1-3 NUMEROS OCTALES

El sistema octal es el de base 8, y 10s ocho simbolos que utiliza son 0, I , 2, 3, 4, 5, 6, y 7. La tabla de la fi-

gura 1-7 compara como se cuenta en 10s sistemas decimal, binario y octal. La utilidad del sistema octal

- radica en que posee un simbolo diferente para cada numero binario del 000 al 11 1.

NOMEROS UTILIZADOS EN ELEcTR~NICA DIGITAL

Fig 1-7 Forma de contar en los sistemas decimales, binario y octal

-

El sistema octal tambien utiliza el valor de posicibn. La figura 1-8a ensefla el valor de 10s cuatro pri-

meros lugares a la izquierda del punto octal. El digito menos significative (dms) es el que estA en el lugar

de las unidades, mientras que el lugar del 8' es igual a 8 y asi sucesivamente, por lo tanto, el valor o peso

-

de las posiciones 1, 8, 64, 512, etc.

Ndmero octal

Decimal

Potencias de 8

Valor de posici6n (en dccimales)

a) Valores dc posicibn en el sistema octal

8' 8' 8 ' 8' .+-

512 64 8 I

- Punto octal

b) Conversi6n dc octal a decimal

N~imero octal 2 4 5 7 8

Decimal

c) Conversibn de octal a decimal

Fig 1-8

Convikrtase el nhmero octal 123, a su decimal equivalente. La figura 1-86 ensefla el procedimiento.

Considere primer0 el lugar de las unidades; tres l(unos) es igual a 3, escrito abajo en la linea decimal.

Despues se considera el lugar de 10s 8(ochos); hay dos 8 por lo que 2 x 8 = 16, que se suma a13 de aba-

jo. Considere por ultimo el lugar de 10s 64, sblo hay un 64 que se suma finalmente al 16 y a13 (64 + 16

+ 3 = 83), obteniendo como resultado el 83 decimal, por lo que el octal 123 es igual al 83 decimal.

Convierrase el octal 2457, a nhmero decimal. La figura 1-8c muestra con detalle el procedimiento.

El valor de posicibn se multiplica por el digito en esa posicibn y se suman 10s productos. El resultado es.

que el octal 2457 es igual al 1327 decimal.

El procedimiento para convertir n~imeros decimales a octales es similar al que se utiliza para con-

vertir decimales a binarios. Convertir el decimal 1327 a octal. Este procedimiento se muestra en la figura

- CAP ..I] N~ MEROS UTlLlZADOS EN ELECTR~NI CA DIGITAL 7

-.

1-9. Prirnero el 1327 se divide entre 8, obteniendo como cociente 165 y residuo 7, que pasa a ser el digito

menos significativo del numero octal. El cociente (165) se transfiere (vCase la flecha de la figura 1-9) y se

convierte en el dividendo, Cste se divide entre 8 y se obtiene 20 de cociente y 5 de residuo, que se escribe

abajo como el siguiente digito del nhmero octal. La repeticibn del proceso de dividir entre 8 continua

-

hasta que el cociente sea 0 y el residuo desde I hasta 7, inclusive. En este problema el numero decimal

1327 es equivalente a1 2457 octal.

1327 + 8 = 165 y con residuo 7

I 1

..----J

165 t 8 = 20 y con residuo 5

+

20 + 8 = 7 y con residuo 4

2 t 8 = 0 y con residuo 2

1327,, = 2 4 5 78

Fig 1-9 Conversi6n de decimal a octal

Considere el numero octal 642-21. La figura 1-100 ensena un proceso sencillo para convertir este nu-

rnero octal a nurnero decimal. Cada valor de posici6n se rnultiplica por el digito de ese lugar, que ests.

-

escrito abajo. Se suman 10s 5 valores decirnales (384 + 32 + 2 + 0.25 + 0.015625 = 418.265625) obte-

niendo asi, el numero de base 10 equivalente.

Numero octal 6 4 7 2 1

Potencias de 8

Valor dc posicibn

Decimal

8 8 R0 l/R1 1:8'

64 8 I ,125 ,015625

a) Convcrsibn de octal fraccionario a decimal

418 + U = 52 yconreaiduo 2

I 1

+

52 + 8 = 6 y con rcsiduo 4

d

6 t 8 = 0 y corl residuo 6

418.26562510 = 6 4 2 . 2 Is

0.265 625 x 8 = 2.125

7-1

r---

0.125 x 8 = 1 . 0 0

I

b) Conversion de decimal fraccionario a octal

8 NOMEROS UTlLlZADOS EN ELECTR6NICA DIGITAL ICAP.1 -.

Para convertir el decimal 418.265 625 a octal se invierte el proceso, este se puede observar con de-

-

talle en la figura I-lob. El primer proceso es la divisi6n repetida entre 8; utilizando 10s residuos se genera

la parte entera del ndmero octal; por lo tanto, el decimal 418 es igual al 624 octal.

La parte fraccionaria del decimal se convierte a octal en la secci6n inferior de la figura 1-106, y se

lleva a cab0 por medio de repetidas multiplicaciones por 8. La parte entera de cada producto genera la

-

respuesta. El proceso termina cuando el producto de la multiplicaci6n es 0.00. Combinando el resultado

de las partes entera y fraccionaria se obtiene el nhmero octal 642.21,.

La utilidad del sistema octal, esta en su facilidad de conversi6n a binario. Considerese el numero oc-

-

tal532. Para efectuar esta conversi6n basta memorizar tan s6lo 10s primeros ocho numeros de la cuenta

binaria (000 - 11 1) y sus respectivos octales equivalentes, que se encuentran en la parte sombreada de la

tabla de la figura 1-7. La conversi6n del octal 532, a binario se observa en la figura 1-1 la. N6tese que ca-

da digito octal forma un grupo de tres digitos binarios.

-

a) Conversibn de octal a binar~o b) Conversibn de binario a octal

-

C) Conversibn de octal fraccionario a binario d) Conversibn de binario fraccionario a octal

Fig 1-11

-

La figura 1- l l b muestra otra conversi6n de octal a binario en donde el 74.61, se convierte a su

equivalente binario. N6tese que el punto octal pasa a ser el punto binario en el numero de base 2. Por lo

tanro, 74.61, es igual a1 11 1100.1 10001,.

Para convertir de binario a octal se invierte el proceso. La figura 1- l l c enseAa c6mo el binario

-

1 101 1100d100 se divide en grupos de rres bit cada uno, empezando en el punto binario. Cada grupo gene-

ra su digito octal equivalente, y asi se muestra en la figura 1-1 l c que el 1101 11000100, es igual a1 6704,.

ConviCrtase el binario 101 1.101 1 a su octal equivalente. Primero hay que dividir 10s bit binarios en -

grupos de tres, cada uno a partir del punt o binario. La figura 1-1 l d muestra c6mo dividir 10s bit bina-

rios en grupos de tres; despuks, cada grupo de 3 se traduce al digito octal correspondiente y el punto bi-

nario se transforma en el punto octal. La figura 1-1 l d ilustra c6mo el 101 1.101 1, es igual al 13.54,.

-.

PROBLEMAS RESUELTOS -.

1.15 El sistema octal se llama sistema de base

Soluciim:

El sisrema octal se llama sistema de base 8 .

1.16 Enumere 10s ocho simbolos urilizados en el sistema octal de numeros.

Solucinn:

Los ocho simbolos utilizados en el sistema octal son: 0, 1 , 2, 3, 4, 5 , 6 y 7

-. CAP.11

NUMEROS UTILIZADOS EN ELECTR6NICA DIGITAL

1.17 Conviertanse 10s siguientes numeros octales a sus decirnales equivalentes:

-

a) 42, b) 376, c) 1057, d) 11.11, e) 37.123

Solucion:

.-

Siguiendo el procedimiento de las figuras 1-8 y ~-IOU, 10s decimales equivalentes a estos nhmeros octa-

les son:

a) 42, = 34,, c) 1057, = 559,, e) 37.123, = 31.162,,

- b) 376, = 254,, d) 11.11, = 9.I4ll0

1.18 Convertir 10s siguientes decirnales enteros a sus octales equivalentes:

a ) 3, b) 7, c) 10, 4 50, e) 100, fl 6391

Solucion:

Siguiendo el procedimiento de la figura 1-9, 10s octales equivalentes a 10s nhmeros decimales son:

- a) 3,, = 3, C) 1010 = 12, e) 100,, = 144,

b) 7,, = 7, d) 501, = 62,

fl 6391,, = 14367,

1.19 Conviertanse 10s siguientes numeros decimales a sus octales equivalentes:

a ) 77.375, b) 20.515625, c) 8.15625, d) 44.5625

Solucion:

-

Siguiendo el procedimiento de la figura 1-lob, 10s octales equivalentes a 10s nhmeros decimales son:

a) 77.375,, = 115.3, c) 8.1562510 = 10.12,

b) 20.515625,, = 24.41, d) 44;562510 = 54.44,.

1.20 ConviCrtanse 10s siguientes numeros octales enteros a sus equivalentes binarios:

a ) 3 , b ) 6 , c ) 7 , 4 7 2 , e ) 113

Siguiendo el procedimiento de la figura. 1-1 l a y haciendo uso de la tabla de la figura 1-7.10s binarios

equivalentes a 10s octales enreros son:

.-

a) 3, = 011, c) 7, = 111, e) 113, = 1001011,

b ) 6 1 =1 1 0 2 d) 7 2 , = 111010,

--

1.21 ConviCrtanse 10s siguientes nhrneros octales a sus equivalentes binarios:

a) 7. 5, b) 16. 3, c) 20. 1, 4 3 7 . 6 , e) 11. 4

Solucibn:

Siguiendo el procedimiento que se muesrra en la figura 1-1 l b, 10s binarios equivalentes a 10s octales,

son:

a) 7.5, = 111.101, c) 20.1,= 10000.001, e) 11. 4, = 1001.1,

b) 16.38=1110.0111 d)37. 6, =11111. 11,

.-

1.22 Conviertanse 10s siguientes nhmeros binarios a sus equivalentes octales:

a ) 011, b) 110, c) 111000, 4 101100

Solucibn:

-

Siguiendo el procedimiento que se muestra en la figura I-llc, 10s octales equivalentes a 10s nhmeros ,

binarios son:

a) 011, = 3, c) 111O0O2 = 70,

b) 110, = 6 , d) 101100, = 54,

NUMEROS UTILIZAWS EN ELECTR6NlCA DIGITAL [CAP. I -

1.23 Convertir 10s siguientes numeros binarios a sus equivalentes octales:

a) 111.001, b) 1011.011, C) 110110.11011, d) 11000.1001

Siguiendo el procedimiento de la figura 1-1 lc, 10s octales equivalentes a estos binarios, son:

a) 111.0012 = 7.1B c) 110110.11011, = 66.66,

b) 1011.0112 = 13.3s 4 11000.100lZ = 30.44B

1-4 N~ MEROS HEXADECIMALES

El sistema hexadecimal de nhmeros es el sistema de nhmeros de base 16, utiliza 10s simbolos 0-9, A, B,

C, D, E y F como se muestra en la tabla de la figura 1-12, columna de hexadecimales. La letra A repre-

senta el 10, la B el 11, la C el 12, la D el 13, la E el 14 y la F el 15. La ventaja de este sistema es su facili-

dad de conversion directa a un numero binario de cuatro bit. En la secci6n sombreada de la figura 1-12

cada numero binario de cuatro bit, o sea, del0000 a1 11 11, puede representarse por un s6lo digito hexa-

decimal.

Flg 1-12 Forma de contar en 10s sistemas decimal, binario y hexadecimal

Al fijarse en la columna decimal de la figura 1-12 se puede ver que el equivalente de 16 en el sistema

hexadecimal es 10, lo que demuestra que el sistema hexadecimal tambien emplea el concept0 de valor de

posicibn. El 1 en (lola) significa 16 unidades, mientras que el 0 representa cero unidades.

Convikrtase el hexadecimal 2B6 a numero decimal. La figura 1-13a muestra el proceso que ya cono-

cemos. El 2 estk en el lugar de 10s 256, por lo que 2 x 256 = 512, que se escribe en el rengl6n de 10s decima-

les. El digito hexadecimal B aparece en la columna de 10s 16. Hay que recordar que el B hexadecimal

corresponde al 11 decimal, lo que signilica que hay once que 2 x 256 obteniendo 176 como resultado,

que se suma a15 12 del renglbn de decimales de la figura 1-13a. La colurnna de las unidades muestra que

hay seis de ellas, por lo tanto, se suma un 6 al total de la linea de 10s decimales, obteniendo como resulta-

do final (512 + 176 + 6 = 694) 694,,. La figura 1-130 muestra que 2B6,, es igual a 694,,.

Convikrtase el hexadecimal A3F.C a su decimal equivalente. La figura 1-136 ensefia con detalle este

problema, lnicialmente hay que considerar la columna de 10s 256. El digito hexadecimal A significa que

256 debe multiplicarse por 10, siendo el resultado del product0 2560; el numero hexadecimal muestra ,

que tiene tres 16, por lo tanto 16 x 3 = 48, que se suma a1 rengl6n de 10s decimales. La columna de las

-

unidades contiene el dlgito hexadecimal F, lo que significa que 1 x 15 = 15, que se suma tambiCn a1

rengl6n de 10s decimales. La columna que representa a 16-1 (0.0625) contiene el digito hexadecimal C, lo

que quiere decir que I2 x 0.0625 = 0.75, que se suma al total decimal (2560 + 48 + 15 + 0.75 =

-

..-

- CAP. I ] NUMEROS UTlLlZADOS EN ELECTR6NICA DIOITAL

Potencias de 16

--

Valor de posicibn 256

Numero hexadecimal 2 B 6

256 I h I

x 2 x l l

-

x h

-

Decimal % + 176 + 6 = 6 9 4 , 0

a) Conversibn de hexadecimal a decimal

Potencias de 16 16' 16' 16' 1/16'

Valor de posicibn 1 156

I 6 1 ,0625

Numero hexadecimal A 3 F . C

b) Conversibn fraccionaria de hexadecimal a decimal

Fig 1-13

-

2623.75), obteniendo como resultado final el numero decimal 2623.75. La figura 1-136 ilustra la conver-

sion del A3F.CI6 a1 2623.75,,,.

lnvitrtase ahora el proceso para convertir el numero decimal 45 a su hexadecimal equivalente. La

figura I-14a presenta con detalle el ya conocido proceso de dividir entre 16. El numero decimal 45 se di-

-

vide entre 16, obteniendo cociente 2 y residua 13 (13,, = D13, que es el dms del nhmero hexadecimal. El

cociente (2) pasa a ser el nuevo dividendo, y al dividirse entre 16 se obtiene 0 de cociente y 2 de residuo,

por lo que el 2 pasa a ser el siguiente dlgito del numero hexadecimal. El proceso termina aqul, debido a

.

hue la parte entera del cociente es 0. El proceso que se indica en la figura 1- 140 convierte el ndmero de-

cimal 45 al hexadecimal 2D.

-- 155 1 6 =Z yconresiduo 13

d

2 + I6 = 0 y con residuo

a) Conversibn de decimal a hexadecimal

-

Fig 1-14

I S+ 16= 0 yconresiduo 15

1 I

25O.2SIO = F

A . 416

b) Conversidn de decimal fraccionario a hexadecimal

Conviertase el decimal 250.25 a hexadecimal. La conversibn debe hacerse utilizando dos procesos

-

como se muestra en la figura 1-146. La parte entera del numero decimal (250) se convierte a hexadecimal

por medio del proceso repetido de divisibn entre 16. Los residuos de 10 (A en hexadecimal) y I5 (F en he-

xadecimal) constituyen la parte entera hexadecimal FA. La parte fraccionaria (-25) se multiplica por 16

y se obtiene como resultado 4.00. El 4 se transfiere a la posicibn que se indica en la figura 1-146. La con-

--

versibn completa muestra que el decimal 250.25 es igual a1 FA.4 hexadecimal.

12 NUMEROS UTILIZADOS EN ELECTR6NICA DIGITAL [CAP. I

La principal ventaja del sisterna hexadecimal es su facilidad para convertirlo a binario. La figura

-

I-150 muestra la conversibn del hexadecimal 3B9 a binario. Cada digito hexadecimal forrna un grupo de

cuatro digitos binarios o bit. Para formar el numero binario se cornbinan estos grupos, en este caso

3BglB = 111011 10012.

-

916

1 1 1 3BgI6 = 11101110011

0011 1011 1001

a) Conversibn de hexadecimal a binario

4 7 . F E

1 1 1 1 47. FE16= 10001ll.llllllll

0100 0111 . 1 1 1 1 1110

b) Conversibn de numeros fraccionarios hexadecimales a binarios fraccionarios

C) Conversibn de binario a hexadecimal

a') Conversibn de binarlo fraccionario a hexadecimal

Fig 1-15

En la figura 1-1 Sb se explica con detalle otra conversibn de hexadecimal a binario. Una vez mas, ca-

da digito hexadecimal forrna un grupo de cuatro bit en el numero binario. El punto hexadecimal conser-

va su lugar y pasa a ser el punto binario. El numero hexadecimal 47.FE se convierte en el

10001 11.11 11 11 1 binario. Este sistema es un mttodo fhcil y rhpido para escribir numeros binarios debi-

do a su forma rnhs cornpacta de expresibn.

La figura 1-1Sc enseAa cbmo se convierte el 101010000101 binario a hexadecimal. Primero se divide

el numero binario en grupos de cuatro bit, ernpezando en el punt o binorio, despuks cada grupo de

cuatro bit se convierte a su digito hexadecimal equivalente. La figura 1-15c indica cbmo el

1010100001012 es equivalente a1 ASS,,.

La figura 1-1Sd es un ejemplo de otra conversion binaria a hexadecimal, en donde el binario

10010.01 101 1 se convierte a hexadecimal. Primero el binario se divide en grupos de cuatro bit empezan-

do en el punto binario. Para completar el primer grupo de la izquierda se aAaden tres ceros, formando

asi el 0001 y dos ceros se ailaden a1 ultimo grupo de la derecha, formando ei 1100. Cada grupo tiene asi

cuatro bit, que se convierten a 10s digitos hexadecimales correspondientes como se muestra en la f'igura

I-1Sd. El ndmero binario 10010.01 101 1 es igual al 12.6C hexadecimal.

PROBLEMAS RESUELTOS

1.24 El sistema hexadecimal de numeros tarnbiCn se llama sistema de base

El sistema hexadecimal de numeros tambikn se llama sistema de base 16.

1.25 Enumere 10s 16 simbolos utilizados en el sistema hexadecimal de numeros.

Refirikndose a la figura 1-12, 10s 16 simbolos utilizados en este sistema son: 0, 1 , 2, 3, 4, 5, 6, 7, 8, 9,

A, B, C, D, E y F.

-

CAP. I ] NUMEROS UTILIZADOS EN ELECTR6NICA DIGITAL 13

1.26 Convertir 10s siguientes numeros hexadecimales enteros a sus decimales equivalentes:

-

a) C, b) 9F, c) D52, d) 67E, e) ABCD.

Solucibn:

Se sigue el procedimiento que se muestra en la figura 1-13a.10~ decimales equivalentes a estos nhmeros

hexadecimales son 10s siguientes:

C16 = 1210 c) D5216 = 341Ol0 e) ABCD,, = 43981,,

b) 9F16 = 15910 d) 67E16 = 166210

-

1.27 Convierta 10s siguientes numeros hexadecimales a sus decimales equivalentes:

a) F. 4, b)D3. E, c)1111.1, 4888. 8, e)EBA. C.

Solucibn:

Siguiendo el procedimiento de la figura 1-13b y considerando tambitn la figura 1-12, 10s decimales

equivalentes a estos nirmeros hexadecimales son 10s siguientes:

a) F.416 = 15.2510 C) 1111. I l 6 = 4369.062510 e) EBA.CII = 3770.75,,

b) D3.E16 = 211.87510 d) 888.81s = 2184.510

1.28 Convertir 10s siguientes numerbs decimales enteros a sus hexadecimales equivalentes:

-

a) 8, b) 10, C) 14, 4 16, e) 80, fl 2560,

g) 3000, h) 62 500

Solucibn:

Seguir el procedimiento que se enseila en la figura 1-140 y considerar tambikn la figura 1-12. Los hexa-

decimales equivalentes a estos nhmeros decimales son:

a = g16 C) 14,, = El( e) 8010 = SOl6 8) 300010 = BB8i6

b) 1Ol0 = A16 d) 1610 = lol6 fi 256010 = Aml6 h) 62500,, = F424,,

1.29 Convierta 10s siguientes numeros decimales a sus hexadecimales equivalentes:

a) 204.125, b) 255.875, c) 631.25, d) 10 000.003 906 25.

Siga el procedimiento que se muestra en la figura 1-14b y considere tambikn la figura 1-12. Los hexa-

decimales equivalentes a estos nirmeros decimales son:

a) 204.125,, = CC.2,, c) 631.2510 = 277.416

b) 255.87510 = FF.E16 d) 10 000.003 906 2510 = 2710.0116

-

1.30 Convertir 10s siguientes ndmeros hexadecimales a sus equivalentes binarios:

a) B, b ) E, c) IC, 1 4 A6 4 , e) lF.C, J239.4.

Siguiendo el procedimiento mostrado en la figura 1-150 y considerando la figura 1-12, 10s binarios

equivalentes a estos nhmeros hexadecimales son 10s siguientes:

a) B,, = 1011, c) lC,, = lllOOp e) lF.C16 = 11111.11,

b) E16 = l 1101 d) AMl6 = 1010011001002 j) 239.4,, = 1000111001.012

1.31 Convertir 10s siguientes ndmeros binarios a sus hexadecimales equivalentes:

- a) 1001.1111 C) 110101.011001 e) 10100111.1 1101 1

b) 10000001.1101 4 10000.1 loooooo.0000lll

Solucibn:

-

Seguir el procedimiento indicado en la figura I-15c y d. Considerar tambien la figura 1-12. Los

hexadecimales.equivalentes a 10s binarios dados, son 10s siguientes:

a) 1001.1111, = 9.FI6 c) 110101.011001, = 35.64,, e) 10100111.111011, = A7.EC16

b) 10000001.11012= 81.D16 d) 10000.l2 = 10.816 fi 100~. 00001112 = 40.0E16

NOMEROS UTILIZADOS EN ELECTRONICA DIGITAL (CAP. I

Problemas suplementarios

El sistema de numeros de radix 2 se llama sistema - de nurneros. Resp. binario.

El sistema de numeros de radix 10 se llama sistema - de numeros. Resp. decimal.

El sistema de numeros de base 8 se llama sistema - de numeros. Resp. octal

El sistema de numeros de base 16 se llama sistema - de numeros. Resp, hexadecimal,

Algunas veces un digit0 binario se abrevia y se llama - Resp. bit

iC6mo dirla el numero 1101 en a) binario y b) decimal?

Resp, a) uno, uno, cero, uno b) mil ciento uno.

(b)

y se pronuncia - El nomero 10IOa es un nurnero de base -

Resp.0) 2 b) uno, cero, uno, cero.

Convierta 10s siguientes nbmeros binarios a sus decirnales equivalentes:

a) 00001110, b) 11100000, c) 10000011, d) 10011010.

Resp. 0) 00001110,=141, c) 10000011,=131,,

b) 11100000, = 22A10 d) 1001lOIOa = 1541p

~llOO1l.lll = I , Resp. 51.75

llllOOOO.OO1ll = , , Rap. 240.1875

Convierta 10s siguientes numeros decimales a sus equivalentes binarios:

a) 32, b) 200, c) 170, d) 258.

Resp. a) 32,, = l a ) o, c) 17010 = 10101O1Oa

b) 2fM10 = 110010002 d) 25S10 1000OOOIOa

999.125,, = Resp. 1111100111.001

--.a ."-

Convertir 10s siguientes numeros octales a sus decimales equivalentes:

a) 37, b) 725, C) 2476.2 d) 1117.16. ,

Resp, a) 37, = 31,, C) 2476.2a = 1342.2510

b) 725, = 469,, d) 1117.16B = 591.2187510

Convierta 10s siguientes nurneros decimales a sus equivalentes octales:

a) 399, b) 1500, C) 600.5. 4 3000.8125.

Resp. a) 399,, = 617, c) 600.510 = 1130.4,

6) 15OOlO = 2734, d) 3000.812510 = 5670.64a

Convierta 10s siguientes nbmeros octales a sus binarios equivalentes:

(1) 731, b)6450, c)26.41, 417. 74.

R~sP. a) 731, = lllO1lOO1a C) 26.41. = 101lO.lOOOO1a

b) 6450, = 1101001010002 d) 17.74, = 1111.111Ia

b

- CAP.]] N~JMEROS UTILIZADOS EN ELECTR~NICA DlGlTAL

1.48 Convierta 10s siguientes nurneros binarios a sus equivalentes octales:

--

a) 111010011, b) 1100101, c) 10000.11011, d) 1111110.0001

Re.rp. a) 11 101001 l1 = 723, c) 10000.110112 = 20.66,

b) 1100101, = 1458 d) 1111110.00012 = 176.04,

-

1.49 Convierta 10s siguientes nurneros hexadecirnales a sus decirnales equivalentes:

a) l3AF, b) 2586, c) B4.C9, d) 78.D3.

Resp. a) 13AF1, = 503910 c) B4.C9,, = 180.785151,

- 6) 25E616 = 970210 d) 78.D3,, = 120.8242Il0

1.50 Convierta 10s siguientes nurneros decirnales a sus hexadecimales equivalentes:

a) 3016, b) 64881. c) 17386.76, d) 9817.625.

-

Resp. a) 3016,, = BCS,, C) 17386.7510 = 43EA.C16

b) 648811, = FD71,, d) 9817.62510 = 2659.A16

-

1.51 Convierta 10s siguientes nurneros hexadecirnales a sus equivalentes binarios:

a) A6, b) 19, c) E5.04, d) lB.78. '

Resp. a) A6,, = 10100110, c) ES.04,, = 11100101.000001,

b) 1g16 = 11001, d) 1B.781a = llO1l.O1lllz

-. -

1.52 Convierta 10s siguientes nurneros binarios a sus hexadecirnales equivalentes:

a) 11110010, b) 11011001, c) 111110.000011, d) 10001.11111

Resp. a) . 11110010, = FZ16 c) 111110.000011, = 3E.OC,,

b) 110110011 = DgI6 d) 10001.111112 = 11.FE1,

Codigos binarios -

Los sistemas digitales sblo procesan numeros binarios (ceros y unos). El cbdigo binario se discutio en el

capitulo anterior. En 10s ultirnos arfos han surgido otros codigos binarios especiales para realizar fun-

ciones especificas en equipos digitales. Estos cbdigos usan ceros y unos, pero sus significados pueden va-

-

riar. Aqui se detallarhn varios codigos binarios junto con las rnaneras en las que se traducen a forrna de-

cimal. En un sistema digital, 10s traductores electrbnicos (Ilarnados codificadores y decodricadores), se

usan para pasar de cbdigo a cbdigo. En las siguientes secciones detallarernos el proceso de conversion de

un cbdigo a otro.

I f

Decimal 1 5 0 Decimal 3 2 . 8 4

1 1 ! 1 1 1 1

BCD 0001 0101 0000 BC D 0011 0010 . 1000 0100

2-2 c ~DI GOS BINARIOS PESADOS

Los numeros binarios son algo diflciles de entender. Por ejemplo,

trate de convertir el nhrnero binario 10010110, en un numero deci-

mal. Resulta que 100101 10, = 150,, pero toma cierto tiernpo y es-

fuerzo hacer esta conversibn.

El cbdigo BCD (del inglts binary-coded-decimal) que signifi-

ca decimal codificado en binario hace mucho m8s f8cil la conver-

sibn a decirnales. En la figura 2-1 se rnuestra el cbdigo BCD de

cuatro bit para 10s digitos decimales 0-9. Nbtese que el cbdigo

BCD es un cbdigo pesado. El bit mhs significativo tiene un peso de

8 rnientras que el menos significative s610 tiene un peso de 1. A este

cbdigo se le conoce rnhs precisamente corno el cddigo BCD 8421. El

8421 el nombre se refiere a1 peso que se le da a cada lugar en el cbdi-

a) Conversibn decimal a BCD C) Conversibn decimal fractional a BCD

BCD 1001 0110 .

1 1

Decimal 9 6 .

go de cuatro bit. Existen varios cbdigos BCD que tienen otros pesos

Fig. Z-l C6digo 8421

para 10s cuatro lugares. Como el cbdigo BCD 8421 es el m8s popu-

-

lar, se acostumbra referirse a el simplemente como el cbdigo BCD.

~Cb mo se expresa el nhrnero 150 corno un nurnero BCD? En la figura 2-2a se muestra una ttcnica

sencilla para convertir nurneros decirnales a numeros BCD (8421). Cada digito decimal se convierte a su

equivalente en BCD de cuatro bit. (Vease Fig. 2-1). El numero decimal 150 es entonces, igual al ndrnero

BCD 000101010000.

Decimal

0

I

7

&

3

4

5

6

7

8

9

b) Conversibn BCD a decimal

RCD

8 1 2 1

0 0 0 o

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 I 0

0 1 1 1

1 0 0 0

1 0 0 1

BCD 0111 0001 . 0000 1000

1 1 1 1

Decimal 7 1 . 0 8

d) Conversibn BCD fraccional a decimal

C6DlOOS BINARIOS

Tambitn es bastante simple convertir numeros BCD a numeros decimales. En la figura 2-2b se

-

muestra la ttcnica. Primero se divide el numero BCD 100101 10 en grupos de cuatro bit, empezando por

el punto binario. Cada grupo de cuatro se convierte luego en el digito decimal equivalente, que se anota

debajo. El nhmero BCD 10010110 es, entonces, igual al 96 decimal.

-

La figura 2-2c ilustra un numero decimal fraccionario convertido a su equivalente BCD. Cada

digito decimal se convierte en su equivalente BCD. El punto decimal se pasa para abajo y se convierte en

el punto binario. La figura 2-2c muestra que el decimal 32.84 corresponde a1 numero BCD

- 001 10010.10000100.

Convierta el nhmero fraccionario BCD 01 110001.00001000 a su equivalente decimal. En la figura

2-2d se muesrra el procedimiento. El numero BCD se divide en grupos de cuatro bit empezando en el

punto binario. Cada grupo de cuatro bit se convierte desputs a su equivalente decimal. El punto binario

-

se convierte en el punro del numero decimal. En la figura 2-2d se muestra el numero BCD

01 110001.00001000 a1 ser convertido a su equivalente decimal 71.08.

Considere ahora el problema de convertir un numero BCD en su equivalente binario. En la figura

- 2-3 se muestran 10s tres pasos de que consta el procedimiento. En el Paso 1 el nhmero BCD se divide en

grupos de cuatro bitempezando en el punto binario. Cada grupo de cuatro bit se traduce a su equivalen-

te decimal. En la figura 2-3 se ve que el numero BCD 00010000001 1.0101 al ser traducido a1 nhmero de-

- cimal es 103.5.

BCD OOOI 0000 0011 .0101

1 1 1 1

Decimal I 0 3 . 5

103 + ! = 51 y residuo I

5 1 - 2 = 25 y rcsiduo I

25 + 2 = 12 Y res~duo l

I ? + ? = 6 yresiduo 0

6 - ? = 3 y residuo 0

3 t 2 = 1 y rcs~duo I

1 + 2 = 0 y residuo

Binario 1 1 0 0 1 I 1 . 1 ,

0.5 x 2 = 1.0

-

0.0 x 2 = 0.0

6

Fig. 2-3 Conversibn BCD a binario

El paso 2, en la figura 2-3, muestra la parte entera de numero decimal a1 ser traducida a binario. El

10310 se convierte en 11001 11, en el paso 2 por el procedimiento de dividir repetidamente entre dos.

-

El paso 3, en la figura 2-3, ilustra la parte fraccionaria del nbmero decimal a1 ser traducida a bina-

rio. El 0.Sl0 se convierte en 0.1, en el paso 3 por medio del procedimiento de multiplicar repetidamente

por dos. La parte enrera y la parte fraccionaria se unen. El ndmero BCD 00010000001 1.0101 es entonces

-

igual a1 nhmero binario 11001 1 1.1.

N6tese que usualmente es m8s efectivo escribir un numero en binario que en BCD. Los numeros bi-

narios usualmente tienen menos unos y ceros, como se ve en la conversibn de la figura 2-3. Aunque son

m8s largos, 10s nhmeros BCD se usan en 10s sistemas digitales cuando se requiere que 10s numeros se tra-

-

duzcan fhcilmente a decimales.

Traduzca el numero binario 10001010.101 a su equivalente BCD 8421. El proceso se muestra en la figura

2-4. El numero binario se convierte primer0 en su equivalente decimal. Entonces, el numero binario

- 10001010.101 es igual a 138.625,,. Cada digito decimal se traduce entonces a su equivalente BCD. En

C6DIGOS BINARIOS

Binario I O 0 0 I O I O ~ 1 0 1

1

Decimal 128

I ir'r'

+ii0.5~0.125;l

7

BCD OOO1 001 1 1000 . 01 10 0010 0101

Fig. 2-4 Conversibn binario a BCD

l a f i gur a 2-4 se mues t r a cbmo el deci mal 138.625 se convi er t e en el numer o BCD

0001001 11000.01 1000100101, Finalmente vemos que la conversi6n completa traduce a1 binario

10001010.1012 en el BCD 0001001 11000.01 1000100101.

El BCD es un tkrmino general que puede aplicarse a diversos mktodos. El c6digo BCD mas popu-

lar es el 8421. Los numeros 8,4,2,1 representan el peso de cada bit en el grupo de 4 bit. En la figura 2-5 se

muestran otros ejemplos de BCD pesados de cuatro bit.

Fig. 2-5 Tres cbdigos BCD pesados

842 1 BCD 422 1 BCD 542 1 HC'D

8 4 2 1 8 4 2 1 4 2 2 1 4 2 2 1 5 4 2 ' 5 4 2 1

PROBLEMAS RESUELTOS

0

I

2

3

4

5

6

2.1 Las letras BCD significan:

Soluci6n:

Las letras BCD significan "decimal codificado en binario" en todas Las soluciones.

0 0 0 0 ,

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

2.2 Convierta 10s siguientes numeros BCD 8421 a sus equivalentes decimales:

a) 1010 c) lOOOO110 e) 00110010.10010100

b) 00010111 4 O ~ O ~ O I O O O O ~ I oooloooooooooooo.olo~

I 0 1.0

1 0 1 1

1 1 0 0

0 0 0 1 0 0 0 0

0 0 0 1 0 0 0 1

0 0 0 1 0 0 1 0

0 0 0 1 0 0 1 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

1 0 0 0

0 1 1 1

1 I 0 0

0 1 1 1 1 I 1 0 1

1 0 0 0 1 1 1 1 0

9 I 1 1 1 1 '

l U O I I

0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0

lo 1 1 ~ 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

1 0 0 0

1 0 0 1

0 0 0 1 0 0 1 0

0 0 0 1 0 0 1 1

12

13

.-

0 0 0 1 0 0 1 0

0 0 0 1 0 0 1 I

CAP.21

-

C~DIGOS BINARIOS

Soluclbn:

Los equivalentes decimales de 10s numeros BCD son como sigue:

a) 1010 = ERROR (no hay tal ndmero BCD) 6) 01010100001 1 = 543

b ) 000lOlll = 17 e) 001 10010.10010100 = 32.94

C) 10000110 = 86 . 0001000000Ci00000.0101 = 1000.5

Convierta 10s siguientes nhmeros decimales en sus equivalentes BCD: 8421:

a) 6, b) 13, c) 99.9, d) 872.8, e) 145.6, A 21.001

Los equivalentes BCD para esos numeros decimales son:

a) 6 = 0110 c) 99.9 10011001.1001 e ) 145.6 = 000101000101.0110

b ) 13 = 00010011 6) 872.8 = 100001110010.1000 A 21.Wl = 00100001.-I

Convierta 10s siguientes numeros binarios a sus equivalentes BCD 8421:

a) 10000, b) 11100.1, c) 101011.01, d) 100111.11, e) 1010.001, A l l l l l l oool .

Los equivalentes BCD para esos nurneros binarios son:

a) 1000 = 00010110 6) 100111.11 = 00111001.01110101

b) 11100.1 = 00101000.0101 e) 1010.001 = 00010000.000100100101

C ) ioioii.oi = oi mi 1. 001001oi A 1111110001 = m~oooooooo~ooi

Convierta 10s siguientes nhmeros BCD 8421 a sus equivalentes binarios:

a) 0001 1000 c) 01 10.011 10101 e ) 01 100000.00100101

b) 01001001 4 001 101 I 1.0101 ~ ~ I . O O I I O I I lo101

Solucion:

Los equivalentes binarios parn estos numeros BCD son como sigue:

a) 00011000 = 10010 d) 00110111.0101 = 100101.1

b) 01001001 = 110001 e) 01100000.00100101 = 111 100.01

C ) o ~ i o . o i ~ ~ o i o i = 110.11 o o o i . o o ~ ~ o ~ i ~ o ~ o i = 1.011

Mencione tres cbdigos BCD pesados.

Sulucion:

Tres cbdigos BCD son: a) BCD 8421, b ) BCD 4221 c) BCD 5421

El equivalente BCD 4221 del decimal 98 e s .

Solucibn:

El equivalente BCD = 4221 del decimal 98 es I 11 11 110.

El equivalente BCD 5421 del decimal 75 es .

Solucibn:

El equivalente BCD 5421 del decimal 75 es 10101000.

~ Qu C clase de nhmero (BCD o binario) seria mhs fhcil de traducir a decimal?

Los numeros BCD son 10s mils filciles de traducir a sus equivalentes decimales.

C6DIGOS BINARIOS

2-3 CODIGOS BINARIOS NO PESADOS

Algunos cbdigos binarios son no pesados. Cada bit, por lo tanto, no tiene un peso especial. Dos de estos

cbdigos no pesados son el c6digo Gray y el cbdigo exceso-3.

El cbdigo exceso-3 (XS3) esta relacionado a1 BCD 8421 por su naturaleza de decimal codificado bi-

-

nario. En otrzs palabras, cada grupo de cuatro bit en el cbdigo XS3 es igual a un digito decimal

especifico. La figura 2-6 muestra el cbdigo XS3 junto con sus equivalentes en BCD 8421 y decimal. No-

tese que el nurnero XS3 siernpre es tres m6s que el numero BCD 8421.

Fig. 2-6 Cbdigo de exceso 3 (XS3)

Decimal

0

I

2

3

4

5

6

7

8

9

10

11

Considere el cambio del numero decimal 62 a su numero equivalente en XS3. El paso 1 en la figura

2-7a muestra cbmo se suma 3 a cada digito decimal. En el paso 2 se muestra cbmo el 9 y el 5 se convier-

ten en su equivalente BCD 8421. El n6mero decimal 62 es, entonces, igual al nfimero BCD XS3

10010101.

Decimal 6 2

I

fi @ mads 3

19

f @ Conversibn a binario -- + +E @ Af i adal

XS3 1001 0101 XS3 0111 0011

8421 BCD XS3 BCD

a) Conversibn decimal a XS3 b) Conversibn BCD a XS3

10 1

0000

OOO1

0010

0011

0100

0101

0110

0111

l o00

1001

OOOI 0000

OOO1 OOO1

XS3 l oo0 1100

1 -0011 -0011

BC D

1 1

Decimal 5 9

10 1

0011 0011

0011 0100

0011 0101

0011 0110

0011 0111

0011 1OOO

001 1 1001

0011 1010

0011 1011

0011 1100

0100 0011.

0100 0100

c) Conversi6n XS3 a decimal

Fig. 2-7

Convierta el numero BCD 8421 OlOOOOOOa su equivalente XS3. En la figura 2-7b se ve el procedi-

miento. El nlimero BCD se divide en grupos de cuatro bit empezando en el punto binario. El paso I

muestra c6mo se suma 3 (binario 001 1) a cada grupo de 4 bit. La surna es el nlimero XS3 resultante. La

figura 2-7b muestra el nlimero BCD 8421 OlOOOOOOa1 ser convertido a su numero BCD XS3 equivalente

que es 01110011.

-. CAP.21 C6DIGOS BINARIOS

Considere ahora la conversibn del cbdigo XS3 a decimal. En la figura 2-7c se muestra el numero

-

XS3 10001 100 a1 ser convertido a su equivalente decimal. El nhmero XS3 se divide en grupos de cuatro

bit empezando en el punto binario. El paso 1 muestra el 3 (binario 001 1) al ser restado de cada grupo de

cuatro bit. El resultado es un numero BCD 8421. El paso 2 muestra cada grupo de cuatro bit en el nume-

-

ro BCD 8421 a1 ser traducido a su equivalente decimal. El nhmero XS3 10001 100 es igual a1 decimal 59

de acuerdo con el procedimiento de la figura 2-7c.

El c6digo XS3 tiene un valor significative en circuitos aritmeticos. El valor del codigo esth en su fa-

-

cilidad de complementaci6n. Si cada bit es complementado (0 a 1 y 1 a 0), la palabra de cuatro bit resul-

tante sera el complemento a 9 del numero. Los sumadores usan nhmeros complemento 9 para realizar la

sustraccibn.

El Cddigo Gray, es otro codigo binario no pesado. El cbdigo Gray no es un cbdigo tipo BCD. En la

-.

figura 2-8 se compara el c6digo Gray con niimeros binarios y decimales equivalentes. Observe cuidado-

samente el codigo Gray. Advierta que cada aumento en la cuenta (incremento) viene acompafiado por

un solo cambio en el estado del bit. Vea el cambio de las lineas decimales 7 a 8. En hinario 10s cuatro bit

. cambian de estado (de 011 1 a 1000). En esta nlisma linea el codigo Gray s6lo cambia de estado en el bit

izquierdo, (0100 a 1100). Este cambio en un solo bit en el cbdigo por incremento es una caracteristica

irnportaiite en algunas aplicaciones en electrbnica digital.

Fig. 2-8 C6digo Gray

Convierta ahora un numero binario a su equivalente en cbdigo Gray. La figura 2 . 9 ~ rnuestra el nu-

mero binario 0010 al ser traducido a su equivalente en codigo Gray. Empiece en el BMS del numero bina-

-

rio. Tansfiera Cste a la posicibn izquierda en el cbdigo Gray como lo muestra la flecha. Ahora sume el bit

de 10s 8 al siguiente bit (bit de 10s 4). La suma es 0 (0 + 0 = O), que se transfiere y se escribe como el

segundo bit de la izquierda en el cbdigo Gray. El bit de 10s 4 se suma ahora a1 bit de 10s 2 en el nbmero

- binario. La suma es 1 (0 + 1 = 1) y se transfiere y se escribe como el tercer bit de la izquierda en el c6di-

go Gray. El bit de 10s 2 se suma ahora a1 bit de 10s 1 del nhmero binario. La suma es 1 (1 + 0 = I) y se

transfiere y se escribe como el bit de la derecha en el cbdigo Gray. Entonces, el nun~er o binario 0010 es

-

igual a1 nurnero 001 1 en cbdigo Gray. Esto puede verificarse en la linea 2 decimal de la tabla de la figura

2-8.

Decimal

0

1

2

3

4

5

6

7

Binario Binario

I l l

i

I I I I

suma suma suma suma

1 1 1 1

Codigo Gray 0 0 1 1 Cbdigo Gray 1 1 1 0 1

Binario

loo0

100 1

1010

101 1

1 100

1101

1 1 10

1 1 1 1

(a) ( b)

Fig. 2-9 Conversiones de c6digos Binarios-Gray y Gray-Binario

Binario

0000

OOO1

0010

001 1

0100

0101

01 10

0111

Cbdigo Gray

1100

1101

1 1 1 1

1110

1010

101 1

1001

lo00

C6digo Gray

0000

OOO1

001 1

0010

01 10

01 1 1

0101

0 100

Decimal

8

9

10

1 1

12

13

14

I5

22 C~ DI GOS BINARIOS [CAP.2

Las reglas para convertir cualquier numero binario a su equivalente en cbdigo Gray son las siguien-

-

tes:

1. El bit de la izquierda es igual en cbdigo Gray que en el nhmero binario.

2. Sume el BMS a1 bit inmediatamente a la derecha y anote la suma (desprbciese cualquier acarreo) de-

bajo en la linea de cbdigo Gray.

-

3. Continhe sumando 10s bit a1 bit de la derecha y anotando las sumas hasta que se llegue a1 bms.

4. El ndmero en cbdigo Gray siempre tendrti el mismo ndmero de bit que el numero binario.

Pruebe estas reglas para convertir el binario 10110 a su equivalente en cbdigo Gray. La figura 2-9b -

muestra el BMS (1) en el ndmero binario a1 ser transferido hacia abajo y escrito como parte del numero

en cbdigo Gray. El bit de 10s 16 se suma entonces a1 bit de 10s 8 en el ndmero binario. La suma es l(1 +

0 = l), que se anota en el cbdigo Gray (segundo bit de la izquierda). Luego el bit de 10s 8 se suma a1 bit

-

de 10s 4 en el numero binario. La suma es l (0 + 1 = l), que se anota en el cbdigo Gray (tercer bit de la

izquierda). Luego el bit de 10s 4 se suma al bit de 10s 2 del ndmero binario. La suma es 0 (1 + 1 = lo),

porque el acarreo ( I ) se descarta. El cero se anota en la segunda posicibn de la derecha en el cbdigo

Gray. Luego se suma el bit de 10s 2 a1 bit de 10s 1 en el ndmero binario. La suma es 1 (1 + 0 = I) que se

-

anota en el cbdigo Gray (bit de la derecha). El proceso se ha completado. La figura 2-96 muestra a1 nu-

mero binario 101 10 al ser traducido al numero 11 101 en cbdigo Gray.

Convierta ahora el numero 1001 en codigo Gray a su equivalente en binario. En la figura 2-10a se .-

detalla el procedimiento. Pr i me r ~ el bit de la izquierda (1) se transfiere hacia abajo al renglbn binario

formando el bit de 10s 8. El bit de 10s 8 en el numero binario se transfiere (ver flecha) arriba del siguiente

bit en cbdigo Gray y se suman 10s dos. La suma es I (1 + 0 = 1) que se escribe en el lugar del bit de 10s 4

en el numero binario. El bit de 10s 4 (1) se suma entonces al siguic~ite bit en cbdigo Gray. La suma es 1

-

(1 + 0 = 1). Este 1 se escribe en el lugar de 10s 2 del numero binario. El bit de 10s 2 del binario 1 se suma

a1 bit de la derecha en cbdigo Gray. La suma es 0 (1 + 1 = 10) porque se descarta el acarreo. Este 0 se

escribe en el lugar de 10s 1 en el numero binario. La figura 2-1Ou muestra el ndmero 1001 cbdigo Gray

-

Traducido a su numero binario equivalente 11 10. Esta conversibn puede verificarse mirando la linea de-

cimal 14 en la figura 2-8.

-

Cbdigo Gray I Cbdigo Gray

-

Binario Binario

(1 h )

-

Fig. 2-10 Conversiones de c6digo Gray a binario

Convierta el numero de seis bit 01 101 1 en cbdigo Gray a su equivalente en binario. Empiece a la iz-

-

quierda y siga las flechas de la figura 2-106. Siga el procedimiento, recordando que 1 + I = 10. El

acarreo (1) se descarta y se pone cero en la linea binaria. La figura 2-l ob muestra que el numero codigo

Gray 01 101 1 es igual a1 numero binario 010010.

-

PROBLEMAS RESUELTOS

2.10 Las letras y numeros XS3 significan codigo -

Solucibn:

XS3 significa c6digo exceso 3.

-

2.1 1 El cbdigo BCD - (8421, XS3) es un ejemplo de un cbdigo no pesado.

SuluriOn:

El cbdigo BCD XS3 es un ejemplo de un cbdigo no pesado

C~DIGOS BINARIOS

El cbdigo - (Gray, XS3) es un cbdigo BCD.

Solucibn:

El c6digo XS3 es un cbdigo BCD.

Convierta 10s siguientes numeros decimales a sus equivalentes en cbdigo XS3:

a) 9, b) 18, c) 37, d) 42, e) 650

Solucibn:'

Los equivalentes XS3 para estos numeros decimales son como sigue:

a) 9 = 1100 c) 37 = 01101010 e) 650 = 100110000011

b) 18 = 01001011 d) 42 = 01110101

Convierta 10s siguientes numeros BCD8421 a sus equivalentes en cbdigo XS3:

a) 0001, b) 011.1, c) 01 100000, d) 00101001, e) 10000100.

Solucibn:

Los equivalentes XS3 para 10s nhmeros BCD8421 son 10s siguientes:

a) 0001 = 0100 c) 01100000 = 10010011 e) 10000100 = 10110111

b) 0111 = 1010 d) 00101001 = 01011100

Convierta 10s siguientes nbmeros X S ~ sus equivalentes decimales:

a) 0011, b) 01100100, c) 1100101 1 d) 10011010 e) 10000101

Los decimales equivalentes de 10s numeros XS3 son 10s siguientes;

a) 0011 = 0 c) 11001011 = 98 e) 10000101 = 52

b) 01100100 = 31 d) 10011010 = 67

El Cddigo (Gray, XS3) se usa generalmente en aplicaciones aritmkticas en circuitos di-

gitales.

Solucibn:

El cbdigo XS3 se usa generalmente en aplicaciones aritmeticas.

Convierta 10s siguientes numeros binarios a sus equivalentes en cbdigo Gray:

a) 1010, b) 10000, c) 10001, d) 10010, e) 10011

Soiuclbn:

Los equivalentes en cbdigo Gray para estos numeros binarios son:

a) 1010 = 1111 C) 10001 = 11001 e) 10011 = 11010

b) 10000 = 11000 d) 10010 = 11011

Convierta 10s siguientes numeros en cbdigo Gray a sus equivalentes en binario.

a) 0100, b) 1111 1, c) 10101, d) 110011, e) 011100

Solucibn:

Los equivalentes binarios para estos numeros en codigo Gray son:

a) 0100 = 0111 C) 10101 = 11001 e) 01 1100 = 0101 1 1

b)11111=10101 d)110011=1OGQ10

La caracteristica mas importante del cddigo Gray es que cuando la cuenta se incrementa en uno,

- (sblo un, mas de) un bit cambia de estado.

La caracteristica mas importante del c6digo Gray es que cuando la cuenta se incrementa en uno, s6lo

un bit cambia de estado.

2-4 CODIGO DE DETECCION DE ERRORES

-

Una ventaja de 10s sistemas digitales (como la cornputadora digital) es su gran precision. Aunque 10s sis-

ternas digitales son bastante exactos, pueden surgir algunos errores. ~ s t o s deben ser detectados cuando

ocurren durante la transrnisibn de 10s datos. Un rnetodo simple de deteccibn de errores usa el bit de pari-

-

dad. El bit de paridad es un bit extraque viaja a travks de una palabra digital (un grupo de bit ) y ayuda

a detectar 10s posibles errores que pueden ocurrir durante la transrnisibn.

Un sisterna de transrnisi6n digital se muestra en forma de bloques en la figura 2.1 1. El transmisor

de la izquierda esta mandando bit de datos A, B, C y D (una palabra de cuatro bit). Corno una pre-

caucibn contra cualquier error esta palabra de cuatro bit se mete a un generador de bit de paridad, que

genera el bit de paridad apropiado (A. El bit de paridad y la palabra de cuatro bit se mandan a travts

de la linea de transmisibn. La palabra de cuatro bit se rnanda al sistema digital receptor. La palabra de

cuatro bit junto con el bit de paridad se mandan a1 circuito de deteccidn de errores. Si ocurre un error

durante la transrnisibn, el circuito de deteccibn de errores activara una alarrna.

Fig. 2-1 1 Deteccian de error usando bit de paridad en sisterna de transmisibn de datos

La tabla de la figura 2-12 nos ayudara a explicar c6-

mo opera el metodo de paridad. Esta tabla es realrnente

una tabla de verdad para el generador de bit de paridad

que se muestra en la figura 2-1 1. La palabra de cuatro

bit que esta siendo transmitida se rnuestra bajo las

entradas (D, C, B, A) en la figura 2-12. El bit extra, de

paridad que se transmite con la palabra de cuatro bit se

rnuestra en la columna de salida (P). La tigura 2-12 es

una tabla de verdad para un circuito gerlerador de bit de

paridad par. La tabla de verdad da todas las posibles

cornbinaciones de D, C, B y A con la salida resultante.

El circuito generador de bit de paridad examina las

entradas para ver si estan presentes en ntimero par de

I . Si existe un nurnero par de 1, la salida del circuito (el

bit de paridad) es 0. Si no hay un nurnero par de 1 en las

entradas, el circuito generador de bit de paridad genera

una salidad de 1 (el bit de paridad es 1).

Observe el rengl6n I en la figura 12. Hay cero I (o

-

es un nurnero par), asi que el bit de paridad es 0. Las

entradas en el renglbn 2 son 0001. Ahi hay un nurnero

impar de 1 (un unico I), asi que el circuito genera un 1

en la salida (el bit de paridad es 1). Las entradas del

renglbn 4 contienen dos 1 (001 1). Este nurnero par de 1

genera un bit de paridad cero en la salida de P. La entra-

Fig 2-12 Tabla de verdad para un gene-

da en el renglbn 8 contiene tres 1 (01 11). Un nurnero im-

rador de bit de paridad par

Lines

I

I

0 0 I 0

5 0 I 0 0 I

6 0 1 0 1

7 O I I O

n 0 1 1 1

9 1 0 0 0

0

I

1 6 1 I 1

Llnea Palabre

I 811 de

paridad

Enlradas

- -.

D ( ' B . 4

o o o o

Salida

P

o

par de 1 genera un bit de paridad 1 en la colurnna de salidas. En otras palabras, el generador de bit de

paridad se asegura de que haya un nllmero par de 1 en la linea de transrnision.

El circuit0 de deteccibn de errores sblo hace sonar una alarrna si aparece un n6rnero irnpar de 1 en

su entrada. Un numero irnpar de 1 significa error, y debe sonar la alarrna. Este sistema simple sblo de-

tecta errores, no puede corregirlos.

Algunas veces se usa el metodo deparidad impar, siernpre que se transrnita un nhrnero impar de 1.

El sistema seria similar al de la figura 2-1 1. Los circuitos dentro del generador de bit de paridad y el de-

tector de errores serian ligerarnente diferentes.

Existen sisternas rnlls complicados que corrigen errores en la transrnisibn. Un ejernplo de estos cbdi-

gos de correccibn de errores es el cddigo Hamming.

PROBLEMAS RESUELTOS

2.20 10s errores de transtnisibn en 10s sisternas digitales pueden detectarse por rnedio de un bit de

Solucibn:

Los errores de transmisibn en 10s sisternas digitales pueden ser detectados por medio de un bit de pari-

dad.

2.21 Si siernpre se transmite un numero par de 1, el sisterna de deteccibn de errores se conoce corno

un sisterna de paridad

(par, irnpar)

Solucibn:

Un sistema de paridad par siempre transmite.un numero par de 1

2.22 El bit de paridad ayuda a (corregir, detectar) errores que ocurren durante la trans-

rnisibn de datos.

Solucibn:

El bit de paridad ayuda a derectar errores que ocurren durante la transrnisibn de datos.

2.23 Enurnere las salidas (P) del generador de bit de paridad par para cada uno de 10s doce pulsos de

entrada que se muestran en la figura 2-13.

Entradas Salida

1 1 1 1 l 1 0 1 1 1 1

--- 3 7

Fig. 2-13 Generador de bit de paridad para el problema de secuencia de pulsos

Solucibn:

Las salidas ( P) del generador de bit de paridad par de la figura 2-13 son las siguientes:

a) pulso a = 0 4 pulso d - 0 g) pulso g = 0

J) pulso j = 0

6) pulso b = 0 e) pulso e = 1

h) ~ U I S O h = 1 k ) pulso k = 0

C) puiso c = I n pu~sof = o 9 ~ U I S O i = I I ) pulse I o

26 C~ DI GOS BINARIOS ICAP.2 -

2.24 Enumere las salidas del circuito detector de errores para cada uno de 10s doce pulsos de entra-

-

da que se muestran en la figura 2-14. Suponga que el sisiema usa el mttodo de paridad par para

la deteccibn de errores.

Entradas Salida

de error

Fig. 2-14 Detector de errores para el problema de secuencia de pulsos

Solucibn:

Las salidas del circuito detector de errores de la figura 2-14 son como sigue:

a) pulso a = OK (no hay error) g) pulso g = OK (no hay error)

b) pulso b = OK (no hay error) h) pulso h = ERROR (se activa la alarma)

c) pulso c = ERROR (se activa la alarma) I) pulso i = ERROR (se activa la alarma)

d) pulso d = OK (no hay error) j) pulso j = OK (no hay error)

e) pulso e = OK (no hay error) k) pulso k = ERROR (se activa la alarma)

j) pulso f = OK (no hay error) I ) pulso I = OK (no hay error).

2-5 C~ DI GO DE CORRECCI~N DE ERRORES .-

En la secci6n anterior se us6 un solo bit de paridad para detectar un error durante la transmisi6n de in-

formacibn digital. Este h i c o bit de paridad, solamente indicaba que existia un error, pero no indicaba

cuPl era el bit incorrecto. El C6digo Hamming detecta un error e indica cual es el bit err6neo. Entonces

- -

este bit incorrect~ puede cambiarse a su forma correcta, siendo entonces el C6digo Hamming un c6digo

autocorrector.

Una palabra de 4 bit (D7, D,, Dgr Dl), se esta transmitiendo en la figura 2-15. Tres bit de paridad

par (P,, P,, P& estan siendo generados en la izquierda y transmitidos junto con 10s datos. Cualesquiera

errores se detectan en la derecha de la figura 2-15 por 10s tres circuitos de detecci6n de errores conoci-

dos. Si no existe ningun error en 10s datos (D,, D,, D,, 03 a1 salir de la linea de transmisi6n,los indica-

dores de error marcaran 000. Con 10s indicadores de error en 000, el circuito corrector de errores no ha-

ce nada a los datos (D,, D6, D5, Dl) y los manda a1 sistema receptor digital.

Sup6ngase que la palabra de datos que se va a transmitir es 1010 como se ilustra en la figura 2-16u.

iCuhl sera la salida del generador de bit de paridad par en P,? Las entradas son D,, D, y D5 que son

iguales a 101. La salida P4 sera un 0 para producir un nlimero par de 1, Esto se muestra en la figura 2-16b.

A continuaci6n, jcuhl es la salida en P, del segundo generador de bit de paridad par? Las entradas son

D,, D, y D,, que son iguales a 100. La salida P, sera un 1 para producir un ndmero par de I . Esto se

muestra en la figura 2-16c. Finalmente, CUM es la salida en PI, del generador debit de paridad par de la

parte inferior de la figura 2-15? Las entradas son D,, D, y D,, que son iguales a 110. La salida P1 serP un

0 para producir un numero par de 1. Esto se muestra en la Fig. 2-16d. La informaci6n binaria que entra

en la llnea de transmisi6n sera 1010010 como lo muestra la figura 2-16d.

Suponga que en la figura 2-15 no hay errores durante la transmisi6n. La salida de la linea de trans-

misi6n sera 1010010, como se ve en la figura 2-170. El circuito detector de errores de la parte superior de

la figura 2-15 tiene la entrada que se muestra en la figura 2-176. La entrada 1010 genera un 0 en la salida

E4 lo que significa que no hay error en el detector de errores de 10s 4. Luego, en la figura 2-17c se

muestran las entradas del circuito detector de errores de en medio como 1001. Los dos 1 generan un 0 en

la salida E,, lo que significa que no hay error en el indicador de errores de 10s 2. Finalmente en la figura

2-17d se muestra que las entradas en el circuito detector de errores inferior son 1100. Este circuito genera

---

CdDIGOS BINARIOS

a) Palabra de dalos

C ) Bit de paridad (P,) generado

b) Bit de paridad (P,) generado d) Bit de paridad (P,) generado

-

Fig. 2-16

D7 D, D, P, D, P, P , Salida E2

l 0 X X O l X 0

a) Salida de la llnea de transmisibn c) Entradas y salida del circuito detector de errores de enmedio

D T 0 6 D, P4 D3 P2 P I

Salida E4

l o I O X X X 0

-

D: D, D, P4 D~ p 2 p I

Salida El

l X l X O X 0 0

b) Entradas y salida del circuito detector de errores superior d) Entradas y saiida del circuito detector de errores inferior

Fig. 2-17

un 0 en la salida El , lo que significa que no hay error en el indicador de error de 10s 1. Aparecen tres 0 en

10s indicadores de errores, lo que significa que no ocurrib ningdn error durante la transmisibn. Esto pro-

voca que el circuito detector de errores deje pasar 10s datos D,, D,, D, y D3 hacia el sistema receptor di-

gital en su forma original (1010).

Ahora suponga que ha sucedido un error durante la transmisibn de la palabra de datos 1010. Su-

ponga que el bit de datos 5 (D,) ha cambiado de 1 a 0, segdn se rnuestra en la figura 2-18a. Observe el cir-

cuito detector de errores de la parte superior de la figura 2-15. Las entradas a este circuito se muestran

como 1000 en la figura 2-1 86. El detector de errores superior genera una salida de 1 en E,, lo que signifi-

ca que se ha detectado un error. A continuacibn se muestra que las entradas en el circuito detector de

errores de en medio es 1001 (Fig. 2-18~). El circuito detector de errores de en nnedio no advierte ningun

error y genera un 0 en la salida E,. Finalmente las entradas del circuito detector de errores inferior son

0 7 De, Ds P4 D.1 Pz P I

I O I 0 O I 0 Entrada a la llnea de transmisibn

error

L

I 0 0 0 0 I 0 Salida de la Hnea de transmisibn

a) Error introducido en el bit 5 de 10s datos

D- Dh D) P4 D, P2 PI Salida E4

l 0 0 0 X X X 1

b) Entradas y salida del circuito detector de error superior

D- D, D, P4 D, P, P I

Salida E2

l 0 X X O l X 0

C) Entradas y salida del circuito detector de error de enmedio

D7 D , D, P, D3 PI P I Salida El

I X O X 0 X 0 1

d) Entradas y salida del circuito detector de error inferior

Fig. 2-18

C6DIGOS BINARIOS

1000, segun se muestra en la figura 2-18d. El circuito inferior genera un 1 en la salida E, debido a un

error. El indicador de errores de la figura 2-15 muestra el binario 101 (5 decimal) que significa que el bit

5 (D,) es incorrecto. El circuito detector de errores cambia el bit de datos 5 (D,) de 0 a 1. Luego la pa-

labra de datos 1010, ya corregida, se manda al sistema receptor digital de la derecha de la figura 2-15.

El cbdigo Hamming es uno de 10s diferentes tipos de cbdigos detectores de errores que usan bits de

paridad. El cbdigo Hamming detectarh y corregirh un solo error, usando varios generadores de bit

de paridad y circuitos detectores de errores. La desventaja obvia del c6digo Hamming es la necesidad de

lineas de transmisibn adicionales y circuitos digitales extra. El c6digo Hamming puede ser usado con pa-

labras de mas de 4 bit afiadiendo mhs bit de paridad.

PROBLEMAS RESUELTOS

2.25 Usando el cbdigo Hamming, un circuito digital puede detectar y ' errores en la transmi-

sibn.

Solucibn:

El Cbdigo Hamming puede usarse para detectar y corregir errores en la transmisibn digital de datos.

2.26 . Consulte la figura 2-15. Este sistema de transmisibn digital esttt mandando una palabra de

bit y tres bit de - a travks de la linea de transmisibn.

El sistema de transmisibn digital de la figura 2-15 estd mandando una palabra de 4 bit y tres bit de pa-

ridad a travts de la linea de transmisibn.

2.27

Enumere las salidas (P) de generador de bit de paridad par para cada uno de 10s pulsos de entra-

da que se muestran en la figura 2-19

Entradas Salida

Ocnerador

I I O D O O I I - - + ?

- dc paridad

h g J e r l c h u

Fiu. 2-19 Generador de bit de paridad para el problema de secuencia de pulsos

Solucibn:

Las salidas (P) para el generador de bit de paridad par de la figura 2-19 son como sigue:

a) pulso a = 1 c) pulso c = 0 e) pulso e = 1 g) pulso g = 1

b) pulso b = 0 d) pulso d = 0 pulso f = 1 h) pulso h = 0

2.28 Consulte la figura 2-15. Si la palabra de datos es 001 1 ( D7=0, D, = 0, D, = 1, D, = l), 10s bit

de paridad serlan P4 =

, p2 = Y PI =

Solucibn:

Cuando la palabra de datos en la figura 2-15 es 001 1,los bit de paridad son P4 = 1, P, = 1 y PI = 0.

2.29 Consulte la figura 2-15 cuando sale 01 1001 1 (D, = 0, PI = 1) de la linea de transmisibn, 10s in-

dicadores de error serttn E, =

. Ez = Y El =

Solucibn:

Al salir 01 1001 1 de la linea de transmisibn en la figura 2-15, 10s indicadores de error serhn E, = 0, El

= OyE1 = 0.

30 C6DIGOS BINARIOS ICAP.2

2.30 (si, no) hubo error en la transmisi6n en el problem anterior.

-

Solucl6n:

No hubo error durante la transmisi6n en el problema anterior.

-

2.31 Consulte la figura 2-15. Cuando sale OOlOlOU (D, = 0 del extremo izquierdo) de la Linea de

transmisi6n, 10s indicadores de error seriin E, =

. E2 = YEL =

Cuando sale OOIOIOO de la llnea de transmisibn en la figura 2-15,los indicadores de error seran E, =

1 , E, = 1 Y E , = 0.

A.

2.32 iCuiil bit estaba equivocado en el problema anterior?

Solucl6n:

El bit de datos 6 (D,) estaba equivocado y debi6 ser cambiado de 0 a 1.

-

2-6 C~ DI GOS ALFANUMERICOS

Se han usado 1 y 0 binarios para representar diferentes numeros. Los bit pueden ser codificados tambikn

para representar letras del alfabeto, numeros y signos de puntuacibn. Uno de estos cbdigos, de 7 bit, es

el American Standard Code for Information Interchange (ASCII, se pronuncia "aski"), se muestra en

la figura 2-20. Note que la letra A se representa como 1000001 en tanto que B es 1000010. El cbdigo AS-

Fig. 2-20 Cbdigos alfanumkricos

Carlcter

Espacio

I

i#

S

76

&

(

1

*

+

1

0

1

7

3

4

5

6

7

8

9

ASCII

010 OW0

010 OOOI

010 0010

010 0011

010 0100

010 0101

010 0110

010 0111

010 loo0

010 1001

010 1010

010 1011

010 1100

010 1101

010 1110

010 1 1 1 1

011 0000

011 OOO1

011 0010

011 0011

011 0100

011 0101

011 0110

011 0111

011 loo0

011 1001

EBCDIC

I 0100 0000

0101 1010

0111 1111

0111 1011

0101 1011

0110 1100

0101 0000

0111 1101

0100 1101

0101 1101

0101 1100

0100 1110

0110 1011

01 10 0000

0100 1011

01 10 0001

1 1 1 1 0000

1 1 1 1 0001

1 1 1 1 0010

1 1 1 1 0011

1 1 1 1 0100

1 1 1 1 0101

1111 0110

1 1 1 1 0111

1111 lo00

1 1 1 1 1001

Caracter ASCII EBCDIC

1100OOO1