Professional Documents

Culture Documents

Features General Description: Advanced Dual PWM and Dual Linear Power Controller

Uploaded by

behzadOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Features General Description: Advanced Dual PWM and Dual Linear Power Controller

Uploaded by

behzadCopyright:

Available Formats

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 1

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain

the latest version of relevant information to verify before placing orders.

Advanced Dual PWM and Dual Linear Power Controller

Provides 4 Regulated Voltages

Microprocessor Core , I/O , Clock Chip and

GTL Bus

Simple Single-Loop Control Design

Voltage-Mode PWM Control

Fast Transient Response

High-Bandwidth Error Amplifier

Full 0% to 100% Duty Ratio

Excellent Output Voltage Regulation

Core PWM Output : 1% Over Temperature

I/O PWM Output : 2% Over Temperature

Other Output : 2.5% Over Temperature

Power-Good Output Voltage Monitor

Microprocessor Core Voltage Protection Against

Shorted MOSFET

Over-Voltage and Over-Current Fault Monitors

Small Converter Size

Constant Frequency Operation

200kHz Free-Running Oscillator ;

Programmagle from 50kHz to 800kHz

Features General Description

The APW3007 provides the power control and pro-

tection for four output voltage in high-performance mi-

croprocessor and computer applications.

The APW3007 is designed to provide termination

voltage VTT(1.25V) with 1% accuracy.

It integrates two PWM controllers , a linear regulator

and a liear controller as well as the monitoring and

protection function into a single package. One PWM

controller regulates the microprocessor core voltage

with a synchronous-rectified buck converter , while the

second PWM controller supplies the I/O 3.3V power

with a standard buck converter. The linear controller

regulates power for GTL bus and the intermal 200mA

regulator for clock driver circuits.

The APW3007 can provide in excess of 14A of out-

put current for an on-board DC/DC converter via in-

ternal reference voltage. It can monitor all the output

voltage , and a single Power Good signal is issued

when the core is within 10% of the internal reference

voltage and the other levels are above their under-

voltage levels. Additional built-in over-voltage protec-

tion for the core output uses the lower MOSFET to

prevent output voltage above 115% of the reference

voltage. The PWM controllers over-current function

monitor the output current by sensing the voltage drop

across the upper MOSFETs R

DS(ON)

, eliminating the

need for a current sensing resistor.

Applications

Motherboard Power Regulation for Computers

Low-Voltage Distributed Power Supplies

VGA Card Power Regulation

Termination Voltage

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 2

Ordering and Marking Information

Pin Description

PHASE2

NC

NC

NC

LGATE1

OCSET1

VSEN1

NC

NC

PGOOD

V5

PGND

FB1

FB3

VSEN2

GND

1

2

3

4

5

6

7

8

12

11

10

9

24

23

22

21

NC

GATE3

PHASE1

FB2

SS

FAULT

NC

13

14

25

26

27

28

20

19

18

17

16

15

UGATE2

UGATE1

V12

OCSET2

NC

PHASE2

NC

NC

NC

LGATE1

OCSET1

VSEN1

NC

NC

PGOOD

V5

PGND

FB1

FB3

VSEN2

GND

1

2

3

4

5

6

7

8

12

11

10

9

24

23

22

21

NC

GATE3

PHASE1

FB2

SS

FAULT

FB4

13

14

25

26

27

28

20

19

18

17

16

15

UGATE2

UGATE1

V12

OCSET2

Vout4

APW3007-12 APW3007-13

APW3007

Voltage Code

12 : 1.25V 13 : 1.30V

Package Code

K : SOP - 28

Temp. Range

C : 0 to 70 C

Handling Code

TU : Tube TR : Tape & Reel

Handling Code

Temp. Range

Package Code

Voltage Code

APW3007 K :

APW3007

XXXXX

XXXXX - Date Code

Absolute Maximum Ratings

Symbol Parameter Rating Unit

V12 Supply Voltage 15 V

V

I

, V

O

Input , Output or I/O Voltage GND -0.3 V to V12 +0.3 V

T

A

Operating Ambient Temperature Range 0 to 70 C

T

J

Junction Temperature Range 0 to 125 C

T

STG

Storage Temperature Range -65 to +150 C

T

S

Soldering Temperature 300 ,10 seconds C

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 3

Thermal Characteristics

Symbol Parameter Value Unit

R

JA

Thermal Resistance in Free Air

SOIC

SOIC (with 3in

2

of Copper)

75

65

C/W

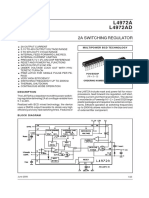

Block Diagram

GATE

CONTROL

SOFT-START

AND FAULT

LOGIC

THERMAL

PROTECTION

GATE

CONTROL

POWER-ON

RESET

FB3

GATE3

OCSET2

UGATE2

PHASE2

FB2

VSEN2

GND

PGND

LGATE1

PHASE1

UGATE1

PGOOD

V12 OCSET1

FB1 SS FAULT

0.3V 1.26V

200uA

VCC

DRIVE2 OC2

INHIBIT

PWM2

2.0V

ERROR

AMP2

2.5V 4.3V

VREF

OSCILLATOR

3.3K

4.6V

ERROR

AMP1

0V

FAULT

OC1

PWM1

VCC

LOWER

DRIVE

VCC

DRIVE1

INHIBIT

115%

90%

110%

200uA

LUV

VSEN1 V5

VOUT4

FB4

0.3V

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 4

Electrical Characteristics

(Recommended operating conditions , Unless otherwise noted) Refer to Block and Simplified Power System

Diagrams , and Typical Application Schematic.

APW3007

Symbol Parameter Test Conditions

Min Typ Max

Unit

Supply UVLO Section

UVLO Threshold-12V Supply ramping up 9.5 V

UVLO Hysterises-12V 0.5 V

UVLO Threshold-5V Supply ramping up 4.3 V

UVLO Hysterises-5V 0.3 V

Supply Current

I

12

V12 6

I

5

Nominal Supply Current

V5 2

mA

Oscillator

F

OCS

Free Running Frequency RT= Open 185 200 215 kHz

V

OSC

Ramp Amplitude RT= Open 1.9 V

P-P

Switching Controller Reference Voltage

1.25

V

REF

Reference Voltage

APW3007-12

APW3007-13 1.30

V

Reference Voltage accuracy 1.0 +1.0 %

VFB2 Output Voltage 2 V

VFB2 Voltage Accuracy -2 +2 %

2.5V Regulator (Vout4)

Vo4 Reference Voltage T

A

=25 , Vout4=FB4 1.26 V

Dropout Voltage Io=200mA 0.6 V

Load Regulation 1mA<Io<200mA 0.5 %

Line Regulation 3.1V<VIO<4V , Vo=2.5V 0.2 %

Input bias Current 2 A

Output Current 200 mA

Current Limit 300 420 mA

Thermal Shutdown 150 C

1.5V Regulator (Vout3)

Vo3 Reference Voltage T

A

=25 , GATE=FB3 1.26 V

Reference Voltage Accaracy -2.5 +2.5 %

Input bias current 2 A

Output Drive Current 50 mA

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 5

Electrical Characteristics Cont.

APW3007

Symbol Parameter Test Conditions

Min Typ Max

Unit

Synchronous PWM Controller Error Amplifier

DC Gain 88 dB

GBWP Gain-Bandwidth Product 15 MHz

SR Slew Rate COMP1 = 10pF 6 V/S

PWM Controller Gate Drive

I

UGATE

UGATE Source V12 = 12V , V

UGATE

= 6V 1 A

R

UGATE

UGATE Sink V

UGATE-PHASE

=1V 3.5

I

LGATE

LGATE Source V12 = 12V , V

LGATE

= 1V 1 A

R

LGATE

LGATE Sink V

LGATE

= 1V 3

Protection

VSEN1 O.V. Upper trip point VSEN1 ramping up 117 %

VSEN1 O.V. lower trip point VSEN1 ramping down 115 %

I

OVP

FAULT Souring Current V

FAULT/RT

=2.0V 8.5 mA

I

OCSET

OCSET Current Source V

OCSET

=4.5V

DC

170 200 230 A

R

SS

Pull up resistor to 5V OCSET=0V , Phase=5V 23 K

Power Good

VSEN1

Upper Threshold VSEN1 Rising 110 %

VSEN1

Under Voltage VSEN1 Rising 94 %

VSEN1

Hysteresis Upper /Lower Threshold 2 %

V

PGOOD-L

PGOOD Voltage Low RL = 3mA 0.4 V

V

PGOOD-H

PGOOD Voltage High RL = 5k Pull up to 5V 4.8 V

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 6

UGATE2 (Pin1)

Connect this pin to the gate of an external MOSFET.

This pin provides the drive for the regulators pass tran-

sistor .

PHASE1 , PHASE2 (Pin26 and 2)

Connect the PHASE pins to the respective PWM

converters upper MOSFET source. These pins are

used to monitor the voltage drop across the upper

MOSFETs for over-current protection .

NC (Pin 3,4,5,6,7,20)

No connection.

PGOOD (Pin8)

PGOOD is an open collector output used to indicate

the status of the output voltages. This pin is pulled

low when the synchronous regulator output is not within

10% of the DACOUT reference voltage or when any

of the other outputs are below their under-voltage

thresholds .

OCSET1 , OCSET2 (Pin23 and Pin9)

Connect a resistor (R

OCSET

) from this pin to the drain of

the respective upper MOSFET. R

OCSET

, an internal

200A current source (I

OCSET

) , and the upper

MOSFETs on-resistance (r

DS(ON)

) set the converter

over-current (OC) trip point according to the following

equation :

I

P E A K

=

DS(ON)

OCSET OCSET

r

R I x

FB2 (Pin10)

This pin provides the feedback for the non-synchro-

nous switching regulator. A resistor driver is con-

nected from this pin to vout2 and GND that sets the

output voltage. The value of the resistor connected

from Vout2 to FB2 must be less than 100 .

V5 (Pin11)

5V supply voltage. A high frequency capacitor (0.1

to 1uF) must be placed close to this pin and con-

nected from this pin to the GND plane for noise free

operation.

SS (Pin12)

This pin provides the soft start for the 2 switching

regulators. An internal resistor charges an external

capacitor that is connected from 5V supply to this pin

which ramps up the outputs of the switching regula-

tors , preventing the outputs from overshooting as well

as limiting the input current. The second function of

the Soft Start cap is to provides long off time for the

synchronoud MOSFET during current limiting .

FAULT (Pin13)

This pin has dual function. It acts as an output of the

OVP cicuitry or it can be used to program the fre-

quency using an extermal resistor. When used as a

fault detector , if any of the switcher outputs exceed

the OVP trip point , the FAULT pin switches to 12V

and the soft start cap is discharged. If the FAULT pin

is to be connected to any external circuity , it needs

to be buffered as shown in the application circuit .

FB4 (Pin14)

APW3007-12 : NC

This pin provides the feedback for the internal LDO

regular that its ourpur is Vout4.

VSEN2 (Pin15)

This pin is connected to the output of the I/O switch-

ing regulator. It is an input that provides sensing for

the Under/Over voltage circuitry for the I/O supply as

well as the power for the internal LDO regulator .

VOUT4 (Pin16)

Functional Pin Description

APW3007-12 : NC

This pin is the output of the internal LDO regulator.

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 7

PGND (Pin 24)

This is the power ground connection . Tie the syn-

chronous PWM converters lower MOSFET source

to this pin .

LGATE (Pin 25)

Connect LGATE to the PWM converters lower

MOSFET gate . This pin provides the gate drive for

the lower MOSFET .

UGATE (Pin 27)

Connect UGATE pin to the PWM converters upper

MOSFET gate . This pin provides the gate drive for

the upper MOSFET .

V12 (Pin28)

Provide a 12V bias supply for the IC to this pin . This

pin also provides the gate bias charge for all the

MOSFETs controlled by the IC . The voltage at this

pin is monitored for Power-On Reset purposes .

Simplified Power System Diagram

GND (Pin 17)

Signal ground for the IC. All voltage levels are

measured with respect to this pin.

GATE3 (Pin 18)

Connect this pin to the gate of an external MOSFET.

This pin provides the drive for the 1.5V regulators

pass transistor.

FB3 (Pin 19)

Connect this pin to the output of the 1.5V linear

regulator. This pin is monitored for under-voltage

events.

FB1 (Pin21)

This pin provides the feedback for the synchronous

switching regulator . Typically this pin can be con-

nected directly to the output of the switching regula-

tor . However , a resistor driver is recommended to

be connected from this pin to vout1 and GND to ad-

just the output voltage for any drop in the output volt-

age that is caused by the trace resistance . The value

of the resistor connected from Vou1 to FB1 must be

less than 100 .

PWM2

Controller

Linear

Controller

PWM1

Controller

5V

CIN

COUT

CIN

COUT

L2

L1

NVVDD

VTT

3.3V

CIN COUT

3.3V

FBVDDQ

Linear

Regulator

VOUT4

Functional Pin Description (Cont.)

VSEN1 (Pin 22).

This pin is connected to the PWM converters output

voltage . The PGOOD and OVP comparator circuits

use this signal to report output voltage status and for

over-voltage protection .

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 8

Typical Application Circuit

UGATE2

NC

NC

NC

NC

PHASE2

V5

FB2

PGOOD

NC

OCSET2

NC

FAULT

SS

VSEN2

NC

OCSET1

VSEN1

FB1

FB3

GATE3

GND

NC

PHASE1

LGATE1

PGND

UGATE1

V12

1

14

13

12

11

10

9

8

7

6

5

4

3

2

28

18

19

20

21

22

23

24

25

26

27

15

17

16

5V

NVVDD

2.05V/4A

VTT

1.25V/3.5A

AGP

3.3V

12V

5V

AGP

3.3V

FBVDDQ

2.5V/1.5A

C807

330uF

C808

1000uF

R812

1.5k

C809

220pF

R813

5.1R

Q802

APM9410

D800

FM5820

C811

330uF

R814

100RF

C810

330uF

R816

4.02KF

C800

10uF

C804

1uF

C805

1uF

R810

97.6RF

C817

330uF

Q800

APM3055

C802

330uF

R821

100R

R820

5.1R

Q803B

APM7313

C815

330uF

C816

330uF

C814

10uF

C813

330uF

L802

2uH

L803

7.8uH

Q803A

APM7313

C812

220pF

R817

1.2K

R819

5.1R

C801

1uF

RX1

10R

L801

7.8uH

L800

2uH

APW3007-12

R811

100RF

UGATE2

NC

NC

NC

NC

PHASE2

V5

FB2

PGOOD

NC

OCSET2

FB4

FAULT

SS

VSEN2

NC

OCSET1

VSEN1

FB1

FB3

GATE3

GND

Vout4

PHASE1

LGATE1

PGND

UGATE1

V12

1

14

13

12

11

10

9

8

7

6

5

4

3

2

28

18

19

20

21

22

23

24

25

26

27

15

17

16

5V

NVVDD

2.05V/4A

VTT

1.25V/3.5A

AGP

3.3V

12V

5V

AGP

3.3V

FBVDDQ

2.5V/1.5A

C807

330uF

C808

1000uF

R812

1.5k

C809

220pF

R813

5.1R

Q802

APM9410

D800

FM5820

C811

330uF

R814

100RF

C810

330uF

R816

4.02KF

C800

10uF

C804

1uF

C805

1uF

R810

97.6RF

C817

330uF

Q800

APM3055

C802

330uF

R821

100R

R820

5.1R

Q803B

APM7313

C815

330uF

C816

330uF

C814

10uF

C813

330uF

L802

2uH

L803

7.8uH

Q803A

APM7313

C812

220pF

R817

1.2K

R819

5.1R

C801

1uF

RX1

10R

L801

7.8uH

L800

2uH

APW3007-13

R811

100RF

APW3007-12

APW3007-13

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 9

Package Information

SO 300mil ( Reference JEDEC Registration MS-013)

Millimeters Variations- D Inches Variations- D

Dim

Min. Max. Variations Min. Max.

Dim

Min. Max. Variations Min. Max.

A 2.35

2.65

SO-16

10.10 10.50

A 0.093 0.1043 SO-16 0.398 0.413

A1

0.10 0.30

SO-18

11.35 11.76

A1 0.004 0.0120 SO-18 0.447 0.463

B

0.33 0.51

SO-20

12.60 13

B 0.013 0.020 SO-20 0.496 0.512

D See variations SO-24

15.20 15.60

D See variations SO-24 0.599 0.614

E

7.40 7.60

SO-28

17.70 18.11

E 0.2914 0.2992 SO-28 0.697 0.713

e 1.27BSC SO-14

8.80 9.20

e 0.050BSC SO-14 0.347 0.362

H

10 10.65

H 0.394 0.419

L

0.40 1.27

L 0.016 0.050

N See variations N See variations

1 0 8 1 0 8

N

1 2 3

E

D

L

GAU

PLA

e B

A1

A

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 10

Classification Reflow Profiles

Package Reflow Conditions

Refolw Condition (IR/ Convection or VPR Reflow)

Physical Specifications

Terminal Material Solder-Plated Copper (Solder Material : 90/10 or 63/37 SnPb)

Lead Solderability Meets EIA Specification RSI86-91, ANSI/J-STD-002 Category 3.

Packaging 1000 devices per reel

Convection or IR/ Convection VPR

Average ramp-up rate(183C to Peak) 3C/second max. 10 C /second max.

Preheat temperature 125 25C) 120 seconds max.

Temperature maintained above 183C 60 ~ 150 seconds

Time within 5C of actual peak

temperature

10 ~ 20 seconds 60 seconds

Peak temperature range 220 +5/-0C or 235 +5/-0C 215~ 219C or 235 +5/-0C

Ramp-down rate 6 C /second max. 10 C /second max.

Time 25C to peak temperature 6 minutes max.

pkg. thickness 2.5mm

and all bags

pkg. thickness < 2.5mm and

pkg. volume 350 mm

pkg. thickness < 2.5mm and pkg.

volume < 350mm

Convection 220 +5/-0 C Convection 235 +5/-0 C

VPR 215-219 C VPR 235 +5/-0 C

IR/Convection 220 +5/-0 C IR/Convection 235 +5/-0 C

Reference JEDEC Standard J-STD-020A APRIL 1999

Pre-heat temperature

183 C

Peak temperature

Time

t

e

m

p

e

r

a

t

u

r

e

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 11

Tape & Reel Dimensions

Reliability test program

Test item Method Description

SOLDERABILITY MIL-STD-883D-2003 245C , 5 SEC

HOLT MIL-STD-883D-1005.7 1000 Hrs Bias @ 125 C

PCT JESD-22-B, A102 168 Hrs, 100 % RH , 121C

TST MIL-STD-883D-1011.9 -65C ~ 150C, 200 Cycles

ESD MIL-STD-883D-3015.7 VHBM > 2KV, VMM > 200V

Latch-Up JESD 78 10ms , I

tr

> 100mA

Application A B C J T1 T2 W P E

3301 62 1.5

12.75 0.

5

2 0.6 24.4 0.2 2 0.2 24 0.3 12 0.1 1.75 0.1

F D D1 Po P1 Ao Bo Ko t SOP- 28

11.5 0.1 1.5 +0.1 1.5+ 0.25 4.0 0.1 2.0 0.1 10.85 0.118.34 0.1 2.97 0.1 0.350.01

t

Ao

E

W

Po

P

Ko

Bo

D1

D

F

P1

A

J

B

T2

T1

C

Copyright ANPEC Electronics Corp.

Rev. A.5 - Jun., 2003

APW3007

www.anpec.com.tw 12

Cover Tape Dimensions

Customer Service

Anpec Electronics Corp.

Head Office :

5F, No. 2 Li-Hsin Road, SBIP,

Hsin-Chu, Taiwan, R.O.C.

Tel : 886-3-5642000

Fax : 886-3-5642050

Taipei Branch :

7F, No. 137, Lane 235, Pac Chiao Rd.,

Hsin Tien City, Taipei Hsien, Taiwan, R. O. C.

Tel : 886-2-89191368

Fax : 886-2-89191369

Application Carrier Width Cover Tape Width Devices Per Reel

SOP- 28 24 21.3 1000

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

You might also like

- HS8108Document8 pagesHS8108Miloš ZorićNo ratings yet

- Ltc1629/Ltc1629-Pg Polyphase, High Efficiency, Synchronous Step-Down Switching RegulatorsDocument28 pagesLtc1629/Ltc1629-Pg Polyphase, High Efficiency, Synchronous Step-Down Switching Regulatorscatsoithahuong84No ratings yet

- Up7706 DatasheetDocument12 pagesUp7706 DatasheetFernando DupuyNo ratings yet

- Datasheet AP1513Document7 pagesDatasheet AP1513timigoNo ratings yet

- FAN7930BDocument22 pagesFAN7930Bpagy snv100% (1)

- BM2596Document9 pagesBM2596Anton AdrianNo ratings yet

- Ap5002 - PWM Control 2a Step-Down ConverterDocument10 pagesAp5002 - PWM Control 2a Step-Down ConverterAmador Garcia IIINo ratings yet

- RT9214Document17 pagesRT9214levimolnarNo ratings yet

- APW7159ADocument23 pagesAPW7159AVoicu AdrianNo ratings yet

- APW7120Document22 pagesAPW7120nishatiwari82No ratings yet

- LM2621Document12 pagesLM2621nad_chadi8816No ratings yet

- Datasheet PJ494Document11 pagesDatasheet PJ494Achmad Rifdatul HisanNo ratings yet

- A 2918 SW Data SheetDocument8 pagesA 2918 SW Data SheetGustavo LunaNo ratings yet

- OB2269Document12 pagesOB2269Juan Ballon100% (1)

- Single Synchronous Buck PWM DC-DC ControllerDocument16 pagesSingle Synchronous Buck PWM DC-DC Controllerbachet56No ratings yet

- STRW6252Document15 pagesSTRW6252miltoncgNo ratings yet

- TSM 101Document15 pagesTSM 101thiemncNo ratings yet

- 3000W Single Output Power Supply Spec SheetDocument6 pages3000W Single Output Power Supply Spec SheetGrigoriu CodrutaNo ratings yet

- Datasheet sg6105dDocument13 pagesDatasheet sg6105dCartman SantosNo ratings yet

- Feature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerDocument11 pagesFeature General Description: HT7A6005 Low Power, Wide Temperature Range General Purpose Current Mode PWM ControllerEnéas BaroneNo ratings yet

- XX3842 Series FunctionDocument7 pagesXX3842 Series FunctionbernabethNo ratings yet

- FP 6321Document11 pagesFP 6321Ahmed HussainNo ratings yet

- Application Note AN4121: Design of Power Factor Correction Circuit Using FAN7527BDocument22 pagesApplication Note AN4121: Design of Power Factor Correction Circuit Using FAN7527BRicardo VieiraNo ratings yet

- Apl 5336Document20 pagesApl 5336FlavianoSilvaNo ratings yet

- Data SheetDocument9 pagesData SheetLesseigne Marie-ClaireNo ratings yet

- 3000W Single Output Power Supply: SeriesDocument7 pages3000W Single Output Power Supply: SeriesAlexander PekarovskiyNo ratings yet

- SG6105 Datasheet, Pinout, Application Circuits Power Supply Supervisor Regulator PWMDocument13 pagesSG6105 Datasheet, Pinout, Application Circuits Power Supply Supervisor Regulator PWMBeatrizEstevesNo ratings yet

- 60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsDocument14 pages60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsIBSDIALLO0% (1)

- Wide Input Voltage 3.0 A Step Down Regulator: Features and Benefits DescriptionDocument10 pagesWide Input Voltage 3.0 A Step Down Regulator: Features and Benefits Descriptioncdan99No ratings yet

- AZ3842 PWM Controller Data Sheet SummaryDocument13 pagesAZ3842 PWM Controller Data Sheet SummaryEngr Khalid IqbalNo ratings yet

- TC120 PWM/PFM Step-Down Combination Regulator/Controller: Features General DescriptionDocument12 pagesTC120 PWM/PFM Step-Down Combination Regulator/Controller: Features General DescriptionRijal SaifurNo ratings yet

- Thb7128 InstructionsDocument9 pagesThb7128 InstructionsanhxcoNo ratings yet

- Fan 6961Document13 pagesFan 6961Ariel NavarreteNo ratings yet

- Datasheet PDFDocument15 pagesDatasheet PDFperro sNo ratings yet

- Data SheetDocument7 pagesData Sheetitamar_123No ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- FAN7602B Green Current-Mode PWM Controller: Features DescriptionDocument17 pagesFAN7602B Green Current-Mode PWM Controller: Features DescriptionNichole RollinsNo ratings yet

- DatasheetDocument9 pagesDatasheetnipunkhatriNo ratings yet

- AP358 DatasheetDocument13 pagesAP358 DatasheetRafael OliveiraNo ratings yet

- DRV 8811Document22 pagesDRV 8811nelson_loboNo ratings yet

- EN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated InductorDocument16 pagesEN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated Inductorcatsoithahuong84No ratings yet

- SSC2001S Application NoteDocument18 pagesSSC2001S Application NoteGerardo Mendez CamarilloNo ratings yet

- AP8012 OFF-LINE SMPS SWITCHERDocument10 pagesAP8012 OFF-LINE SMPS SWITCHERShubham AdkeNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- L4972ADocument23 pagesL4972ARICHIHOTS2No ratings yet

- KA7500 DatasheetDocument6 pagesKA7500 DatasheetSergio Daniel BarretoNo ratings yet

- PDFDocument8 pagesPDFanterommxNo ratings yet

- (On1Note) Fully Regulated ATX Power Supply PDFDocument28 pages(On1Note) Fully Regulated ATX Power Supply PDFBluff FlersNo ratings yet

- Description Power Range: Analog Servo DriveDocument7 pagesDescription Power Range: Analog Servo DriveElectromateNo ratings yet

- Constant Current Led DriverDocument27 pagesConstant Current Led DriverJubin JainNo ratings yet

- LB1845 DDocument9 pagesLB1845 DFernando LizarragaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Miniature magnetic field sensor FLC 100Document2 pagesMiniature magnetic field sensor FLC 100behzadNo ratings yet

- Ijarece Vol 3 Issue 3 347 350 PDFDocument4 pagesIjarece Vol 3 Issue 3 347 350 PDFbehzadNo ratings yet

- Farsi FATEk PDFDocument147 pagesFarsi FATEk PDFbehzadNo ratings yet

- Miniature Size: 7Mml 85, Standard CDocument1 pageMiniature Size: 7Mml 85, Standard CbehzadNo ratings yet

- 1N5817Document3 pages1N5817Gallego OrtizNo ratings yet

- Fravahar 2Document16 pagesFravahar 2behzadNo ratings yet

- FravaharDocument11 pagesFravaharbehzadNo ratings yet

- Low ESR polymer capacitors application guideDocument31 pagesLow ESR polymer capacitors application guidebehzadNo ratings yet

- فرهنگ چیستDocument15 pagesفرهنگ چیستJonbeshEnghelabiNo ratings yet

- Large Capacitance Aluminum Electrolytic Capacitors: S I EsDocument2 pagesLarge Capacitance Aluminum Electrolytic Capacitors: S I EsbehzadNo ratings yet

- EMRLDocument1 pageEMRLbehzadNo ratings yet

- EXR series capacitors for switching power suppliesDocument2 pagesEXR series capacitors for switching power suppliesbehzadNo ratings yet

- 99812028Document1 page99812028behzadNo ratings yet

- High Current MOSFET Polarity Switch: 126 Ridge Road - P.O. Box 187 - Lansing, NY 14882Document1 pageHigh Current MOSFET Polarity Switch: 126 Ridge Road - P.O. Box 187 - Lansing, NY 14882behzadNo ratings yet

- SGH13N60UFDDocument8 pagesSGH13N60UFDbehzadNo ratings yet

- cp3505 Error Messages PDFDocument24 pagescp3505 Error Messages PDFbehzadNo ratings yet

- CDocument14 pagesCbehzadNo ratings yet

- Chopper Regulator, DC DC Converter and Motor Drive ApplicationsDocument6 pagesChopper Regulator, DC DC Converter and Motor Drive ApplicationsbehzadNo ratings yet

- How To Solder 0902e PDFDocument26 pagesHow To Solder 0902e PDFbehzad100% (1)

- Summary - Directional Antennas Dual-Band 800/900 - 1800/2000Document30 pagesSummary - Directional Antennas Dual-Band 800/900 - 1800/2000behzadNo ratings yet

- Fuses & Fuseholders: 6.3x32mm ( "x1 ") Glass and Ceramic FusesDocument1 pageFuses & Fuseholders: 6.3x32mm ( "x1 ") Glass and Ceramic FusesbehzadNo ratings yet

- Installation Instructions SL417U Model SeriesDocument2 pagesInstallation Instructions SL417U Model SeriesbehzadNo ratings yet

- Fuses & Fuseholders: 6.3x32mm ( "x1 ") Glass and Ceramic FusesDocument1 pageFuses & Fuseholders: 6.3x32mm ( "x1 ") Glass and Ceramic FusesbehzadNo ratings yet

- Robot3 PDFDocument8 pagesRobot3 PDFbehzadNo ratings yet

- Tweezer Style Passive Component R/C SMD: One-Hand OperationDocument1 pageTweezer Style Passive Component R/C SMD: One-Hand OperationbehzadNo ratings yet

- Remanufacturing Instructions: HP Color Laserjet 3000/3600/3800Document9 pagesRemanufacturing Instructions: HP Color Laserjet 3000/3600/3800behzadNo ratings yet

- High Power Resistors for Industrial ApplicationsDocument3 pagesHigh Power Resistors for Industrial ApplicationsbehzadNo ratings yet

- Smart Tweezers Manual ST5 PDFDocument16 pagesSmart Tweezers Manual ST5 PDFbehzadNo ratings yet

- Avr Family PDFDocument6 pagesAvr Family PDFbehzadNo ratings yet

- ModelbjtDocument19 pagesModelbjtSuraj KamyaNo ratings yet

- Navigation - Korea VolumeDocument9 pagesNavigation - Korea VolumeDraggon FNNo ratings yet

- Moder Dance Book - 2nd EditionDocument119 pagesModer Dance Book - 2nd EditionLinoraD2180% (10)

- Folk CultureDocument8 pagesFolk CultureArpita DasNo ratings yet

- Letra Sia CancionesDocument14 pagesLetra Sia CancionesSamuel BarriosNo ratings yet

- Discussed Last Time: QCI ARP GBR MBR Apn-Ambr Ue-AmbrDocument4 pagesDiscussed Last Time: QCI ARP GBR MBR Apn-Ambr Ue-AmbrAditya RajNo ratings yet

- Escape From Nowhere EP ReviewDocument1 pageEscape From Nowhere EP ReviewMarty ThompsonNo ratings yet

- Guidelines on Telecom Mast InstallationDocument39 pagesGuidelines on Telecom Mast InstallationOkpara Chibuike James100% (1)

- Hamlet Study Questions 2013 PDFDocument4 pagesHamlet Study Questions 2013 PDFAnonymous 2VcHOTitERNo ratings yet

- Issue 6, Number 33, Date: Friday 23rd July, School WebsiteDocument3 pagesIssue 6, Number 33, Date: Friday 23rd July, School Websitelaceyteresa21No ratings yet

- DissertationDocument205 pagesDissertationPierre Renaud100% (1)

- New Song Book For Dzire PLUS & DzireDocument17 pagesNew Song Book For Dzire PLUS & DzireMukund SidhayeNo ratings yet

- Rotor Stress EvaluatorDocument5 pagesRotor Stress EvaluatorE.C.MADHUDUDHANA REDDYNo ratings yet

- Top 12 Duties of a Mother and Their ImpactDocument5 pagesTop 12 Duties of a Mother and Their ImpactRinkashimeLaizTejeroNo ratings yet

- Acoustic Magazine Issue 50Document2 pagesAcoustic Magazine Issue 50Acoustic Magazine0% (2)

- Proko sonate orchestra scoreDocument5 pagesProko sonate orchestra scoreYardi ViolonNo ratings yet

- PhrasingDocument5 pagesPhrasingdeeceegeeNo ratings yet

- Houston VTS User GuideDocument69 pagesHouston VTS User GuideThomas W. HudsonNo ratings yet

- The Gauntlet Thrown-Complete BookDocument353 pagesThe Gauntlet Thrown-Complete BookXC PublishingNo ratings yet

- Suite Francesa em CM Bach - Menuet AnalisadoDocument6 pagesSuite Francesa em CM Bach - Menuet AnalisadoMayara Confortini MachadoNo ratings yet

- Demi Lovato Lyrics - Gift of A FriendDocument3 pagesDemi Lovato Lyrics - Gift of A FriendArlen RojasNo ratings yet

- Personal Recollections and Experiences Concerning The Battle of Stone River by Hascall, Milo S., 1829-1904Document18 pagesPersonal Recollections and Experiences Concerning The Battle of Stone River by Hascall, Milo S., 1829-1904Gutenberg.orgNo ratings yet

- Spirit of New Orleans ProductionsDocument2 pagesSpirit of New Orleans ProductionsKatja ToivolaNo ratings yet

- List of Set ClassesDocument2 pagesList of Set ClassesAnonymous zzPvaL89fGNo ratings yet

- Permission To Dance (R&B Remix)Document1 pagePermission To Dance (R&B Remix)Azcha MardlotillahNo ratings yet

- Cinderella Risk Assessment FormDocument10 pagesCinderella Risk Assessment Formapi-356127106No ratings yet

- Mcdu Operators GuideDocument313 pagesMcdu Operators GuideAyan Acharya100% (1)

- Mototrbo RDSMDocument410 pagesMototrbo RDSMDavid VelasquezNo ratings yet

- Song Study Outline: Comme L'allodolettaDocument4 pagesSong Study Outline: Comme L'allodolettaAlli ANo ratings yet

- 3rd Periodical Exam (g9)Document4 pages3rd Periodical Exam (g9)Elmar Dela TorreNo ratings yet