Professional Documents

Culture Documents

Digital Logic Design No 6 Counters and Registers

Uploaded by

Jagan RajendiranCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Logic Design No 6 Counters and Registers

Uploaded by

Jagan RajendiranCopyright:

Available Formats

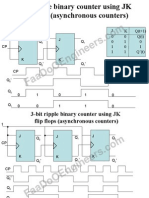

2-bit ripple binary counter using JK

flip flops (asynchronous counters)

K Q(t+1)

0

0

1

1

0

1

0

1

Q(t)

0

1

Q(t)

J

K

J

K

Q

1

Q

1

Q

0

Q

0

1

CP

CP

J

Q

0

Q

0

Q

1

0

0

1

0

0

1

1

1

0

0

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

3-bit ripple binary counter using JK

flip flops (asynchronous counters)

J

K

J

K

Q

1

Q

1

Q

0

Q

0

1

CP

J

K

Q

2

Q

2

Q

0

Q

0

CP

Q

1

Q

2

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

Simple Registers

No external gates.

Example: A 4!it register. A ne" 4!it #ata is loa#e#

on e$er% &lo&' &%&le.

A

4

A

3

A

2 A

1

I

4

I

3

I

2

I

1

CP

!

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

4-bit register with parallel load

Load

Clear

CP

"

"

"

"

#

#

#

#

I

1

I

2

I

3

I

4

A

1

A

2

A

3

A

4

((ontrol Signal)

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

Register "it) *arallel +oa# ,sing - .lip

.lops

!

!

!

!

Load

Clear

CP

I

1

I

2

I

3

I

4

A

1

A

2

A

3

A

4

$oa% A

1

& $oa% I

1

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

'sing #egisters to i(ple(ent "e)uential

Circuits

/

A se01ential &ir&1it ma% &onsist o2 a register (memor%) an# a

&om!inational &ir&1it.

Nextstate $al1e

/

3)e external inp1ts an# present states o2 t)e register #etermine

t)e next states o2 t)e register an# t)e external o1tp1ts4 t)ro1g)

t)e &om!inational &ir&1it.

/

3)e &om!inational &ir&1it ma% !e implemente# !% an% o2 t)e

met)o#s &o$ere# in 5S6 &omponents an# *rogramma!le

+ogi& -e$i&es.

Combinational

Circuit

Register

Inputs

Outputs

Clock

Pulse

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

,sing Registers to implement

Se01ential (ir&1its

/

*+a(ple 1: -esign a Se01ential (ir&1it ")ose state ta!le is gi$en !elo" 1sing t"o 2lip2lops.

A

1

+

7 8 m(449) 7 A

1

. x

:

A

;

+

7 8 m(14;4<49) 7 A

;

.x: + A

:

;

.x 7 A

;

x

% 7 8 m(=4>) 7 A

;

.x

Present

State

A

1

A

2

Input

Next

State

A

1

+

A

2

+

x

Output

y

"tate ,able

1 0 0 1 1 1

0 1 1 0 1 1

0 1 0 1 0 1

0 0 1 0 0 1

1 0 0 1 1 0

0 1 0 0 1 0

0 1 0 1 0 0

0 0 0 0 0 0

A

1

- +.

A

2

+

x

y

$ogic !iagra(

"e)uential Circuit I(ple(entation

A1

A2

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

,sing Registers to implement Se01ential

(ir&1its

/

Example ;: Repeat example 14 !1t 1se a R?5 @Register.

A%%ress /utputs

1 2 3 1 2 3

A

1

A

2

+ A

1

A

2

y

0 0 0 0 0 0

0 0 1 0 1 0

0 1 0 0 1 0

0 1 1 0 0 1

1 0 0 1 0 0

1 0 1 0 1 0

1 1 0 1 1 0

1 1 1 0 0 1

R?5 tr1t) ta!le

1 1

2 2

3 3

A

1

A

2

8 X 3

ROM

!

Sequential circuit using a register and a ROM

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

Serial 6NASerial ?1t S)i2t Registers

"

Accepts #ata seriall! $ one bit at a time an# also

pro#uces output seriall!%

! !

!

!

C$K

"erial Input

("I)

3

"erial /utput

("/)

"hift #egister

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

"erial In1"erial /ut "hift #egisters

/

Appli&ation: Serial trans2er o2 #ata 2rom one register to anot)er.

S)i2t register A S)i2t register B

S?

S? S6

S6

(*

(lo&'

S)i2t (ontrol

(lo&'

&or#time

1011 0010

3

1

3

;

3

=

3

4

(*

S)i2t (ontrol

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

"erial In1"erial /ut "hift #egisters

Serialtrans2er example.

3iming *1lse

6nitial $al1e

A2ter 3

1

A2ter 3

2

A2ter 3

=

A2ter 3

4

S)i2t Register A

1

1

1

0

1

0

1

1

1

0

1

0

1

1

1

1

1

0

1

1

S)i2t Register B

0

1

1

0

1

0

0

1

1

0

1

0

0

1

1

0

1

0

0

1

Serial o1tp1t o2 B

0

1

0

0

1

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

Q

-

Q

-

Q

-

Q

-

'1

()*

0 1 2 3

'1

()*

0 1 2 3

'1

()*

0 1 2 3

'1

()*

0 1 2 3

A

=

A

;

A

4

A

1

6

=

6

;

6

4

6

1

Serial

inp1t 2or

s)i2tle2t

Serial

inp1t 2or

s)i2trig)t

*arallel inp1ts

*arallel o1tp1ts

(lear

(+K

S

1

S

0

2i%irectional "hift #egisters

4-bit bi%irectional shift register 3ith parallel loa%

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

Bi#ire&tional S)i2t Registers

/

4!it !i#ire&tional s)i2t register "it) parallel

loa#.

5o#e (ontrol

s

1

s

0

Register ?peration

0 0 No &)ange

0 1 S)i2t rig)t

1 0 S)i2t le2t

1 1 *arallel loa#

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

An Application-"erial A%%ition

/

5ost operations in #igital &omp1ters are #one in parallel.

Serial operations are slo"er !1t re01ire less e01ipment.

/

A serial a##er is s)o"n !elo". A A+B.

S)i2t register A

S)i2t register B

S6

S6

.A

x

%

C

S

(

Q -

(lear

1010

0111

S?

S?

External inp1t

S)i2trig)t

(*

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

S 7 x + % + Q

JQ 7 x%

KQ 7 x% 7(x+%)

*+citation table for a serial a%%er

Example: -esign a serial a##er 1sing a se01ential logi&

pro&e#1re

"it) JK 2lip2lops.

Next

State 6np1ts ?1tp1t

*resent

State

.lip2lop

inp1ts

Q x % S JQ KQ Q

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

1

0

1

1

1

0

1

1

0

1

0

0

1

0

0

0

1

D

D

D

D

D

D

D

D

1

0

0

0

Q(t) Q(t+1) J

0

0

1

1

0

1

0

1

0

1

D

D

D

D

1

0

K

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

S)i2t register A

S)i2t register B

S S?7x

S?7%

External inp1t

S)i2trig)t

(*

J

K

Q

(lear

Second form of a serial adder

S 7 x + % + Q

JQ 7 x%

KQ 7 x% 7(x+%)

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

4-bit binary ripple counter

J K Q(t+1)

0

0

1

1

0

1

0

1

Q(t)

0

1

Q(t)

3o next stage

Q J

Q J Q J Q J

1 1 1 1

(o1nt

p1lses

1 1 1 1 K K K K

A

=

A

;

A

4

A

1

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

Count se)uence for a binary ripple counter

A

4

0

0

0

0

0

0

0

0

1

A

=

0

0

0

0

1

1

1

1

0

A

;

0

0

1

1

0

0

1

1

0

A

1

0

1

0

1

0

1

0

1

0

(omplement A

1

(omplement A

1

(omplement A

1

(omplement A

1

(omplement A

1

(omplement A

1

(omplement A

1

(omplement A

1

An# so onEE

A

1

"ill go 2rom 1 to 0 an# &omplement A

;

A

1

"ill go 2rom 1 to 0 an# &omplement A

;

A

;

"ill go 2rom 1 to 0 an# &omplement A

=

A

1

"ill go 2rom 1 to 0 an# &omplement A

;

A

1

"ill go 2rom 1 to 0 an# &omplement A

;F

A

;

"ill go 2rom 1 to 0 an# &omplement A

=F

A

=

"ill go 2rom 1 to 0 an# &omplement A

4

(o1nt se01en&e (on#ition 2or &omplementing 2lip2lops

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

"tate %iagra( of a %eci(al 2C! counter

0000 0001 0010 0011 0100

1001 1000 0111 0110 0101

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

$ogic %iagra( of a 2C! ripple counter

J K Q(t+1)

0

0

1

1

0

1

0

1

Q(t)

0

1

Q(t)

Q J

Q J Q J Q J

1

1

(o1nt

p1lses

1 1 1

1

K K K

Q

4

Q

G

0 0

Q

;

0

Q

1

0

0 1 0 1

Q K

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

1 1 1 1

0 0 0 0

1

0 0

0

0

0

0

0

1

0

0

1

1

1

0

1

1

0

0

1

0

0

1

0

1

0

0

1

0

0

0

0

0

0

0

0

Timing diagram for the decimal counter

Q

1

Q

;

Q

=

Q

4

Q

<

(o1nt

p1lses

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

B(-

(o1nter

B(-

(o1nter

B(-

(o1nter

(o1nt

p1lses

10

;

#igit 10

1

#igit 10

0

#igit

0HHH 0HH 0H

Block diagram of a 3-decade decimal BCD counter

Q

1

Q

;

Q

4

Q

G

Q

1

Q

;

Q

4

Q

G

Q

1

Q

;

Q

4

Q

G

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

A

4

A

3

A

2 A

1

J K

K K K

(o1nt

ena!le

(*

3o

next

stage

J K Q(t+1)

0

0

1

1

0

1

0

1

Q(t)

0

1

Q(t)

4-bit synchronous binary counter

1

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

A

4

A

3

A

2 A

1

CP

1

,

, ,

,

'P

!o3n

4-bit up-down binary counter

3o

Next

stage

3 Q(t+1)

0

1

Q(t)

Q(t)

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

1 1 0 0 1 1 0 0 1

0 1 0 0 0 0 0 0 1

0 1 1 1 1 1 1 1 0

0 1 0 0 0 0 1 1 0

0 1 1 0 0 1 0 1 0

0 1 0 0 0 0 0 1 0

0 1 1 1 0 1 1 0 0

0 1 0 0 0 0 1 0 0

0 1 1 0 0 1 0 0 0

0 1 0 0 0 0 0 0 0

% 3Q

1

3Q

;

3Q

4

3Q

G

Q

1

Q

;

Q

4

Q

G

?1tp1t (arr% .lip2lop inp1ts (o1nt Se01en&e

,sing Kmaps4 "e get

3Q

1

71

3Q

;

7 Q

A

G

Q

1

3Q

4

7 Q

;

Q

1

3Q

G

7 Q

G

Q

1

+ Q

4

Q

;

Q

1

% 7 Q

G

Q

1

Q(t) Q(t+1) 3

0

0

1

1

0

1

0

1

0

1

1

0

!esign a 2C! counter using , flip-flops

*+citation table for a 2C! counter

4o3 logic %iagra( can be %ra3n for 2C! synchronous

counter

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

y

CP

Q

1

Q

;

Q

4

Q

G

Q

1

Q

;

Q

4

Q

G

, , , ,

1

3Q

1

71

3Q

;

7 Q

A

G

Q

1

3Q

4

7 Q

;

Q

1

3Q

G

7 Q

G

Q

1

+ Q

4

Q

;

Q

1

% 7 Q

G

Q

1

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

J

J

J

J

K

K

K

K

Count

+oa#

A

4

A

3

A

2

A

1

I

4

I

3

I

2

I

1

Clear

CP Carr!

out

Counters 3ith Parallel $oa%

4!it &o1nter "it)

parallel loa#.

,et -tate

.counting/

1 0 1

+oa# inputs * 1 1

,o C0ange 0 0 * 1

Clear to 0 * * * 0

1unction Count +oa# CP Clear

J K Q(t+1)

0

0

1

1

0

1

0

1

Q(t)

0

1

Q(t)

4!it !inar% &o1nter "it) parallel loa#

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

A

4

A

3

A

2

A

1

Count 2 1

Clear 2 1

CP

Inputs 2 0

+oa#

(a) 2inary states 05152535456

A

4

A

3

A

2

A

1

Count 2 1

Clear 2 1

CP

+oa#

(c) 2inary states 10511512513514516

A

4

A

3

A

2

A

1

Count 2 1

+oa# 2 0

CP

Clear

(b) 2inary states 05152535456

A

4

A

3

A

2

A

1

Count 2 1

Clear 2 1

CP

+oa#

(%) 2inary states 35456575859

1 0 1 0 0 0 1 1

Carr!3out

Counters 3ith Parallel $oa%

-i22erent "a%s o2 getting a 5?-9 &o1nter

I

'

I

3

I

2

I

1

I

'

I

3

I

2

I

1

I

'

I

3

I

2

I

1

I

'

I

3

I

2

I

1

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

"

#

33bit counter

Count enable

CP

CP

-tart

-top

&or#3time

control

&or#3time 2 4 pulses

,i(ing "e)uences

(a) (ir&1it -iagram

(!) Ieneration o2 a "or#time &ontrol 2or serial operations

CP

-tart

-top

Q

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

5

3

5

2

5

1

5

0

2 * '

#eco#er

23bit counter

5

0

5

1

5

2

5

3

Count

enable

-0i6t rig0t

CP

5

0

5

1

5

2

5

3

(a) ring&o1nter (initial $al1e 7 1000)

(!) (o1nter an# -e&o#er

(&) Se01en&e o2 2o1r timing signals

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

!

1

!

1

!

1

!

1

CP

A 2 C *

(a) 4-stage s3itch tail ring counter

A

1

2

1

C

1

*

1

C

1

* 1 0 0 0 9

2

1

C 1 1 0 0 8

A

1

2 1 1 1 0 7

A * 1 1 1 1 6

C *

1

0 1 1 1 4

2 C

1

0 0 1 1 3

A 2

1

0 0 0 1 2

A

1

*

1

0 0 0 0 1

An% gate re)uire%

for outputs

:lip-flop outputs

A 2 C *

"e)uence

nu(ber

b! Count

se"uence and

re"uired

decoding

F

a

a

D

o

O

E

n

g

i

n

e

e

r

s

.

c

o

m

You might also like

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Optical Computing TechnologyDocument26 pagesOptical Computing TechnologyJagan RajendiranNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Optical Computing: Saran Thampy D S7 Cse Roll No 17Document21 pagesOptical Computing: Saran Thampy D S7 Cse Roll No 17Flip FlopsNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- 10 MultitaskingDocument40 pages10 MultitaskingJagan RajendiranNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Optical Computing SystemsDocument48 pagesOptical Computing SystemsChandan BangeraNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Optical ComputingDocument18 pagesOptical ComputingJagan RajendiranNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Chapter 2Document59 pagesChapter 2Jagan RajendiranNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Ece Vi Microprocessors (10ec62) NotesDocument185 pagesEce Vi Microprocessors (10ec62) NotesJagan RajendiranNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Digital Logic Design No 6 Counters and RegistersDocument31 pagesDigital Logic Design No 6 Counters and RegistersJagan Rajendiran100% (1)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Binary Parallel AddersDocument58 pagesBinary Parallel AddersJagan RajendiranNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Block Diagram of A Sequential Logic Circuit: Combinational Circuit Memory Elements Inputs OutputsDocument51 pagesBlock Diagram of A Sequential Logic Circuit: Combinational Circuit Memory Elements Inputs OutputsJagan RajendiranNo ratings yet

- Digital IC Design EXAM05 FinalDocument7 pagesDigital IC Design EXAM05 FinalJagan RajendiranNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Digital Logic Design No 6 Counters and RegistersDocument31 pagesDigital Logic Design No 6 Counters and RegistersJagan Rajendiran100% (1)

- Booth's Algorithm - Multiplication & DivisionDocument27 pagesBooth's Algorithm - Multiplication & Divisionnaveen86% (21)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Placement Consultants Companies Agencies List Prepared by NCDocument16 pagesPlacement Consultants Companies Agencies List Prepared by NCncctrtpNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- EC2042 Embedded and Real Time Systems Lecture NotesDocument79 pagesEC2042 Embedded and Real Time Systems Lecture NotesPraveen ChellapandianNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Boolean Algebra & Logic GatesDocument45 pagesBoolean Algebra & Logic GatesJagan RajendiranNo ratings yet

- MPEG 7 OverviewDocument12 pagesMPEG 7 OverviewJagan RajendiranNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Digital and Logic Design No 3 Logic CircuitsDocument34 pagesDigital and Logic Design No 3 Logic CircuitsJagan RajendiranNo ratings yet

- Lect 08Document14 pagesLect 08Jagan RajendiranNo ratings yet

- Digital IC Design SOL05 (Corrected)Document8 pagesDigital IC Design SOL05 (Corrected)Bruno SilvaNo ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Binary Parallel AddersDocument58 pagesBinary Parallel AddersJagan RajendiranNo ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Ip Based Transport: Presentation By: Kishore R SSN College of EngineeringDocument19 pagesIp Based Transport: Presentation By: Kishore R SSN College of EngineeringJagan RajendiranNo ratings yet

- Pic MicrocontrollersDocument154 pagesPic MicrocontrollersGandy Torres TorresNo ratings yet

- Chap 15Document25 pagesChap 15Jagan RajendiranNo ratings yet

- Edwin Vlsi TestingDocument23 pagesEdwin Vlsi TestingJagan RajendiranNo ratings yet

- VLSI Presentation 1Document18 pagesVLSI Presentation 1Jagan RajendiranNo ratings yet

- Unit V Cmos Testing FinalDocument76 pagesUnit V Cmos Testing FinalJagan Rajendiran50% (2)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- CROSS TALK-Impact of Interconnect ParasiticsDocument15 pagesCROSS TALK-Impact of Interconnect ParasiticsJagan RajendiranNo ratings yet

- Digital Systems DesignDocument6 pagesDigital Systems DesignJagan RajendiranNo ratings yet

- c2900 Password Recovery 00Document8 pagesc2900 Password Recovery 00Mohammed SuhelNo ratings yet

- Minimum Outdoor Display SpecDocument5 pagesMinimum Outdoor Display SpecMohammed JifarNo ratings yet

- VHDL Experiments ListDocument1 pageVHDL Experiments ListPankul BansalNo ratings yet

- Acer Aspire E5 574 E5 574G E5 574TDocument48 pagesAcer Aspire E5 574 E5 574G E5 574TRodrigo Guedes100% (1)

- Managing ROMs RetroPie - RetroPie-Setup WikiDocument8 pagesManaging ROMs RetroPie - RetroPie-Setup WikiBobbyNo ratings yet

- EX4600-40F-AFO Datasheet: Quick SpecDocument4 pagesEX4600-40F-AFO Datasheet: Quick SpecSaid bel haj letaief100% (1)

- Lister - HW3Document3 pagesLister - HW3Jacqueline JensenNo ratings yet

- Inside 8085 AluDocument7 pagesInside 8085 AluarjunNo ratings yet

- Remote Controller Visionline 3G/4G Rfid: Installation ManualDocument39 pagesRemote Controller Visionline 3G/4G Rfid: Installation Manual1ndig0tubeNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Chapter 7 Basic Processing UnitDocument58 pagesChapter 7 Basic Processing UnitRoopa B SNo ratings yet

- Product Sheet: Software-Defined Live Production SwitcherDocument2 pagesProduct Sheet: Software-Defined Live Production SwitcherArjun VysakhNo ratings yet

- 2 - Cisco Switches Models and How To Select The Appropriate SwitchDocument22 pages2 - Cisco Switches Models and How To Select The Appropriate Switchfauzi endraNo ratings yet

- Spin It! - Designing Your Own Motor Drive and Control System (Part 2)Document1 pageSpin It! - Designing Your Own Motor Drive and Control System (Part 2)Hüseyin Murat PolaterNo ratings yet

- Axioo: (Harga Normal RP 11.499.000 Harga Special Diskon)Document9 pagesAxioo: (Harga Normal RP 11.499.000 Harga Special Diskon)Fathur RNo ratings yet

- MPMC SyllabusDocument2 pagesMPMC SyllabusKANCHARLAPALLI VENKATESH,CSE(19-23) Vel Tech, ChennaiNo ratings yet

- System Bit M340Document13 pagesSystem Bit M340ifceeae nhceNo ratings yet

- IBM DS8K VirtualizationDocument450 pagesIBM DS8K VirtualizationRL IyengarNo ratings yet

- Operating System and Computer Architecture In-Course AssignmentDocument8 pagesOperating System and Computer Architecture In-Course AssignmentchanpreetNo ratings yet

- Um10430 1 PDFDocument1,278 pagesUm10430 1 PDFKavyashreeMNo ratings yet

- PID Control and Communication in Siemens PLC Day3Document85 pagesPID Control and Communication in Siemens PLC Day3RizkiNo ratings yet

- Class 12 Computer Science Project On Telephone Directory For C++Document17 pagesClass 12 Computer Science Project On Telephone Directory For C++Jyotirmoy Bandyopadhayaya0% (3)

- Proview Datasheet - SM MDVR 401 4G - INDDocument2 pagesProview Datasheet - SM MDVR 401 4G - INDSlamat AgungNo ratings yet

- Dell LCD Monitor Schematic DiagramDocument2 pagesDell LCD Monitor Schematic Diagramchili pcgameNo ratings yet

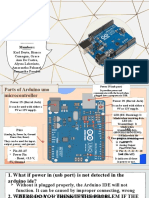

- Arduino Micro-Controller: MembersDocument3 pagesArduino Micro-Controller: MembersKarl Anzen DeytoNo ratings yet

- A Brief History of MicrocontrollersDocument2 pagesA Brief History of Microcontrollerspicupiru kanariariNo ratings yet

- 3D FinalDocument19 pages3D FinalAbrar AhmedNo ratings yet

- Terra 101-qsg PDFDocument121 pagesTerra 101-qsg PDFschmitttNo ratings yet

- Assaiment of Hardware: course:DITM BatchDocument6 pagesAssaiment of Hardware: course:DITM BatchItmahedi HasanNo ratings yet

- SMS Based Device Control Using GSM ModemDocument3 pagesSMS Based Device Control Using GSM ModemNikhil Dixit100% (1)

- NAND Flash Memories - Understanding NAND Flash Factory Pre-Programming SchemesDocument0 pagesNAND Flash Memories - Understanding NAND Flash Factory Pre-Programming SchemesBiswajit BeheraNo ratings yet