Professional Documents

Culture Documents

Microprocessors HC v2

Uploaded by

trigunu100%(1)100% found this document useful (1 vote)

46 views61 pagesThis document provides an introduction to microprocessors, including their historical background, evolution, applications, and the need for education on the topic. It discusses the development of microprocessors from the invention of the transistor in 1947 to modern devices. General purpose microprocessors are used to create computers, while special purpose and microcontroller chips are used in embedded systems. The document outlines a course on microprocessor architecture, covering topics like CPU structure, instruction sets, input/output, and timing. It also discusses administrative details of the course like labs, resources, and evaluation methods.

Original Description:

Microprocessors

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document provides an introduction to microprocessors, including their historical background, evolution, applications, and the need for education on the topic. It discusses the development of microprocessors from the invention of the transistor in 1947 to modern devices. General purpose microprocessors are used to create computers, while special purpose and microcontroller chips are used in embedded systems. The document outlines a course on microprocessor architecture, covering topics like CPU structure, instruction sets, input/output, and timing. It also discusses administrative details of the course like labs, resources, and evaluation methods.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

100%(1)100% found this document useful (1 vote)

46 views61 pagesMicroprocessors HC v2

Uploaded by

trigunuThis document provides an introduction to microprocessors, including their historical background, evolution, applications, and the need for education on the topic. It discusses the development of microprocessors from the invention of the transistor in 1947 to modern devices. General purpose microprocessors are used to create computers, while special purpose and microcontroller chips are used in embedded systems. The document outlines a course on microprocessor architecture, covering topics like CPU structure, instruction sets, input/output, and timing. It also discusses administrative details of the course like labs, resources, and evaluation methods.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 61

Horia Cucu

Speech & Dialogue Research Laboratory

Faculty of Electronics, Telecommunications and Information Technology

University POLITEHNICA of Bucharest

Introduction to Microprocessors

Historical Background

Microprocessors Evolution Tree

Typical Applications

Educational Need

Administrative Issues

06.03.2014 2 Microprocessors Architecture

Historical Background

1947: Invention of the transistor

1959: Invention of the integrated circuit (IC)

1965: Birth of Moore's Law

1971: Development of the first microprocessor

1976: Introduction of the first microcontroller

06.03.2014 3 Microprocessors Architecture

Microprocessors and

Microcontrollers

06.03.2014 4 Microprocessors Architecture

is a CPU-on-a-chip

is a computer-on-a-chip

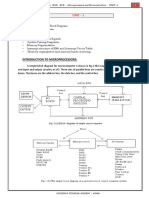

Microprocessors Evolution Tree

06.03.2014 5 Microprocessors Architecture

others

Itanium

RISC

Pentium

80486

80386

80286

8086

8085

8080

8008

4004

8048

8051

DSPs

Comm processors

others

others

General Purpose

Microprocessors

Microcontrollers

Special Purpose

Microprocessors

PIC

AVR

Typical Applications

General purpose microprocessors: used to create computers

PCs, Laptops, Workstations

Servers, Super-computers (32-bit/64-bit powerful computers)

Special purpose microprocessors

Digital Signal Processing (DSP) processors

Multimedia applications

Communication processors

Networking equipment (switches, routers, etc.)

06.03.2014 6 Microprocessors Architecture

Typical Applications

Microcontrollers: used to implement embedded systems

consumer electronics (toys, cameras, robots)

consumer products (washing machines, microwave ovens, etc.)

instrumentation (oscilloscopes, medical equipment)

process control (data acquisition and control)

communication (telephone sets, answering machine, etc.)

office appliances (fax machines, printers, etc.)

multimedia (smart-phones, PDAs, tablets, teleconferencing

equipment)

automotive industry (onboard computers)

06.03.2014 7 Microprocessors Architecture

The Educational Need - a Big Question

06.03.2014 8 Microprocessors Architecture

others

Itanium

RISC

Pentium

80486

80386

80286

8086

8085

8080

8008

4004

8048

8051

DSPs

Comm processors

others

others

General Purpose

Microprocessors

Microcontrollers

Special Purpose

Microprocessors

AVR

PIC

Microprocessors Course Outline

1. The Structure of a Microcomputer. Definitions

2. Overview of a CISC, General Purpose Microprocessor Core

3. Fundamentals of a Typical CISC Architecture

4. Fundamentals of a Typical RISC Architecture

5. Input/Output Strategies

6. Timing for a General Purpose Microprocessor Architecture

06.03.2014 9 Microprocessors Architecture

Administrative Issues

Laboratory

Objective: highlight the architectural attributes for the x86

Microprocessors

Sessions: 5 teaching labs + one evaluation session

Bibliography

C. Burileanu, Microprocesoarele x86 o abordare software, Grupul

pentru microinformatic, Cluj-Napoca, 1999

Communication through the Moodle framework (Arhitectura

Microprocesoarelor - C. Burileanu, Password: Microprocesor)

Lecture slides (contain only a brief summary)

Laboratory documentation

Evaluation results

06.03.2014 10 Microprocessors Architecture

Evaluation

06.03.2014 11 Microprocessors Architecture

Evaluare

Evaluarea activitii pe parcurs (pentru care studentul primete o not: N

laborator

)

este compus din 2 teste obligatorii i o evaluare final opional.

o Nici-o component a evalurii activitii pe parcurs nu se reface.

o Notarea:

Cele 2 teste n timpul edinelor de laborator sunt evaluate cu

note (0 10).

dac media celor 2 note < 5: studentul va reface complet aceast

disciplin n anul urmtor.

dac media celor 2 note >= 5: studentul poate opta pentru:

prezentarea la evaluarea final; n acest caz: N

laborator

= 5 10;

prezentarea direct la examen; n acest caz: N

laborator

= 5.

Examen final n sesiunea de var:

o Examen oral.

o Studentul primete o not: N

examen

= 0 10.

o Se poate reface n septembrie.

Media final: M = (N

laborator

+ N

examen

) / 2

calculat prin trunchiere pentru 4 =< M < 5 i prin rotunjire pentru celelalte

valori.

Evaluation

06.03.2014 12 Microprocessors Architecture

Definitions

Block Diagram of a Microcomputer

06.03.2014 15 Microprocessors Architecture

A microcomputer is a general purpose device that can be programmed

to carry out a set of arithmetic and/or logical operations.

Functional Components

CPU: the hardware block which processes data and

controls the system

Memory: the hardware block which stores data in a

sequence of memory locations

I/Odevices: hardware blocks that form the interface

between the microcomputer and the external world

Busses: the connections between the above blocks

06.03.2014 16 Microprocessors Architecture

The von Neumann Principles

Both data and instructions are stored in the memory

The contents of the memory is accessed by location

The microprocessor is the CPU of the microcomputer; its role is

to process data and control the system

The instructions are fetched from the memory and executed

sequentially by the CPU

I/O ports are used to communicate with other devices

The three hardware blocks are interconnected by the system bus

06.03.2014 17 Microprocessors Architecture

The Memory Basic Principles

Memory sequence of memory locations used to store info

Each memory location:

stores an 8-bit number, a byte of data

is identified by a unique number, called address

The memory is accessed an organized by the CPU only

The CPU can choose to create logical subdivisions within the

memory (called pages or segments)

The memory map all memory locations that can be

addressed by the CPU (not necessarily implemented)

06.03.2014 18 Microprocessors Architecture

The Memory A Closer Look

06.03.2014 19 Microprocessors Architecture

The Memory A Closer Look

The size of the memory is directly linked with the address

size through the following equation:

Example 1:

using an address of 2 bits, one can form 4 different addresses:

00, 01, 10, and 11, for up to 4 different memory locations

consequently, a memory with an address of 2 bits will

comprise 4 memory locations (4 bytes).

Example 2:

using a 20-bit address, one can form 2

20

different addresses,

corresponding to 2

20

different memory locations

consequently, a memory with a 20-bit address will comprise

2

20

memory locations (1 MB).

06.03.2014 20 Microprocessors Architecture

] [

2

bits e addressSiz

memorySize

The Memory Contents Significance

06.03.2014 21 Microprocessors Architecture

This could be a 16-bit result

This could be an instruction

These could be the first two elements in

an array of 8-bit numbers

The significance of the information is given by the programmer.

The memory doesnt know the significance of the information it stores!

Input/Output Devices

I/O Devices hardware blocks that form the interface

between the microcomputer and the external world

I/O Devices can be regarded as a set of I/O Ports

Each I/O port can be used to:

send an 8-bit/16-bit/32-bit number to an external device

receive an 8-bit/16-bit/32-bit number from an external device

is identified by a unique number, called port address

The ports map all ports that can be addressed by the CPU

(not necessarily implemented)

06.03.2014 22 Microprocessors Architecture

The System Bus

Bus set of physical connections that link several hardware

blocks; these connections are used for information transfer

The CPU, Memory and I/O Devices are connected through

a unique System Bus with three components:

A bidirectional Data Bus

Transfers data (operands, results, etc.) and instructions

An unidirectional Address Bus

Through this bus the CPU sends addresses to the Memory and

I/O Devices

A bidirectional Control Bus

Transfers command and control signals from/to the CPU

06.03.2014 23 Microprocessors Architecture

The Software Component

The microcomputer is executing instructions organized in

computer programs, namely the software

Two main categories:

The Operating System: set of programs which facilitate the

users access to the systems resources

User Software: set of programs specifically created by the user

to achieve a certain task

06.03.2014 24 Microprocessors Architecture

Summary

06.03.2014 25 Microprocessors Architecture

The CPU: executes instructions (processes data) and controls the system

The Memory: stores both the data and the instructions

The I/O Devices: interconnect the microcomputer with the outside world

Information Representation in Computer Systems

Information Representation in

Computer Systems

06.03.2014 27 Microprocessors Architecture

Information is stored using electronic circuits, called flip-

flops (or bistables), that have two stable states: on/off

The state of a bistable can be used to represent a bit (i.e.

binary digit: 0, 1) or a boolean value (true, false)

Data types with more than two possible values are stored

using sequences of bits:

Byte (B) a sequence of 8 bits: can store max 2

8

(256) values

Word (w) a sequence of 16 bits: can store max 2

16

values

Double word (dw) 32 bits: can store max 2

32

values

Numbers representation

06.03.2014 28 Microprocessors Architecture

Unsigned (positive) integer numbers

Natural binary representation

Signed integer numbers

Sign & magnitude representation

1s complement representation

2s complement representation

Signed real numbers

Fixed point representation

Floating point representation

Integer numbers representation

06.03.2014 29 Microprocessors Architecture

Decimal

value

Sign and magnitude 1s complement 2s complement

5 natural binary: 00000101 natural binary: 00000101 natural binary: 00000101

-5

natural binary: 00000101

flip the sign bit: 10000101

natural binary: 00000101

flip all bits: 11111010

natural binary: 00000101

flip all bits: 11111010

add 1: 11111011

12 natural binary: 00001100 natural binary: 00001100 natural binary: 00001100

-12

natural binary: 00001100

flip the sign bit: 10001100

natural binary: 00001100

flip all bits: 11110011

natural binary: 00001100

flip all bits: 11110011

add 1: 11110100

Real numbers representation

06.03.2014 30 Microprocessors Architecture

Fixed point representation

A fixed sequence of bits is used to represent decimal part

Twos complement representation

A fixed sequence of bits is used to represent the fractional part

Natural binary representation

Floating point representation

A fixed sequence of bits is used to represent the mantissa

Twos complement representation

A fixed sequence of bits is used to represent the exponent

Natural binary representation

Example: real number = mantissa 2

exponent

Characters representation

06.03.2014 31 Microprocessors Architecture

Coding

conventions:

ASCII

UTF-8

UTF-16

Unicode

Instructions are represented using sequences of bytes;

Some processors have fixed-size instructions

8086 has variable-size instructions (1-6 bytes)

The instruction codes

are formed of several fields:

one instruction type field

none, one or several data fields

none, one or several address fields

are associated with mnemonics (to be used in programming)

Example: add AX, 8017h <=> 051780h

Programs representation

06.03.2014 32 Microprocessors Architecture

The binary, decimal

and hexadecimal bases

06.03.2014 33 Microprocessors Architecture

Any sequence of bits can also be represented as:

a decimal number (number in base 10)

can be written as a sequence of decimal digits (0, 1, , 9)

a hexadecimal number (number in base 16)

can be written as a sequence of hexadecimal digits (0, 1, , 9, A,

B, C, D, E and F)

Hexadecimal numbers representation conventions:

the h suffix: 1A44h

the 0x prefix: 0x1A44

Conversion algorithms

binary

decimal

hexa

Von Neumann Architecture Reminder and Example

Block Diagram of a Microcomputer

06.03.2014 36 Microprocessors Architecture

The CPU: executes instructions (processes data) and controls the system

The Memory: stores both the data and the instructions

The I/O Devices: interconnect the microcomputer with the outside world

Instruction Execution Example

06.03.2014 37 Microprocessors Architecture

The CPU is reset and starts executing instructions from a

predefined address in the memory (100h)

Reset

Execute

instructions from

address 100h

Instruction Execution Example

06.03.2014 38 Microprocessors Architecture

The CPU sends the address of this first instruction (100h)

through the Address Bus

The CPU sends a MEM-READ signal through the Control Bus

100h

MEM-READ

Instruction Execution Example

06.03.2014 39 Microprocessors Architecture

The Memory receives the MEM-READ signal and reads the

address from the Address Bus

100h

MEM-READ

Instruction Execution Example

06.03.2014 40 Microprocessors Architecture

The Memory finds the instruction (instruction #1) in the

memory location(s) with the corresponding address (100h)

Instruction Execution Example

06.03.2014 41 Microprocessors Architecture

The Memory sends the instruction through the Data Bus and

sends an ACK signal through the Control Bus

instruction #1

ACK

Instruction Execution Example

06.03.2014 42 Microprocessors Architecture

The CPU receives the ACK signal and reads the instruction

from the Data Bus

instruction #1

ACK

Instruction Execution Example

06.03.2014 43 Microprocessors Architecture

The CPU decodes the instruction to "understand" what it has

to do next

Let's suppose that it has to add the value 50h to the value

stored in the memory location with the address 2000h

Decode

instruction

Instruction Execution Example

06.03.2014 44 Microprocessors Architecture

The CPU sends the address (2000h) on the Address Bus and

sends a MEM-READ signal through the Control Bus

2000h

MEM-READ

Instruction Execution Example

06.03.2014 45 Microprocessors Architecture

The Memory receives the MEM-READ signal and reads the

address from the Address Bus

2000h

MEM-READ

Instruction Execution Example

06.03.2014 46 Microprocessors Architecture

The Memory finds the data (85h) in the memory location

with the corresponding address (2000h)

Instruction Execution Example

06.03.2014 47 Microprocessors Architecture

The Memory sends the data (85h) through the Data Bus and

sends an ACK signal through the Control Bus

85h

ACK

Instruction Execution Example

06.03.2014 48 Microprocessors Architecture

The CPU receives the ACK signal and reads the data from the

Data Bus

85h

ACK

Instruction Execution Example

06.03.2014 49 Microprocessors Architecture

The CPU temporarily stores the data in a register

Instruction Execution Example

06.03.2014 50 Microprocessors Architecture

The CPU adds the value 50h to the register (the result will be

D5h)

Instruction Execution Example

06.03.2014 51 Microprocessors Architecture

The CPU sends

the result (D5h) through the Data Bus,

the address (2000h) through the Address Bus and

a MEM-WRITE signal through the Control Bus

2000h

MEM-WRITE

D5h

Instruction Execution Example

06.03.2014 52 Microprocessors Architecture

The Memory

receives the MEM-WRITE signal,

reads the address (2000h) from the Address Bus,

reads the result (D5h) from the Data Bus and

stores the result into the corresponding memory location

2000h

MEM-WRITE

D5h

Instruction Execution Example

06.03.2014 53 Microprocessors Architecture

The CPU continues by executing the next instruction

The set of general purpose registers

CPU Registers

06.03.2014 55 Microprocessors Architecture

Register a small amount of storage inside the CPU

Implemented as a set of N synchronized bistables

Stores N bits of data

Highest access speed among all storage options

Several types of registers:

General vs. special purpose (dedicated) registers

Physical vs. logical registers

User-accessible vs. non user-accessible registers

General Purpose Registers

06.03.2014 56 Microprocessors Architecture

General purpose registers (GPRs)

Set of equally-sized registers used to store temporary data

(operands/results) needed in the execution of the program

User-accessible (architectural attributes)

Implemented as physical or logical registers

The size of the GPRs performance criterion

Equal to the size of the Internal Data Bus

The number of GPRs performance criterion

A larger number of GPRs => faster, more compact programs,

ease of programming,

General Purpose Registers

06.03.2014 57 Microprocessors Architecture

MUX (multiplexer) outputs one of the data inputs

(depending on the address inputs)

Internal Data Bus extension of the External Data Bus

inside the CPU

Special Purpose Registers

06.03.2014 58 Microprocessors Architecture

Special purpose registers

Dedicated registers that can be used only for specific purposes

Size depends on the particular role of the register

Some are user-accessible (architectural attributes), some not

Examples:

Data register (DR) and Address register (AR)

Accumulator (A)

Status (Flags) register (F)

Instruction Pointer (IP)

Stack Pointer (SP)

The interface between the CPU and the System Bus

The Data Register

and the Address Register

06.03.2014 60 Microprocessors Architecture

DR (data register): the CPU DataBus interface

The data in DR are available to all the hardware blocks

connected on the Data Bus

The size of DR is the size of the Data Bus

DR is not an architectural attribute

The Data Register

and the Address Register

06.03.2014 61 Microprocessors Architecture

AR (address register): the CPU AddressBus interface

The address in AR is available to all the hardware blocks

connected on the Address Bus; only the CPU writes in AR

The size of AR is the size of the Address Bus

AR is not an architectural attribute

You might also like

- Microprocessor Chapter 1 IntroductionDocument15 pagesMicroprocessor Chapter 1 IntroductionKrishna GuragaiNo ratings yet

- Introduction To ComputersDocument97 pagesIntroduction To Computersta_1091100% (1)

- Course Title Microprocessor SystemDocument20 pagesCourse Title Microprocessor SystemElmustafa Sayed Ali AhmedNo ratings yet

- CSC 109 New Notes 2017Document62 pagesCSC 109 New Notes 2017Kadima ChitechiNo ratings yet

- Fund Concepts of MPU N MCUDocument10 pagesFund Concepts of MPU N MCUDaisuke SSNo ratings yet

- MPMC Unit 1Document204 pagesMPMC Unit 1Nimmagadda Chandra PaulNo ratings yet

- Vtu 4th Sem Cse Microprocessors Notes 10cs45 PDFDocument112 pagesVtu 4th Sem Cse Microprocessors Notes 10cs45 PDFPRINCE DEWANGANNo ratings yet

- Computer Introduction ModuleDocument59 pagesComputer Introduction ModuleCrissa Valmoria BalasabasNo ratings yet

- Embedded Systems Notes (Cse & It)Document148 pagesEmbedded Systems Notes (Cse & It)Sasi KanthNo ratings yet

- Microprocessor Chapter 1Document73 pagesMicroprocessor Chapter 1Wann FarieraNo ratings yet

- Unit 1Document28 pagesUnit 1GopinathManoharanNo ratings yet

- Wa0010.Document12 pagesWa0010.v5kbkrmdfpNo ratings yet

- Embedded Systems Lecture 2Document29 pagesEmbedded Systems Lecture 2migadNo ratings yet

- L3: Microprocessor and MicrocontrollerDocument78 pagesL3: Microprocessor and MicrocontrollerMahesh100% (1)

- Unit 1 Lect 1Document12 pagesUnit 1 Lect 1tankdhruvik800000No ratings yet

- Microprocessors and MicrocontrollersDocument22 pagesMicroprocessors and Microcontrollers6012 ANILNo ratings yet

- Mca PPT - New1Document86 pagesMca PPT - New1Ashwini MateNo ratings yet

- Computer System ArchitectureDocument13 pagesComputer System ArchitectureAmitNo ratings yet

- Computer CourseDocument20 pagesComputer CourseAnu RadhaNo ratings yet

- MAP NotesDocument115 pagesMAP NotesSudershan DolliNo ratings yet

- Computer CourseDocument62 pagesComputer CourseKoram TomboyNo ratings yet

- Review:: Computer Organization, Architecture & Assembly LanguageDocument8 pagesReview:: Computer Organization, Architecture & Assembly LanguageBryle DrioNo ratings yet

- Chapter - 04: Ques.01: Shortly Describe 5 Key Components of A MicrocomputerDocument4 pagesChapter - 04: Ques.01: Shortly Describe 5 Key Components of A MicrocomputerKawsar MobinNo ratings yet

- MicroProcessors 1Document39 pagesMicroProcessors 1Gatheru NjorogeNo ratings yet

- Microcomputer Architecturei 1Document16 pagesMicrocomputer Architecturei 1Augustine NonsoNo ratings yet

- Computer-Architecture 1 PDFDocument0 pagesComputer-Architecture 1 PDFwww.bhawesh.com.npNo ratings yet

- Unit 1 100523023559 Phpapp01Document13 pagesUnit 1 100523023559 Phpapp01loganathanNo ratings yet

- Department of Information and Communication Technology Course: ICT-3205: Computer Architecture and MicroprocessorDocument11 pagesDepartment of Information and Communication Technology Course: ICT-3205: Computer Architecture and MicroprocessorBashar AhmedNo ratings yet

- Unit 1&2 CoaDocument38 pagesUnit 1&2 Coasahil914012No ratings yet

- Computer Arch NotesDocument9 pagesComputer Arch NoteszomukozaNo ratings yet

- Microcontroller&Its Applications 2021 NotesDocument38 pagesMicrocontroller&Its Applications 2021 NotesAnirban MandalNo ratings yet

- MicroprocessorsDocument64 pagesMicroprocessorssharmaamit6059No ratings yet

- Computer Organization NotesDocument126 pagesComputer Organization NotesPriyadarsini karthikNo ratings yet

- Microprocessors and Peripheral Devices - PDF NotesDocument70 pagesMicroprocessors and Peripheral Devices - PDF Noteszsarthak99No ratings yet

- PSP Unit 1 Introduction 25 6 2022 5amDocument37 pagesPSP Unit 1 Introduction 25 6 2022 5ampovir39461No ratings yet

- CH6 MicrocontrollerDocument8 pagesCH6 MicrocontrollerKibrom MenasboNo ratings yet

- Module 3: Programmable Logic Devices (PLDS) Introduction To Micro-Processors and Micro-ControllersDocument36 pagesModule 3: Programmable Logic Devices (PLDS) Introduction To Micro-Processors and Micro-ControllersDhanish KumarNo ratings yet

- CAM Tutorial 1Document15 pagesCAM Tutorial 1ram010No ratings yet

- COMPUTER-ARCHITECTURE Lec 3Document9 pagesCOMPUTER-ARCHITECTURE Lec 3Ahmed Yahia MogaliNo ratings yet

- Computer Organization and Assembly Language: Lecture 1 & 2 Introduction and BasicsDocument33 pagesComputer Organization and Assembly Language: Lecture 1 & 2 Introduction and Basicsdarwinvargas2011No ratings yet

- Microprocessor and MicrocontrollerDocument25 pagesMicroprocessor and MicrocontrollerHafizuddin Mohamad100% (1)

- Embedded Systems Lecture 2Document60 pagesEmbedded Systems Lecture 2migadNo ratings yet

- MicroprocessorDocument11 pagesMicroprocessornave101No ratings yet

- COA NotesDocument110 pagesCOA NotesPavitra GuptaNo ratings yet

- Fundamentals of MicrocontrollerDocument23 pagesFundamentals of Microcontrollerashley panganNo ratings yet

- Introduction To Computing and Programming: Lecture # 9 Parts of CPU (Central Processing Unit)Document18 pagesIntroduction To Computing and Programming: Lecture # 9 Parts of CPU (Central Processing Unit)Ali Akbar KhuhroNo ratings yet

- Contents of Interest For ExamsDocument14 pagesContents of Interest For ExamsThanh NguyenNo ratings yet

- Microprocessor Chapter OneDocument28 pagesMicroprocessor Chapter OneEphrem HabtamuNo ratings yet

- Large Computers: (Mainframe and Super Computers)Document18 pagesLarge Computers: (Mainframe and Super Computers)Shivansh tomarNo ratings yet

- Lecture-2 (Overview of Microcomputer Structure and Operation)Document18 pagesLecture-2 (Overview of Microcomputer Structure and Operation)Salmon Ashik0% (2)

- Microprocessors and Programming: Fall: 2021Document50 pagesMicroprocessors and Programming: Fall: 2021Emirhan AlmaNo ratings yet

- Chapter 1 P 2022 2023 enDocument6 pagesChapter 1 P 2022 2023 enoussama khNo ratings yet

- Sheet 1 - MADocument6 pagesSheet 1 - MALê Mạnh KhánhNo ratings yet

- Advanced Computer Architecture NotesDocument4 pagesAdvanced Computer Architecture NotesSHIVANI NANDANo ratings yet

- Microcontrollers: Veena Hegde, BMSCE, BangaloreDocument10 pagesMicrocontrollers: Veena Hegde, BMSCE, BangaloreAjay YANo ratings yet

- The Brain Behind The Computing: TechnologyDocument3 pagesThe Brain Behind The Computing: TechnologykarmaNo ratings yet

- Introduction To Computing Human Vs Computer: Basic ConceptsDocument7 pagesIntroduction To Computing Human Vs Computer: Basic ConceptsOvais YatooNo ratings yet

- Unit - Ii 2.0) Introduction: Digital Logic and Computer OrganizationDocument32 pagesUnit - Ii 2.0) Introduction: Digital Logic and Computer OrganizationJit AggNo ratings yet

- 1 UnitDocument21 pages1 UnitrambabuNo ratings yet

- A Standard Microcomputer Consists of A Microprocessor (CPU), Buses, Memory, Parallel Input/output, Serial Input/output, Programmable I/O Interrupt, and Direct Memory Access DMADocument14 pagesA Standard Microcomputer Consists of A Microprocessor (CPU), Buses, Memory, Parallel Input/output, Serial Input/output, Programmable I/O Interrupt, and Direct Memory Access DMAAzər NuriNo ratings yet

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesFrom EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesNo ratings yet

- MPLAB XC8 PIC Assembler User's Guide 50002974A PDFDocument78 pagesMPLAB XC8 PIC Assembler User's Guide 50002974A PDFJean Tsuna Kalaw100% (1)

- Final RtosDocument52 pagesFinal RtosDaksh BothraNo ratings yet

- 1st Year Computer NotesDocument67 pages1st Year Computer NotesMuhammadNo ratings yet

- DxdiagDocument41 pagesDxdiagLeal AlejandroNo ratings yet

- E Waste MaterialDocument6 pagesE Waste Materialmurthy lsvrNo ratings yet

- IQReport 20190109 091135 PDFDocument57 pagesIQReport 20190109 091135 PDFLuis Avit Medina QuispeNo ratings yet

- Canon LR - FA - MF4750 - V9 - 2 PDFDocument2 pagesCanon LR - FA - MF4750 - V9 - 2 PDF80ALLA86iNo ratings yet

- PPC 154tDocument2 pagesPPC 154ticpa icpaNo ratings yet

- PIXMA Ip4000 PIXMA Ip5000: Service ManualDocument34 pagesPIXMA Ip4000 PIXMA Ip5000: Service ManualΓιώργος ΠλεύρηςNo ratings yet

- Fraktur Klavikula: Presentasi Oleh Ayu Sartika RDocument46 pagesFraktur Klavikula: Presentasi Oleh Ayu Sartika RTursina RidhoNo ratings yet

- 1 1coreprogrammingunderstandcomputerstorageanddatatypes 110330031933 Phpapp02Document16 pages1 1coreprogrammingunderstandcomputerstorageanddatatypes 110330031933 Phpapp02galacticoceanNo ratings yet

- Introduction To TO Programming Paradigm Programming ParadigmDocument40 pagesIntroduction To TO Programming Paradigm Programming ParadigmViraj KumarNo ratings yet

- Embedded Systems RoadMapDocument14 pagesEmbedded Systems RoadMapMAHESH VNo ratings yet

- PC Express Laptop Pricelist - NOV 29 2022Document8 pagesPC Express Laptop Pricelist - NOV 29 2022Ariel AguilarNo ratings yet

- SKYWAVE Terminal - Installer - Instructions PDFDocument8 pagesSKYWAVE Terminal - Installer - Instructions PDFmrservice7782No ratings yet

- Modbus Card-Manual-20111121Document2 pagesModbus Card-Manual-20111121IamŞůřąjNo ratings yet

- Keyboard InterfacingDocument24 pagesKeyboard InterfacingBhautik DaxiniNo ratings yet

- SB 16 ValuDocument2 pagesSB 16 ValuJim LeonardNo ratings yet

- List ManlessDocument3 pagesList ManlessgivazaharaNo ratings yet

- EliteBook x360 1030 G3Document159 pagesEliteBook x360 1030 G3Patrice WillemNo ratings yet

- EE100 User Manual V 1.1Document21 pagesEE100 User Manual V 1.1PujiyonoNo ratings yet

- Canon Ir2016Document5 pagesCanon Ir2016SergeyMyradovNo ratings yet

- Racing Glider CODEXDocument2 pagesRacing Glider CODEXGhazisNo ratings yet

- Log ErroDocument74 pagesLog ErroMichelle BisNo ratings yet

- Programmable Logic ControllerDocument27 pagesProgrammable Logic ControllerbimalishaNo ratings yet

- An Illustrated History of ComputersDocument41 pagesAn Illustrated History of ComputersPanagiwta RoumpiNo ratings yet

- ASRock Z77 Extreme4 User ManualDocument79 pagesASRock Z77 Extreme4 User ManualMarian BucurNo ratings yet

- Question Bank-Unit 1 2 3Document2 pagesQuestion Bank-Unit 1 2 3Sunil KumarNo ratings yet

- Computer Architecture A Quantitative Approach 5th Edition Hennessy Solutions ManualDocument14 pagesComputer Architecture A Quantitative Approach 5th Edition Hennessy Solutions Manualkevinsnyder22051995fne100% (21)