Professional Documents

Culture Documents

L10

Uploaded by

Jay Padaliya0 ratings0% found this document useful (0 votes)

53 views24 pagesL20

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentL20

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

53 views24 pagesL10

Uploaded by

Jay PadaliyaL20

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 24

L10 Clocks 1 6.

371 Fall 2002 10/4/02

Clocking and Storage Elements

L10 Clocks 2 6.371 Fall 2002 10/4/02

Why Clocks and Storage Elements?

Inputs

Outputs

Combinational Logic

Want to reuse

combinational logic

from cycle to cycle

L10 Clocks 3 6.371 Fall 2002 10/4/02

Digital Systems Timing Conventions

All digital systems need a convention about when a receiver

can sample an incoming data value

synchronous systems use a common clock

asynchronous systems encode data ready signals alongside, or

encoded within, data signals

Also need convention for when its safe to send another value

synchronous systems, on next clock edge (after hold time)

asynchronous systems, acknowledge signal from receiver

Data

Clock

Data

Ready

Acknowledge

Synchronous Asynchronous

L10 Clocks 4 6.371 Fall 2002 10/4/02

Large Systems

Most large scale ASICs, and systems built with these

ASICs, have several synchronous clock domains connected

by asynchronous communication channels

Chip A

Chip B

Chip C

Clock

domain 1

Clock

domain 4

Clock

domain 2

Clock domain 3

Clock

domain 5

Clock

domain 6

Asynch.

channel

Well focus on a single synchronous clock domain for this

lecture

L10 Clocks 5 6.371 Fall 2002 10/4/02

Clocked Storage Elements

Transparent Latch, Level Sensitive

data passes through when clock high, latched when clock low

Clock

D Q

Clock

D

Q

Transparent Latched

Clock

D Q

Clock

D

Q

D-Type Register or Flip-Flop, Edge-Triggered

data captured on rising edge of clock, held for rest of cycle

(Can also have latch transparent on clock low,

or negative-edge triggered flip-flop)

L10 Clocks 6 6.371 Fall 2002 10/4/02

Building a Latch

1

0

CLK

D

Q

Latches are a mux, clock selects

either data or output value

D

Q

Optional

output buffer

Optional

input buffer

CMOS Transmission Gate Latch

Parallel N and P transistors act as

switch, called a transmission gate

CLK

CLK

CLK

D

Q

Usually have local

inverter to

generate CLK

L10 Clocks 7 6.371 Fall 2002 10/4/02

Static CMOS Latch Variants

D

CLK

CLK

CLK

CLK

Q

Clocked CMOS

(C

2

MOS)

feedback inverter

Output buffer shields storage

node from downstream logic

D

CLK

CLK

Q

Weak feedback inverter

so input can overpower it

CLK

D

Q Q

Pulldown stack

overpowers

cross-coupled

inverters

Generally the best, fast

and energy efficient

Has lowest clock load

Can be small, lower clock load, but

sizing problematic

L10 Clocks 8 6.371 Fall 2002 10/4/02

Latch Timing Parameters

T

CQmin

/T

CQmax

propagation inout when clock opens latch

T

DQmin

/T

DQmax

propagation inout while transparent

usually the most important timing parameter for a latch

T

setup

/T

hold

define window around closing clock edge during which data

must be steady to be sampled correctly

Clock

D

Q

T

CQmax

T

CQmin

T

DQmax

T

DQmin

T

setup

T

hold

L10 Clocks 9 6.371 Fall 2002 10/4/02

The Setup Time Race

D

CLK

CLK

CLK

CLK

Q

Setup represents the race for new data to propagate

around the feedback loop before clock closes the input gate.

(Here, were rooting for the data signal)

L10 Clocks 10 6.371 Fall 2002 10/4/02

Failing Setup

D

CLK

CLK

CLK

CLK

Q

If data arrives too close to clock edge, it wont set up

the feedback loop before clock closes the input

transmission gate.

L10 Clocks 11 6.371 Fall 2002 10/4/02

The Hold Time Race

D

CLK

CLK

CLK

CLK

Q

Hold time represents the race for clock to close the input

gate before next cycles data disturbs the stored value.

(Here were rooting for the clock signal)

Added clock buffers to demonstrate positive

hold time on this latch other latch designs

naturally have positive hold time

L10 Clocks 12 6.371 Fall 2002 10/4/02

Failing Hold Time

D

CLK

CLK

CLK

CLK

Q

If data changes too soon after clock edge, clock might

not have had time to shut off input gate and new data

will corrupt feedback loop.

L10 Clocks 13 6.371 Fall 2002 10/4/02

Flip-Flops

Can build a flip-flop using two latches back to

back

CLK

D Q

Master Slave

Master

Transparent

Master

Latched

CLK

Slave

Latched

Slave

Transparent

Master

Transparent

Slave

Latched

On positive edge, master latches input D, slave

becomes transparent to pass new D to output Q

On negative edge, slave latches current Q,

master goes transparent to sample input D again

L10 Clocks 14 6.371 Fall 2002 10/4/02

Flip-Flop Designs

Transmission-gate master-slave latches most popular in ASICs

robust, convenient timing parameters, energy-efficient

Many other ways to build a flip-flop other than transmission gate

master-slave latches

usually trickier timing parameters

only found in high performance custom devices

D

CLK

CLK

CLK

CLK

CLK

CLK

CLK

CLK

Q

CLK CLK

Q

Can have true or

complementary

output or both

L10 Clocks 15 6.371 Fall 2002 10/4/02

Flip-Flop Timing Parameters

T

CQmin

/T

CQmax

propagation inout at clock edge

T

setup

/T

hold

define window around rising clock edge during which

data must be steady to be sampled correctly

either setup or hold time can be negative

Clock

D

Q

T

CQmax

T

CQmin

T

setup

T

hold

L10 Clocks 16 6.371 Fall 2002 10/4/02

Single Clock Edge-Triggered Design

Single clock with edge-triggered registers most

common design style in ASICs

Slow path timing constraint

T

cycle

T

CQmax

+ T

Pmax

+ T

setup

can always work around slow path by using slower clock

Fast path timing constraint

T

CQmin

+ T

Pmin

T

hold

bad fast path cannot be fixed without redesign!

might have to add delay into paths to satisfy hold time

CLK

Combinational

Logic

T

Pmin

/T

Pmax

L10 Clocks 17 6.371 Fall 2002 10/4/02

Clock Distribution

Cant really distribute clock at same instant to

all flip-flops on chip

Central

Clock

Driver

Clock

Distribution

Network

Local

Clock

Buffers

Variations in trace

length, metal width and

height, coupling caps

Variations in local clock

load, local power supply,

local gate length and

threshold, local

temperature

Difference in

clock arrival time

is clock skew

L10 Clocks 18 6.371 Fall 2002 10/4/02

Clock Grids

One approach for low skew is to use a single

metal clock grid across whole chip (Alpha 21064)

Low skew but very high power, no clock gating

Clock driver tree

spans height of

chip. Internal

levels shorted

together.

Grid feeds flops

directly, no local

buffers

L10 Clocks 19 6.371 Fall 2002 10/4/02

H-Trees

Recursive pattern to distribute signals uniformly with

equal delay over area

Uses much less power than grid, but has more skew

In practice, an approximate H-tree is used at the top

level (has to route around functional blocks), with local

clock buffers driving regions

L10 Clocks 20 6.371 Fall 2002 10/4/02

Intel Itanium Clock Distribution

DSK = Active Deskew Circuits, cancels out systematic skew

PLL = Phase Locked Loop

Regional

Grid

L10 Clocks 21 6.371 Fall 2002 10/4/02

Skew Sources and Cures

Systematic skew due to manufacturing variation

can be mostly trimmed out with adaptive

deskewing circuitry

cross chip skews of <50ps reported

Main sources of remaining skew are temperature

changes (low-frequency) and power supply noise

(high frequency)

Power supply noise affects clock buffer delay

and also frequency of PLL

often power for PLL is provided through separate pins

clock buffers given large amounts of local on-chip

decoupling capacitance

L10 Clocks 22 6.371 Fall 2002 10/4/02

Skew versus Jitter

Skew is spatial variation in clock arrival times

variation in when the same clock edge is seen by two

different flip-flops

Jitter is temporal variation in clock arrival times

variation in when two successive clock edges are seen

by the same flip-flop

Power supply noise is main source of jitter

From now on, use skew as shorthand for

untrimmable timing uncertainty

L10 Clocks 23 6.371 Fall 2002 10/4/02

Timing Revisited

Skew eats into timing budget

Slow path timing constraint

T

cyc

T

CQmax

+ T

Pmax

+ T

setup

+ T

skew

worst case is when CLK2 is earlier/later than CLK1

Fast path timing constraint

T

CQmin

+ T

Pmin

T

hold

+ T

skew

worst case is when CLK2 is earlier/later than CLK1

Combinational

Logic

T

Pmin

/T

Pmax

CLK1 CLK2

L10 Clocks 24 6.371 Fall 2002 10/4/02

More Later

Latch-based clocking schemes

Borrowing time across cycle boundaries

Tolerating skew and jitter

Crossing clock domains

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Main GPUDocument87 pagesMain GPUJay PadaliyaNo ratings yet

- R Rec BT.601 7 201103 I!!pdf eDocument19 pagesR Rec BT.601 7 201103 I!!pdf eJay PadaliyaNo ratings yet

- Lab5 Synopsys Tetramax DFTDocument20 pagesLab5 Synopsys Tetramax DFTJay PadaliyaNo ratings yet

- STA IntelDocument81 pagesSTA IntelJay PadaliyaNo ratings yet

- Final REVIEW Voltage FollowerDocument17 pagesFinal REVIEW Voltage FollowerJay PadaliyaNo ratings yet

- Ppt-Review2 Voltage FollowerDocument48 pagesPpt-Review2 Voltage FollowerJay PadaliyaNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Topographic Map of HagansportDocument1 pageTopographic Map of HagansportHistoricalMapsNo ratings yet

- New Product Development ProcessDocument12 pagesNew Product Development ProcessAyushi SinghNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityfeyayel988No ratings yet

- Regenerative Desiccant Dryers: KAD, KED and KBD SeriesDocument10 pagesRegenerative Desiccant Dryers: KAD, KED and KBD SeriesNaveen KumarNo ratings yet

- VOLVO EC360C HR EC360CHR EXCAVATOR Service Repair Manual PDFDocument19 pagesVOLVO EC360C HR EC360CHR EXCAVATOR Service Repair Manual PDFfjjsjekdmme0% (1)

- English 3 Lesson PlanDocument9 pagesEnglish 3 Lesson PlanRegine MalanaNo ratings yet

- GRADE 11 General Mathematics Week 2 Quarter 1 ModuleDocument12 pagesGRADE 11 General Mathematics Week 2 Quarter 1 ModuleCasey Erica Nicole CarranzaNo ratings yet

- Perkahwinan Remaja: Satu Kajian Di Kuching, Sarawak (Teenage Marriage: A Study in Kuching, Sarawak)Document15 pagesPerkahwinan Remaja: Satu Kajian Di Kuching, Sarawak (Teenage Marriage: A Study in Kuching, Sarawak)Lim Shu QingNo ratings yet

- Repair Instruction For Engine Repair Manual: PrecautionDocument3 pagesRepair Instruction For Engine Repair Manual: PrecautionHenry SilvaNo ratings yet

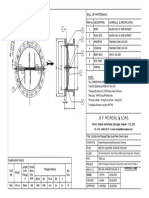

- Dual Plate 800 NB-ModelDocument1 pageDual Plate 800 NB-ModelTanmoy DuttaNo ratings yet

- Doménech Carbó Osete Cortina2016 - Article - AnotherBeautyOfAnalyticalChemiDocument50 pagesDoménech Carbó Osete Cortina2016 - Article - AnotherBeautyOfAnalyticalChemigmjNo ratings yet

- The Design of International Trade AgreementsDocument4 pagesThe Design of International Trade AgreementsasmexNo ratings yet

- REHAU CatalogDocument25 pagesREHAU CatalogGeorge PetziNo ratings yet

- Punctuation Guide Modif. Sept. 2017Document14 pagesPunctuation Guide Modif. Sept. 2017Boris SalgeNo ratings yet

- BOECO Hydrometer Alcohol Meter PDFDocument5 pagesBOECO Hydrometer Alcohol Meter PDFTianTrafNo ratings yet

- Installation Manual MaldivesDocument23 pagesInstallation Manual MaldivesutaiuliancatalinNo ratings yet

- Additional Topics in Variance Analysis: True / False QuestionsDocument232 pagesAdditional Topics in Variance Analysis: True / False QuestionsElaine GimarinoNo ratings yet

- Digital Communication Lab Report: Experiment Number 7Document9 pagesDigital Communication Lab Report: Experiment Number 7Saketh RaviralaNo ratings yet

- Datasheet For Safety Device ConveyorDocument6 pagesDatasheet For Safety Device ConveyorJoe GrosirNo ratings yet

- DRWG Part7Document10 pagesDRWG Part7Ravindra singh TanwarNo ratings yet

- PalmistryDocument115 pagesPalmistryverne4444100% (3)

- ELEN1000 Lab Cover Sheet - LAB 1Document10 pagesELEN1000 Lab Cover Sheet - LAB 1Francis GomesNo ratings yet

- TeSys Control Relays - CAD32G7Document3 pagesTeSys Control Relays - CAD32G7muez zabenNo ratings yet

- Solidity Part 2Document103 pagesSolidity Part 2Muhammad Zahid FaridNo ratings yet

- Finrl: Deep Reinforcement Learning Framework To Automate Trading in Quantitative FinanceDocument9 pagesFinrl: Deep Reinforcement Learning Framework To Automate Trading in Quantitative FinancegyhtujrtyNo ratings yet

- Working With ComplexityDocument7 pagesWorking With ComplexitychoileoNo ratings yet

- Adobe Photoshop 7 - Classroom in A Book - Cs PDFDocument15 pagesAdobe Photoshop 7 - Classroom in A Book - Cs PDFoliverNo ratings yet

- Position, Velocity and AccelerationDocument12 pagesPosition, Velocity and AccelerationawbNo ratings yet

- Homework 3Document3 pagesHomework 3Haonan ZhangNo ratings yet

- 4) Findings and Recommendations and Conclusions-OkkDocument15 pages4) Findings and Recommendations and Conclusions-OkkAshiqur RahmanNo ratings yet