Professional Documents

Culture Documents

Question Bank For DLC

Uploaded by

Avina AshOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Question Bank For DLC

Uploaded by

Avina AshCopyright:

Available Formats

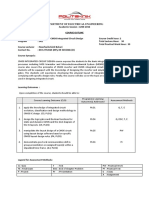

DIGITAL LOGIC CIRCUITS

KINGS

COLLEGE OF ENGINEERING

DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING ACADEMIC YEAR 2009-2010/ EVEN SEMESTER

QUESTION BANK

SUBJECT NAME: DIGITAL LOGIC CIRCUITS YEAR / SEM: II / IV

UNIT I BOOLEAN ALGEBRA AND COMBINATIONAL CIRCUITS

PART-A (2 MARKS)

1. What is variable mapping? 2. Name the two canonical forms for Boolean algebra. 3. State the steps involved in Gray to binary conversion? 4. State De Morgan's theorem. 5. Reduce A'B'C' + A'BC' + A'BC 6. Prove that ABC + ABC' + AB'C + A'BC = AB + AC + BC 7. State the limitations of karnaugh map. 8. What is a full-adder? 9. What is Magnitude Comparator? 10. What is code conversion? 11. Give an application each for a mux and demux. 12. What is a priority encoder? 13. Implement the given function in 4:1 mux f= m(0,1,3,5,6) 14. Can a decoder function as a Demultiplexer? 15. What are prime-implicants?

KINGS COLLEGE OF ENGINEERING, PUNALKULAM 1

DIGITAL LOGIC CIRCUITS

PART-B

1. Obtain the minimum sop using QUINE- McCLUSKY method and verify using K-map F=m0+m2+m4+m8+m9+m10+m11+m12+m13 (16) 2. Reduce the following using tabulation method. F=m2+m3+m4+m6+m7+m9+m11+m13. (16)

3.Reduce the Boolean function using k-map technique and implement using gates f (w, x, y, z)= m (0,1,4,8,9,10) which has the dont cares condition d (w, x, y, z)= m (2,11). (16) 4. a) Design an 8421 to gray code converter. b) Implement the Boolean function using 8:1 mux. F (A, B, C, D) =ABD+ACD+BCD+ACD. 5. Design A Full Adder And A Full Subtractor. 6 A combinational circuit is defined by the following three Boolean functions F1 = xyz+xz F2= xyz+xy F3= xyz+xy Design the circuit with a decoder and external gates. 7. Simplify the following Boolean function by using Tabulation method F (w, x, y, z) =m (0, 1, 2, 8, 10, 11, 14, 15) 8. Simplify the following Boolean functions by using KMap in SOP & POS. F (w, x, y, z) = m (1, 3, 4, 6, 9, 11, 12, 14) 9. a) Design a 2 bit magnitude comparator. b) Explain the operation of 4 to 10 decoder. (8) (8) (16)

(16) (16) (16) (8) (8)

KINGS COLLEGE OF ENGINEERING, PUNALKULAM 2

DIGITAL LOGIC CIRCUITS

UNIT II

SYNCHRONOUS SEQUENTIAL SIRCUITS

PART-A (2 MARKS)

1. 2. 3. 4. 5. 6. 7. 8. 9. 10. Write the characteristic equations for Jk and D Flip Flops. How can a D flip flop be converted into T flip-flop? What is meant by the term edge triggered? How many ffs are required to design a mod-7 up down counter? Define synchronous sequential circuit Define flip flop What is race around condition? What is the difference between synchronous and asynchronous counter? What is meant by modulus of a counter? What is a state equation?

PART B

1. A sequential circuit has 2D ffs A and B an input x and output y is specified by the following next state and output equations. A (t+1)= Ax + Bx B (t+1)= Ax Y= (A+B) x (i) (ii) (iii) table. 3. a)Write the excitation tables of SR, JK, D, and T Flip flops b) Realize D and T flip flops using Jk flip flops Draw the logic diagram of the circuit. Derive the state table. Derive the state diagram. (16) (16) (8) (8)

2. Design a mod-10 synchronous counter using Jk ff. write excitation table and state

KINGS COLLEGE OF ENGINEERING, PUNALKULAM 3

DIGITAL LOGIC CIRCUITS 4. Design a sequential circuit using JK flip-flop for the following state table [use state diagram]

(16) 5. Design a counter with the following repeated binary sequence:0, 1, 2, 3, 4, 5, 6.use JK Flip-flop. (16)

UNIT III ASYNCHRONOUS SEQUENTIAL CIRCUIT

PART-A (2 MARKS)

1. Distinguish between synchronous and asynchronous sequential circuits 2. What is an essential hazard and how to eliminate it? 3. What is meant by state assignment? 4. Define Asynchronous sequential circuit? 5. What is the significance of state assignment? 6. What is primitive flow chart? 7. What is fundamental mode? 8. What are the steps for the design of asynchronous sequential circuit? 9. Define merger graph. 10. When do race conditions occur?

KINGS COLLEGE OF ENGINEERING, PUNALKULAM 4

DIGITAL LOGIC CIRCUITS

PART B

1. Design an asynchronous sequential circuit that has 2 inputs x2 and x1, and one output z. the output is to remain 0 as long as an X1 is 0. The first change in x2 that occurs while x1 is 1 will cause z to be 1. Z is to remain 1 until x1 returns to 0. Construct a state diagram and flow table. Determine the output equations. (16)

2.Design a circuit with inputs A and B to give an output z=1 when AB=11 but only if A becomes 1 before B, by drawing total state diagram, primitive flow table and output map in which transient state is included. (16)

3. Obtain the primitive flow table for an asynchronous circuit that has 2 inputs x, y and output z. an output z=1, is to occur only during the input state xy=01 and then if and only if the input state xy=01 is preceded by the input sequence xy=01, 00, 10, 00, 10, 00 4. Design a circuit with input a and b to give an output z=1 when which transient state is included. (16)

AB =11 but only if A (16)

becomes 1 before B, by drawing total state diagram, primitive flow table and output map in

5. Design a asynchronous sequential circuit with 2 inputs T and C. The output attains a value of 1 when T = 1 & c moves from 1 to 0. Otherwise the output is 0. (16)

6. Design an Asynchronous sequential circuit using SR latch with two inputs A and B and one output y. B is the control input which, when equal to 1, transfers the input A to output y. when B is 0, the output does not change, for any change in input. (16)

KINGS COLLEGE OF ENGINEERING, PUNALKULAM 5

DIGITAL LOGIC CIRCUITS

UNIT-IV PROGRAMMABLE LOGIC DEVICS ,MEMORY AND LOGIC FAMILIES

PART-A (2 MARKS)

1. Mention the classification of saturated bipolar logic families 2. What are the difference between PLA and PAL? 3. What is the major difference between ECL and TTL? 4. What are the types of TTL logic? 5. Define address and word: 6. What is programmable logic array? How it differs from ROM? 7. Explain EPROM. 8. Give the classification of PLDs. 9. Define Static RAM and dynamic RAM

PART B

1. a) Explain in detail about PLA with a specific example.

(8) (8)

b) Explain with neat diagrams RAM architecture 2. Implement the following function using PLA. A (x, y, z) = m (1, 2, 4, 6) B (x, y, z) = m (0, 1, 6, 7) C (x, y, z) = m (2, 6) 3. Implement the following function using PAL. W (A, B, C, D) = m (2, 12, 13) X (A, B, C, D) = m (7, 8, 9, 10, 11, 12, 13, 14, 15) Y (A, B, C, D) = m (0, 2, 3, 4, 5, 6, 7, 8, 10, 11, 15) Z (A, B, C, D) = m (1, 2, 8, 12, 13)

(16)

(16)

KINGS COLLEGE OF ENGINEERING, PUNALKULAM 6

DIGITAL LOGIC CIRCUITS

4. Discuss on the concept of working and applications of following memories. i) ROM ii) EPROM iii) PLA. 5. i) A combinational circuit is defined by the functions. F1 (a, b, c) = m (3, 5, 6, 7) F2 (a, b, c) = m (0, 2, 4, 7) implement the circuit with a PLA. ii) Write short notes on semiconductor memories 6. a) compare the various digital logic families. b) Write notes on FPGA. (8) (8) (8) (8) (16)

UNIT V VHDL

PART-A (2 MARKS)

1) What do the acronyms VHDL and VHLSI stand for? 2) What are the advantages of using a hard ware description language? 3) What is VHDL? 4) What are the features of VHDL 5) Define entity 6) What do you meant by concurrent statement 7) Define VHDL package 8) What are the operates used in VHDL language 9) Give short notes on logic simulation and logic synthesis 10) What do you mean by test bench

KINGS COLLEGE OF ENGINEERING, PUNALKULAM 7

DIGITAL LOGIC CIRCUITS

PART B

1) Write a HDL code for state machine to BCD to ex 3 codes Converter 2) Write a behavioral VHDL description of the 4 bit counter 3) (I) Write VHDL code for a full sub tractor using logic Equation (II) Write a VHDL description of an S-R latch using a process 4) Write a HDL code for 8:1 MUX using behavioral model (16) (16) (8) (8) (16)

5) Write the HDL description of the circuit specified by the Following Boolean equations (16) S = xy + x y C =xy 6) (I) Write an HDL data flow description of a 4 bit adder subtractor numbers use the conditional operator (II) Write the HDL gate level description of the priority encoder of Unsigned (8) (8)

*****************************************

KINGS COLLEGE OF ENGINEERING, PUNALKULAM 8

You might also like

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- Digital Logic Circuits PDFDocument8 pagesDigital Logic Circuits PDFnaina10691No ratings yet

- Ee 2255 Digital Logic CircuitsDocument7 pagesEe 2255 Digital Logic CircuitsjohnsamvlbNo ratings yet

- Ec 1202 Digital System DesignDocument8 pagesEc 1202 Digital System DesignworkubNo ratings yet

- WWW - Universityquestions.in: Unit 1 Number Systems and Digital Logic Families Part ADocument7 pagesWWW - Universityquestions.in: Unit 1 Number Systems and Digital Logic Families Part Abunny_589318117No ratings yet

- EC 1312 - Digital Logic Circuits Question BankDocument5 pagesEC 1312 - Digital Logic Circuits Question BankDeepak RavichandranNo ratings yet

- EE6301 DLC Question Bank Rejinpaul 2Document8 pagesEE6301 DLC Question Bank Rejinpaul 2aruljothiNo ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question Bankjjshree79No ratings yet

- Subject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeeDocument16 pagesSubject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeePavithra ManiNo ratings yet

- VEC EE6301 Digital Logic Circuits NotesDocument7 pagesVEC EE6301 Digital Logic Circuits Notesariv2009No ratings yet

- Ec34 Question BankDocument6 pagesEc34 Question Bankkartheeswaran11No ratings yet

- Ap9212 AdsdDocument12 pagesAp9212 AdsdKartheeswaran Arumugam33% (3)

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- B.Tech Digital Principles and System Design Exam Question BankDocument24 pagesB.Tech Digital Principles and System Design Exam Question Bankdigital1206No ratings yet

- Digital Electronics QBDocument7 pagesDigital Electronics QBvinaytmkNo ratings yet

- Kings: Subject Code: Subject Name: Unit - IDocument6 pagesKings: Subject Code: Subject Name: Unit - IBalasubramaniam SaravananNo ratings yet

- Deld QB EndsemDocument4 pagesDeld QB EndsemUV New MoviesNo ratings yet

- DPSD Question BankDocument5 pagesDPSD Question Bankmohanraj1990No ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- Digital Logic CircuitsDocument7 pagesDigital Logic CircuitsMATHANKUMAR.SNo ratings yet

- EC 6302 2-Marks and 16 Marks QuestionsDocument12 pagesEC 6302 2-Marks and 16 Marks QuestionsskaruppaiaheceNo ratings yet

- A.R. Engineering College, Villupuram Ece Department: Ec2203/Digital ElectronicsDocument8 pagesA.R. Engineering College, Villupuram Ece Department: Ec2203/Digital ElectronicsNitu VlsiNo ratings yet

- Digital Principles and System DesignDocument7 pagesDigital Principles and System DesignnofeelingrahulNo ratings yet

- Digital Fundamentals BE SEM 3Document2 pagesDigital Fundamentals BE SEM 3Dhwanil BhattNo ratings yet

- Digital Logic Circuits Model Exam QuestionsDocument2 pagesDigital Logic Circuits Model Exam QuestionsreporterrajiniNo ratings yet

- Question Bank: Ec6302 Digital ElectronicsDocument14 pagesQuestion Bank: Ec6302 Digital ElectronicsBarry SmithNo ratings yet

- Digital Electronics QuestionsDocument8 pagesDigital Electronics QuestionsShivamahendar SunkaNo ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- EC2203 U Q BankDocument12 pagesEC2203 U Q Bankvlsi_satheeshNo ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- Ec2203 Digital ElectronicsDocument8 pagesEc2203 Digital ElectronicspappujayaNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- Digital Logic Circuits Tutorial (2014-2015) ODD SemDocument7 pagesDigital Logic Circuits Tutorial (2014-2015) ODD SemSai Er SaravananNo ratings yet

- Ec1206 DPSDDocument8 pagesEc1206 DPSDkingraajaNo ratings yet

- Dem QB Ut-1 110120Document2 pagesDem QB Ut-1 110120ABHI THORATNo ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- Epc Questions - Cs8351 Digital Principles and System DesignDocument2 pagesEpc Questions - Cs8351 Digital Principles and System DesignaltaNo ratings yet

- EC6302 Digital ElectronicsDocument12 pagesEC6302 Digital ElectronicsJabeen BanuNo ratings yet

- apr - may 2023Document3 pagesapr - may 2023Pandyselvi BalasubramanianNo ratings yet

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- Ec1312 QBDocument7 pagesEc1312 QBGopinathan MuthusamyNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- nov - dec 2021Document3 pagesnov - dec 2021Pandyselvi BalasubramanianNo ratings yet

- Model Important Questions (1fffffffffffffffffffffffDocument2 pagesModel Important Questions (1fffffffffffffffffffffffinfinitywaysalwaysNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- Dica Question BankDocument4 pagesDica Question BankOmprakash KuswahaNo ratings yet

- DellDocument6 pagesDellamu_manuNo ratings yet

- KEE401 ASSIGNMENTS and QUESTION BANKDocument17 pagesKEE401 ASSIGNMENTS and QUESTION BANKPrince VermaNo ratings yet

- Question Bank Subject Code: Ec6302 Subject: Digital Electronics Sem / Year: Iii / Ii-Ece Unit-I Minimization Techniques and Logic Gates Part-ADocument3 pagesQuestion Bank Subject Code: Ec6302 Subject: Digital Electronics Sem / Year: Iii / Ii-Ece Unit-I Minimization Techniques and Logic Gates Part-AmohanaNo ratings yet

- STLD Question BankDocument6 pagesSTLD Question Bankrachasaikiran0% (1)

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- Fundamentals of Electronics 1: Electronic Components and Elementary FunctionsFrom EverandFundamentals of Electronics 1: Electronic Components and Elementary FunctionsNo ratings yet

- Idea For The Animated MovieDocument2 pagesIdea For The Animated MovieAvina AshNo ratings yet

- Final Justice Teaser CutsDocument1 pageFinal Justice Teaser CutsAvina AshNo ratings yet

- My ResumeDocument2 pagesMy ResumeAvina AshNo ratings yet

- New Mystery Murder Story Base PointsDocument1 pageNew Mystery Murder Story Base PointsAvina AshNo ratings yet

- Ramya Laxmi Vasu Ravi: Character Choice 1 Choice 2 Choice 3Document1 pageRamya Laxmi Vasu Ravi: Character Choice 1 Choice 2 Choice 3Avina AshNo ratings yet

- Sankaran - Radhakrishnan Tamil Script Book Learner's ManualDocument225 pagesSankaran - Radhakrishnan Tamil Script Book Learner's ManualSathyamoorthy VenkateshNo ratings yet

- Ravikumar CharacterDocument1 pageRavikumar CharacterAvina AshNo ratings yet

- Life Time Learning TopicsDocument1 pageLife Time Learning TopicsAvina AshNo ratings yet

- LocationsDocument1 pageLocationsAvina AshNo ratings yet

- TM TRVLDocument2 pagesTM TRVLAvina AshNo ratings yet

- Some Dialogue and Situation For The Alappuza MysteryDocument1 pageSome Dialogue and Situation For The Alappuza MysteryAvina AshNo ratings yet

- MARMAYOGI - Mystery, Crime, ThrillerDocument2 pagesMARMAYOGI - Mystery, Crime, ThrillerAvina AshNo ratings yet

- Sankaran - Radhakrishnan Tamil Script Book Learner's ManualDocument225 pagesSankaran - Radhakrishnan Tamil Script Book Learner's ManualSathyamoorthy VenkateshNo ratings yet

- Points To Remember Before Making A MovieDocument2 pagesPoints To Remember Before Making A MovieAvina AshNo ratings yet

- HurricaneDocument1 pageHurricaneAvina AshNo ratings yet

- A Student's Guide To Living in KoreaDocument4 pagesA Student's Guide To Living in KoreaAvina AshNo ratings yet

- 2015 Sundance Film Festival Award WinnersDocument1 page2015 Sundance Film Festival Award WinnersAvina AshNo ratings yet

- Questions To Be AskedDocument1 pageQuestions To Be AskedAvina AshNo ratings yet

- GoplasDocument1 pageGoplasAvina AshNo ratings yet

- GOPLDocument1 pageGOPLAvina AshNo ratings yet

- Registration Cum Admission Form EiiDocument2 pagesRegistration Cum Admission Form EiiAvina AshNo ratings yet

- How To Waste 4 Years of Your LifeDocument12 pagesHow To Waste 4 Years of Your LifeAvina AshNo ratings yet

- Ec2254-Linear Integrated CircuitsDocument3 pagesEc2254-Linear Integrated CircuitsTamil PavaiNo ratings yet

- Harappan Civilization NotesDocument42 pagesHarappan Civilization Notesshardha100% (3)

- Ec2254-Linear Integrated CircuitsDocument3 pagesEc2254-Linear Integrated CircuitsTamil PavaiNo ratings yet

- The Rotating MachineDocument1 pageThe Rotating MachineAvina AshNo ratings yet

- Indian Polity in TamilDocument22 pagesIndian Polity in Tamilalluse79% (14)

- Scribleindia EC2254 Linear Integrated Circuits Question Bank PDFDocument4 pagesScribleindia EC2254 Linear Integrated Circuits Question Bank PDFAvina AshNo ratings yet

- Lang Code MybbDocument3 pagesLang Code Mybbwhite_snow19No ratings yet

- Hosts UmbrellaDocument1 pageHosts UmbrellaFabsor SoralNo ratings yet

- Research Task GraphDocument1 pageResearch Task Graphapi-419834532No ratings yet

- Dronacharya Microprocessor - Lab - 17012013Document25 pagesDronacharya Microprocessor - Lab - 17012013virendra.aryaNo ratings yet

- Loknete Vyankatrao Hiray College, Panchavati, Nashik-03: Departmenet of Electronic ScienceDocument9 pagesLoknete Vyankatrao Hiray College, Panchavati, Nashik-03: Departmenet of Electronic ScienceMonali NiphadeNo ratings yet

- Electric Circuits NotesDocument646 pagesElectric Circuits NotesEmadElDinEzzat100% (3)

- Reconfigurable Threshold Logic Gates Using Memristive DevicesDocument20 pagesReconfigurable Threshold Logic Gates Using Memristive DevicesSalman KhanNo ratings yet

- Pulsed LatchesDocument83 pagesPulsed LatchesRatnakarVarun100% (1)

- Pixie Transceiver OZDocument7 pagesPixie Transceiver OZjasonm212No ratings yet

- RC Phase Shift Oscillator WorkshopDocument21 pagesRC Phase Shift Oscillator Workshopksreddy2002No ratings yet

- Spartan-3E FPGA Family: Complete Data Sheet: Introduction and Ordering Information DC and Switching CharacteristicsDocument193 pagesSpartan-3E FPGA Family: Complete Data Sheet: Introduction and Ordering Information DC and Switching CharacteristicsDaniel RodriguezNo ratings yet

- Fm/Am Radio Ic: CD2003GP/GBDocument7 pagesFm/Am Radio Ic: CD2003GP/GBМаксим МульгинNo ratings yet

- HCF 4511 BEDocument16 pagesHCF 4511 BEy2k_yah7758No ratings yet

- CYT1000Document1 pageCYT1000Renato Hernandez50% (2)

- Switched Capacitor CircuitsDocument6 pagesSwitched Capacitor CircuitsEduardo ReynaNo ratings yet

- Instructors: Dr. Phillip JonesDocument44 pagesInstructors: Dr. Phillip JonesskarthikpriyaNo ratings yet

- Lab Session # 8 Latches, Gated Latches and Flip-Flops: CircuitsDocument10 pagesLab Session # 8 Latches, Gated Latches and Flip-Flops: Circuitsmaraim4eveNo ratings yet

- Circuit Function and Benefits: AD9834 AD5620Document3 pagesCircuit Function and Benefits: AD9834 AD5620Anonymous oyUAtpKNo ratings yet

- DEE6113 Course Outline Jun2016Document4 pagesDEE6113 Course Outline Jun2016FonzBahariNo ratings yet

- IC693ALG221: This Datasheet Is For TheDocument5 pagesIC693ALG221: This Datasheet Is For TheMauricio AstorgaNo ratings yet

- 869 SingleDocument1 page869 Singleapi-3833673No ratings yet

- DAC80 CB1 V DatasheetDocument10 pagesDAC80 CB1 V DatasheetsunhuynhNo ratings yet

- Microcontroller Basics ExplainedDocument2 pagesMicrocontroller Basics ExplainedJK CreationNo ratings yet

- P1260ATF: N-Channel Enhancement Mode MOSFETDocument5 pagesP1260ATF: N-Channel Enhancement Mode MOSFETGioVoTamNo ratings yet

- EXPERIMENT #2 Frequency Response of Common Emitter AmplierDocument6 pagesEXPERIMENT #2 Frequency Response of Common Emitter AmplierGhabriel Javier SembranoNo ratings yet

- Damian Hall Assignment7 DctheoryDocument18 pagesDamian Hall Assignment7 DctheoryDamian HallNo ratings yet

- Digital Logic Design Combinational LogicDocument29 pagesDigital Logic Design Combinational LogicsfdNo ratings yet

- Applied II NoteDocument142 pagesApplied II NoteTemesgen MekonenNo ratings yet

- Sequential Circuits: Output Is DependentDocument66 pagesSequential Circuits: Output Is DependentSiddharth SharmaNo ratings yet

- Log amp tutorial questionsDocument2 pagesLog amp tutorial questionsy shuangNo ratings yet

- 2SC5343Document3 pages2SC5343Abigail HoobsNo ratings yet

- MC145031 Encoder Manchester PDFDocument10 pagesMC145031 Encoder Manchester PDFson_gotenNo ratings yet