Professional Documents

Culture Documents

FSDM07652R Datasheet

Uploaded by

marianos67Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FSDM07652R Datasheet

Uploaded by

marianos67Copyright:

Available Formats

www.fairchildsemi.

com

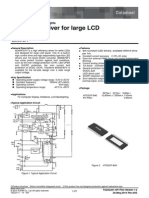

FSDM07652R

Features

Fairchild Power Switch(FPS)

Description

The FSDM07652R is specially designed for an off-line Switched mode power supply (SMPS). This device is a current mode PWM controller combined with a high voltage power SenseFET in a single package using BCDMOS technology. The PWM controller includes integrated fixed frequency oscillator, under voltage lockout, leading edge blanking (LEB), optimized gate driver, internal soft start, temperature compensated precise current sources for a loop compensation and self protection circuitry. Compared with discrete MOSFET and PWM controller solution, it can reduce total cost, component count, size and weight simultaneously increasing efficiency, productivity, and system reliability. This device is well suited for cost effective design of LCD monitor adapter.

TO-220F-6L

6 : Vstr 5 : N.C. 4 : Feedback 3 : Vcc 2 : GND 1 : Drain

Precise Fixed Operating Frequency (66kHz) Low power consumption (under 1W) at 265VAC with 0.5W load using a burst-mode operation Pulse by Pulse Current Limit Abnormal Over Current Protection (Auto Restart Mode) Over Voltage Protection (Auto Restart Mode) Over Load Protection (Auto Restart Mode) Thermal Shutdown (Auto Restart Mode) Under Voltage Lockout Fully Avalanche Rated and 100% Tested SenseFET Internal Soft Start

Application

LCD Monitor SMPS Adaptor

Internal Block Diagram

Vcc 3 N.C 5 0.5/0.7V

+

Vstr 6

Drain 1

Istart

Vref 8V/12V Vcc good Internal Bias

Vcc Idelay Vref OSC IFB

2.5R

PWM

FB 4

R Q

Soft start

R LEB

Gate driver

VSD Vcc Vovp TSD Vcc good

S Q

2 GND

AOCP

Vocp

Rev.1.0.1

2003 Fairchild Semiconductor Corporation

FSDM07652R

Pin Definitions

Pin Number 1 2 3 Pin Name Drain GND Vcc Pin Function Description This pin is the high voltage power SenseFET drain. It is designed to drive the transformer directly. This pin is the control ground and the SenseFET source. This pin is the positive supply voltage input. During start up, the power is supplied by an internal high voltage current source that is connected to the Vstr pin. When Vcc reaches 12V, the internal high voltage current source is disabled and the power is supplied from auxiliary transformer winding. This pin is internally connected to the inverting input of the PWM comparator. The collector of an optocoupler is typically tied to this pin. For stable operation, a capacitor should be placed between this pin and GND. If the voltage of this pin reaches 6.0V, the over load protection is activated resulting in shutdown of the FPS. This pin is connected directly to the high voltage DC link. At startup, the internal high voltage current source supplies internal bias and charges the external capacitor that is conneted to the Vcc pin. Once Vcc reaches 12V, the internal current source is disabled.

Feedback

5 6

N.C Vstr

FSDM07652R

Absolute Maximum Ratings

(Ta=25C, unless otherwise specified) Parameter Drain-Gate Voltage (RGS=1M) Gate-Source (GND) Voltage Drain Current Pulsed

(2) (3)

Symbol VDGR VGS IDM EAS IAS VCC VFB PD(Watt H/S) Derating Tj TA TSTG

Value 650 30 28 370 13 19 -0.3 to VCC 62 1.163 +150 -25 to +85 -55 to +150

Unit V V ADC mJ A V V W W/C C C C

Single Pulsed Avalanche Energy Supply Voltage Input Voltage Range Total Power Dissipation Operating Junction Temperature Operating Ambient Temperature Storage Temperature Range

Single Pulsed Avalanche Current (4)

Notes: 1. Tj=25C to 150C 2. Repetitive rating: Pulse width limited by maximum junction temperature 3. L= mH, starting Tj=25C 4. L=13uH, starting Tj=25C

FSDM07652R

Electrical Characteristics (SenseFET part)

(Ta=25C unless otherwise specified) Parameter Drain Source Breakdown Voltage Zero Gate Voltage Drain Current Static Drain Source On Resistance (1) Forward Transconductance Input Capacitance Output Capacitance Reverse Transfer Capacitance Turn On Delay Time Rise Time Turn Off Delay Time Fall Time Total Gate Charge (Gate-Source+Gate-Drain) Gate-Source Charge Gate-Drain (Miller) Charge

Note: 1. Pulse test : Pulse width 300S, duty 2%

Symbol BVDSS IDSS RDS(ON) gfs Ciss Coss Crss td(on) tr td(off) tf Qg Qgs Qgd

Condition VGS = 0V, ID = 250A VDS = 650V, VGS = 0V VDS= 520V VGS = 0V, TC = 125C VGS = 10V, ID = 1.8A VDS = 50V, ID = 1.8A VGS = 0V, VDS = 25V, f = 1MHz VDD= 325V, ID= 6.5A (MOSFET switching time is essentially independent of operating temperature) VGS = 10V, ID = 6.5A, VDS = 520V (MOSFET switching time is essentially independent of operating temperature)

Min. 650 -

Typ. 1.4 8 1415 100 15 25 60 115 65 40 7 12

Max. 200 300 1.6 -

Unit V A A

mho pF

ns

nC

FSDM07652R

Electrical Characteristics (Continued)

(Ta=25C unless otherwise specified) Parameter UVLO SECTION Start Threshold Voltage Stop Threshold Voltage OSCILLATOR SECTION Initial Frequency Voltage Stability Temperature Stability (note4) Maximum duty cycle Minimum Duty Cycle FEEDBACK SECTION Feedback Source Current Shutdown Feedback Voltage Shutdown Delay Current PROTECTION SECTION Over Voltage Protection Abnormal Over Current Protection Voltage (Note2) Thermal Shutdown Temp.(Note4) SOFTSTART SECTION Softstart Time BURST MODE SECTION Burst mode Enable Feedback Voltage (Note4) Burst mode Disable Feedback Voltage (Note4) CURRENT LIMIT(SELF-PROTECTION)SECTION Peak Current Limit (Note3) TOTAL DEVICE SECTION IOP Operating Supply Current (Note1) IOP(MIN) IOP(MAX) Vfb=GND, VCC=14V Vfb=GND, VCC=10V Vfb=GND, VCC=18V 3 5 mA IOVER Vfb=5V, VCC=14V 2.2 2.5 2.8 A VBEN VBDV Vcc=14V Vcc=14V 0.5 0.7 V V Ts Vfb=3 10 15 msec VOVP VOCP TSD 18 1.44 130 19 1.6 145 20 1.76 160 V V C IFB VSD Idelay VFB=GND VFB 5.5V VFB=5V 0.7 5.5 2.8 0.9 6.0 3.5 1.1 6.5 4.2 mA V A FOSC FOSC DMAX DMIN VFB = 3V -25C Ta 85C 60 0 0 75 66 1 5 80 72 3 10 85 0 kHz % % % % FSTABLE 13V Vcc 18V VSTART VSTOP VFB=GND VFB=GND 11 7 12 8 13 9 V V Symbol Condition Min. Typ. Max. Unit

Note: 1. These parameters, although guaranteed at the design, are not tested in mass production.. 2. These parameters, although guaranteed, are tested in EDS(wafer test) process.

FSDM07652R

Typical Performance Characteristics

(These Characteristic Graphs are Normalized at Ta= 25C)

1.2 1.0 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

1.2 1.0 Start Thershold Voltage (Normalized to 25) 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

Operating Current (Normalized to 25)

1.2 1.0 Stop Threshold Voltage (Normalized to 25)

Initial Frequency (Normalized to 25)

1.2 1.0 0.8 0.6 0.4 0.2 0.0

0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

-50

-25

25

50

75

100

125

Junction Temperature()

1.2 1.0 Maximum Duty Cycle (Normalized to 25) FB Source Current (Normalized to 25) -50 -25 0 25 50 75 100 125 0.8 0.6 0.4 0.2 0.0 Junction Temperature()

1.2 1.0 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

FSDM07652R

Typical Performance Characteristics (Continued)

(These Characteristic Graphs are Normalized at Ta= 25C)

1.2 1.0 Shutdown FB Voltage (Normalized to 25) 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

1.2 1.0 Shutdown Delay Current (Normalized to 25) 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

1.2 1.0 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

Burst Mode Enable Voltage (Normalized to 25)

1.2 1.0 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

Over Voltage Protection (Normalized to 25)

1.2 1.0 Over Current Limit (Normalized to 25) 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

1.2 1.0 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

Burst Mode Disable Voltage (Normalized to 25)

FSDM07652R

Typical Performance Characteristics(Continued)

(These Characteristic Graphs are Normalized at Ta= 25C)

1.2 1.0 Soft Start Time (Normalized to 25) 0.8 0.6 0.4 0.2 0.0 -50 -25 0 25 50 75 100 125 Junction Temperature()

FSDM07652R

Functional Description

1. Startup : At startup, an internal high voltage current source supplies the internal bias and charges the external capacitor that is connected to the Vcc pin as illustrated in figure 1. When Vcc reaches 12V, the FPS begins switching operation and the internal high voltage current source is disabled. Then, the FPS continues its normal switching operation until Vcc goes below the stop voltage of 8V and the power is supplied from the auxiliary transformer winding.

V DC Vc

Vcc 2uA Vref 0.9mA

OSC

Vo

Vfb

FB 4

Cfb

D1

D2 Vfb*

28R Gate driver

R

431

VSD

OLP

Figure 2. Pulse width modulation (PWM) circuit

Vcc 3 6

Vstr

Istart

Vref 8V/12V Vcc good Internal Bias

Figure 1. Internal startup circuit

2. Feedback Control : FSDM07652R employs current mode control. As illustrated in figure 2, the feedback voltage determines the peak value of the SenseFET drain current. Usually opto-coupler along with TL431 are used to implement feedback network. The collector of the optocoupler transistor is connected to feedback pin and the emitter is connected to the ground pin. When the voltage of the reference pin of TL431 exceeds the internal reference voltage of 2.5V, the optocoupler diode current increases, pulling down the feedback voltage. 2.1 Pulse-by-pulse current limit: Because current mode control is employed, the drain current of the power MOSFET is limited by the inverting input of PWM comparator (Vfb*). Assuming that the 0.9mA current source flows only through the internal resistor (2.5R +R= 3 k), the cathode voltage of diode D2 is about 2.7V. Since D1 is blocked when the feedback voltage (Vfb) exceeds 2.7V, the maximum voltage of the cathode of D2 is 2.7V. Therefore, the maximum value of Vfb* is about 0.8V, which determines the maximum peak value of the power MOSFET drain current. 2.2 Leading edge blanking (LEB) : When MOSFET turns on, usually there exists high current spike in the MOSFET current caused by primary-side capacitance and secondaryside rectifier reverse recovery. In order to prevent premature termination of the switching pulse due to the current spike, the FPS employs leading edge blanking (LEB). The leading edge blanking circuit inhibits the PWM comparator for a short time after the MOSFET is turned on.

3. Protection Circuit : The FSDM07652R has 4 self protective functions such as over load protection (OLP), abnormal over current protection (AOCP), over voltage protection (OVP) and thermal shutdown (TSD). Because these protection circuits are fully integrated into the IC without external components, the reliability can be improved without cost increase. In the event of these fault conditions, the FPS enters into auto-restart operation. Once the fault condition occurs, switching operation is terminated and MOSFET remains off, which forces Vcc to be reduced. When Vcc reaches 8V, the protection is reset and the internal high voltage current source charges Vcc capacitor. When Vcc reaches 12V, the FPS resumes its normal operation if the fault condition is removed. In this manner, the auto-restart alternately enables and disables the switching of the power MOSFET until the fault condition is eliminated as shown in figure 3.

Fault occurs

Vds

Power on

Fault removed

Vcc

12V 8V

t

Normal operation Fault situation Normal operation

Figure 3. Auto restart operation after protection

3.1 Over Load Protection (OLP) : Overload means that the load current exceeds a pre-set level due to an abnormal situation. In this situation, protection circuit should be activated in order to protect the SMPS. However, even when the 9

FSDM07652R

SMPS is in the normal operation, the over load protection circuit can be activated during the load transition. In order to avoid this undesired operation, the over load protection circuit is designed to be activated after a specified time to determine whether it is a transient situation or an overload situation. Because of the pulse-by-pulse current limit capability, the maximum peak current through the SMPS is limited, and therefore the maximum input power is restricted with a given input voltage. If the output consumes beyond this maximum power, the output voltage (Vo) decreases below the set voltage. This reduces the current through the opto-coupler diode, which also reduces opto-coupler transistor current increasing feedback voltage (Vfb). If Vfb exceeds 2.7V, D1 is blocked and the 3.5uA current source starts to charge Cfb slowly compared to when the 0.9mA current source charges Cfb. In this condition, Vfb continues increasing until it reaches 6.0V, and the switching operation is terminated at that time as shown in figure 4. The delay time for shutdown is the time required to charge Cfb from 2.7V to 6.0V with 3.5uA.

3.3 Over voltage Protection (OVP) : In case of malfunction in the secondary side feedback circuit, or feedback loop open caused by a defect of solder, the current through the optocoupler transistor becomes almost zero. Then, Vfb climbs up in a similar manner to the over load situation, forcing the preset maximum current to be supplied to the SMPS until the over load protection is activated. Because energy more than required is provided to the output, the output voltage may exceed the rated voltage before the over load protection is activated, resulting in the breakdown of the devices in the secondary side. In order to prevent this situation, an over voltage protection (OVP) circuit is employed. In general, Vcc is proportional to the output voltage and the FPS uses Vcc instead of directly monitoring the output voltage. If VCC exceeds 19V, OVP circuit is activated resulting in termination of the switching operation. In order to avoid undesired activation of OVP during normal operation, Vcc should be properly designed to be below 19V. 3.4 Thermal Shutdown (TSD) : The SenseFET and the control IC are built in one package. This makes it easy for the control IC to detect the heat generation from the SenseFET. When the temperature exceeds approximately 145C, the thermal shutdown is activated. 4. Soft Start : FSDM07652R has an internal soft start circuit that increases the feedback voltage together with the MOSFET current slowly when it starts up. The soft start time is 10msec.

V FB Over load protection

6.0V

2.7V

T 12 = Cfb*(6.0-2.7)/I delay

T1

T2

Figure 4. Over load protection

3.2 Abnormal Over Current Protection (AOCP) : When the transformer secondary pins or the rectifier diodes are shorted, a steep current with extremely high di/dt can flow during the LEB time. Therefore, the abnormal over current protection (AOCP) block is added to ensure the reliability as shown in figure 5. It turns off the SenseFET within 300ns after the abnormal over current condition is sensed.

5. Burst operation : I In order to minimize the power dissipation in the standby mode, FSDM07652R has burst operation. The FPS enters into the auto burst mode for itself when the feedback voltage decreases as the load decreases. When the feedback voltage decreases below 0.5V, the FPS stops the switching operation. Then, the output voltage drops below the set voltage, which increases the feedback voltage. When the feedback voltage goes higher than 0.7V, the FPS resumes the switching operation and the feedback voltage decreases. When the feedback voltage drops to 0.5V again, the FPS ceases the switching operation. In this manner, the burst operation alternately enables and disables the switching of the power MOSFET to reduce the switching loss in the standby mode.

2.5R Vx

OSC

PWM

S R

Q Q

Gate driver

LEB

2 Vocp GND

AOCP

-

Figure 5. AOCP block

10

FSDM07652R

Vo

Vo set

VFB

0.7V 0.5V

Ids

Vds

time

Figure 6. Waveforms of auto burst operation

11

FSDM07652R

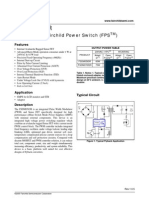

Typical application circuit

1. 40W Universal Input Power Supply For LCD Monitor

1 + 2

T1:EER 3016

10

D202 MBRF10100

L201

DB101 1 2KBP06M3N257 -

C104 10nF/1kV 3 + C103 100uF/400V R102 30K R105 40K

R103 56K/2W 2 2 D101 UF4007 3

C201 1000uF/25V 8

C202 + 1000uF/25V

12V

C102 220nF/275VAC

R104 5

D102 TVR10G

D201 MBRF1045

L202

6 5 Line Filter: LF101:23mH 4 3

Vstr N.C Vfb Vcc

Drain GND

1 2

C203 1000uF/10V 5 C301 4.7nF R201 1K 6

C204 + 1000uF/10V

5V

R101 560K/1W ZD101 22V +

IC101 FSDM07652R

C101 220n/275VAC

C105 22uF/50V

C106 47nF/50V

IC301 H11A817A

R202 R204 1.2k 5.6K R203 1.2k IC201 KA431 C205 47nF R205 5.6K

RT101

5D-9

250V 2A

F101 FUSE

2. Transformer Schematic Diagram

1 Np 2

10

Nvo1 3 8 7 Nvcc 4 Nvo2

12

FSDM07652R

3.Winding Specification

No Nvcc Np/2 Nvo1 Nvo2 Np/2 Pin (sf) 45 21 10 8 76 32 Wire 0.2 1 Turns 8 18 7 3 18 Winding Method Center Winding Solenoid Winding Center Winding Center Winding Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 2Layers 0.4 1 0.3 3 0.3 3 0.4 1 Insulation: Polyester Tape t = 0.050mm, 2Layers Insulation: Polyester Tape t = 0.050mm, 2Layers Insulation: Polyester Tape t = 0.050mm, 2Layers Outer Insulation: Polyester Tape t = 0.050mm, 2Layers

4.Electrical Charateristics

Pin Inductance Leakage Inductance 1-3 1-3 Specification 520uH 10% 10uH Max Remarks 100kHz, 1V 2nd all short

5. Core & Bobbin

Core : EER 3016 Bobbin : EER3016 Ae(mm2) : 96

13

FSDM07652R

6.Demo Circuit Part List

Part F101 RT101 R101 R102 R103 R104 R105 R201 R202 R203 R204 R205 Value Fuse 2A/250V NTC 5D-9 Resistor 560K 30K 56K 5 40K 1K 1.2K 1.2K 5.6K 5.6K 1W 1/4W 2W 1/4W 1/4W 1/4W 1/4W 1/4W 1/4W 1/4W Bridge Diode BD101 Capacitor C101 C102 C103 C104 C105 C106 C201 C202 C203 C204 C205 220nF/275VAC 220nF/275VAC 100uF/400V 10nF/1kV 22uF/50V 47nF/50V 1000uF/25V 1000uF/25V 1000uF/10V 1000uF/10V 47nF/50V Box Capacitor Box Capacitor Electorlytic Capacitor Ceramic Capacitor Electorlytic Capacitor Ceramic Capacitor Electorlytic Capacitor Electorlytic Capacitor Electorlytic Capacitor Electorlytic Capacitor Ceramic Capacitor IC101 IC201 IC301 FSDM07652R KA431(TL431) H11A817A LF101 23mH IC FPS(7A,650V) Voltage reference Phote coupler(QT) Line Filter Wire 0.4mm 2KBP06M 3N257 Bridge Diode D101 D102 D201 D202 ZD101 UF4007 TVR10G MBRF1045 MBRF10100 Zener Diode 22V Diode L201 L202 5uH 5uH Inductor Wire 1.2mm Wire 1.2mm Note Part C301 Value 4.7nF Note Polyester Film Cap.

14

FSDM07652R

Package Dimensions

TO-220F-6L(Forming)

15

FSDM07652R

Ordering Information

Product Number FSDM07652RYDTU

YDTU : Forming Type

Package TO-220F-6L(Forming)

Marking Code DM07652R

BVdss 650V

Rds(on)Max. 1.6

DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

www.fairchildsemi.com 9/22/03 0.0m 001 Stock#DSxxxxxxxx 2003 Fairchild Semiconductor Corporation

2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

You might also like

- Sony Hcd-gx470 Gx570Document106 pagesSony Hcd-gx470 Gx570Daniel González100% (1)

- Max 17126Document34 pagesMax 17126918329078250% (2)

- Datasheet CM6802Document18 pagesDatasheet CM6802Gilson3DNo ratings yet

- LG Chassis MC 049a RT 29fd15Document31 pagesLG Chassis MC 049a RT 29fd15Alana Clark100% (2)

- OB2269Document12 pagesOB2269Juan Ballon100% (1)

- V270B1-L01 T-ConDocument31 pagesV270B1-L01 T-ConKerrie PerryNo ratings yet

- Bd9397efv e PDFDocument30 pagesBd9397efv e PDFshafiuddin7326No ratings yet

- Pa-9312 9324 9336Document2 pagesPa-9312 9324 9336cadatiNo ratings yet

- (Codientu - Org) - 29Q317B, CHASSIS CW4Document14 pages(Codientu - Org) - 29Q317B, CHASSIS CW4GioVoTam100% (1)

- Manual TV TRCDocument14 pagesManual TV TRCPedro MoraNo ratings yet

- General Description Features: Cost Effective LED ControllerDocument10 pagesGeneral Description Features: Cost Effective LED ControlleranilNo ratings yet

- Service Manual CD Stereo System NSX-D20 NSX-R20Document56 pagesService Manual CD Stereo System NSX-D20 NSX-R20taz1mxNo ratings yet

- LG Eay62609701 Pspi-L103aDocument23 pagesLG Eay62609701 Pspi-L103aIvanilto Martins da Cruz100% (1)

- 7cw SMD Mmbt2222a - NXPDocument8 pages7cw SMD Mmbt2222a - NXPnikkoninNo ratings yet

- Okok Sony - kv-2197m3 - Cxp85220a - Tda8375 - str-6707 - La7830 - Ta8248k PDFDocument13 pagesOkok Sony - kv-2197m3 - Cxp85220a - Tda8375 - str-6707 - La7830 - Ta8248k PDFAloui Zakaria100% (1)

- Sony HCD Bx3 Dx3Document66 pagesSony HCD Bx3 Dx3videoson100% (2)

- Dap011 DDocument24 pagesDap011 Dsontuyet82No ratings yet

- Sony STR-De635 Ver 1.1Document58 pagesSony STR-De635 Ver 1.1rumendm100% (1)

- Service Manual: Model: HT-2199 (Europe)Document48 pagesService Manual: Model: HT-2199 (Europe)Eze KielNo ratings yet

- General Description Product Summary: Bvdss Rdson IDDocument4 pagesGeneral Description Product Summary: Bvdss Rdson IDDavid BarriosNo ratings yet

- Datasheet DMO565RDocument21 pagesDatasheet DMO565RSteve Bravo83% (6)

- Bd7682fj LB eDocument30 pagesBd7682fj LB eKartik ShuklaNo ratings yet

- D 1875 LM 1875 Nte 7143Document2 pagesD 1875 LM 1875 Nte 7143ANTONIO PEREZNo ratings yet

- SOYEA LCD Service Manual PDFDocument40 pagesSOYEA LCD Service Manual PDFraipedriNo ratings yet

- Game Monitor Series: MODEL: VS-20475 VS-14428Document13 pagesGame Monitor Series: MODEL: VS-20475 VS-14428silgaNo ratings yet

- Maida Catalog Specifications Standard SeriesDocument16 pagesMaida Catalog Specifications Standard SeriesRetanaMaferNo ratings yet

- 2576 LDocument9 pages2576 LclanonNo ratings yet

- WR - DA7 Manual de ServicioDocument86 pagesWR - DA7 Manual de ServicioDanielNo ratings yet

- Enhancement Mode N-Channel Power MOSFET: OSG65R900xTFDocument10 pagesEnhancement Mode N-Channel Power MOSFET: OSG65R900xTFCube7 Geronimo100% (1)

- Vestel 17mb62-1 SCHDocument9 pagesVestel 17mb62-1 SCHb.nedelkov100% (2)

- DC BRUSHLESS DRIVER BLDC-5015A manualDocument5 pagesDC BRUSHLESS DRIVER BLDC-5015A manualroozbehxoxNo ratings yet

- TV Sanyo Cm29af8x (La76818)Document34 pagesTV Sanyo Cm29af8x (La76818)deimos1No ratings yet

- Videocon Nano1-Cst Vcn14mbf-CnaDocument24 pagesVideocon Nano1-Cst Vcn14mbf-CnaRamesh Singh100% (1)

- Panasonic TX-25lk1p TX-28lk1p Chassis z8Document22 pagesPanasonic TX-25lk1p TX-28lk1p Chassis z8drrebyNo ratings yet

- DTQ 20v1ssDocument48 pagesDTQ 20v1sselectronika806067% (3)

- PF6000AGDocument1 pagePF6000AGlibre2009No ratings yet

- S1117 Adjustable and Fixed LDO Voltage RegulatorsDocument6 pagesS1117 Adjustable and Fixed LDO Voltage RegulatorszincdnlNo ratings yet

- Tps 54628Document22 pagesTps 54628fet_50No ratings yet

- Xr-A670 370Document78 pagesXr-A670 370pepitito22No ratings yet

- การติดตั้งแผงโซล่าเซลล์ในบ้านรุปแบบวิธีการและเอกสารDocument39 pagesการติดตั้งแผงโซล่าเซลล์ในบ้านรุปแบบวิธีการและเอกสารChanade WichasilpNo ratings yet

- AN733 Graphic Eq Ic Data SchematicDocument5 pagesAN733 Graphic Eq Ic Data SchematicrobertlivingstoneNo ratings yet

- BN44-00554B PD32GV0Document3 pagesBN44-00554B PD32GV0Devorador De PecadosNo ratings yet

- Transistor specifications comparison tableDocument440 pagesTransistor specifications comparison tableRicardo Calderon ClarosNo ratings yet

- Sony HCD Rv222 Ver 1.1Document86 pagesSony HCD Rv222 Ver 1.1Carlos Raul100% (2)

- PORTABLE CD/MP3 RADIO CASSETTE RECORDER SPECIFICATIONSDocument23 pagesPORTABLE CD/MP3 RADIO CASSETTE RECORDER SPECIFICATIONSLuis Ardila100% (1)

- Silicon P-Channel MOSFET Features and SpecificationsDocument9 pagesSilicon P-Channel MOSFET Features and SpecificationsLuis AbrahamNo ratings yet

- TDA8375ADocument73 pagesTDA8375Asontuyet82No ratings yet

- DM 0565 RDocument20 pagesDM 0565 R81968No ratings yet

- DatasheetDocument20 pagesDatasheetWellington DiasNo ratings yet

- IC-ON-LINE - CN dm0365r 44840Document20 pagesIC-ON-LINE - CN dm0365r 44840MoscandoNo ratings yet

- DM0265Document19 pagesDM0265liberthNo ratings yet

- FSDH0265RN, FSDM0265RN: Green Mode Fairchild Power Switch (FPS)Document20 pagesFSDH0265RN, FSDM0265RN: Green Mode Fairchild Power Switch (FPS)Wsad WsadNo ratings yet

- 161 20551 0 FS7M0880Document16 pages161 20551 0 FS7M0880Edwin Vitovis TorresNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- Fan 7314Document14 pagesFan 7314Kamal NonekNo ratings yet

- DM0565Document21 pagesDM0565Tammy WashingtonNo ratings yet

- CM0565R-FSCM0565RC - A23865227 10699 PDFDocument21 pagesCM0565R-FSCM0565RC - A23865227 10699 PDFAnonymous mzYL0zDGNo ratings yet

- DL 0165 RDocument20 pagesDL 0165 Rledu035No ratings yet

- Ic 3843Document4 pagesIc 3843nishatiwari82No ratings yet

- CD Player REVOX b225 Service en deDocument125 pagesCD Player REVOX b225 Service en demarianos67No ratings yet

- 43uk6950 Eng PDFDocument30 pages43uk6950 Eng PDFmarianos67No ratings yet

- 43uk6950 Eng PDFDocument30 pages43uk6950 Eng PDFmarianos67No ratings yet

- Alesis RA500 Power AmplifierDocument32 pagesAlesis RA500 Power AmplifierputitibiNo ratings yet

- Inverter LCD Bit3105pDocument1 pageInverter LCD Bit3105pmarianos67No ratings yet

- Vaddis8 DVD ProcessorDocument2 pagesVaddis8 DVD Processormarianos67No ratings yet

- LP78A CH - 32LC7R - 32LC51 - 32LC52Document38 pagesLP78A CH - 32LC7R - 32LC51 - 32LC52Ermir KafaziNo ratings yet

- AIWA CDC-R136 SchematicsDocument2 pagesAIWA CDC-R136 Schematicsmarianos67No ratings yet

- VTU Seminar Report on Plastic MemoryDocument31 pagesVTU Seminar Report on Plastic MemoryKasetti BharathiNo ratings yet

- TEC40092203Document11 pagesTEC40092203Dhanesh GoelNo ratings yet

- Fm-200 Component Description: Discharge IndicatorsDocument1 pageFm-200 Component Description: Discharge IndicatorsLogan Marquez AguayoNo ratings yet

- HUMAN COMPUTER INTERACTION ASSIGNMENTDocument8 pagesHUMAN COMPUTER INTERACTION ASSIGNMENTSamridhi SamNo ratings yet

- Polyamide 610 KasarDocument8 pagesPolyamide 610 KasarAlison BurksNo ratings yet

- Modified Sine-Wave Inverter Enhanced With New WaveformDocument3 pagesModified Sine-Wave Inverter Enhanced With New WaveformJoão Pedro AlmeidaNo ratings yet

- GIS OrmazabalDocument40 pagesGIS Ormazabalnarinder kumarNo ratings yet

- FET Terminal Functions and JFET Biasing CharacteristicsDocument7 pagesFET Terminal Functions and JFET Biasing CharacteristicsDiana Jane Terez LazaroNo ratings yet

- Adc 1283Document24 pagesAdc 1283Manuel MarquesNo ratings yet

- Waveform DifferentiationDocument10 pagesWaveform DifferentiationJun YoutubeNo ratings yet

- Gemstone WarriorDocument14 pagesGemstone Warriorremow67% (3)

- Kingston EMMC32G IX29 8AD01 v1 2-3236216Document26 pagesKingston EMMC32G IX29 8AD01 v1 2-3236216ManunoghiNo ratings yet

- Analysis of Constant-Current Characteristics For Current SourcesDocument6 pagesAnalysis of Constant-Current Characteristics For Current SourcesFitri PuspasariNo ratings yet

- User Manual GuideDocument28 pagesUser Manual Guideahmad zahafizNo ratings yet

- Panasonic OnsitegoDocument1 pagePanasonic Onsitegosu30solomonNo ratings yet

- QuestionsDocument7 pagesQuestionsVeera AnjuNo ratings yet

- Compact solenoid valves for commercial applicationsDocument16 pagesCompact solenoid valves for commercial applicationsJorge Jarpa VNo ratings yet

- Att Acquisition by Bloom BergDocument32 pagesAtt Acquisition by Bloom BergcrosleyjNo ratings yet

- 0186660sby-E Nexus Lts 200aDocument2 pages0186660sby-E Nexus Lts 200aRabzyyNo ratings yet

- MRA 4 Incoming and Outgoing Feeder ProtectionDocument2 pagesMRA 4 Incoming and Outgoing Feeder ProtectionFlo MircaNo ratings yet

- 01 - GST UL System Overview - 2017v2.1Document42 pages01 - GST UL System Overview - 2017v2.1RaviNo ratings yet

- Audio UnitsDocument3 pagesAudio Unitsjoosh908No ratings yet

- RRB Assistant Loco Pilot Syllabus 2015, Download PDF - E-Job Mart RecruitmentDocument6 pagesRRB Assistant Loco Pilot Syllabus 2015, Download PDF - E-Job Mart RecruitmentMonirul Islam0% (1)

- 3.5 To 30 MHZ Automatic Antenna Impedance Matching SystemDocument100 pages3.5 To 30 MHZ Automatic Antenna Impedance Matching SystemAlexandru MaiorNo ratings yet

- Digital Laser MFP SCX-6322DN Service ManualDocument185 pagesDigital Laser MFP SCX-6322DN Service ManualjaimecamoNo ratings yet

- A Perspective On Online Partial Discharge Monitoring For Assessment of The Condition of Rotating Machine Stator Winding InsulationDocument6 pagesA Perspective On Online Partial Discharge Monitoring For Assessment of The Condition of Rotating Machine Stator Winding InsulationfbogomesNo ratings yet

- Company ProfileDocument11 pagesCompany ProfileRobito LubisNo ratings yet

- Free Space OpticsDocument14 pagesFree Space OpticsMahesh PatilNo ratings yet

- Experiment-5:: Program DefinitionDocument4 pagesExperiment-5:: Program DefinitionAmitabh KumarNo ratings yet

- Free Energy Ws John BediniDocument4 pagesFree Energy Ws John Bedinigui9871No ratings yet