Professional Documents

Culture Documents

Digital Electronics and Circuits

Uploaded by

GuruKPOOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Electronics and Circuits

Uploaded by

GuruKPOCopyright:

Available Formats

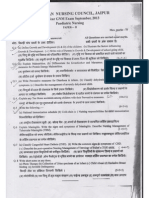

This question paper contains 16+8+3 printed pages]

B.C.A (Pt.II) 212 Digital Elect. And Circuits

BACHELOR OF COMPUTER APPLICATION (Part II) EXAMINATION,2013 (Faculty of Science)

(Three-Year Scheme of 10+2+3 Pattern) DIGITAL ELECTRONICS AND CIRCUITS PAPER 218 TIME ALLOWED: THREE HOURS Maximum Marks

Answers of all the question (objective as well as descriptive) are to be given in the main answer-book only. Answer of objective type questions must be given in sequential order. Similarly all the parts of one question of descriptive part should be answered at one place in the answer-book. One complete question should not be answered at different places in the answer-book. No supplementary answer-book will be given to any candidate. Hence the candidates should write their answers precisely in the main answer-book only.

OBJECTIVE PART-I Maximum Marks: 20 It contains 40 multiple choice questions with four choices and students will have to pick the correct one (each carrying mark) 1 Octal equivalent of (47)10 is (a) 49 (b) 57

(c) 21 (d) 48 2 Decimal value of hexadecimal FFFF is : (a) 65535 (b) 65534 (c) 65536 (d) 65537 3 Decimal value of hexadecimal FFFF is : (a) C (b) C (c) A (d) A 4 A(A+B) will reduce to : (a) AB (b) AB (c) A+B (d) A+B 5 Which of the following logic expressions is wrong? (a) 1 0 =1 (b) 1 1 =0 (c) 1 (d) 1 6 The NAND gate is AND gate followed by : (a) AND gate (b) NOR gate (c) NOT gate (d) None of the above

7 A half-adder consists of : (a) X-OR and OR gates (b) AND and OR gates (c) X-OR and AND gates (d) XOR, AND and OR gates 8 256 kB memory is equivalent to : (a) 2,52,144 byte (b) 2,62,144 byte (c) 2,72,144 byte (d) 2,56,000 byte 9 The transistor is in off state when it is in : (a) Cut-off (b) Saturation (c) Active (d) None of the above 10 The term RTL means : (a) Retreat logic (b) Receiver through logic (c) Resistor-transistor logic (d) Reverse transistor logic 11 A diode is called in condition state, when (a) It is in reverse biased (b) Without biasing (c) It is in forward biased (d) Either (a) or (b) 12 Which one of the following gates is used as parity checker? (a) NOT (b) NAND

(c) NOR (d) EX-NOR 13 The simplest expression of AA + B B is : (a) B (b) B (c) A (d) A 14 De-Morgans first theorem is given by: (a) A+B = AB (b) A+B =AB (c) A+B=A+B (d) A+B=AB 15 The SOP form of logical expression is most suitable for design logic circuit using only: (a) NAND gate (b) NOR gates (c) EX-OR gates (d) AND gates 16 Which is not a minimization technique for logical expression? (a) Using Boolean theorem (b) Karnaugh map (c) Gate realization (d) Quine McCluskey method 17 Dont care combination are assumed: (a) Always 0 (b) Always 1 (c) Either 0 or 1 (d) Neither 0 nor 1

18 The maxterm M0 is equivalent to: (a) (A+B + C + D) (b) A B C D (c) ABCD (d) (A + B +C +D) 19 The function : Can be written as : (a) (b) (c) (d) 20 Minimization of logical expression while designing digital helps in reducing : (a) Cost (b) Space requirements (c) Power requirements (d) All of the above 21 A standard TTL, gate, average power dissipation is : (a) 10nw (b) 10 (c) 1mw (d) 10mw 22 Schottky TTL series is given by the IC: (a) 7400 (b) 74S00 (c) 74H00

(d) 74L00 23 If the applied voltage in MOSFET is more than the threshold voltage, then it behaves like: (a) Closed switch (b) Open switch (c) FET (d) BJT 24 The most suitable IC family for LSI chips: (a) TTL (b) ECL (c) NMOS (d) RTL 25 The IC which is used as decimal to BCD priority encoder is : (a) 74145 (b) 74180 (c) 74147 (d) 7490 26 The IC which is used as 4 line to 16 line decoder demultiplexer is: (a) 74150 (b) 74151 (c) 74154 (d) 74152 27 Filp-flop is a : (a) Monostable device (b) Bistable device (c) Astable device (d) None of the above

28 In a J-K flip-flop if J=1 and K=0, then the output Q and Q (when the clock input is applied ) as : (a) Q =1 and Q =1 (b) Q=0 and Q =0 (c) Q=1 and Q= 0 (d) Q = 0 and Q=1 29 A type of shift register that requires access to the Q outputs of all stages is : (a) Serial in-parallel out (b) Parallel in-serial out (c) Serial in-serial out (d) A bidirectional shift register 30 A major drawback to an SR latch is its: (a) Complexity (b) Slow speed (c) Invalid condition (d) Latch mode 31 A 4-bit binary UP/DOWN counter is in the binary state of zero. The next state in DOWN mode is: (a) 0001 (b) 1111 (c) 1000 (d) 1110 32 A 3-bit binary counter has a maximum modulus of : (a) 3 (b) 6 (c) 8 (d) 16

33 To obtain output frequency equal to half the clock frequency, one should use the counter: (a) Decade counter (b) Up counter (c) Down counter (d) Johnson counter 34 The SiO2 layer in an IC acts as : (a) Mechanical output (b) A register (c) An insulating layer (d) None of the above 35 The component cannot be fabricated on IC: (a) Transistors (b) Diodes (c) Resistors (d) Inductors and transformers 36 The highest count in an n-bit ripple counter is : (a) (b) (c) (d) 37 The simplified Boolean expression in SOP form from K-map given below is: C AB 00 01 11 10 0 0 1 1 0

(a) BC (b) BC (c) AB (d) BC

+ + + +

BC BC BC AB

38 The Boolean function F simulated by the logic circuit, is : A F B (a) A.B (b) A.B (c) A+B + C (d) A 39 .The truth table of a logic gate is given below. The gate is : A 0 1 0 1 B 0 0 1 1 Y 0 1 1 0

(a) OR (b) XOR (c) NAND (d) NOR

40 -

A B S

C The above diagram is of: (a) Subs tractor (b) Full adder (c) Multiplexer (d) Half adder

DESCRIPTIVE PART-II Maximum Marks :30 Attempt any four descriptive type of questions out of six. All questions carry 7.5 marks each. 1- (a) (b) (b) What is EX-NOR gate? Give its significance. 2 Draw the block diagram and truth table of the following basic gates. AND, NOR, XOR, and Bubbled OR. Solve expression : Y= AB + AC + ABC (AB + C) Using Boolean theorems. 2- (a) (b) (c) Prove the statement A positive logic AND operation is equivalent to a negative logic OR operation and vice-versa. Realize the circuit of EX-OR gate with the help of Boolean theorems by using NOR gate only Prove that: AB + C (A + D) = AB + BD +BD + A C D If AB + CD =0 Given the logical expression : Y(A, B C) = (A +BC) . (B+ CA) (i) Convert this equation in sum-of-products (SOP)form and in product-of-sums (POS) form. (ii) Design the circuits with only one type of gates corresponding to SOP and POS equations obtained above. Express the following function into minterm and maxterm notation :Y=(A,B,C,D) =D What is use of K-map in circuit in circuit designing? Define redundant group in a given K-map.

3- (a)

(b) (c)

4- (a)

Write short notes on the following ICs : (i) 7400 (ii) 74S00 (iii) 74L00 Explain speed and delay in logic circuits. Draw CMOS NOR gate and explain its operation. Define multiplexer. Draw the pin out diagram and truth table for IC74151, 8 to 1 multiplex. Explain the construction and working of a 1:16 demultiplexer. Draw pin out diagram and logic diagram for 74154 demultiplexer IC and truth table for this. Write brief notes on the : (i) Priority encoder , and (ii) Up/down counter Make circuits for SR flip-flop using NAND gates and NOR gate. Convert one of these circuits into clocked SR flip-flop and make truth table for this . What is meant by edge triggering? Give the difference between positive and negative edge triggering. What is ripple counter and ring counter? Write their application one of each counter.

(b) (c) 5- (a) (b)

(c)

6- (a)

(b) (c)

_________________

You might also like

- CS 25000 Spring 2017 Final Practice SolutionsDocument13 pagesCS 25000 Spring 2017 Final Practice SolutionsTiger TangNo ratings yet

- Advanced Algorithms Quiz 3Document2 pagesAdvanced Algorithms Quiz 3mathuNo ratings yet

- Assembly x86 Exam1 SolutionDocument5 pagesAssembly x86 Exam1 Solutionkhayat_samirNo ratings yet

- Motorola TETRA MTH800 Basic User Guide enDocument218 pagesMotorola TETRA MTH800 Basic User Guide enForum PompieriiNo ratings yet

- Mcqs On MicrocontrollerDocument8 pagesMcqs On Microcontrollernitesh100% (1)

- IES - Electronics Engineering - Digital Electronic CircuitsDocument66 pagesIES - Electronics Engineering - Digital Electronic Circuitsedwinaustine100% (4)

- Biyani's Think Tank: Concept Based NotesDocument49 pagesBiyani's Think Tank: Concept Based NotesGuruKPO71% (7)

- Digital Logic Design ProjectsDocument23 pagesDigital Logic Design ProjectsMychon KanNo ratings yet

- CS2010Document19 pagesCS2010Rahul RoyNo ratings yet

- Digital Number Systems 3 AnsDocument3 pagesDigital Number Systems 3 AnsbhagNo ratings yet

- GATE 2015 COMPUTER SCIENCE QUESTIONS AND ANSWERSDocument12 pagesGATE 2015 COMPUTER SCIENCE QUESTIONS AND ANSWERSPooja SinhaNo ratings yet

- Computer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GateDocument8 pagesComputer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GatepranavbommiNo ratings yet

- CS Sample Paper QuestionsDocument12 pagesCS Sample Paper QuestionsAnuragGuptaNo ratings yet

- Computer Architecture Objective Type Questions and AnswersDocument129 pagesComputer Architecture Objective Type Questions and AnswersRajesh TiwaryNo ratings yet

- October 2012: Questions Must Be Answered in Accordance With The FollowingDocument31 pagesOctober 2012: Questions Must Be Answered in Accordance With The FollowingAndrew CordonNo ratings yet

- SCM, CSU 201430 ITC161/411 Instruction Set ArchitecturesDocument4 pagesSCM, CSU 201430 ITC161/411 Instruction Set ArchitecturesSaimo MghaseNo ratings yet

- CS GATE'2017 Paper 01 Key SolutionDocument29 pagesCS GATE'2017 Paper 01 Key SolutionnilanjanNo ratings yet

- Cat Ii-G1-Ak: School of Computer Science and Engineering CSE2001-Computer Architecture and OrganizationDocument3 pagesCat Ii-G1-Ak: School of Computer Science and Engineering CSE2001-Computer Architecture and OrganizationkumarklNo ratings yet

- Cache Memory Mapping TechniquesDocument43 pagesCache Memory Mapping TechniquesLalala LandNo ratings yet

- Ugc SolutionDocument174 pagesUgc SolutionNirmal Pandey100% (1)

- Calculate The Size of Memory If Its Address Consists of 22 Bits and The Memory Is 2-Byte AddressableDocument4 pagesCalculate The Size of Memory If Its Address Consists of 22 Bits and The Memory Is 2-Byte AddressableAakash KaushikNo ratings yet

- Digital Logic Design Practice Problems Covering Number Systems, Logic Gates, Boolean Expressions & MoreDocument36 pagesDigital Logic Design Practice Problems Covering Number Systems, Logic Gates, Boolean Expressions & MoreAlexanderHmNo ratings yet

- Ai Unit 1 NotesDocument19 pagesAi Unit 1 NotesIndumathiNo ratings yet

- Digital Logic Circuits Objective Questions PDFDocument9 pagesDigital Logic Circuits Objective Questions PDFNoor AhmedNo ratings yet

- Cid - EttiDocument380 pagesCid - EttiCilibiu Ionuţ-AlinNo ratings yet

- Line Following Robot in VerilogDocument12 pagesLine Following Robot in VerilogAparna GopalNo ratings yet

- DIGITAL SYSTEMS LAB MCQsDocument5 pagesDIGITAL SYSTEMS LAB MCQsSharan SengottuvelNo ratings yet

- On Suitability of Programming Competition Tasks For Automated TestingDocument12 pagesOn Suitability of Programming Competition Tasks For Automated TestingHemesh SinghNo ratings yet

- PpooDocument44 pagesPpooAndrei BadescuNo ratings yet

- Differential Amplifier Using BJTDocument11 pagesDifferential Amplifier Using BJTAssini HussainNo ratings yet

- Module 4 - Number Systems and Boolean AlgebraDocument8 pagesModule 4 - Number Systems and Boolean AlgebraSuyog ChavanNo ratings yet

- X With Respect To Different Bases.: Mca Entrance 1. One Giga Byte Is 11Document5 pagesX With Respect To Different Bases.: Mca Entrance 1. One Giga Byte Is 11Himanshu Agarwal100% (1)

- 100 TOP C Language Multiple Choice Questions and Answers Multiple Choice Questions and Answers Beginners and Experienced PDFDocument32 pages100 TOP C Language Multiple Choice Questions and Answers Multiple Choice Questions and Answers Beginners and Experienced PDFesmani840% (1)

- SS Lab ManualDocument48 pagesSS Lab ManualKannan RNo ratings yet

- Advanced Microprocessors & PeripheralsDocument69 pagesAdvanced Microprocessors & Peripheralsgninagpur0% (1)

- LOGIC - CIRCUITS Final Exam Q2 2010 - 2011 Problems and Answer KeyDocument2 pagesLOGIC - CIRCUITS Final Exam Q2 2010 - 2011 Problems and Answer KeySimon Gregory Mabanta100% (1)

- Assignment 1Document2 pagesAssignment 1kartik0% (1)

- BaremDocument7 pagesBaremFlorin MoldovanuNo ratings yet

- Neamen - Electronic Circuit Analysis and Design 2nd Ed Chap 013Document17 pagesNeamen - Electronic Circuit Analysis and Design 2nd Ed Chap 013greyiris7No ratings yet

- Gate-Cs 2008Document31 pagesGate-Cs 2008tomundaNo ratings yet

- 8051 Microcontroller Bubble Sort Assembly ProgramDocument1 page8051 Microcontroller Bubble Sort Assembly ProgramutpalwxyzNo ratings yet

- Full Adder Using 4x1 MuxDocument3 pagesFull Adder Using 4x1 MuxRasigan UrNo ratings yet

- Dell 5330dn Service ManualDocument206 pagesDell 5330dn Service ManualDeshone MarshallNo ratings yet

- VHDL FaqDocument6 pagesVHDL FaqRavindra Mathanker100% (2)

- Sylveste's Rank InequalityDocument8 pagesSylveste's Rank InequalityRana Vivek SinghNo ratings yet

- DSP Objective QuestionsDocument4 pagesDSP Objective QuestionsshankarNo ratings yet

- Karnaugh Maps - Rules of Simplification: Grouping OnesDocument14 pagesKarnaugh Maps - Rules of Simplification: Grouping OnesProfessor RajputNo ratings yet

- ALL Tehnici de Optimizare Grile RASPUNSURIDocument64 pagesALL Tehnici de Optimizare Grile RASPUNSURImuadib_3000No ratings yet

- Titu Andreescu Contests Around The World 19992000Document344 pagesTitu Andreescu Contests Around The World 19992000claus160867No ratings yet

- DC-Lab Report 02Document10 pagesDC-Lab Report 02Shahriar Ahsan JohaNo ratings yet

- HFSS Tutorial 4: 20-dB Microstrip Coupled Line: W L W S BDocument6 pagesHFSS Tutorial 4: 20-dB Microstrip Coupled Line: W L W S Bamit261287No ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- Testpaper - 1 NTDocument13 pagesTestpaper - 1 NTGattu SadashivaNo ratings yet

- RRB Junior Electronics Engineer Study Material 3Document66 pagesRRB Junior Electronics Engineer Study Material 3thirumalNo ratings yet

- IES Electrical Engineering Topic wise Questions Analog & Digital Circuits YEAR 2008Document81 pagesIES Electrical Engineering Topic wise Questions Analog & Digital Circuits YEAR 2008Vishal KumarNo ratings yet

- Ab+Ab: Base X Base X Base XDocument3 pagesAb+Ab: Base X Base X Base XVani Bindal AgarwalNo ratings yet

- IES - Digital Mock Test - 2014Document9 pagesIES - Digital Mock Test - 2014Meenakshi SundaramNo ratings yet

- Computer Science Gcet Question Papers-2005Document10 pagesComputer Science Gcet Question Papers-2005Lokesh KumarNo ratings yet

- 9Document10 pages9Sachin RathodNo ratings yet

- Digital Logic DesignDocument4 pagesDigital Logic DesignShareef KhanNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Applied ElectronicsDocument40 pagesApplied ElectronicsGuruKPO75% (4)

- Applied ElectronicsDocument37 pagesApplied ElectronicsGuruKPO100% (2)

- Algorithms and Application ProgrammingDocument114 pagesAlgorithms and Application ProgrammingGuruKPONo ratings yet

- Data Communication & NetworkingDocument138 pagesData Communication & NetworkingGuruKPO80% (5)

- Advertising and Sales PromotionDocument75 pagesAdvertising and Sales PromotionGuruKPO100% (3)

- Biyani Group of Colleges, Jaipur Merit List of Kalpana Chawala Essay Competition - 2014Document1 pageBiyani Group of Colleges, Jaipur Merit List of Kalpana Chawala Essay Competition - 2014GuruKPONo ratings yet

- Think Tank - Advertising & Sales PromotionDocument75 pagesThink Tank - Advertising & Sales PromotionGuruKPO67% (3)

- OptimizationDocument96 pagesOptimizationGuruKPO67% (3)

- Abstract AlgebraDocument111 pagesAbstract AlgebraGuruKPO100% (5)

- Production and Material ManagementDocument50 pagesProduction and Material ManagementGuruKPONo ratings yet

- Computer Graphics & Image ProcessingDocument117 pagesComputer Graphics & Image ProcessingGuruKPONo ratings yet

- Phychology & Sociology Jan 2013Document1 pagePhychology & Sociology Jan 2013GuruKPONo ratings yet

- Algorithms and Application ProgrammingDocument114 pagesAlgorithms and Application ProgrammingGuruKPONo ratings yet

- Fundamental of Nursing Nov 2013Document1 pageFundamental of Nursing Nov 2013GuruKPONo ratings yet

- Paediatric Nursing Sep 2013 PDFDocument1 pagePaediatric Nursing Sep 2013 PDFGuruKPONo ratings yet

- Community Health Nursing Jan 2013Document1 pageCommunity Health Nursing Jan 2013GuruKPONo ratings yet

- Phychology & Sociology Jan 2013Document1 pagePhychology & Sociology Jan 2013GuruKPONo ratings yet

- Community Health Nursing I Nov 2013Document1 pageCommunity Health Nursing I Nov 2013GuruKPONo ratings yet

- Community Health Nursing I July 2013Document1 pageCommunity Health Nursing I July 2013GuruKPONo ratings yet

- Business LawDocument112 pagesBusiness LawDewanFoysalHaqueNo ratings yet

- Biological Science Paper I July 2013Document1 pageBiological Science Paper I July 2013GuruKPONo ratings yet

- Service MarketingDocument60 pagesService MarketingGuruKPONo ratings yet

- Biological Science Paper 1 Nov 2013Document1 pageBiological Science Paper 1 Nov 2013GuruKPONo ratings yet

- Business Ethics and EthosDocument36 pagesBusiness Ethics and EthosGuruKPO100% (3)

- Product and Brand ManagementDocument129 pagesProduct and Brand ManagementGuruKPONo ratings yet

- Biological Science Paper 1 Jan 2013Document1 pageBiological Science Paper 1 Jan 2013GuruKPONo ratings yet

- Banking Services OperationsDocument134 pagesBanking Services OperationsGuruKPONo ratings yet

- BA II English (Paper II)Document45 pagesBA II English (Paper II)GuruKPONo ratings yet

- Software Project ManagementDocument41 pagesSoftware Project ManagementGuruKPO100% (1)

- A Mini Project ReportDocument54 pagesA Mini Project ReportPosi NamdamNo ratings yet

- Electrical and Electronics Mini Project Report On Control of PC With TV Remote Cusat UniversityDocument61 pagesElectrical and Electronics Mini Project Report On Control of PC With TV Remote Cusat UniversityAju MtNo ratings yet

- CD4069UBM/CD4069UBC Inverter Circuits DatasheetDocument6 pagesCD4069UBM/CD4069UBC Inverter Circuits DatasheetCamila QuadrosNo ratings yet

- GWSetup Help ManualDocument64 pagesGWSetup Help Manualestefania A.CNo ratings yet

- SN74LS05D - Motorola Hex InverterDocument5 pagesSN74LS05D - Motorola Hex InverterdeTorioNo ratings yet

- Question Bank: Siddharth Group of Institutions:: PutturDocument23 pagesQuestion Bank: Siddharth Group of Institutions:: PutturArindam SenNo ratings yet

- Lmg1205 80-V, 1.2-A To 5-A, Half Bridge Gan Driver With Integrated Bootstrap DiodeDocument24 pagesLmg1205 80-V, 1.2-A To 5-A, Half Bridge Gan Driver With Integrated Bootstrap DiodeArtur ZaidullinNo ratings yet

- I Series CommDocument19 pagesI Series CommYoel OcminNo ratings yet

- Installation & Operating Instructions: Models 150T, 151T, & 152T Smartstep Programmable AttenuatorsDocument12 pagesInstallation & Operating Instructions: Models 150T, 151T, & 152T Smartstep Programmable AttenuatorsMehmet YıldızNo ratings yet

- LT9211 Datasheet R2.1Document18 pagesLT9211 Datasheet R2.1周勇No ratings yet

- Voltage Drop Calculator: Calculate Wire Size & Voltage LossDocument29 pagesVoltage Drop Calculator: Calculate Wire Size & Voltage LossnassimNo ratings yet

- Datasheet Diodo ZenerDocument22 pagesDatasheet Diodo ZenerAntonio Carlos CardosoNo ratings yet

- Data Sheet Nidaq Ni 6008Document5 pagesData Sheet Nidaq Ni 6008Erick Tamayo LoezaNo ratings yet

- T 1000S ManualDocument7 pagesT 1000S Manualmughees_itcompNo ratings yet

- LVC 244a NXPDocument17 pagesLVC 244a NXPChethan RajNo ratings yet

- Creating Your Own Models For Use With Proteus VSM PDFDocument289 pagesCreating Your Own Models For Use With Proteus VSM PDFcarlosgnNo ratings yet

- Del Lab ManualDocument84 pagesDel Lab ManualRohit ChaharNo ratings yet

- ULN2004AC-inversor LvadoraDocument8 pagesULN2004AC-inversor Lvadoraarturo_hernandez_78No ratings yet

- TSS Meridian Gyrocompasses Product LeafletDocument4 pagesTSS Meridian Gyrocompasses Product Leafletlucas barriosNo ratings yet

- 8 Channel Relay Board - Electronics-LabDocument5 pages8 Channel Relay Board - Electronics-LabJavier Mendoza V.No ratings yet

- ISO72x Single Channel High-Speed Digital Isolators: 1 FeaturesDocument36 pagesISO72x Single Channel High-Speed Digital Isolators: 1 FeaturesAnkitNo ratings yet

- Get TRDocDocument229 pagesGet TRDocdkalatzisNo ratings yet

- Jdy 30 Bluetooth ModuleDocument3 pagesJdy 30 Bluetooth ModuleJohan LopezNo ratings yet

- LM7805 Voltage RegulatorDocument9 pagesLM7805 Voltage RegulatorFaris Ichigo IrawanNo ratings yet

- DA-30 Datenblatt Uni Rev-CDocument21 pagesDA-30 Datenblatt Uni Rev-CGaurav AmberkarNo ratings yet

- Max5048aaut (Abwf)Document11 pagesMax5048aaut (Abwf)Dwp BhaskaranNo ratings yet

- Pio16 Plugin Mach3Document2 pagesPio16 Plugin Mach3ramjoceNo ratings yet

- 74HC HCT597Document20 pages74HC HCT597Hamid SamavatiNo ratings yet

- Parity Generator Checker PDFDocument3 pagesParity Generator Checker PDFSujesh P Lal67% (3)