Professional Documents

Culture Documents

Coleccion de Problemas Resueltos de Electronica Digital B Sica

Uploaded by

Hurtado93Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Coleccion de Problemas Resueltos de Electronica Digital B Sica

Uploaded by

Hurtado93Copyright:

Available Formats

UNIVERSIDAD CARLOS III DE MADRID

Problemas de Electrnica Digital: Fundamentos de Ingeniera Electrnica

Grado en Ingeniera Mecnica

2 Curso 2 Cuatrimestre

Fecha: 24/02/2010

Autores: Luis Mengibar, Virginia Urruchi

ESCUELA POLITCNICA SUPERIOR DEPARTAMENTO DE TECNOLOGA ELECTRNICA

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

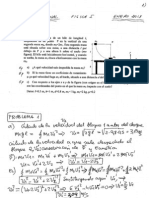

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 1 Convierta el siguiente nmero binario a base decimal. Indique el desarrollo utilizado. Nmero binario: 1110002 Solucin: Utilizando la estructura de pesos para codificacin en base binaria se puede poner:

1 25 + 1 24 + 1 23 + 0 2 2 + 0 21 + 0 20 = = 32 + 16 + 8 + 0 + 0 + 0 = 56

1110002=5610 EJERCICIO 2 Codifique en base octal los siguientes nmeros binarios: a) 10010010012 b) 111000111002 c) 110012 Solucin: a) 10010010012 Se agrupan los dgitos binarios de 3 en 3 tanto a izquierda como a derecha, a partir de la coma. Se aaden los ceros necesarios en los extremos para completar los grupos de 3.

001 { 001 { 001 { 001 {

1 1 1 1

10010010012=11118 b) 111000111002=34348 c) 110012=318 EJERCICIO 3 Codifique en base hexadecimal los siguientes nmeros binarios: b) 1110001112 a) 111000112 Solucin: a) 111000112 Se agrupan los dgitos binarios de 4 en 4 tanto a izquierda como a derecha, a partir de la coma. Se aaden los ceros necesarios en los extremos para completar los grupos de 4.

1110 { 0011 {

E 3

111000112=E316 b) 1110001112=1C716 EJERCICIO 4 Convierta a base binaria los siguientes nmeros hexadecimales: b) F116 c) 78D16 a) CAE 16 Solucin: a) CAE16 Se transforma cada dgito hexadecimal en su correspondiente cdigo binario:

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

C A E } } } 1100 1010 1110

CAE16=1100101011102 b) F116=111100012 c) 78D16=0111100011012 EJERCICIO 5 Convierta a base binaria los siguientes nmeros octales: a) 6538 b) 78 c) 41208 Solucin: a) 6538 Se transforma cada dgito octal en su correspondiente cdigo binario:

6 } 5 } 3 } 110 101 011

6538=1101010112 b) 78=1112 c) 41208=1000010100002 EJERCICIO 6 Exprese en hexadecimal los siguientes nmeros decimales: a) 6084510 b) 1010 c) 1100 10 Solucin: a) 6084510 Como el nmero decimal slo tiene parte entera se aplica divisin sucesiva entre 16.

60845 16 128 3802 0045 60 13 122 10 D A

Solucin: 6084510=EDAD16 b) 1010=A16 c) 110010=44C16 EJERCICIO 7

16 237 16 077 14 MSB 13 E D

Simplifique las siguientes expresiones aplicando las Leyes del lgebra de Boole. a) C B + C B A + C A + A b) C BA + ( A B)(C + BA) Solucin:

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital a)

C B + C BA + C A + A =

= C B + C (1 BA +3 A) + A = 2

A

Propiedad Distributiva Ley de Absorcin Axioma: A + AC = A + C Axioma: C + C B = C + B

= C B + CA + A = = CB + C + A = =C+B+ A

b)

C BA + ( A B)(C + BA) = = C ( B + A) + ( AB + AB)(C BA) = = C B + C A + ( AB + AB)(C B + C A) = = C B + C A + CB A + C B A = =C B+C A

EJERCICIO 8

T De Morgan, OR-exclusivo Prop. Distributiva, T. De Morgan Prop. Distributiva, B B = 0 Ley de Absorcin

Simplifique las siguientes expresiones booleanas utilizando el Teorema de De Morgan y las leyes del lgebra de Boole. a) ( A + B ) C + A + B C + AC b) (( DA + C ) + C ) + B A( A + C ) ( B + D ) Solucin: a)

( A + B) C + A + B C + AC = = A + B + C + A BC + AC = = A B + C + A ( B + C ) + AC = = A B + C + A B + A C + AC = = A B+ A B+C + A=

=C+B+ A

Teorema de De Morgan Teorema de De Morgan Ley Involutiva y Prop. Distributiva Ley de absorcin y C + CA = C + A Ley de absorcin y A + A B = A + B

b) (( DA + C ) + C ) + B A( A + C ) ( B + D ) =

T De Morgan T De Morgan, Distributiva,

= ( DA + C ) C + ( B A + A + C )( B + D) =

CC = 0 = DCA + ( B + A + AC )( B + D) = = DCA + B + DB + B A + D A + C BA + DC A = = DCA + B + D A + DC A = = DA(C + C ) + B + D A =

Prop. Distributiva Ley de Absorcin Prop. Distributiva

C + C = 1 , Prop. Distributiva

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

= D( A + A) + B = = D+B

EJERCICIO 9

A+ A =1

Se conoce la tabla de verdad de la funcin F. Obtenga la expresin cannica como suma de productos. BA 00 01 10 11 Expresin como suma de productos: F 0 1 0 1

F = B A + BA

EJERCICIO 10 Simplifique la funcin lgica y compruebe que el valor de la expresin, simplificada y sin simplificar, coincide para todas las combinaciones de valores de las variables de entrada.

G = (CB + A)( B + CA)

Solucin:

G = (CB + A)( B + CA) = = CB A ( B + CA) = = (C + B) A ( B + CA) = = (C A + B A) ( B + CA) = =C B A

Teorema de De Morgan Teorema de De Morgan Propiedad Distributiva Propiedad Distributiva y C C = 0

Finalmente: G = (CB + A)( B + CA) = C B A Tabla de verdad para el primer trmino de la igualdad se desarrolla como sigue:

CBA

000 001 010 011 100 101 110 111

CB

0 0 0 0 0 0 1 1

CB + A

0 1 0 1 0 1 1 1

CB + A

1 0 1 0 1 0 0 0

CA

0 0 0 0 0 1 0 1

B + CA

0 0 1 1 0 1 1 1

Primer trmino 0 0 1 0 0 0 0 0

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital Tabla de verdad para el segundo trmino de la igualdad se desarrolla como sigue: Segundo CBA C A trmino 000 1 1 0 001 1 0 0 010 1 1 1 011 1 0 0 100 0 1 0 101 0 0 0 110 0 1 0 111 0 0 0 Se puede observar que los valores de los dos trminos de la igualdad coinciden para todas las combinaciones de valores de variables de entrada. EJERCICIO 11 Simplifique las siguientes expresiones booleanas expresadas como sumas de productos utilizando las Leyes del lgebra de Boole.

(0,1,2) b) H = (0,2,4,6,7)

a) H =

2 3

Solucin: a)

H = (0,1,2) = B A + B A + B A = B ( A + A) + B A = B + B A = B + A 123 2

1

b) H =

(0,2,4,6,7) = C B A + CB A + C B A + CB A + CBA =

3 1

Prop. Distributiva Prop. Distributiva Ley:

= (C + C ) B A + (C + C ) B A + CBA = B A + B A + CBA = 1 4 2 4 3 1 4 2 4 3

1

= ( B + B) A + CBA =

A + AB = A + B = A + CB

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 12 Obtenga a partir de la tabla de verdad de la funcin F, su expresin en forma cannica algebraica y numrica, como suma de productos.

CBA

000 001 010 011 100 101 110 111

F

1 0 1 1 0 1 0 0

m 0 1 2 3 4 5 6 7

FORMA ALGEBRAICA Suma de productos: F = C B A + C B A + C BA + C B A FORMA NUMRICA Suma de productos: F =

(0,2,3,5)

3

EJERCICIO 13 Sintetice las siguientes funciones lgicas. a) F = (C BD + A) BA + DBC b) F = ( A ( B + C )) D + B (C + A + D )

Solucin: a) F = (C BD + A) BA + DBC

A B

C D

F

b) F = ( A ( B + C )) D + B (C + A + D )

A B

C D

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 14 Realice los clculos necesarios y rellene la tabla de verdad que se acompaa. La funcin f se describe en el circuito de la figura. Nota: LSB= bit menos significativo. MSB= bit ms significativo. Nota: LSB = Least Significant Bit. MSB = Most Significant Bit, Bit de menos peso y de ms peso respectivamente. Los nmeros 0, 1, 2, etc. indican el peso de cada una de las salidas del decodificador u multiplexor.

a 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

b 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

c 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

d 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Solucin: En general, existen dos mtodos de resolucin de este tipo de ejercicios de anlisis de circuitos: El primero consiste en asignar valores a las entradas hasta completar todas las filas de la tabla de verdad. El valor de las salidas del circuito se calcula propagando las el valor de las entradas de izquierda a derecha hasta alcanzar las salidas, calculando todos los valores intermedios que sean necesarios. Este mtodo es general y se puede utilizar para analizar cualquier circuito combinacional. Sin embargo, resulta tedioso. El segundo mtodo consiste en observar cuidadosamente el circuito para encontrar alguna propiedad de alguno de sus bloques que nos permita analizarlo ms fcilmente, dividindolo en partes ms sencillas. Dependiendo de los componentes que forman el circuito, su complejidad y de cmo se conectan entre s, ser ms ventajoso aplicar un mtodo u otro. Analizaremos a continuacin algunos casos de la tabla de verdad para el circuito propuesto aplicando el primer mtodo. Para ello se utilizar la siguiente figura, en la que aparecen representadas las seales intermedias del circuito (salidas del decodificador D0, D1, D2, D3 y entradas al multiplexor M0, M1, M2, M3).

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

Decodificador 0 d LSB c MSB 1 2 3 D1 D2 D3 D0 M0 M1 M2 M3 Multiplexor 0 1 2 3

MSB LSB

Si se considera que las entradas abcd=0000, al ser ab=00 la salida f coincidir con el valor presente en la entrada 0 del multiplexor (seal M0). Por otra parte, al ser cd=00, se activar la salida 0 del decodificador que tomar el valor 0, siendo el resto de salidas del decodificador 1, por lo que la salida f valdr 0. Si las entradas toman el valor 0001, al ser cd=01 se activar la salida 1 del decodificador, por lo que la seal D1 valdr 0 y D0, D2 y D3 tomarn el valor lgico 1. La salida f tomar el valor presente en la entrada M0 al ser ab=00, es decir valdr 1. Siguiendo un razonamiento semejante para todos los casos posibles que se pueden presentar en las entradas, se calcularan las seales intermedias que fueran necesarias para cada caso y se obtendran a partir de ellas el valor que tomara la salida f. A continuacin analizaremos este circuito mediante el segundo mtodo. Si se consideran nicamente las variables a y b (entradas de seleccin del multiplexor), podemos dividir la tabla de verdad en cuatro partes (ab=00, 01, ). Examinaremos cada caso por separado: Si a = 0 y b = 0 la salida f tomar el valor de la entrada 0 del multiplexor (f = M0). Esta entrada est conectada directamente a la salida de menor peso (0) del decodificador (M0 = D0). Por definicin, en un decodificador nicamente puede encontrarse activa una de las salidas en cada instante. Por lo que para este circuito, al ser las salidas activas a nivel bajo, la salida 0 del decodificador valdr 0 cuando C = 0 y D = 0, y 1 en el resto de casos. Este resultado nos permite calcular los primeros 4 valores de la salida. Tal como se muestra en la siguiente tabla de verdad: a 0 0 0 0 b 0 0 0 0 c 0 0 1 1 d 0 1 0 1 f 0 1 1 1

Si a = 1 y b = 1 la salida f del multiplexor toma el valor de su entrada 3 de dato (f = M3), la cual est conectada directamente a la salida 3 del decodificador (M3 = D3). Aplicando un razonamiento similar al seguido cuando se analiz el caso a = 0 y b = 0, se obtiene el valor que toma la salida f para las cuatro ltimas filas de la tabla de verdad. La salida 3 del decodificador

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital tomar el valor 0 nicamente cuando c = 1 y d = 1, siendo 1 en el resto de los casos. Es decir la tabla de verdad, cuando ab =11, es: a 1 1 1 1 b 1 1 1 1 c 0 0 1 1 d 0 1 0 1 f 1 1 1 0

El resto de casos para a y b, se analizan de forma similar pero teniendo en cuenta que las entradas al multiplexor no se encuentran conectadas de forma directa a las salidas del decodificador. Para el caso a = 0 y b = 1, la salida f toma el valor de la entrada 1 del multiplexor (seal M1, f = M1), el cual se puede calcular a partir de la siguiente figura, en la que se han representado las seales intermedias (D0, D1, D2, D3, M1, M2) del circuito.

Decodificador 0 d LSB c MSB 1 2 3 D1 D2 D3 D0 M1 M2 Multiplexor 0 1 2 3

MSB LSB

La seal M1 (entrada 1 del multiplexor) valdr 1 cuando D0 y D1 (salidas 0 y 1 del decodificador respectivamente) valgan 0 a la vez. Sin embargo, esto es imposible, ya que en cada instante nicamente una de las salidas del decodificador puede estar activada y valer 0. Por ello, M1 siempre tomar el valor 0, independientemente del valor que tomen a y b. Es decir la tabla de verdad, cuando ab = 01, es a siguiente: a 0 0 0 0 b 1 1 1 1 c 0 0 1 1 d 0 1 0 1 f 0 0 0 0

Para el caso a = 1 y b = 0, la salida f toma el valor de la entrada 2 del multiplexor (seal M2, f = M2). M2 valdr 1 (puerta NAND) cuando D1 D2 valgan 0, es decir para los casos cd = 00 y cd =10, y cero en el resto.

10

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital a 1 1 1 1 b 0 0 0 0 c 0 0 1 1 d 0 1 0 1 f 0 1 1 0

La tabla de verdad completa es la siguiente: a b c d f 0 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 0 1 0 0 0 0 1 0 0 1 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 EJERCICIO 15 En una memoria EPROM 1Kx8, debido a un error durante el proceso de fabricacin, la patilla correspondiente al bit ms significativo del bus de direcciones se encuentra conectada permanentemente a 0. Ponga una V sobre la lnea en las respuestas verdaderas y una F en las falsas. La memoria con el error... En la memoria con el error...

_ Pasa a denominarse EEPROM. _ Es no voltil _ Es de acceso aleatorio _ No se puede conectar con otras

memorias por el bus de datos.

_ Se reduce a la mitad el nmero de bits

utilizables

_ Se reduce a la mitad el ancho de cada

palabra utilizable

_ El bus de direcciones es bidireccional. _ Solo se puede acceder a las

posiciones pares.

_ El bus de datos es bidireccional. _ No puede utilizarse en ningn caso _ Para borrarla basta con no alimentarla.

_ Solo se puede acceder a las

posiciones con direccin menor que 512

_ Solo es necesario conectar 7 lneas

del bus de datos.

_ Su capacidad, medida en nmero de

palabras, se reduce a la mitad

11

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital Solucin: Se han marcado en negrita las respuestas verdaderas La memoria con el error... En la memoria con el error...

_ Pasa a denominarse EEPROM. _ Es no voltil _ Es de acceso aleatorio _ No se puede conectar con otras

memorias por el bus de datos.

_ Se reduce a la mitad el nmero de

bits utilizables

_ Se reduce a la mitad el ancho de cada

palabra utilizable

_ El bus de direcciones es bidireccional. _ Solo se puede acceder a las

posiciones pares.

_ El bus de datos es bidireccional. _ No puede utilizarse en ningn caso _ Para borrarla basta con no alimentarla.

_ Solo se puede acceder a las

posiciones con direccin menor que 512

_ Solo es necesario conectar 7 lneas

del bus de datos.

_ Su capacidad, medida en nmero

de palabras, se reduce a la mitad EJERCICIO 16 En el sistema lgico de la figura todos los circuitos son multiplexores cuatro a uno donde C y A son las entradas de seleccin menos significativas. Se pide: Obtener la tabla de verdad de la funcin de salida F (A,B,C,D). Realizar la misma funcin lgica con una PLA de cuatro entradas. Indique los fusibles que permanecen tras el proceso de programacin.

12

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital Solucin:

M0

M1 M4

M2

M3

La salida F toma el valor presente en la entrada de dato que se seleccione en el multiplexor M4 mediante las entradas A B del circuito. Las entradas al multiplexor M4 son las salidas de los multiplexores M0, M1, M2 y M3. Hay que tener en cuenta que A es la entrada de seleccin de menor peso del multiplexor M4, por lo que cuando en la tabla de verdad AB = 01, se seleccionar el dato presente en la entrada 10 del multiplexor M4 y cuando AB = 10 se seleccionar el dato presente en la entrada 01 del multiplexor M4. Por otra parte, el valor en la salida de los multiplexores M0 a M3 depende del valor de las entradas CD que actan como entradas de seleccin para estos multiplexores. Segn lo anterior, y teniendo en cuenta que las entradas de seleccin menos significativas son A y C, se puede calcular la tabla de verdad del circuito directamente. En la siguiente tabla de verdad se han incluido, adems de las entradas y la salida del circuito (columnas A, B, C, D, F), el multiplexor que proporciona el dato a la salida F, segn los valores de A y B (columna MUX), y una breve explicacin sobre como se obtiene el valor de salida de ese multiplexor (Valor seleccionado).

13

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

A B C D F 0 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 0 0 1 1 0 1 0 1 1 1 0 1 0 0 0 1 1 0 0 1 1 1 0 1 0 0 1 0 1 1 1 1 1 0 0 0 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1

MUX MO (AB=00) (BA=00)

M2 (AB=01) (BA=10)

M1 (AB=10) (BA=01)

M3 (AB=11) (BA=11)

Valor seleccionado Entrada de dato 00 de M0 Entrada de dato 10 de M0 (C es la entrada de seleccin de menor peso de M0) Entrada de dato 01 de M0 (C es la entrada de seleccin de menor peso de M0) Entrada de dato 11 de M0 Entrada de dato 00 de M2 Entrada de dato 10 de M2 (C es la entrada de seleccin de menor peso de M2) Entrada 01 de M2 (C es la entrada de seleccin de menor peso de M1) Entrada de dato 11 de M2 Entrada de dato 00 de M1 Entrada de dato 10 de M1 (C es la entrada de seleccin de menor peso de M1) Entrada de dato 01 de M1 (C es la entrada de seleccin de menor peso de M1) Entrada de dato 11 de M1 Entrada de dato 00 de M3 Entrada de dato 10 de M3 (C es la entrada de seleccin de menor peso de M3) Entrada de dato 01 de M3 (C es la entrada de seleccin de menor peso de M3) Entrada de dato 11 de M3

El esquema de la PLA con los fusibles que permanecen tras la grabacin es el de la siguiente figura:

1 2 4 6 9 11 14 15 8

14

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 17 El circuito de la figura representa las funciones lgicas XY de tres entradas, A, B y C.

Se pide: a) Obtenga la tabla de verdad de las funciones X(A,B.C) e Y(A,B.C). Tome en ambos casos la variable A como la ms significativa. b) Obtenga las ecuaciones en forma de suma de productos sin simplificar para la variable X

Solucin:

X = ( AB) ( A + C ) Y = AB BC

A partir de las ecuaciones anteriores, asignando valores a las variables y calculando el valor de las expresiones, se puede completar la tabla de verdad para X e Y:

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C AB A+C BC 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 1 1 0 1 1 0 1 1 1 1 1 1 0 X 0 1 0 1 1 1 0 0 Y 0 0 0 1 0 0 1 0

La expresin sin simplificar forma de suma de productos se obtiene a partir de las filas en las que X toma el valor 1. Cada una de las filas representa un producto formado por todas las variables de entrada (negadas o sin negar). Si la variable toma el valor 0 aparece negada y si toma el valor 1 aparece sin negar. Cada uno de estos productos en los que aparecen todas las variables de la funcin se denomina minitrmino. La expresin en forma de suma de productos en los que aparecen todas las variables (en forma directa o complementada) se denomina forma

15

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

cannica (producto cannico). Esta suma de productos se puede expresar de forma compacta mediante una expresin con un sumatorio que se denomina forma compacta o numrica. La funcin X est formada por la suma de los minitrminos 1, 3, 4 y 5.

X = ABC + ABC + ABC + ABC =3 (1,3,4,5)

EJERCICIO 18 En el circuito de la figura todos los componentes son ideales. El decodificador trabaja considerando como 1 lgico la tensin de 5 V y como 0 lgico la tensin de 0 V. Dibuje la forma de onda de la tensin en la salida del operacional (Us) cuando la tensin en las entradas A y B varan segn la forma de onda del cronograma de la figura. Indique los puntos ms significativos de la tensin Us. En qu configuracin trabaja el operacional?

Solucin: Existe realimentacin al estar conectada la salida Us al terminal del operacional, por lo que trabaja como amplificador sumador inversor.

16

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

El decodificador trabaja considerando como 1 lgico la tensin de 5V. y como 0 lgico 0V. El funcionamiento del decodificador se puede representar en la siguiente tabla: Entradas A B 0 0 0 1 1 0 1 1 Salidas 01 10 0 0 1 0 0 1 0 0

00 1 0 0 0

11 0 0 0 1

Solamente se encuentra activa una sola salida del decodificador en cada instante, por lo que la salida activa tendr una tensin de 5V. y el resto 0V. Analicemos el caso A = 0 B = 0:

Us =

R1 5V = 5V R1

Como solamente se encuentra activa una entrada, el resto de casos se resuelve de la misma forma. Pero considerando el valor correspondiente para la resistencia conectada al terminal inversor (-) del operacional (R1, 2R1, 4R1, 8R1). Por lo tanto: A 0 0 1 1 B 0 1 0 1 R (-) R1 2R1 4R1 8R1 Us

R1 5V = 5V R1 R1 Us = 5V = 2,5V 2 R1 R1 Us = 5V = 1,25V 4 R1 R1 Us = 5V = 0,625V 8 R1 Us =

17

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

Con la tabla anterior, dibujar el cronograma es inmediato:

EJERCICIO 19 Disear un sistema formado por tres pulsadores y un LED, de forma que ste se enciende solamente cuando se pulsen dos pulsadores a la vez. a) Con puertas AND, OR y NOT b) NAND c) NOR Solucin: Llamaremos A, B y C a los pulsadores y L al LED. Cuando un pulsador se encuentre pulsado su variable lgica tomar el valor lgico 1 y valdr 0 cuando no se encuentre pulsado. Cuando el LED est encendido L vale 1 y 0 cuando est apagado. Teniendo en cuenta lo anterior, se construye la siguiente tabla de verdad que define el comportamiento del circuito lgico que controla el LED. A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 L 0 0 0 1 0 1 1 0 Pulsadores Ningn pulsador activado Un nico pulsador activado Un nico pulsador activado Dos pulsadore activados Un nico pulsador activado Dos pulsadores activados Dos pulsadore activados Tres pulsadores activados

Las ecuaciones lgicas del circuito en forma de sumas de productos se pueden obtener a partir de la tabla de verdad:

18

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

L = ABC + ABC + ABC = (3,5,6)

3

A partir de la ecuacin anterior se puede dibujar de forma directa, sustituyendo cada operador por la puerta lgica equivalente, el circuito lgico sin simplificar con puertas AND, OR e inversores (NOT) que controla el encendido del LED:

NOT

NOT

inst20

inst22

inst21

NOT

AND3

inst16

AND3 OR3

inst17

AND3

inst19

inst18

Para obtener el circuito equivalente sin simplificar implementado nicamente con puertas NAND, se transformara la ecuacin obtenida anteriormente aplicando las propiedades del lgebra de Boole, o modificado de forma grfica el circuito obtenido anteriormente con puertas AND, OR y NOT.

L = ABC + ABC + ABC =

L = ABC + A BC + ABC = L = ABC ABC ABC

Doble inversin Teoremas de DeMorgan

Un inversor se puede obtener a partir de una puerta NAND cortocircuitando sus dos entradas. Esto se puede demostrar comparando las tablas de verdad de un inversor y la de una puerta NAND de dos entradas con sus dos entradas unidas entre si. C A B

19

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital Para obtener el circuito equivalente implementado nicamente con puertas NOR, Hay que transformar la ecuacin obtenida anteriormente con puertas AND, OR y NOT aplicando las propiedades del lgebra de Boole, o modificar de forma grfica ese circuito obtenido anteriormente.

L = ABC + A BC + ABC

L = ABC + A BC + ABC L = ABC ABC ABC L = ( A + B + C) ( A + B + C) ( A + B + C) L = ( A + B + C) + ( A + B + C) + ( A + B + C)

Doble inversin Teoremas de DeMorgan Teoremas de DeMorgan Teoremas de DeMorgan

En la ltima expresin cada uno de los sumandos parciales se puede representar mediante una puerta NOR de 3 entradas. En la figura se representa como se puede transformar el resto del circuito para dibujarlo nicamente con puertas NOR. Al igual que para el caso de las puertas NAND, un inversor se puede obtener cortocircuitando las entradas de una puerta NOR.

A

NOR2

B

NOR2

C

NOR2

inst9

inst10

inst11

NOR3

NOR3

inst13

inst

NOR3 OR3

NOT

NOT

inst1

NOR3

inst6

inst8

inst12

inst2

NOR2

inst15

Nota: En general, antes de implementar el circuito se utiliza algn mtodo de minimizacin (lgebra de Boole, mapas de Karnaugh, algoritmos implementados en computadora, etc.) para as obtener un circuito ms sencillo, con un menor nmero de componentes. En nuestro caso se podra utilizar el A. de Boole para obtener una expresin ms sencilla, con menos literales (variables) y operadores lgicos, lo que dara lugar a un circuito con menos componentes. En este caso particular, el lector puede comprobar que no es posible simplificar el circuito Nota: Las puertas NAND y NOR son especialmente interesantes, ya que cualquier circuito se puede disear nicamente con puertas NAND o NOR.

20

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 20 Un sistema de alarma tiene 4 detectores A, B, C y D situados en distintas zonas de un edificio. La alarma se encender cuando se activen 3 4 detectores. La alarma nunca se disparar si se activan uno o dos detectores, tampoco se disparar si A = 0 y B = C = D = 1. Por razones de seguridad la alarma se encender si B = C = D = 0 y A = 1. Suponga que cuando el detector se activa proporciona un 1 lgico a su salida y que cuando se activa la alarma se indica mediante un 1. Implemente el circuito de activacin de la alarma con puertas, AND, OR y NOT. Solucin: A partir de los datos del enunciado se puede obtener la tabla de verdad para la activacin de la alarma (F): A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Y la ecuacin lgica del circuito: B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 F 0 0 0 0 0 0 0 0 1 0 0 1 0 1 1 1

F = ABC D + ABCD + ABC D + ABC D + ABCD

El esquema del circuito sin simplificar con puertas AND, OR y NOT es el siguiente:

A B C D

21

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 21 Dada la funcin lgica f(A,B,C,D) = (0,1,3,5,7,9,11,12) (Vale 1 para la entradas 0,1,3 y 0 en el resto de casos). Obtenga la expresin de puertas utilizando nicamente puertas NAND. No es necesario que dibuje el esquema de puertas, solo las ecuaciones. Solucin:

f = ABC D + ABC D + ABCD + ABC D + ABCD + ABC D + ABCD + ABC D f = ABC D + ABC D + ABCD + ABC D + ABCD + ABC D + ABCD + ABC D

f = ABC D ABC D ABCD ABC D + ABCD ABC D ABCD ABC D

Doble inversin Teorema de DeMorgan

EJERCICIO 22 Dada la PAL de la figura, en la que se han implementado las funciones lgicas F y G, se pide: a) Obtenga las expresiones algebraicas cannicas en forma de suma de productos de las funciones F y G de la Figura 1 b) Suponga ahora que A= 0. Implemente las funciones F y G mediante un multiplexor de tres entradas de seleccin (segn se muestra en la Figura 2, de forma que si la entrada de seleccin S2 es 0 se obtiene en la salida Y del multiplexor la funcin F y si S2 es 1 se obtiene G.

A B C D

D0 D1 D2 D3 D4 D5 D6 D7 Y=F Y=G

FG

MUX

S2 S1 S0

0 1 C D

Figura 2

Figura 1

22

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

Solucin: Las expresiones algebraicas de F y G se obtienen observando los contactos existentes en el plano AND y en el plano OR.

F = ABC + ABCD + CD G = AD + BC + AD

Si suponemos que A=0, las expresiones anteriores se simplifican, al eliminarse todos los productos lgicos en los que aparezca la variable A:

F = BCD + CD = CD (1+B) = CD G = BC +D

Por la definicin de funcionamiento de un multiplexor: c) Cuando S2=0 se seleccionarn las entradas de dato D0 a D3 del multiplexor segn los valores de C y D. d) Cuando S2=1 se seleccionarn las entradas de dato D4 a D7 del multiplexor segn los valores de C y D. F se debe obtener cuando S2 = 0. En este caso, se seleccionan las entradas de dato D0 a D3 del multiplexor. Por otra parte, como F = CD, quiere decir que F valdr 1 nicamente cuando C = D = 1. Por lo que se debe seleccionar un 1 cuando CD=11. Por lo tanto, en las entradas de seleccin del multiplexor se deben poner los siguientes valores lgicos (fila Valor dato): Seleccin CD 00 Entrada de dato D0 seleccionada Valor dato 0 01 D1 0 10 D2 0 11 D3 1

Para G, podemos aplicar las propiedades del a. de Boole para obtener una expresin en la que aparezcan las dos variables de seleccin del multiplexor (C y D).

G = BC + D = BC ( D + D) = BCD + BC D

Esta ltima expresin lgica indica que G toma el valor de B cuando C=1, y vale 1 cuando D=1, siendo indiferente el valor de B y C en este ltimo caso. G valdr 0 en el resto de casos.

Seleccin CD 00 (D4) Entrada de dato D4 seleccionada Valor dato 0

01 (D5) D5 1

10 (D6) D6 B

11 (D7) D7 B

23

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

0 0 0 1 0 1 B B

0 1 C D D0 D1 D2 D3 D4 D5 D6 D7

F: S2 = 0

MUX

G: S2 = 1

S2 S1 S0

Y=F Y=G

EJERCICIO 23 El circuito de la figura tiene 4 entradas A, B, C, D y una salida S. Obtenga la tabla de verdad de la salida S(A, B, C, D). Justifique su respuesta.

DECODIFICADOR

S0 S1 C B A E0 E1 E2 S2 S3 S4 S5 S6 S7

0 1

MUX S Sel D

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

24

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital Solucin: Del esquema del circuito se observa que cuando D = 0 la salida S = 0 (al ser D la entrada a una puerta AND), esta propiedad del circuito permite obtener directamente la mitad de la tabla para S. Por el mismo motivo, la salida S ser 0 cuando la salida del multiplexor (MUX) sea 0. Para analizar este caso se van a considerar las seales intermedias X, Y, Z, T. Del funcionamiento del multiplexor se deduce que cuando Z = 0 T = X y cuando Z = 1 T = Y, las cuales se representan en la siguiente figura:

DECODIFICADOR

S0 S1 C B A E0 E1 E2 S2 S3 S4 S5 S6 S7

X Y

0 1

MUX

T

S

Sel D

Z ser 0 cuando S6 = S7 = 1 (puerta NAND). Esta condicin es imposible, ya que deberan estar activadas al mismo tiempo las dos salidas del decodificador, por lo que Z es 1 siempre. Esto implica que T = Y, ya que X no se seleccionar nunca. Por otra parte, Y = 1 cuando S2 S3 (puerta XOR). Esta condicin se cumple cuando est seleccionada una de las dos salidas (S2 S3) del decodificador y el resto de las salidas del decodificador valen 0. Esta condicin se cumple cuando ABC = 010 ABC = 011. Por lo que se cumple que S1 = 1 cuando se da alguna de las siguientes condiciones (marcadas en rojo en la tabla de verdad): ABC = 010 y D = 1 ABC = 011 y D = 1

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 S 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 0

25

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 24 Dado el circuito de la figura, cuyas entradas son A, B, C, D y sus salidas S1 y S2. Obtenga la tabla de verdad que define el valor de las salidas en funcin de las entradas. Ordene las columnas de la tabla de verdad de la forma A B C D S1 S2.

C

Decodificador

A0 A B E1 E0 A1

0 MUX 1

S1

A2 A3

0 1

MUX S2

Solucin: S1 es 1 cuando alguna de las entradas a la puerta OR es 1. Es decir, cuando el multiplexor selecciona la entrada salida activa del multiplexor. Esto se produce para las siguientes combinaciones de las entradas: C=0 C=1 D=0 D=1 y AB = 00 y AB = 01 y AB = 10 y AB = 11

Para el resto de combinaciones de las entradas S1 es 0. S2 es 1 cuando D = 1 y S1 = 1 a la vez (puerta AND). En el resto de casos valdr 0. Teniendo en cuenta lo anterior se puede completar la tabla de verdad: A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 S1 1 1 0 0 0 0 1 1 1 0 1 0 0 1 0 1 S2 0 1 0 0 0 0 0 1 0 0 0 0 0 1 0 1

26

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 25 Para el circuito de la figura, cuyas entradas son A, B, C y D y sus salidas X, Y, Z. Complete la tabla de verdad para las entradas y salidas del circuito.

C D D0 C D 1 C D D1 D2 D3 S1 A S0 E B S1 Z X A

MUX

X

DECOD

S0

A 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Solucin:

B 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

C 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1

D 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Para obtener el valor de X, hay que dar valores a A y B y calcular el valor correspondiente de la entrada de dato (D0 a D3) al multiplexor, el cual depende de C y D. Por ejemplo, cuando AB = 00, X = C+D (X valdr 1 cuando alguna de ellas sea 1). Cuando AB = 10 X = 1 siempre, etc. Y vale 1 cuando A = 1 cuando S0 = 1 (puerta OR). Esta ltima condicin equivale a que X = 0 (entrada al decodificado). Por lo que cuando X = 0 Y vale 1. Observando el circuito se deduce que Z =1 cuando X = 1 (se activa S1) y A = 1

27

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital (ambas condiciones a la vez, al ser una puerta AND) Considerando las condiciones anteriores, se puede completar la tabla de verdad par X, Y, Z: A B C D X Y Z 0 0 0 0 0 1 0 0 0 0 1 1 0 0 0 0 1 0 1 0 0 0 0 1 1 1 0 0 0 1 0 0 1 0 0 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 1 1 0 1 0 1 0 0 0 1 1 1 1 0 0 1 1 1 1 1 0 1 0 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 1 0 1 1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0 1 0 EJERCICIO 26 Dados los nmeros X= AC16 y 8910. Se pide: Represente X en decimal, binario, octal y complemento a dos. Represente Y en signo magnitud, complemento a 1 y complemento a 2, con el mnimo nmero de bits necesario en los tres casos. Solucin:

Para convertir a binario, se aplican divisiones sucesivas por 2:

X2 = 10101100 Como comprobacin, se va a convertir el nmero binario obtenido a hexadecimal. Para convertir a hexadecimal, se agrupa en grupos de 4 bits de derecha a izquierda, aadiendo a la izquierda los ceros que sean necesarios.

28

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital X2 = 1010 1100 = AC16 = ACH Por lo que la conversin a binario es correcta. Tambin se podra haber convertido A antes a binario directamente desde hexadecimal. Para ello, hay que sustituir cada dgito hexadecimal por su equivalente binario de 4 bits (16 = 24), segn la siguiente tabla de equivalencias entre decimal, binario y hexadecimal. Decimal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Binario 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 Hexadecimal 0 1 2 3 4 5 6 7 8 9 A B C D E F

Para convertir a octal se agrupa en grupos de tres bits de derecha a izquierda (8 = 23), aadiendo a la izquierda los ceros que sean necesarios.

Como X es un nmero positivo, para expresarlo en complemento a dos (C2) hay que aadir un 0 a la izquierda a su expresin binaria, ya que en el convenio de C2 el bit ms significativo representa una magnitud dada por su peso y un signo. Cuando es 1 el signo es negativo y cuando es 0 el nmero es positivo. X2 = 101011002 = 010101100C2

29

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 27 Suponga la misma entrada de datos D y la misma seal de reloj CLK para dos biestables D. Considere el primero activo por flanco de subida (salida Q1) y el segundo por flanco de bajada (salida Q2). Represente las seales de salida de cada uno de los biestables.

CLK D Q1 Q2

EJERCICIO 28

Complete el cronograma para el circuito de la figura. Suponga que inicialmente el estado del biestable es 0. La seal D se corresponde con la entrada del biestable.

Solucin: La entrada del biestable D sigue la expresin:

D = AB + AC

30

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital La salida del biestable, Q (que coincide con la salida del circuito, C) se actualiza en los flancos ascendentes de reloj, tomando el valor de D.

EJERCICIO 29 Complete el cronograma para el circuito de la figura. Suponga que inicialmente el estado del biestable es 0. La seal D se corresponde con la entrada del biestable.

Solucin: La seal D de entrada al biestable, se corresponde con la expresin:

D = AQ + BQ

donde Q se corresponde con la salida del biestable en el estado actual. Por otra parte, Q actualiza la salida del circuito en los flancos ascendentes de reloj, tomando el valor de D.

31

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 30 Complete el cronograma para el circuito de la figura. Suponga que inicialmente el estado del biestable es 0. Las seales Q1 y Q2 se corresponden con las salidas del primer y segundo biestable, respectivamente.

Solucin: Los biestables D actualizan sus salidas (Q1 y Q2) en los flancos ascendentes de reloj. La seal OUT, se corresponde con la expresin:

OUT = Q1 Q 2

EJERCICIO 31 Disee una memoria de 2kx4 con integrados de 1kx4. Solucin: Se dispone de integrados de 1k de capacidad, que se direccionan con:

210 = 1024 10 lineas de direcciones

Estas lneas de direcciones se numeran de la ms significativa a la menos significativa como: A9, A8, A7, etc. hasta la A0. Como se pretende direccionar una memoria de 2k palabras de capacidad, se necesitan:

32

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

2 210 = 211 11 lineas de direcciones

Es decir, se necesitan 2 memorias de capacidad 210 (1k) y adems es preciso aadir una nueva lnea de direccin, que llamamos A10. Esta nueva lnea de direccin, A10, se puede utilizar para distinguir cual de las dos memorias de 1k se esta direccionando. - Cuando A10 = 0 /CS1 = 0, se selecciona la memoria N1 y no se selecciona la N2 (/CS2=1). - Cuando A10 = 1 /CS2 = 0, se selecciona la memoria N2 y no se selecciona la N1 (/CS1=1). La implementacin descrita anteriormente se realiza con una puerta NOT conectada como se muestra en la figura de forma que, en cada momento, nicamente puede estar seleccionado uno de los chips de 1k. Las lneas de datos, denominadas en el ejemplo como I04:IO1, se unen una a una a la salida de ambos chips.

EJERCICIO 32 Se desea disear una memoria de 4kx4 y se dispone de memorias de 1kx4. Solucin: Se dispone de integrados de 1k de capacidad, que se direccionan con:

210 = 1024 10 lineas de direcciones

Estas lneas de direcciones se numeran de la ms significativa a la menos significativa como: A9, A8, A7, etc. hasta la A0. Como se pretende direccionar una memoria de 4k palabras de capacidad, se necesitan:

4 210 = 2 2 210 = 212 12 lineas de direcciones

Es decir, se necesitan 4 memorias de capacidad 210 (1k) y adems es preciso aadir dos lneas

33

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital nuevas de direcciones, (respecto de las 10 lneas para integrados de 1k), que llamamos A11 y A10. Estas dos lneas nuevas de direccin, se pueden utilizar para distinguir cual de las 4 memorias de 1k se esta direccionando. Una forma sencilla de hacerlo es utilizar un decodificador. El decodificador permite seleccionar cada uno de los integrados, de forma que nicamente uno de ellos este activo en cada instante. En este caso se utiliza un decodificador 2 a 4, con salidas activas a nivel bajo. Las entradas del decodificador se conectan a las lneas A11 y A10 y sus salidas decodificadas a las entradas de seleccin de cada chip de memoria RAM. De este modo: A11 0 0 1 1 A10 0 1 0 1 RAM seleccionada Chip 0 Chip 1 Chip 2 Chip 3

Las lneas de datos, denominadas en el ejemplo como D3:D0, se unen una a una a la salida de los 4 chips.

EJERCICIO 33 Se quiere disear del mapa de memoria de una nueva consola porttil de videojuegos que 34

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital ser lanzar al mercado en breve. Este dispositivo se caracteriza por trabajar con palabras de 32 bits y utilizar 21 lneas de direcciones. La distribucin de la memoria es como sigue: En la parte baja de la misma (posicin 0) se ubican 128K de ROM. A continuacin se sitan 256 K de memoria no voltil pero reprogramable para poder realizar actualizaciones del sistema. A continuacin se dispone de 256 K libres para ser utilizados en otros modelos que se lanzarn al mercado posteriormente. Tras este hueco se desea ubicar 1 M de memoria DRAM. En la parte superior del espacio de memoria se colocan 128 K de SRAM, para la memoria grfica del sistema. Entre esta zona (SRAM) y la inmediata inferior (DRAM) de deja un hueco para conectar perifricos al sistema y tarjetas especiales de ampliacin. Para la construccin del circuito se dispone de un nmero suficiente de los siguientes circuitos: o ROM de 128Kx16 o DRAM de 512Kx16 o SRAM de 64Kx32 o FLASH de 256Kx32 1. Cuntos circuitos integrados se necesitan de cada tipo para completar el esquema de memoria?

Para completar el esquema de memoria se necesitan: - 2 memorias ROM de 128kx16 para extender la longitud de palabra hasta 32 bits - 1 memoria FLASH de 256kx32 - 4 memorias DRAM de 512kx16 para extender la longitud de palabra hasta 32 bits y completar 1M de DRAM - 2 memorias SRAM de 64kx32 para completar 128k de SRAM

2. Disee el mapa de memoria del sistema indicando en hexadecimal las direcciones de comienzo y final de cada uno de los circuitos integrados de memoria.

Direccin hexadecimal

SRAM2 64kx32 SRAM1 64kx32 Libre 256k DRAM3 512kx16 DRAM1 512kx16 DRAM4 512kx16 DRAM2 512kx16 Libre 256k FLASH 256kx32 ROM1 ROM2 128kx16 128kx16 Final: 1 F F F F F Inicio: 1 F 0 0 0 0 Final: 1 E F F F F Inicio: 1 E 0 0 0 0 Final: 1 D F F F F Inicio: 1 A 0 0 0 0 Final: 1 9 F F F F Inicio: 1 2 0 0 0 0 Final: 1 1 F F F F Inicio: 0 A 0 0 0 0 Final: 0 9 F F F F Inicio: 0 6 0 0 0 0 Final: 0 5 F F F F Inicio: 0 2 0 0 0 0 Final: 0 1 F F F F Inicio: 0 0 0 0 0 0

35

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital 3. Disee un sistema de decodificacin para los distintos circuitos que componen la memoria. Una posible implementacin para direccionar los distintos circuitos de memoria, es el empleo de un decodificador. Un decodificador diseado adecuadamente permite seleccionar directamente, a travs de una de sus salidas, las memorias de menor tamao y, mediante lgica adicional, las memorias de tamao superior.

O0 O1 O2 O31 O5 O6 O31 O9 O10 O31 DEC O 5:32 31 O17 O18 O31 O31 O25 O26 O31 O29 O30 O31

CS ROM1 Y ROM2

. . . . . . . . . . . . . . . . . . . . . . . .

CS FLASH

Hueco perifricos

A20 A19 A18 A17 A16

I4 I3 I2 I1 I0

CS DRAM1 Y DRAM2

CS DRAM3 Y DRAM4

256k libres

CS SRAM1 CS SRAM2

Figura 1 El mapa de memoria posee 21 lneas de direccin, numeradas como A20: A0. Con 21 lneas de direccin se pueden direccionar hasta 2 21 posiciones de memoria, es decir, 2M = 2048k. El tamao total de la memoria se puede repartir teniendo en cuenta el tamao menor de los chips, en este caso de las memorias SRAM de 64k.

2Mb 2048k = = 32 64k 64k

De esta manera se pueden direccionar hasta 32 tramos de 64k cada uno, si se emplea un decodificador 5:32 como se muestra en la Figura 1. Las entradas del decodificador se corresponden con las 5 lneas de mayor peso del bus de direcciones: A20, A19, A18, A17 y A16. La salida O31, por ejemplo, se conecta directamente a la entrada de seleccin de chip ( CS ), de la memoria SRAM2. Las salidas O0 y O1 generarn la seal de seleccin de los chips ROM1 y ROM2 conjuntamente (mediante una puerta AND), ya que el circuito integrado ROM1 contiene los 16 bits de mayor peso de la palabra (parta alta) y ROM2 los 16 bits de menor peso de la misma (parte baja). El procedimiento es anlogo con el resto de salidas de decodificador. Por otro lado, es preciso dejar los dos huecos especificados en el enunciado para ampliaciones posteriores. 4. Dibuje el circuito completo indicando de forma clara todas las conexiones. Las lneas del bus de direcciones, mediante las cuales se accede a cada tipo de memoria, se calculan segn las posiciones de memoria que se quieran direccionar. Por ejemplo, para las memorias ROM de 128k de necesitan 17 lneas de direccin:

36

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

128k = 2 7 210 = 217

Para las memorias ROM las lneas del bus de direcciones seran las numeradas como A16: A0. El nmero de lneas de datos que parten de cada memoria depende de si la longitud de la palabra del circuito integrado de memoria es de 16 de 32 bits. En el caso de ser de 16 bits, la numeracin puede ser D31: D16 D15: D0, dependiendo de si es la parte alta o baja de la palabra, respectivamente. Si la longitud de la palabra del chip es de 32, las lneas de datos se numeran como D31: D0.

A20:A0 21 A16:A0 17

O0 O1 O2 O31 O5 O6 O31 O9 O10 O31 DEC O 5:32 31 O17 O18 O31 O31 O25 O26 O31 O29 O30 O31 ROM1 128kx16 A D CS

D31:D0 32 5 D31:D16 16 A16:A0 128kx16

A ROM2

A20:A16

D15:D0 16

17

CS

A17:A0 256kx32

. . . . . . . . . . . . . . . . . . . . . . . .

FLASH

D31:D0 32

18

Hueco perifricos

CS

A20 A19 A18 A17 A16

I4 I3 I2 I1 I0

A18:A0 512kx16

A

DRAM1

D31:D16 16

A18:A0 512kx16

A

DRAM2

D15:D0 16

19

CS

19

CS

A18:A0 512kx16

A

DRAM3

D31:D16 16

A18:A0 512kx16

A

DRAM4

D15:D0 16

19

256k libres

CS

19

CS

A15:A0 16

SRAM1 64kx32 A D CS

D31:D0 32

A15:A0 16

SRAM2 64kx32 A D CS

D31:D0 32

EJERCICIO 34 En la figura se representa una PROM que no ha sido programada (todos sus fusibles estn intactos). Indique los fusibles que permanecern tras el proceso de grabacin,

37

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital si se desea implementar un conversor de cdigo binario a cdigo Gray, cuya tabla de verdad se indica en la figura.

Solucin: En una PROM el usuario programa el plano OR. Como en el plano AND estn implementadas todas las posibles combinaciones de las entradas (B3, B2, B1, B0), en el plano OR se sumarn todas las combinaciones que hacen 1 cada una de las funciones de salida (G3, G2, G1, G0). 38

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital Para que una combinacin se sume a la salida, el fusible que conecta dicha combinacin con la salida, debe permanecer intacto (en la figura aparece marcado con un punto gordo azul). Se observa que, el proceso es tan sencillo como copiar la tabla de verdad sobre la matriz programable OR: - Si en la tabla aparece un 1 para la funcin G0, el fusible permanece - Si en la tabla aparece un 0 para la funcin G0, el fusible se funde y no hay conexin

39

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital EJERCICIO 35 Implemente en la PAL de la figura las siguientes funciones lgicas:

F1 ( A, B, C ) = 4 (0,2,5,6) F2 ( A, B) = 2 (0,7) F3 ( A, B, C , D) = 5 (1,4,31)

Solucin: Cada una de las funciones de salida, F1, F2 y F3, viene expresada como suma de productos. En una PAL el usuario puede programar el plano AND. La funcin F1 es una funcin de 4 variables de entrada (A, B, C y D), por lo que se puede implementar con esta PAL de 4 entradas. De la misma manera ocurre con la funcin F2, que es nicamente de dos variables (A y B). Sin embargo, la funcin F3, que es de 5 variables no se puede implementar, en principio con esta PAL por tener ms variables que entradas tiene la PAL que son 4. Slo podra hacerse en el caso de poder simplificar la funcin e intentar eliminar alguna variable. En este caso no es posible. En la figura se muestran los fusibles que se funden en el plano AND para implementar las funciones F1 (azul) y F2 (rojo). F3 tiene ms variables (5) que entradas hay en la PAL (4), por lo que para implementar dicha funcin en la PAL de la figura hay que simplificar la funcin para intentar eliminar alguna variable. En este caso no se puede implementar F3, ya que no se puede simplificar ms la expresin, lo que se puede comprobar empleando el lgebra de Boole o cualquier otro mtodo de simplificacin.

40

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

EJERCICIO 36 Indique en la PLA de la figura, los fusibles que permanecern tras el proceso de grabacin, si se desea implementar las siguientes funciones.

F1 = (0,2,3,7,15)

4

F 2 = abc + abd + ad + bc

41

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital Solucin: En una PLA el usuario puede programar, tanto el plano AND como el plano OR. Ambas funciones F1 y F2, de 4 y 3 variables, respectivamente, se pueden implementar con esta PLA de 4 entradas. En la figura se muestra la implementacin final marcando con puntos gordos los fusibles que permanecen en ambos planos y por tanto sirven de conexin entre entradas y salidas.

F1(a, b, c, d ) = (0,2,3,7,15)

4

F 2 = abc + abd + ad + bc

0 2 3 7 15

EJERCICIO 37 Para el dispositivo programable de la figura se pide: a. Qu tipo de dispositivo programable es? Justifique su respuesta. Indique qu tipos de dispositivos lgicos programables conoce, comentando sus principales caractersticas. b. Implemente las siguientes funciones lgicas, marcando mediante un crculo todos los fusibles que permanecen tras el proceso de grabacin.

42

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital

F1 = ABC + ABC F 2 =BC + AC F 3 =AB + AB F 4 = A F1 + C F1

Solucin: a) Se trata de una PAL, ya que el plano OR es fijo. Existen varios tipos de dispositivos programables segn el plano que programe el usuario.

Tipo PROM PAL GAL PLA

Plano Programable AND OR X X X X X

b) La implementacin de las funciones se muestra en la figura. Se observa que la funcin F4 depende de la funcin F1 por lo que para su implementacin ser preciso conectar F1 en una de las entradas de la PAL.

43

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital PREGUNTAS DE TEST 1) En una memoria RAM dinmica de 2Kx8 a) Podemos almacenar como mximo 2000 palabras de un byte b) La memoria tiene 12 lneas de direccin y 8 de datos c) Cada bit se almacena en un condensador d) La memoria es de solo lectura 2) Debido a un error durante el proceso de fabricacin, en una Memoria RAM de 1Kx8 la patilla correspondiente a la direccin de mayor peso A9 no tiene conexin con el interior del chip. Adems, debido a este error, internamente A9 se encuentra permanentemente conectada al valor 0 lgico. Entonces: a) La memoria no puede utilizarse en ningn caso b) Si se puede utilizar, pero solo se pueden direccionar las posiciones pares c) Si se puede utilizar, pero solo se pueden direccionar las posiciones impares d) Si se puede utilizar, pero la capacidad de la memoria ha disminuido a 4K bits 3) En una Memoria EPROM de 2KB a) Los datos almacenados se borran si se desconecta la alimentacin b) Los datos se pueden borrar elctricamente c) Los datos los graba el fabricante del circuito d) Los datos los graba el usuario y los borra mediante luz ultravioleta 4) Una GAL a) Es totalmente idntica a una PAL b) Tiene dos planos AND programables y biestables c) Tiene un plano AND programable y un plano OR fijo d) Tiene un plano AND fijo y un plano OR programable 5) Se desea construir un circuito de memoria de 2Kx16 lo ms sencillo posible a partir de memorias de 1Kx16. Entonces a) Se necesitan nicamente 2 memorias 1Kx16 b) Se necesitan 2 memorias 1Kx16 y un multiplexor c) Se necesitan 2 memorias 1Kx16 y un inversor d) Es imposible construir esa memoria con los integrados 1Kx16 6) Se quiere construir un circuito de memoria de 2Kx8 con el mnimo nmero de componentes mediante chips de 1Kx4. Se necesitan: a) Un decodificador y 4 memorias 1Kx4 b) Un decodificador y 2 memorias 1Kx4 c) Un inversor y 4 memorias 1Kx4 d) Un multiplexor y 4 memorias 1Kx4 7) Una SRAM 1Mx8 a) Se debe refrescar para que no se borren los datos almacenados en ella b) Es no voltil c) La informacin se almacena mediante pulsos elctricos d) Puede almacenar 1M bit de informacin 8) Si una memoria RAM de 32Kx4 se ha construido mediante un nico chip RAM de 64Kx8, entonces

44

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital a) b) c) d) Es falso ya que es imposible hacerlo Una lnea del bus de datos se ha conectado a GND Una lnea del bus de datos se ha conectado a VCC Una lnea del bus de direcciones se ha conectado a un valor lgico fijo

9) Una PLA a) Tiene dos planos OR y ambos son programables por el usuario b) Tiene dos planos AND y ambos son programables por el usuario c) Tiene un plano AND y un plano OR y el plano OR es fijo d) Ninguna de las anteriores 10) En una memoria de semiconductor 1Kx8 a) Se pueden implementar todas las funciones lgicas b) Se pueden implementar nicamente 8 funciones lgicas de 10 variables c) Se dispone de 8 lneas de direccin d) Ninguna de las anteriores 11) Una FPGA a) Tiene una arquitectura ms sencilla que una PAL b) Tiene una arquitectura ms compleja que una PAL c) Es un tipo de memoria que necesita refresco d) Ninguna de las anteriores 12) Si la primera direccin de una memoria EEPROM de 1Kx16 es la cero, la ltima direccin de la memoria es la a) 102410 b) 100010 c) 3FFH d) 400H 13) Para disear una memoria de 256Kx8 con integrados de 128Kx4, mediante el hardware ms sencillo, se necesitan a) 2 integrados de 128Kx4 y un decodificador b) 4 integrados de 128Kx4 y un multiplexor c) 4 integrados de 128Kx4 y un inversor d) Ninguna de las anteriores 14) En una memoria SRAM de 1Kx16, debido a un fallo, una de las patillas del bus de direcciones se encuentra conectada permanentemente al valor lgico 1. Entonces a) La memoria no puede utilizarse b) La memoria puede utilizarse, aunque su capacidad se ha reducido a la mitad c) La memoria puede utilizarse si la entrada de Chip Select se pone a 0 d) Ninguna de las anteriores

15) En una memoria PROM de 1Kx16 se pueden almacenar a) 1000 bytes b) 1023 bytes c) 2048 bytes 45

Universidad Carlos III de Madrid Departamento de Tecnologa Electrnica

Fundamentos de Ingeniera Electrnica Problemas de Electrnica Digital d) 1Kbyte 16) Indique la opcin en la que aparecen tres fabricantes de FPGAs a) Xlinx, Altera, Acme b) Intel, Motorola, GNU c) Xilinx, Altera, Actel d) Xilinx, lattice, Intel 17) En un computador con arquitectura Von Newman a) Se utiliza un nico espacio de memoria para datos e instrucciones b) No se utilizan integrados de memoria c) Se utilizan espacios de memoria separados para datos e instrucciones d) Ninguna de las anteriores 18) Un computador con arquitectura Harvard a) Utiliza el mismo espacio de memoria para datos e instrucciones b) Almacena datos e instrucciones en una ROM c) Utiliza memorias separadas para datos e instrucciones d) Ninguna de las anteriores Solucin a las preguntas de test: 1 c 2 d 3 d 4 c 5 c 6 a 7 c 8 d 9 d 10 d 11 b 12 c 13 d 14 b 15 c 16 c 17 a 18 c

46

You might also like

- Diseño de Una Puerta Electrónica para Un GarajeDocument7 pagesDiseño de Una Puerta Electrónica para Un GarajeTrabajos Academicos0% (1)

- Control de Invernadero..EQUIPODocument8 pagesControl de Invernadero..EQUIPOVeronica sanchezNo ratings yet

- Ilovepdf Merged PDFDocument6 pagesIlovepdf Merged PDFEduardo Saavedra LizarazúNo ratings yet

- CODIFICACION BINARIA (Paper Teoria)Document6 pagesCODIFICACION BINARIA (Paper Teoria)Joseph Muje RamosNo ratings yet

- Introducción a los Microcontroladores PIC16F8XX: Aplicaciones, Periféricos y Programación BásicaDocument31 pagesIntroducción a los Microcontroladores PIC16F8XX: Aplicaciones, Periféricos y Programación BásicacarlosbuitronNo ratings yet

- Multiplex OresDocument17 pagesMultiplex Oresyouacrazy100% (1)

- Bootloader USB para PIC18F4550Document9 pagesBootloader USB para PIC18F4550Maria MartinNo ratings yet

- EXA2G3OI PdfcreatorDocument38 pagesEXA2G3OI PdfcreatorTomas Sanchez TronoNo ratings yet

- Sistema de Riego AutomaticoDocument7 pagesSistema de Riego AutomaticoJoel Erico Escobar SalaNo ratings yet

- Control de Fase Con TriacDocument17 pagesControl de Fase Con TriacljgalloNo ratings yet

- Transmisión Analógica 4-20mA vs Voltaje: Ventajas Distancia RuidoDocument3 pagesTransmisión Analógica 4-20mA vs Voltaje: Ventajas Distancia RuidoArte VidriosNo ratings yet

- Practica2 TermistorDocument44 pagesPractica2 TermistorVerónica Marisol Barros BurneoNo ratings yet

- Contadores y RegistrosDocument32 pagesContadores y RegistrospepaNo ratings yet

- Manual de Prácticas Labview - López Jiménez VioletaDocument30 pagesManual de Prácticas Labview - López Jiménez Violetavioleta_jiménez_2No ratings yet

- Puente HDocument4 pagesPuente HEdrey91No ratings yet

- Modulo 3: Puerto Serie. Introducción Al Lenguaje CDocument51 pagesModulo 3: Puerto Serie. Introducción Al Lenguaje CJuan Gonzalez Gomez100% (1)

- Relevadores InteligentesDocument18 pagesRelevadores InteligentesJoseLuisMartinezNo ratings yet

- Parcial Electronica AnalogaDocument21 pagesParcial Electronica AnalogaAlexander WalkerNo ratings yet

- LabVIEW Robotics Starter KitDocument11 pagesLabVIEW Robotics Starter KitToño MontielNo ratings yet

- Circuito de luces audiorítmicas con filtros activosDocument12 pagesCircuito de luces audiorítmicas con filtros activosMidwar Miguel ChuraNo ratings yet

- Ejercicios ACDocument4 pagesEjercicios ACjavier andres perez gomez100% (1)

- Tema 1 - Ej - Transistor - BJT PDFDocument5 pagesTema 1 - Ej - Transistor - BJT PDFRaul Rufo RodriguezNo ratings yet

- Laboratorio Lenguaje Ensamblador ATmega16Document12 pagesLaboratorio Lenguaje Ensamblador ATmega16Angélica Trochez100% (1)

- Transistor Unijuntura (Ujt)Document14 pagesTransistor Unijuntura (Ujt)William CañónNo ratings yet

- Motor A Pasos VHDLDocument9 pagesMotor A Pasos VHDLAdrian TenaNo ratings yet

- Practica 2 InformeDocument13 pagesPractica 2 InformeAbel CabaNo ratings yet

- DigitalesDocument158 pagesDigitalesLeonel Chipana100% (1)

- Robot RubikDocument4 pagesRobot RubikM Sc Marco Antonio CancholaNo ratings yet

- Manual Labview PDFDocument113 pagesManual Labview PDFEdwin Fernandez Gonzales100% (1)

- Entrenador DigitalDocument16 pagesEntrenador DigitalJeisson Andres Cortes0% (1)

- Decodificador DAC0800Document4 pagesDecodificador DAC0800COBRACAN2208No ratings yet

- Innovación Electrónica - Problemas Resueltos Sobre Contadores, Flip-Flop (J-K) - Parte 2Document18 pagesInnovación Electrónica - Problemas Resueltos Sobre Contadores, Flip-Flop (J-K) - Parte 2Ovanio Molina100% (1)

- CLASE 1 - Introducción A La Programación Con ArduinoDocument69 pagesCLASE 1 - Introducción A La Programación Con ArduinoMauricio LorcaNo ratings yet

- Reporte de Seguidor de LineaDocument10 pagesReporte de Seguidor de LineaRaymond KenneyNo ratings yet

- Fuente Regulable Con ProteccionDocument1 pageFuente Regulable Con ProteccionFabian BecerraNo ratings yet

- Arduino lm35Document2 pagesArduino lm35Miguel Angel Ramirez RestrepoNo ratings yet

- Capacimetro Con Pic16f877aDocument17 pagesCapacimetro Con Pic16f877aAns Shel Cardenas YllanesNo ratings yet

- Partes de NI ELVIS IIDocument13 pagesPartes de NI ELVIS IIKatty Pinto100% (1)

- Contador de CajasDocument3 pagesContador de CajasMundoRo ComiPaNo ratings yet

- Cómo Hacer Un Capacímetro DigitalDocument22 pagesCómo Hacer Un Capacímetro DigitalAntonio José Montaña Pérez de CristoNo ratings yet

- Trabajo Automatización IndustrialDocument2 pagesTrabajo Automatización IndustrialCristhian Manuel Durán AcevedoNo ratings yet

- Lab. Control y Automatización 06 - 2020Document9 pagesLab. Control y Automatización 06 - 2020123456579No ratings yet

- PLC-Practica No 10Document4 pagesPLC-Practica No 10Adrian Alberto Palafox OrozcoNo ratings yet

- Control de Velocidad de Un Motor CD y Su Funcion de Transferencia Por MatlabDocument11 pagesControl de Velocidad de Un Motor CD y Su Funcion de Transferencia Por MatlabOmar Zupa100% (5)

- Ejercicios Sobre Sistemas DigitalesDocument2 pagesEjercicios Sobre Sistemas DigitalesAlejandro MontoyaNo ratings yet

- Decodificador BCD a 7 segmentos y codificador de prioridadDocument29 pagesDecodificador BCD a 7 segmentos y codificador de prioridadalexanderNo ratings yet

- Problemas DigitalDocument155 pagesProblemas DigitalEsteban Jose Hontoria ArlandizNo ratings yet

- Pensum Electronica Industrial 0Document1 pagePensum Electronica Industrial 0daniel moralesNo ratings yet

- Curso Altium DesignerDocument22 pagesCurso Altium DesignerAdrian CelaNo ratings yet

- Informe ProyectoDocument6 pagesInforme ProyectoJorge ZambranoNo ratings yet

- Innforme Practica VHDL ALUDocument13 pagesInnforme Practica VHDL ALUNatalia_meneses8No ratings yet

- Proyectos de Circuitos ElectricosDocument2 pagesProyectos de Circuitos ElectricosMarco MasNo ratings yet

- PROYECTO Termometro DigitalDocument5 pagesPROYECTO Termometro DigitalJoel Rubiano ArevaloNo ratings yet

- Circuitos DigitalesDocument11 pagesCircuitos DigitalesShirley Beleño BarriosNo ratings yet

- Retardo de Encendido Con 555Document47 pagesRetardo de Encendido Con 555Tratos ContratosNo ratings yet

- TAREA 2 Electrónica 1Document18 pagesTAREA 2 Electrónica 1Santiago Pabon100% (1)

- Sistemas Logicos - 1 - Guia de PracticosDocument22 pagesSistemas Logicos - 1 - Guia de PracticosFranklin ElPatronNo ratings yet

- Deber Circuitos DigitalesDocument3 pagesDeber Circuitos DigitalesWilliam LópezNo ratings yet

- Digital EsDocument8 pagesDigital EsAdrián SuárezNo ratings yet

- Métodos Matriciales para ingenieros con MATLABFrom EverandMétodos Matriciales para ingenieros con MATLABRating: 5 out of 5 stars5/5 (1)

- Examen 345 SolucionDocument3 pagesExamen 345 SolucionHurtado93No ratings yet

- Examen 67 SolucionDocument7 pagesExamen 67 SolucionHurtado93No ratings yet

- Ev Parcial 3Document1 pageEv Parcial 3Hurtado93No ratings yet

- Ev Parcial 1Document1 pageEv Parcial 1Hurtado93No ratings yet

- Ev Parcial 2Document1 pageEv Parcial 2Hurtado93No ratings yet

- 1 Control Soluciones PDFDocument6 pages1 Control Soluciones PDFHurtado93No ratings yet

- Soluciones Enero 2013 PDFDocument8 pagesSoluciones Enero 2013 PDFHurtado93No ratings yet

- Tipos de Alivios de ElementosDocument3 pagesTipos de Alivios de ElementosJulio Cesar Aguilar CaceresNo ratings yet

- EL KARMA ES UN JUEGO ARREGLADODocument19 pagesEL KARMA ES UN JUEGO ARREGLADOManuel Ortiz Garcia100% (1)

- Sesión de aprendizaje de taller de dramatización imitando animalesDocument4 pagesSesión de aprendizaje de taller de dramatización imitando animalesLucia Pinedo Paima100% (3)

- Dictamen DactiloscopicoDocument5 pagesDictamen DactiloscopicoAlejandra FallaNo ratings yet

- Revistas de EducaciónDocument45 pagesRevistas de EducaciónRafael Valverde SánchezNo ratings yet

- Acrilicos y CerasDocument7 pagesAcrilicos y CerasNahomi ArguellesNo ratings yet

- La Empresa Consultora de Ingenieria CivilDocument2 pagesLa Empresa Consultora de Ingenieria CivilwilliamIINo ratings yet

- Pisco ExposicionDocument17 pagesPisco ExposicionMary Trini Coari CoilaNo ratings yet

- Dirofiliarosis en Perros SJL LimaDocument4 pagesDirofiliarosis en Perros SJL LimaNice RamosNo ratings yet

- Cómo Reconciliarme Con Mi ParejaDocument4 pagesCómo Reconciliarme Con Mi ParejaSandra NiesvizkyNo ratings yet

- Guía llenado CFDI globalDocument42 pagesGuía llenado CFDI globalriosgNo ratings yet

- Empresas Transnacionales en El Agronegocio SoyeroDocument72 pagesEmpresas Transnacionales en El Agronegocio SoyeroCecy MéndezNo ratings yet

- SalazarpadillaCruzRodrigo Alumno Práctica No 2Document11 pagesSalazarpadillaCruzRodrigo Alumno Práctica No 2Omar Adrian Hernandez JimenezNo ratings yet

- Ficha ReflexivaDocument2 pagesFicha Reflexivayasccoa100% (1)

- Escuelas Psicológicas - PsicologiaDocument11 pagesEscuelas Psicológicas - PsicologiaLuis PLNo ratings yet

- TrayectoriaDocument82 pagesTrayectoriasunnet_mex100% (1)

- Caso CAROL ALDANA AnálisisDocument4 pagesCaso CAROL ALDANA AnálisisNeidy E. NuñezNo ratings yet

- Trabajo Final Numero 2 EstadisticaDocument17 pagesTrabajo Final Numero 2 EstadisticaAna Belen SomocurcioNo ratings yet

- Los Siete Pecados Capitales Del Imperio - Sebastian HaffnerDocument102 pagesLos Siete Pecados Capitales Del Imperio - Sebastian HaffnerRuben Mesias Cornejo100% (4)

- Aprendizaje Basado en Proyectos Comunitarios 2Document6 pagesAprendizaje Basado en Proyectos Comunitarios 2Martín PietraNo ratings yet

- Caso Practicp Terapia Narrativa PDFDocument19 pagesCaso Practicp Terapia Narrativa PDFMariaNo ratings yet

- Derivada y Antiderivada Cálculo IntegralDocument10 pagesDerivada y Antiderivada Cálculo IntegralGiovana MoralesNo ratings yet

- Leyes de NewtonDocument3 pagesLeyes de NewtonJhair Diaz Peche 1No ratings yet

- Responsabilidad SocialDocument3 pagesResponsabilidad SocialNgr BeatzNo ratings yet

- Caso Practico Construcciones AlturaDocument5 pagesCaso Practico Construcciones AlturaoLAt oz71% (7)

- Foro de DiscusionDocument6 pagesForo de DiscusionAnyie CoboNo ratings yet

- Residuos Generados Por La MineriaDocument90 pagesResiduos Generados Por La Mineriaperzy_xyz0% (1)

- Puente Grua Manipulación de CargasDocument73 pagesPuente Grua Manipulación de CargasAtilio PesquinNo ratings yet

- Presupuesto de Gastos Empresariales1Document52 pagesPresupuesto de Gastos Empresariales1Carmen BrunoNo ratings yet

- Fundamentos del emprendedurismoDocument11 pagesFundamentos del emprendedurismoAnny BorbonNo ratings yet