Professional Documents

Culture Documents

13.1 A Fully-Integrated Single-Chip SOC For Bluetooth

Uploaded by

kurabyqldOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

13.1 A Fully-Integrated Single-Chip SOC For Bluetooth

Uploaded by

kurabyqldCopyright:

Available Formats

ISSCC 2001 / SESSION 13 / Wireless LAN / 13.

13.1

A Fully-Integrated Single-Chip SOC for Bluetooth

Frank Opt Eynde1, Jean-Jacques Schmit1, Vincent Charlier1, Rudolph Alexandre1, Charles Sturman2, Kevin Coffin1, Bruno Mollekens1, Jan Craninckx1, Steven Terrijn1, Andrea Monterastelli1, Sofie Beerens1, Paul Goetschalckx1, Mark Ingels1, Dieter Joos1, Selim Guncer3, Ared Pontioglu3 Alcatel Microelectronics, Zaventem, Belgium TTP Communications, Melbourne, UK 3 Alcatel Microelectronics Teletas, Istanbul, Turkey

2 1

13.1.2) which also manages the Bluetooth clock offset application and re-synchronization. Synchronization and recognition of a valid access code (which initiates the receive function in the baseband controller) is by the RX-correlator block. The Audio Subsystem has a link to the Dual-Port buffer memory and a link to the microprocessor interface. This allows Bluetooth-specific speech over Host Controller Interface as well as a standard PCM-dedicated speech interface. The latter is more optimum for low-latency applications such as in a cellular terminal. In general, the Dual-Port RAM contains just enough information for the Baseband Core to operate during the next timeslot pair Rx-Tx or Tx-Rx. It is the responsibility of the LC state machine software to download just enough control information at the appropriate point to sustain the system. This is achieved by programming the next packet header and control information during transmission of the current packet. The analog radio front-end block schematic is shown in Figure 13.1.3. Since the Bluetooth specification [1] requires a receiver image rejection of only about 20dB, this image rejection is obtained fairly easily with a classical image-reject mixer, followed by a polyphase filter. The receiver intermediate frequency is 1MHz. With 15dB overall receiver noise figure, the sensitivity is 80dBm. This is 10dB better than the specification requirement. The differential LNA is realized with a common-gate architecture, as shown in Figure 13.1.4. Transistor M1 and resistor R1 form an amplifier stage, with a gain equal to gm1R1, and with an input impedance 1/gm1. The transconductance of transistor M1 is boosted by a second gain stage, formed by M2 and resistor R2. In this way, total LNA gain and input impedance are: A = gm1 R1 (1+ gm2 R2) and Zin = 2 gm (1+ gm R ) 1 2 2 For the transmitter, direct conversion is used. Image rejection and carrier feedthrough are improved by on-chip digital calibration. The calibration words are determined during factory testing, and stored in the Flash memory. The Transmitter Power Amplifier is integrated on-chip, and delivers up to +2dBm into a symmetrical antenna of 75W. The synthesizer is also fully integrated. The PLL is built around an integrated VCO, running at double the Local Oscillator frequency (4.8 to 5.0GHz). In this way, the parasitic coupling between PA and VCO is reduced. Furthermore, the VCO frequency divider (/2 in Figure 13.1.3) immediately provides the two quadrature LO signals. To compensate for process variations, a coarse digital VCO frequency autocalibration is integrated, in the same way as in Reference 2. The circuit is realized in a 0.25m CMOS technology and occupies a 40 mm2 die. A die micrograph is shown in Figure 13.1.5. About 50% of the chip area is occupied by the 48kB of Data RAM. The process features standard digital nMOS and pMOS transistors and an analog extention to realize resistors and metal-insulator-metal capacitors. Furthermore, additional process layers are included, to realize the Flash memory. A summary of the circuit specifications in given in Table 13.1.1. In normal operation, the Flash is seen by the processor as a ROM, without write access. The memory content is programmed by the foundry during device production test. Device-specific data such as the device serial number or calibration data for the radio are also pre-programmed. The Flash memory can also be re-programmed in the field: at power-up, a boot routine from a BootROM is executed by the microprocessor. Two dedicated pins are used to select the loading of a new program, either from the UART or from the SPI interface. An on-chip crystal oscillator provides the 13MHz reference clock for the RF frontend (Figure 13.1.6). By means of a bank of integrated capacitors, the crystal frequency can be slightly tuned. The tuning control word is stored in the Flash memory. The required frequency precision of 20ppm can be obtained with a low-precision quartz.

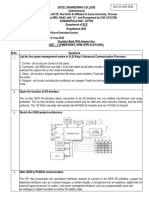

Market price targets for Bluetooth call for a low-cost integration of the full Bluetooth modem function. This single-chip Bluetooth implementation contains all necessary analog and digital functions for a fullfledged implementation of the V.0.1.b. Bluetooth specification [1], including point-to-multipoint communications, seven simultaneous links, multislot packets, encryption, master-slave switch, scatternet, etc. The circuit is built around four basic building blocks, as shown in Figure 13.1.1: a) The heart of the circuit is formed by an embedded microprocessor system (Processor, 48kB of RAM, 256kB Flash, BootROM in Figure 13.1.1). Parts of the physical layer protocol are executed by software on this microprocessor. All software layers up to the Host Control Interface are implemented. Since the software is stored in an on-chip Flash memory, it can be easily adapted towards future modifications of the Bluetooth standard, or towards specific customer needs. b) Dedicated Digital Baseband Processor hardware is foreseen for the time-critical parts of the Bluetooth physical layer protocol. c) An RF analog frontend is integrated on the chip. d) Several digital audio and data interfaces (Voice, UART and SPI in Figure 13.1.1) are included in the circuit. These interfaces are highly reprogrammable. In this way, the integration of the IC in an overall system is facilitated. Furthermore, theer are 12 general-purpose IO pins (GPIO in Figure 13.1.1). This allows interfacing the IC to external devices such as a display or a keyboard. The IC is primarily intended to serve as a Bluetooth modem for data and/or voice. However, spare Flash memory space is available for customer applications. Hence, complete Bluetooth applications (such as a Bluetooth mouse, for instance) can be realised as true single-chip systems. The Digital Baseband Core, as depicted in Figure 13.1.2, forms the lowest layer of the Link Controller function within the Bluetooth system. The hardware Baseband Core is complemented by a C-coded Bluetooth protocol stack. The lowest layer of this software is the Link Control state machine, which directly controls the hardware baseband processor. Together, the Link Control (LC) state machine software and the baseband processor device form the LC part of the Bluetooth protocol stack. The internal architecture of the Baseband processor is centered around a dual-port RAM buffer memory of 8kB, serving as data interface between the hardware Baseband Core and the microprocessor. For each active communication, the data stream is stored in this RAM. Also stored in this RAM are the encryption keys for each active link and all the context information such as active member address, packet type and encryption key selection ID. The bitstream Data Path performs all the required data processing such as Forward Error Correction, CRC calculation and Data Whitening. It is controlled directly by the Baseband State Controller. In this State Controller, the packet header is assembled from the link context information. This header is appended to the appropriate payload data stream from the Dual-Port RAM. The resulting packet is applied to the Data Path for bit-level data processing. The State controller interfaces with the software Link Control Interrupt Service Routine via the link context information in RAM. Sequencing of all baseband operations, such as header and payload assembly and radio interface timing, is by a Timing engine (Figure

2001 IEEE International Solid-State Circuits Conference

0-7803-6608-5

2001 IEEE

ISSCC 2001 / February 6, 2001 / Salon 7 / 1:30 PM

The digital baseband processor and microprocessor operate using a 26MHz clock obtained from an on-chip PLL. An optional 32kHz crystal can be connected to the IC. This allows turning off the 13MHz clock while still maintaining the Bluetooth clock with the benefit of lower power consumption. The presence of the optional 32kHz crystal is detected automatically. The overall circuit development cycle was shorter than 18 months, achieved using concurrent engineering wherever possible. When the project started, neither the silicon technology nor the package were available. Furthermore, the Bluetooth specification was still in evolution. Parallel teams worked on technology development, silicon parameter extraction, package engineering, digital design, software design and analog front-end design.

References: [1] The Bluetooth Special Interest group, The Bluetooth specification V.1.0.b. [2] J. Craninckx et al., A Fully-Integrated Zero-IF DECT Transceiver, ISSCC Digest of Technical Papers, pp. 138-139, Feb. 2000.

Table 13.1.1: Major circuit specifications.

Figure 13.1.2: Baseband processor block diagram.

Figure 13.1.1: Bluetooth SOC block diagram.

Figure 13.1.3: RF frontend block schematic.

2001 IEEE International Solid-State Circuits Conference

0-7803-6608-5

2001 IEEE

Figure 13.1.4: Low-noise amplifier schematic.

Figure 13.1.5: Die micrograph.

Figure 13.1.6: Tunable crystal oscillator.

2001 IEEE International Solid-State Circuits Conference

0-7803-6608-5

2001 IEEE

You might also like

- From GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandFrom EverandFrom GSM to LTE-Advanced Pro and 5G: An Introduction to Mobile Networks and Mobile BroadbandNo ratings yet

- 65 Caprio ElecLett 1973Document2 pages65 Caprio ElecLett 1973kurabyqldNo ratings yet

- Financial Analysis of Wipro LTDDocument101 pagesFinancial Analysis of Wipro LTDashwinchaudhary89% (18)

- 8051 LAB Manual NewDocument189 pages8051 LAB Manual New9491104570100% (2)

- Manual For Cycle 1Document193 pagesManual For Cycle 1Seth GreeneNo ratings yet

- Base Band Modem Hardware Design: P. Antognoni, E. Sereni, S. Cacopardi, S. Carlini, M. ScafiDocument5 pagesBase Band Modem Hardware Design: P. Antognoni, E. Sereni, S. Cacopardi, S. Carlini, M. Scafikokome35No ratings yet

- PCT Manual 2.3.1Document115 pagesPCT Manual 2.3.1SzefElityNo ratings yet

- Table of ContentDocument49 pagesTable of ContentAnonymous QIuAGIadXmNo ratings yet

- ATM Terminal Design Based On Figure Print Recognition DocuDocument115 pagesATM Terminal Design Based On Figure Print Recognition DocuPraveen NaiduNo ratings yet

- Ee 549 Undergraduate Project Ii: "Voip To PSTN Converter"Document30 pagesEe 549 Undergraduate Project Ii: "Voip To PSTN Converter"Obaweya SeyiNo ratings yet

- Rajavardhan UTMIDocument69 pagesRajavardhan UTMIRajavardhan_Re_6459No ratings yet

- A Reconfigurable Digital Signal Processing SystemDocument6 pagesA Reconfigurable Digital Signal Processing Systempym1506gmail.comNo ratings yet

- Project Report (Sample)Document80 pagesProject Report (Sample)Swapnith VarmaNo ratings yet

- Microcontroller (AT89S52) Based Remote Notice Board Using GSMDocument72 pagesMicrocontroller (AT89S52) Based Remote Notice Board Using GSMAkshayNo ratings yet

- ARM Question Bank Unit - 5Document14 pagesARM Question Bank Unit - 5sakthivelv.eecNo ratings yet

- PC To PC Optical Fibre CommunicationDocument7 pagesPC To PC Optical Fibre CommunicationPolumuri LovakumarNo ratings yet

- Rs-232 To I2c Protocol ConverterDocument4 pagesRs-232 To I2c Protocol ConverterHarsha100% (2)

- An Efficient Cordic Processor For Complex Digital Phase Locked LoopDocument7 pagesAn Efficient Cordic Processor For Complex Digital Phase Locked LoopInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- ZTE UniRan ZXSDR B8200 Hardware DescriptionDocument14 pagesZTE UniRan ZXSDR B8200 Hardware DescriptionAndika Alvi SahriNo ratings yet

- 25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentDocument84 pages25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentdileeppatraNo ratings yet

- DSP Hardware White PaperDocument5 pagesDSP Hardware White PaperSivaji MopideviNo ratings yet

- Project Report On Microcontroller Based Traffic Light ControllerDocument22 pagesProject Report On Microcontroller Based Traffic Light ControllerMohitpariharNo ratings yet

- Can Bus Standalone ControllerDocument24 pagesCan Bus Standalone ControllerDoan Van TuanNo ratings yet

- Sinclair QL Service Manual - Sinclair ResearchDocument45 pagesSinclair QL Service Manual - Sinclair Researchabo alasrarNo ratings yet

- RF Based Pick-And-place-robot Use ZigbeeDocument66 pagesRF Based Pick-And-place-robot Use Zigbeesumit_saNo ratings yet

- Messenger Development Without Internet Using Zigbee TechnologyDocument89 pagesMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyNo ratings yet

- A Rapid Prototyping Environment For Microprocessor Based System-on-Chips and Its Application To The Development of A Network ProcessorDocument4 pagesA Rapid Prototyping Environment For Microprocessor Based System-on-Chips and Its Application To The Development of A Network ProcessorSamNo ratings yet

- Describe The Operation of Timing and Control BlockDocument4 pagesDescribe The Operation of Timing and Control BlockTamayo Arrianna MurielNo ratings yet

- QL ServiceManualDocument98 pagesQL ServiceManualOscar Arthur KoepkeNo ratings yet

- Lab2 MotorControl 08Document18 pagesLab2 MotorControl 08ĐạiDương100% (1)

- SIMCON, Ver. 3.0.: FPGA Based, DSP Integrated, 8-ChannelDocument34 pagesSIMCON, Ver. 3.0.: FPGA Based, DSP Integrated, 8-ChanneljuanNo ratings yet

- User Manual lpc2141 lpc2142 lpc2144 lpc2146 lpc2148Document354 pagesUser Manual lpc2141 lpc2142 lpc2144 lpc2146 lpc2148Anonymous kT0ONWNo ratings yet

- GSM Based Electronic Notice Display SystemDocument7 pagesGSM Based Electronic Notice Display SystemNaga Neelima ThunuguntlaNo ratings yet

- Implementing Cognitive Radio for Efficient RF CommunicationDocument8 pagesImplementing Cognitive Radio for Efficient RF CommunicationinfydiptiNo ratings yet

- A Mixed-Signal Sensor Interface MicroinstrumentDocument12 pagesA Mixed-Signal Sensor Interface MicroinstrumentPhạm Ngọc HòaNo ratings yet

- Bluetooth Based Home AutomationDocument71 pagesBluetooth Based Home Automationakshat singh50% (2)

- 2.microcontroller Based Transformer Health Monitoring System Using IotDocument38 pages2.microcontroller Based Transformer Health Monitoring System Using IotDinesh KumarNo ratings yet

- ArmputerDocument14 pagesArmputerapi-3726520100% (1)

- Usb Implementation Using Utmi MacrocellDocument71 pagesUsb Implementation Using Utmi Macrocellrockfloyd100% (6)

- Moving message display: Embedded C and hardware requirementsDocument45 pagesMoving message display: Embedded C and hardware requirementsMuraliKrishnaNo ratings yet

- FM Based Long Range Remote Control: Project Work ONDocument42 pagesFM Based Long Range Remote Control: Project Work ONVenkatesh DoppalapudiNo ratings yet

- RTL 8186Document50 pagesRTL 8186Maria Alejandra DalcolmoNo ratings yet

- Project Report On Microcontroller Based Traffic Light ControllerDocument23 pagesProject Report On Microcontroller Based Traffic Light Controllerالموعظة الحسنه chanelNo ratings yet

- Microcontroller Based SMS Gateway DesignDocument10 pagesMicrocontroller Based SMS Gateway DesignMohammed RiyazuddinNo ratings yet

- Usbkbd 5Document25 pagesUsbkbd 5youcef88No ratings yet

- Index: A. About KielDocument73 pagesIndex: A. About KieldileeppatraNo ratings yet

- LPC2148 MCU User ManualDocument354 pagesLPC2148 MCU User ManualzelalembirhanuNo ratings yet

- Xport TCP IpDocument5 pagesXport TCP IpKarthick Vijayan100% (1)

- Color Detection Using FPGA Based Smart CameraDocument19 pagesColor Detection Using FPGA Based Smart Cameratry199No ratings yet

- d900 MSC HardwareDocument9 pagesd900 MSC HardwareDeepakNo ratings yet

- TechnicalDocument65 pagesTechnicalMehdiNo ratings yet

- A Development Platform For Microcontroller STM32F103Document67 pagesA Development Platform For Microcontroller STM32F103picatilioNo ratings yet

- I2CDocument6 pagesI2CGovinda RaoNo ratings yet

- Adsp-Bf534 BF536 BF537Document68 pagesAdsp-Bf534 BF536 BF537StalinVasyaNo ratings yet

- RS 485Document51 pagesRS 485mgitecetech100% (1)

- PC to PC fiber optic data transferDocument7 pagesPC to PC fiber optic data transferpallaishashankashekharNo ratings yet

- ARM7 UM10139 - LPC214xDocument354 pagesARM7 UM10139 - LPC214xnilmak2u2No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Digital Electronics, Computer Architecture and Microprocessor Design PrinciplesFrom EverandDigital Electronics, Computer Architecture and Microprocessor Design PrinciplesNo ratings yet

- How Will Climate Change Affect The Cairns Region?Document2 pagesHow Will Climate Change Affect The Cairns Region?kurabyqld100% (1)

- Ucc3941 5Document20 pagesUcc3941 5kurabyqldNo ratings yet

- 0115Document7 pages0115kurabyqldNo ratings yet

- Azeez SramlimitsDocument4 pagesAzeez SramlimitskurabyqldNo ratings yet

- RHPZ, A Two Way Control PathDocument11 pagesRHPZ, A Two Way Control PathkurabyqldNo ratings yet

- JAP1998 Nonvolatilememory Ac NitrogendopedDocument5 pagesJAP1998 Nonvolatilememory Ac NitrogendopedkurabyqldNo ratings yet

- Low Frequency CapacitorsDocument3 pagesLow Frequency CapacitorskurabyqldNo ratings yet

- Features Description: Ltc3536 1A Low Noise, Buck-Boost DC/DC ConverterDocument28 pagesFeatures Description: Ltc3536 1A Low Noise, Buck-Boost DC/DC ConverternevdullNo ratings yet

- P578Document1 pageP578Anonymous 0YEApBuZINo ratings yet

- APL 2009 RateequationanalysisDocument3 pagesAPL 2009 RateequationanalysiskurabyqldNo ratings yet

- 0217Document1 page0217kurabyqldNo ratings yet

- 15 Thomsen ISSCC 2000Document2 pages15 Thomsen ISSCC 2000kurabyqldNo ratings yet

- Logicworks4 TutorialDocument10 pagesLogicworks4 TutorialAbdullah HasanNo ratings yet

- Pronouns EnglishDocument13 pagesPronouns EnglishMihai AlexxNo ratings yet

- NanoMat12 Optional Paper 01bDocument6 pagesNanoMat12 Optional Paper 01bkurabyqldNo ratings yet

- ECE 304: Iterative Design of Feedback Network: SchematicDocument6 pagesECE 304: Iterative Design of Feedback Network: SchematickurabyqldNo ratings yet

- Fully DepletedDocument4 pagesFully DepletedkurabyqldNo ratings yet

- Apl 2002 Electronic CharacDocument3 pagesApl 2002 Electronic CharackurabyqldNo ratings yet

- Integrator's Time ConstantsDocument2 pagesIntegrator's Time ConstantskurabyqldNo ratings yet

- 30 Bollati JSSC 2001Document11 pages30 Bollati JSSC 2001kurabyqldNo ratings yet

- Abstract ISSCC2011 SC1 AbstractDocument1 pageAbstract ISSCC2011 SC1 AbstractkurabyqldNo ratings yet

- Analysis and Optimization of Accumulation-Mode Varactor For RFDocument2 pagesAnalysis and Optimization of Accumulation-Mode Varactor For RFkurabyqldNo ratings yet

- 2 Kinget CICC 2008Document6 pages2 Kinget CICC 2008kurabyqldNo ratings yet

- Transactions Briefs: Improved Switched Tuning of Differential Cmos VcosDocument4 pagesTransactions Briefs: Improved Switched Tuning of Differential Cmos VcoskurabyqldNo ratings yet

- New F820 Survival Magnesium Flint Fire Steel Starter Start StickDocument4 pagesNew F820 Survival Magnesium Flint Fire Steel Starter Start StickkurabyqldNo ratings yet

- Abstract ISSCC2011 SC2 AbstractDocument1 pageAbstract ISSCC2011 SC2 AbstractkurabyqldNo ratings yet

- 709 Op AmpDocument7 pages709 Op AmpWuttichai KiamNo ratings yet

- PLCC Lightbar Modules (IP67) - Eng - v2Document0 pagesPLCC Lightbar Modules (IP67) - Eng - v2kurabyqldNo ratings yet

- Damcos Mas2600 Installation UsermanualDocument26 pagesDamcos Mas2600 Installation Usermanualair1111No ratings yet

- Computer Networks Transmission Media: Dr. Mohammad AdlyDocument14 pagesComputer Networks Transmission Media: Dr. Mohammad AdlyRichthofen Flies Bf109No ratings yet

- Seminar Course Report ON Food SafetyDocument25 pagesSeminar Course Report ON Food SafetyYanNo ratings yet

- Physioex 9.0 Exercise 1 Act 1Document5 pagesPhysioex 9.0 Exercise 1 Act 1Adela LhuzNo ratings yet

- H I ĐĂNG Assigment 3 1641Document17 pagesH I ĐĂNG Assigment 3 1641Huynh Ngoc Hai Dang (FGW DN)No ratings yet

- Journals OREF Vs ORIF D3rd RadiusDocument9 pagesJournals OREF Vs ORIF D3rd RadiusironNo ratings yet

- Assembly ModelingDocument222 pagesAssembly ModelingjdfdfererNo ratings yet

- An Introduction To Ecology and The BiosphereDocument54 pagesAn Introduction To Ecology and The BiosphereAndrei VerdeanuNo ratings yet

- 202112fuji ViDocument2 pages202112fuji ViAnh CaoNo ratings yet

- Gabinete STS Activity1Document2 pagesGabinete STS Activity1Anthony GabineteNo ratings yet

- Audi Q5: First Generation (Typ 8R 2008-2017)Document19 pagesAudi Q5: First Generation (Typ 8R 2008-2017)roberto100% (1)

- LIST OF ENROLLED MEMBERS OF SAHIWAL CHAMBER OF COMMERCEDocument126 pagesLIST OF ENROLLED MEMBERS OF SAHIWAL CHAMBER OF COMMERCEBASIT Ali KhanNo ratings yet

- Tutorial 1 Discussion Document - Batch 03Document4 pagesTutorial 1 Discussion Document - Batch 03Anindya CostaNo ratings yet

- Bad DayDocument3 pagesBad DayLink YouNo ratings yet

- SiloDocument7 pagesSiloMayr - GeroldingerNo ratings yet

- Form 709 United States Gift Tax ReturnDocument5 pagesForm 709 United States Gift Tax ReturnBogdan PraščevićNo ratings yet

- 4 Influencing Factors of Learners Career Choice Parents Choice Vs Personal DescisionDocument24 pages4 Influencing Factors of Learners Career Choice Parents Choice Vs Personal Descisionmatteo mamaloNo ratings yet

- Excel Solver Optimization ReportDocument9 pagesExcel Solver Optimization ReportMy Duyen NguyenNo ratings yet

- Todo Matic PDFDocument12 pagesTodo Matic PDFSharrife JNo ratings yet

- Link Ratio MethodDocument18 pagesLink Ratio MethodLuis ChioNo ratings yet

- 2018 NAMCYA CHILDREN'S RONDALLA ENSEMBLE GuidelinesDocument3 pages2018 NAMCYA CHILDREN'S RONDALLA ENSEMBLE GuidelinesJohn Cedrick JagapeNo ratings yet

- SBI Sample PaperDocument283 pagesSBI Sample Paperbeintouch1430% (1)

- Simba s7d Long Hole Drill RigDocument2 pagesSimba s7d Long Hole Drill RigJaime Asis LopezNo ratings yet

- 02 Slide Pengenalan Dasar MapinfoDocument24 pages02 Slide Pengenalan Dasar MapinfoRizky 'manda' AmaliaNo ratings yet

- PHY210 Mechanism Ii and Thermal Physics Lab Report: Faculty of Applied Sciences Uitm Pahang (Jengka Campus)Document13 pagesPHY210 Mechanism Ii and Thermal Physics Lab Report: Faculty of Applied Sciences Uitm Pahang (Jengka Campus)Arissa SyaminaNo ratings yet

- Evaluative Research DesignDocument17 pagesEvaluative Research DesignMary Grace BroquezaNo ratings yet

- WindSonic GPA Manual Issue 20Document31 pagesWindSonic GPA Manual Issue 20stuartNo ratings yet

- Reading and Writing Q1 - M13Document13 pagesReading and Writing Q1 - M13Joshua Lander Soquita Cadayona100% (1)