Professional Documents

Culture Documents

7 CLK Tree Synthesis

Uploaded by

dharma_panga8217Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

7 CLK Tree Synthesis

Uploaded by

dharma_panga8217Copyright:

Available Formats

Day 7 Clock Tree Synthesis

Session Speaker Ajaya Kumar.s

PEMP VSD531

Session objective

After completing this session students will be able to: Clock Tree General Concepts Impact of clock skew Clock Skew Types CTS in design flow and basic steps CTS in real P&G flow Set up the design for clock tree synthesis Perform clock tree synthesis Perform post CTS optimizations Analyze timing and clock specifications post CTS

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Session Topics

Clock Tree Synthesis (CTS) goals Clock tree attribute Clock Distribution schemes Clock Skew Clock Tree Optimization Techniques Effect of clock tree synthesis

Identify settings of key timing parameters for pre-CTS and post-CTS stages

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Design Status, Start of CTS Phase

Placement - completed Power and ground nets prerouted Estimated congestion acceptable Estimated timing acceptable (~0ns slack) Estimated max cap/transition no violations High fanout nets: Reset, Scan Enable synthesized with buffers Clocks are still not buffered

Why Whyare arethere thereno nobuffers bufferson onclock clocknets? nets?

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Before CTS

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

Clock

FF FF FF FF FF FF

FF

FF

FF

FF

FF

FF

All Allclock clockpins pinsare aredriven drivenby bya asingle singleclock clocksource. source.

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

CTS Goals

Meet logical Design Rule Constraints (DRC):

� � � �

Maximum transition delay Maximum load capacitance Maximum fanout Maximum buffer levels Maximum skew Min/Max insertion delay

Constraints Constraints are are upper upper bound bound goals. goals. If If constraints constraints are are not not met, met, violations violations will will be be reported. reported.

Meet the clock tree targets:

� �

Targets are "nice "nice to to have" have" goals. goals. If If Targets are targets targets are are not not met, met, no no violations violations will will be be reported. reported.

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Clock Tree Synthesis (CTS) (1/2)

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

Clock

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

A A buffer buffer tree tree is is built built to to balance balance the the loads loads and and minimize minimize the the skew. skew.

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Clock Tree Synthesis (CTS) (2/2)

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

Clock

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

FF

A A delay delay line line is is added added to to meet meet the the minimum minimum insertion insertion delay. delay.

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Where does the Clock Tree Begin and End?

Clock tree begins at SDC-defined clock source:

�

D Q STOP

GATED

FF CLK

create_clock

STOP

D Q FF CLK

� �

Clock tree ends at sinks Clock sinks are:

� �

CLOCK

Start

STOP

D Q FF

Stop / Float pins Exclude pins (aka ignore pins)

CLK

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Define Clock Root Attributes (1/2)

When the clock root is a primary port of a block

�

� � �

Ensure that an appropriate driving cell is defined set_driving_cell The synthesis constraints may include a weak driving cell for all inputs, including the clock port Because the clock is ideal during synthesis it has no effect on design QoR But a weak driver on the clock port affects clock tree QoR during CTS

Driving Cell External driving cell specified for clock port Clock root defined on primary clock port 10 CLK

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Define Clock Root Attributes (2/2)

When the clock root is a primary port, but at the CHIPlevel through an IO-PAD

�

Ensure that an appropriate input transition is defined set_input_transition

Specify input transition

CLK

IO_PAD

Clock root defined on primary clock port

M.S.Ramaiah School Of Advanced Studies

11

PEMP VSD531

Stop, Float and Exclude Pins

Exceptions

Implicit STOP or FLOAT pins

skew and insertion delay are optimized

STOP Pins: � CTS optimizes for DRC and clock tree targets (skew, insertion delay) FLOAT Pins: � Like Stop pins, but with delays on clock pin EXCLUDE Pins: � CTS optimizes for DRC only (ignores clock tree targets)

GATED

D Q

CLOCK

FF D Q CLK FF IP_CLK IP CLK

skew and insertion delay are ignored

Implicit EXCLUDE pins

D Q CLK_OUT

FF

CLK

M.S.Ramaiah School Of Advanced Studies

12

PEMP VSD531

Generated and Gated Clocks

Q FF1 CLK

GATED

0.64

D

All insertion delays are matched

Q FF2 CLK

0.65

D

Q FF3

CLOCK

D Q

CLK

0.63

D FF4 CLK Q

create_clock

FFD

CLK QN

D

Q FF5 CLK

create_generated_clock

Skew will be balanced globally, within each clock domain, across all clock-pins of both master and generated clock.

M.S.Ramaiah School Of Advanced Studies

13

PEMP VSD531

User-defined or Explicit Stop Pins

Scenario: If the clock pin inside a macro cell is correctly defined, CTS will treat that pin as an implicit stop pin. In this example the clock pin is not defined. What is the problem here?

The The macros macros clock clock pin pin is is marked marked as as an an implicit implicit exclude exclude pin pin no no skew skew optimization! optimization!

CLOCK

D Q FF3 CLK

skew and insertion delay are ignored

IP_CLK Implicit exclude pin

no clock pin definition

D Q FF CLKn

IP (FRAM)

M.S.Ramaiah School Of Advanced Studies

14

PEMP VSD531

Defining an Explicit Stop Pin

Defining an explicit stop pin allows CTS to optimize for skew and insertion delay targets. CTS has no knowledge of the IP-internal clock delay it can only see up to the stop pin!

CLOCK

Q FF CLK

0.42

0.43

skew and insertion delay are now optimized

IP_CLK

Explicit stop pin defined

D Q FF CLKn

0.17

IP

set_clock_tree_exceptions stop_pins [get_pins IP/IP_CLK]

M.S.Ramaiah School Of Advanced Studies

15

PEMP VSD531

Defining an Explicit Float Pin

Exceptions

Defining Defining an an explicit explicit float float pin pin allows allows CTS CTS to to adjust adjust the the insertion insertion delays delays based based on on specification. specification.

CLOCK

0.42

D Q FF CLK

0.27

skew and insertion delay are now optimized

IP_CLK

D Q

Explicit float pin defined

0.15

FF D Q CLKn

FF

set_clock_tree_exceptions \ -float_pins IP/IP_CLK \ -float_pin_max_delay_rise 0.15

IP

CLKn

M.S.Ramaiah School Of Advanced Studies

16

PEMP VSD531

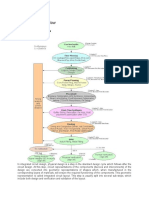

Clock Tree Optimization

Perform additional Clock Tree Optimization as necessary to further improve clock skew.

Placed design with clock tree synthesized that meets setup/hold, tran/cap

Clock Clock Analysis Analysis

CT optimization is run inside clock_opt, and can be run independently as well:

No CTO CTO

Clock Clock spec spec met? met? Yes Routing

optimize_clock_tree

M.S.Ramaiah School Of Advanced Studies

17

PEMP VSD531

Clock Distribution Systems

Style Unconstrained tree Balanced tree Central spine Spines with matched branches Grid Hybrid distribution Distribution Automated buffer placements with unconstrained trees Multiple levels of balanced tree segments H-tree is most common Central clock driver Multiple central structures with length (or delay) matched branches Interconnected (shorted) clock structure Combination of multiple techniques Common theme is tree + grid or spine + grid

M.S.Ramaiah School Of Advanced Studies

18

PEMP VSD531

Unconstrained tree

It is commonly used in automatic synthesis flows and usually placed with little or no restriction on the number of buffer stages and explicit matching between interconnect delays and the buffer delays

M.S.Ramaiah School Of Advanced Studies

19

PEMP VSD531

Balanced Tree

Uses Recursive H structure to distribute the clock signal At each point of a new H in the tree, the resistance is halved and the capacitance is doubled Larger line width is used for the main H structure to minimize resistance Narrower line width is used at the branching points along the tree to minimize capacitance

M.S.Ramaiah School Of Advanced Studies

20

PEMP VSD531

Balanced Tree Cont.

Balanced H-tree clock topology is a structural symmetry, a balanced tree exhibits identical nominal delay and identical buffer and interconnect segments from the root of the distribution to all branches. Full balanced tree topologies are designed to span the entire die in both the horizontal and vertical dimensions. They are capable of delivering the clock to all regions of the die.

M.S.Ramaiah School Of Advanced Studies

21

PEMP VSD531

H structure

Clock Driver Larger line width to reduce resistance

Narrow line to reduce capacitance

M.S.Ramaiah School Of Advanced Studies

22

PEMP VSD531

Grid Network

Gridded clock distribution was common on earlier DEC Alpha microprocessors. Advantages: Clock signals are available everywhere Tolerant to process variations Usually yields extremely low skew values Disadvantages: Huge amounts of wiring & power Routing area large Wire cap large

M.S.Ramaiah School Of Advanced Studies

23

PEMP VSD531

Central Spine

A central spine clock distribution is a specific implementation of a binary tree. Figure shows an idealized central spine implementation with the final branches serving all parts of the die. The binary tree is shown to have embedded shorting at all distribution levels and unconstrained routing to the local loads at the final branches.

In this configuration, the clock can be transported in a balanced fashion across one dimension of the die with low structural skew. The unconstrained branches are simple to implement although there will be residual skew due to asymmetry

M.S.Ramaiah School Of Advanced Studies

24

PEMP VSD531

Hybrid Distribution

A hybrid clock distribution incorporates a combination of earlier described topologies. Common configurations are spines-grid distribution or tree-grid distribution. It employs a multilevel H-tree driving a common grid. Specifically, the multilevel Htree delivers the clock from the clock generator to various regions of the die.

Regional buffers (labeled as level 4 buffers in Fig.) residing at the end of the multilevel H-tree drive a common grid that includes all local loads

M.S.Ramaiah School Of Advanced Studies

25

PEMP VSD531

Hybrid Distribution Cont

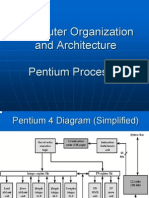

Pentium 4 processor clock distribution using centralized spines with delay matched final branches.

M.S.Ramaiah School Of Advanced Studies

26

PEMP VSD531

Clock distribution characteristics of commercial processors

Name

Merom Power6

Frequency

3,000 5000

skew

18 8

Technology

65 65

Clock Dist. style

Tree/Grid Sym. HTree/Grid Tree/Grid

Xeon processor Pentium 4 processor Itanium 2 processor

3,400 3,600

11 16

65 180

Spine/Grid 1,500 24 130 Asymmetric tree

27

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Clock Distribution Network

M.S.Ramaiah School Of Advanced Studies

28

PEMP VSD531

Path Length and its Delay Model

S0

L0, W0

R1 S1

CL1

N0

L2, W2 L1, W1

S0

C0/2

R0

C0/2

C1/2

C1/2

R2

C2/2 C2/2

S2

CL2

S2

S1 The delay Model

29

An equal Path length clock Tree

M.S.Ramaiah School Of Advanced Studies

PEMP VSD531

Path Length and its Delay Model Cont.

The skew between S1 and S2 is given by :

rl1 rl 2 ts = C L1 CL2 w1 w2

The skew variation in terms of wire width variation

t 2 rl 2 C L 2 t1 rl1C L1 w2 = w1 + w2 w1 + t s = 2 2 w2 w1 w2 w1

If w = 0.15w the worst case additional skew is

rl1C L1 rl 2 C L 2 t s = 0.15 w + w 2 1

M.S.Ramaiah School Of Advanced Studies

30

PEMP VSD531

Buffer Insertion in Clock Tree

Different buffer delays cause phase delay variations on different source to sink paths, the given tolerable skew of a buffered clock tree ts into two components Tolerable skew for buffer delays,

ts = t + t

b s

w s

t

t

b = tolerable skew for buffer delays s

= wire width variation after buffer insertion

w s

Buffer insertion problem is to find the location on the clock tree to insert intermediate buffers and and these locations are buffer insertion points (BIPs)

M.S.Ramaiah School Of Advanced Studies

31

PEMP VSD531

Clock Skew

Clock skew is the maximum difference in the arrival time of a clock signal at two different components. Clock skew forces designers to use a large time period between clock pulses. This makes the system slower. So, in addition to other objectives, clock skew should be minimized during clock routing.

M.S.Ramaiah School Of Advanced Studies

32

PEMP VSD531

Local Skew

DIN

A_OUT

D FF3 CLK Q

DIN

A

T3 (0.4ns)

D

A_OUT

D FF3 CLK Q

Q FF1 CLK

Q FF1 CLK

CLOCK

CLOCK

T1 (0.2ns)

B_OUT

D FF2 CLK Q

B_OUT

D FF2 CLK Q

B

T2 (0.2ns)

Related path is minimized for skew

Longer runtime

M.S.Ramaiah School Of Advanced Studies

33

PEMP VSD531

Global Skew

DIN

A_OUT

D FF3 CLK Q

DIN

A

T3 (0.38ns)

A_OUT

D FF3 CLK Q

D D Q FF1 CLK

Q FF1 CLK

CLOCK

CLOCK

T1 (0.37ns)

B_OUT

D FF2 CLK Q

B_OUT

D FF2 CLK Q

B

T2 (0.38ns)

All clock delays are matched as close as possible

Global skew is recommended - fastest

M.S.Ramaiah School Of Advanced Studies

34

PEMP VSD531

Useful Skew

DIN DIN

A_OUT

D FF3 CLK Q

A

T3 (0.22ns)

A_OUT

D FF3 CLK Q

D D Q FF1 CLK

Q FF1 CLK

B

B_OUT

D FF2 CLK Q

CLOCK

CLOCK

T1 (0.11ns)

B_OUT

D FF2 CLK Q

T2 (0.35ns)

Add clock delay to FF2 to help setup time

Use to fix small violations where local or global failed

M.S.Ramaiah School Of Advanced Studies

35

3X

F F F F F F F 3X F F F F F F F F F

4X 4X

4X 2X 3X

F F F F F F

F F F F F F

Clock Tree Optimization (1/2)

After

4X F F F F F F 5X 4X

After Before

F F F F F F

3X

F F F F F F F F F F F 2X F F F

M.S.Ramaiah School Of Advanced Studies

3X F F F F F F F F 4X 4X 2X F F F F F F F F F 4X

4X

F F F F F F

3X

F F F F F F F F

4X

2X

F F F F F F F F F 4X F F F

After

36

After

PEMP VSD531

F F F

PEMP VSD531

Clock Tree Optimization (2/2)

F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F

F F F

Before Level Adjustment

F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F F

F F F

Before

F F F F F F F F F F F F F F F

Reconfiguration After

M.S.Ramaiah School Of Advanced Studies

After

37

PEMP VSD531

Clock Design Problem

What are the main concerns for clock design? Skew No. 1 concern for clock networks For increased clock frequency, skew may contribute over 10% of the system cycle time Power very important, as clock is a major power consumer! It switches at every clock cycle! Noise Clock is often a very strong aggressor May need shielding Delay Not really important But slew rate is important (sharp transition)

M.S.Ramaiah School Of Advanced Studies

38

PEMP VSD531

Effects of Clock Tree Synthesis

Clock buffers added Congestion may increase Non clock cells may have been moved to less ideal locations Inserting clock trees can introduce new timing and max tran/cap violations

M.S.Ramaiah School Of Advanced Studies

39

PEMP VSD531

Timing-Driven P&R

optimizes the logic gates, places and routes them to meet all timing constraints Timing Constraints == Speed Goals

M.S.Ramaiah School Of Advanced Studies

40

PEMP VSD531

Timing Constraints

� �

Arrival time of inputs Clock period Required arrival time at outputs

M.S.Ramaiah School Of Advanced Studies

41

PEMP VSD531

Timing is Based on Cell and Net Delays

0.5 ns Rnet Cnet Cpin

Cell Delay = (Input Transition Time, Cnet + Cpin) Net Delay = (Rnet, Cnet + Cpin)

� �

IC Compiler calculates delay for every cell and every net To calculate delays, needs to know each nets parasitic Rs and Cs

M.S.Ramaiah School Of Advanced Studies

42

PEMP VSD531

TLU

TLU model comes from the vendor and is contained in tech file Contains capacitance look-up tables only Resistance is calculated from the net geometry and a resistance/length (unit resistance) value from the tech file

Layer "METAL1" { unitNomResistance }

= 6.4e-5

CapTable "metal1_C_LATERAL_14MIN" { wireWidthSize = 5 wireSpacingSize = 16 wireWidth = (0.16, 0.32, 0.48, 0.64, 0.8) wireSpacing = (0.18, 0.36, 0.54, 0.72, , 2.88) capValue = (0.000183764, 9.85682e-05, 6.5029e-05, ) } CapModel "metal1Config4" { refLayer = "METAL1" lateralCapType = "Table" lateralCapDataMin = "metal1_C_LATERAL_14MIN" }

M.S.Ramaiah School Of Advanced Studies

43

PEMP VSD531

TLU +:

� � � �

TLU+ models: Model UDSM process effects Contain C and R look-up tables If TLU+ models are available, use them!

UDSM UDSMProcess ProcessEffects Effects �� Conformal Dielectric Conformal Dielectric �� Metal MetalFill Fill �� Shallow ShallowTrench TrenchIsolation Isolation �� Copper Dishing: Copper Dishing: Density DensityAnalysis Analysis Width/Spacing Width/Spacing �� Trapezoid TrapezoidConductor Conductor

TLU+

Astro

Single Process File (ITF)

M.S.Ramaiah School Of Advanced Studies

nxtgrd

Star-RCXT

44

PEMP VSD531

Mapping file

The Mapping File maps the .tf layer/via names to Star-RCXT .itf layer/via names.

cb13.tf Layer "METAL" { layerNumber maskName cb13.map conducting_layers poly metal1 metal2 = 14 = "metal1" cb13.itf DIELECTRIC cm_extra3 { THICKNESS=0.06 ER=4.2 } CONDUCTOR cm { THICKNESS=0.26 WMIN=0.16 } DIELECTRIC diel1d { THICKNESS=0.435 ER=4.2 }

poly cm cm2

M.S.Ramaiah School Of Advanced Studies

45

PEMP VSD531

Calculating Cell and Net Delay

�

Now that R and C are known from TLU/TLU+, the delays can be calculated For Cell Delays, only Ceff is needed

R3 C3 C4

U2

U1

R2 R1 C2

C1

Calculating Net Delay is done using Delay Calculation algorithms: Elmore, AWE, Arnoldi

M.S.Ramaiah School Of Advanced Studies

46

PEMP VSD531

PreRoute Delay Calculation Algorithm: Elmore

Virtual Route

Pin-to-pin timing

� �

After placement, but prior to routing, net geometry is estimated based on a Virtual Route Since Virtual Routing is only an estimate, Elmore should be used for all steps up to and including routing

M.S.Ramaiah School Of Advanced Studies

47

PEMP VSD531

PostRoute Delay Calculation Algorithms (Cont..)

Detailed Route

� �

After routing, detailed nets are available and extraction will be more accurate Use AWE or Arnoldi for postroute optimizations Arnoldi is preferred when comparing to PrimeTime

M.S.Ramaiah School Of Advanced Studies

48

PEMP VSD531

Timing SetUp parameters [a] Ignore Interconnect (OFF by default):

When turned ON ignores any parasitic capacitance and resistance effects of the interconnect nets (i.e. Rnet = 0; Cnet = 0) during optimization and timing reporting The only time this is recommended is when performing a timing sanity check on the starting netlist, before beginning placement. atiming sanity check is performed by running a timing report with all the timing panel settings in preCTS mode, but with Ignore Interconnect turned ON.

M.S.Ramaiah School Of Advanced Studies

49

PEMP VSD531

Timing Setup parameters (Cont..)

[b] Enable Preset/Clear Arcs (OFF by default):

By default, asynchronous preset and clear timing arcs are not analyzed for timing. Depending on your design, you may have to enable this setting after CTS. E.g. if Your design contains a reset network that is asserted asynchronously, will not analyze for preset/clear violations on the flip-flops unless this setting is enabled

M.S.Ramaiah School Of Advanced Studies

50

PEMP VSD531

Prior to Clock Tree Synthesis (1/3)

� �

Clock Tree not built yet Clock signal ports are connected directly to all FF clock ports without a buffer tree Clock

Many more FFs

The SDC should use set_clock_uncertainty command to model an estimate for the Clock Skew that is going to appear once the Clock Tree is synthesized

D Even more FFs

Q Clock skew?

M.S.Ramaiah School Of Advanced Studies

51

PEMP VSD531

Prior to Clock Tree Synthesis (Cont.)

� �

Load on clock port/driver pre-CTS is tremendous CTS will buffer the load

Many more FFs D Q

Clock1 Pre-CTS, Pre-CTS, the the delay delay to to the the FFs FFs is is ideal. ideal. i.e. i.e. the the delay delay is is zero, zero, unless unless commands commands are are used used to to model model the the clock clock insertion insertion delay. delay. example: example: set_clock_latency set_clock_latency Clock2 D Q

D Q

Even more FFs

M.S.Ramaiah School Of Advanced Studies

52

PEMP VSD531

Prior to Clock Tree Synthesis (Cont.)

�

Clock transition at FF clk ports is unknown until CTS has been performed You need to provide an estimate for pre-CTS timing analysis (default is 0)

D Q

Pre-CTS, use SDC command set_clock_transition to apply a transition to all FF clock pins

?

Clock1

D Q

?

Clock2

D Q

?

M.S.Ramaiah School Of Advanced Studies

53

PEMP VSD531

Setup timing check

A setup timing check verifies the timing relationship between the clock and the data pin of a flip-flop so that the setup requirement is met. In other words, the setup check ensures that the data is available at the input of the flip-flop before it is clocked in the flip-flop. The data should be stable for a certain amount of time, namely the setup time of the flip-flop, before the active edge of the clock arrives at the flip-flop.

M.S.Ramaiah School Of Advanced Studies

54

PEMP VSD531

Hold Timing Check

A hold timing check ensures that a flip-flop output value that is changing does not pass through to a capture flip-flop and overwrite its output before the flip-flop has had a chance to capture its original value. This check is based on the hold requirement of a flip-flop. The hold specification of a flip-flop requires that the data being latched should be held stable for a specified amount of time after the active edge of the clock.

M.S.Ramaiah School Of Advanced Studies

55

PEMP VSD531

Removal timing check

A removal timing check ensures that there is adequate time between an active clock edge and the release of an asynchronous control signal. The check ensures that the active clock edge has no effect because the asynchronous control signal remains active until removal time after the active clock edge. In other words, the asynchronous control signal is released (becomes inactive) well after the active clock edge so that the clock edge can have no effect.

M.S.Ramaiah School Of Advanced Studies

56

PEMP VSD531

Recovery Timing Check

A recovery timing check ensures that there is a minimum amount of time between the asynchronous signal becoming inactive and the next active clock edge. In other words, this check ensures that after the asynchronous signal becomes inactive, there is adequate time to recover so that the next active clock edge can be effective.

M.S.Ramaiah School Of Advanced Studies

57

PEMP VSD531

On-Chip Variations

Due to process variations, identical MOS transistors in different portions of the die may not have similar characteristics . These differences are due to process variations within the die. Note that the process parameter variations across multiple manufactured lots can cover the entire span of process models from slow to fast These differences can arise due to many factors, including: i. IR drop variation along the die area affecting the local power supply. ii. Voltage threshold variation of the PMOS or the NMOS device. iii. Channel length variation of the PMOS or the NMOS device. iv. Temperature variations due to local hot spots. v. Interconnect metal etch or thickness variations impacting the interconnect resistance or capacitance.

M.S.Ramaiah School Of Advanced Studies

58

PEMP VSD531

Derating setup timing check for OCV.

M.S.Ramaiah School Of Advanced Studies

59

PEMP VSD531

Derating Hold timing check for OCV.

M.S.Ramaiah School Of Advanced Studies

60

PEMP VSD531

Data to Data Checks

One important distinction with respect to the setup check of a flip-flop is that the data to data setup check is performed on the same edge as the launch edge (unlike a normal setup check of a flip-flop, where the capture clock edge is normally one cycle away from the launch clock edge). Thus, the data to data setup checks are also referred to as zero-cycle checks or same-cycle checks.

M.S.Ramaiah School Of Advanced Studies

61

PEMP VSD531

Clock Gating Checks

A clock gating check occurs when a gating signal can control the path of a clock signal at a logic cell. An example is shown in Figure. The pin of the logic cell connected to the clock is called the clock pin and the pin where the gating signal is connected to is the gating pin. The logic cell where the clock gating occurs is also referred to as the gating cell.

M.S.Ramaiah School Of Advanced Studies

62

PEMP VSD531

Power Gating

Power gating involves gating off the power supply so that the power to the inactive blocks can be turned off. This procedure is illustrated in Figure, where a footer (or a header) MOS device is added in series with the power supply. The control signal SLEEP is configured so that the footer (or header) MOS device is on during normal operation of the block. Since the power gating MOS device (footer or header) is on during normal operation, the block is powered and it operates in normal functional mode.

M.S.Ramaiah School Of Advanced Studies

63

PEMP VSD531

Session Summary

�

Clock tree synthesis is one of the most important steps of IC design and can have a significant impact on timing, power, area, etc. Clock tree synthesis and optimization are an iterative processes and can require replacement and rerouting various times in order to optimize clock tree parameters. CTS importance increases for 90nm and below technologies and especially when applying low power design techniques as they significantly change the ratio of gate interconnects as well as manners of building clock trees depending on their multi-level structures. Differentiating between TLU/TLU+ models wrt process Foundry rules

M.S.Ramaiah School Of Advanced Studies

64

You might also like

- Your UNIX Linux The Ultimate Guide 3rd Edition by Sumitabha Solution ManualDocument1 pageYour UNIX Linux The Ultimate Guide 3rd Edition by Sumitabha Solution ManualAasif Wani0% (1)

- ICC Design PlanningDocument471 pagesICC Design Planningm100% (1)

- CLock Tree Synthesis PDFDocument50 pagesCLock Tree Synthesis PDFMudit Agarwal100% (2)

- AMD Interview QuestionsDocument4 pagesAMD Interview QuestionsRohit Somkuwar100% (1)

- Advanced Fusion Compiler Synthesis and P& R Technologies To Drive Performance andDocument37 pagesAdvanced Fusion Compiler Synthesis and P& R Technologies To Drive Performance andyang hu100% (1)

- Steps To Root Cause Clock Latency - Insertion Delay QOR Post CCopt CTSDocument8 pagesSteps To Root Cause Clock Latency - Insertion Delay QOR Post CCopt CTSPradeep Kumar ManthaniNo ratings yet

- Static Timing Analysis 9100Document32 pagesStatic Timing Analysis 9100Balaji VenkataramanNo ratings yet

- LowPower Practical Guide April08 ReleaseDocument253 pagesLowPower Practical Guide April08 ReleaseDeepak JagannathNo ratings yet

- Synopsys PrimeTime - Introduction To Static Timing Analysis WorkshopDocument21 pagesSynopsys PrimeTime - Introduction To Static Timing Analysis WorkshopApoorva Bhatt100% (2)

- Configure Debug Complex Clock Network CCOptDocument41 pagesConfigure Debug Complex Clock Network CCOptANSHITA100% (2)

- VLSI Test Principles and Architectures: Design for TestabilityFrom EverandVLSI Test Principles and Architectures: Design for TestabilityRating: 4.5 out of 5 stars4.5/5 (4)

- System-on-Chip Test Architectures: Nanometer Design for TestabilityFrom EverandSystem-on-Chip Test Architectures: Nanometer Design for TestabilityNo ratings yet

- STA Concepts and Interview Questions PDFDocument173 pagesSTA Concepts and Interview Questions PDFAtul100% (3)

- Ackend (Physical Design) Interview Questions and AnswersDocument46 pagesAckend (Physical Design) Interview Questions and AnswersP Brahma Reddy100% (2)

- SynthesisDocument18 pagesSynthesissrajeceNo ratings yet

- PostRoute ClockTran FixDocument8 pagesPostRoute ClockTran Fixsneha96669100% (1)

- Clock Skew: Hold Time RequirementsDocument4 pagesClock Skew: Hold Time Requirementsniranjanpujari25100% (1)

- Designing A Robust Clock Tree StructureDocument9 pagesDesigning A Robust Clock Tree StructureStudent100% (1)

- Constraints Sta PDFDocument92 pagesConstraints Sta PDFPudi SriharshaNo ratings yet

- Clock Gating MethodologyDocument71 pagesClock Gating MethodologyGirish BabuNo ratings yet

- Special CelllsDocument14 pagesSpecial Celllspdnoob100% (4)

- Clock GatingDocument12 pagesClock Gatingsandyk_24No ratings yet

- PD Flow I - Floorplan - Physical Design, STA & Synthesis, DFT, Automation & Flow Dev, Verification Services. Turnkey ProjectsDocument21 pagesPD Flow I - Floorplan - Physical Design, STA & Synthesis, DFT, Automation & Flow Dev, Verification Services. Turnkey ProjectsShwethNo ratings yet

- Physical Synthesis 2.0Document52 pagesPhysical Synthesis 2.0ravishopingNo ratings yet

- PrimeTime SlidesDocument47 pagesPrimeTime SlidesRamakrishnaRao SoogooriNo ratings yet

- Static Timing AnalysisDocument100 pagesStatic Timing Analysismrinalmishra100% (2)

- Clock BuffersDocument29 pagesClock Buffersnaveen silveri100% (2)

- Clock Issues in Deep Submircron DesignDocument50 pagesClock Issues in Deep Submircron DesignRay Hua100% (1)

- Smart Physical Aware ECODocument11 pagesSmart Physical Aware ECOMukul AnandNo ratings yet

- ICCII Physical Lib Analysis For Optimal Routing v1 0122 EditDocument59 pagesICCII Physical Lib Analysis For Optimal Routing v1 0122 Editferrari100% (1)

- Physical Design FundamentalsDocument92 pagesPhysical Design FundamentalsLakshman YandapalliNo ratings yet

- Design & Verification of Low Power SocsDocument54 pagesDesign & Verification of Low Power SocsAnkit GoelNo ratings yet

- High Fanout NetsDocument26 pagesHigh Fanout NetsAditya Devarakonda100% (3)

- 11timing Concepts and Physical DesignDocument42 pages11timing Concepts and Physical DesignTeja Reddy100% (3)

- Low Power VerificationDocument19 pagesLow Power VerificationJyothi ShrinivasNo ratings yet

- Physical DesignDocument52 pagesPhysical DesigndtatdtaNo ratings yet

- Timing Analysis in Physical DesignDocument32 pagesTiming Analysis in Physical Designgoud.mahesh0584269100% (2)

- Cells of Low-Power Design - Switch CellDocument19 pagesCells of Low-Power Design - Switch Cellveeru100% (1)

- Static Timing AnalysisDocument40 pagesStatic Timing Analysissaranya008No ratings yet

- Physical Design FlowDocument42 pagesPhysical Design Flowelumalaianitha100% (1)

- Scenario: + Mode: Supply VoltagesDocument40 pagesScenario: + Mode: Supply VoltagesShwethNo ratings yet

- Ccopt Rak For Beginners: Product - Innovus 16.20 April 2017Document71 pagesCcopt Rak For Beginners: Product - Innovus 16.20 April 2017Akshat Pathak100% (1)

- Eco FlowDocument25 pagesEco Flowprabhakar reddyNo ratings yet

- Reducing Congestion With IC CompilerDocument9 pagesReducing Congestion With IC Compilermaharajm98100% (1)

- Synopsys Class 2 5 1Document67 pagesSynopsys Class 2 5 1prashanth kumarNo ratings yet

- STA CornersDocument39 pagesSTA Cornerscannister100% (1)

- Sta Constraints Nandan RoyDocument6 pagesSta Constraints Nandan RoyAvas RoyNo ratings yet

- Advanced Node Experience From CadenceDocument92 pagesAdvanced Node Experience From Cadencexiaokang.liu100% (2)

- BlockImplementation151 LabDocument49 pagesBlockImplementation151 Labkishore kumar kota100% (2)

- Static Timing AnalysisDocument71 pagesStatic Timing Analysisapi-3762689100% (13)

- SynthesisDocument51 pagesSynthesissudhir100% (1)

- Examples of Setup and Hold Time - Static Timing Analysis (STA) Basic (Part 3c) - VLSI ConceptsDocument7 pagesExamples of Setup and Hold Time - Static Timing Analysis (STA) Basic (Part 3c) - VLSI ConceptsRakesh KumarNo ratings yet

- Ccopt InnovusDocument2 pagesCcopt InnovussagarNo ratings yet

- Sta NotesDocument33 pagesSta NotesSujith ChallaNo ratings yet

- Wire Load ModelDocument18 pagesWire Load Modelvincentvln100% (1)

- Synthesis Guide Very GoodDocument332 pagesSynthesis Guide Very GoodAtif Ammed SyedNo ratings yet

- Clock Tree Synthesis: Pushpendra Patel Project EngineerDocument22 pagesClock Tree Synthesis: Pushpendra Patel Project EngineerUtkarsh AgrawalNo ratings yet

- Clock Balance Ieee Seminar04Document49 pagesClock Balance Ieee Seminar04Anvesh Reddy100% (1)

- CTS SignoffsemiconductorsDocument7 pagesCTS SignoffsemiconductorsAgnathavasiNo ratings yet

- CMOS Transistor Layout KungFuDocument39 pagesCMOS Transistor Layout KungFuAyo Iji100% (5)

- DRCDocument16 pagesDRCdharma_panga8217No ratings yet

- DRCDocument16 pagesDRCdharma_panga8217No ratings yet

- Ir em Syn PDFDocument6 pagesIr em Syn PDFKhadar BashaNo ratings yet

- Layout DesignDocument21 pagesLayout Designdharma_panga8217No ratings yet

- VLSI Cell PlacementDocument78 pagesVLSI Cell Placementdharma_panga8217No ratings yet

- Art Control High Speed DesignsDocument4 pagesArt Control High Speed Designsdharma_panga8217No ratings yet

- Kipp CU4HDDsg 01a 0915Document17 pagesKipp CU4HDDsg 01a 0915Remote sipilNo ratings yet

- Nokia X2-00 RM-618 Service Manual L1L2 v1.0Document22 pagesNokia X2-00 RM-618 Service Manual L1L2 v1.0Pedro De Leon LimaNo ratings yet

- Modelsim Se TutDocument205 pagesModelsim Se TutAbdul MutaalNo ratings yet

- Memmert UN55 ManualDocument48 pagesMemmert UN55 ManualMuhammad LuqmanNo ratings yet

- FRC Game ManualDocument65 pagesFRC Game Manualmaths22No ratings yet

- TTL Texas Instruments: 7400 Series Integrated CircuitsDocument14 pagesTTL Texas Instruments: 7400 Series Integrated CircuitsRickey Castillo ValenzuelaNo ratings yet

- CNC Router ProjectDocument32 pagesCNC Router ProjectanouarNo ratings yet

- Practical Introduction To PCI Express With FPGAs - ExtendedDocument77 pagesPractical Introduction To PCI Express With FPGAs - ExtendedNH Hoang XuanNo ratings yet

- Autolisp NotesDocument53 pagesAutolisp NotesTejashree SatheNo ratings yet

- Pentium 4 StructureDocument38 pagesPentium 4 Structureapi-3801329100% (6)

- ZF Actuator PDFDocument40 pagesZF Actuator PDFMATIAS100% (3)

- Lab Manual 1 ExpDocument21 pagesLab Manual 1 ExpSujana Kalyan50% (2)

- Le Unigear Zs1 BTB Reva 1vcp000275Document2 pagesLe Unigear Zs1 BTB Reva 1vcp000275hizbi7No ratings yet

- 2700 Recetas ThermomixDocument1,144 pages2700 Recetas Thermomixgamusino007No ratings yet

- SNFv3.0.13 User GuideDocument88 pagesSNFv3.0.13 User Guideatalasa-1No ratings yet

- Release NotesDocument130 pagesRelease NotesVishalNo ratings yet

- PSMC Designer Users GuideDocument42 pagesPSMC Designer Users GuideelvinguitarNo ratings yet

- Bca SyllabusDocument33 pagesBca SyllabuspratheepaNo ratings yet

- 1101261296107806assistant Garade II ODEPC - PMDDocument8 pages1101261296107806assistant Garade II ODEPC - PMDratheesh1981No ratings yet

- Automated School BellDocument1 pageAutomated School BellgoahelloNo ratings yet

- Oscillators For Microcontrollers: June 1983Document40 pagesOscillators For Microcontrollers: June 1983Pavankumar KalliNo ratings yet

- Integrating Technology in The Classroom 1Document12 pagesIntegrating Technology in The Classroom 1api-457024644No ratings yet

- Abr 200 ManDocument200 pagesAbr 200 ManalanseabraNo ratings yet

- Smk1060f - MosfetDocument8 pagesSmk1060f - Mosfetagus2kNo ratings yet

- P+F Universal Power RailDocument3 pagesP+F Universal Power RailJeremiah CayondongNo ratings yet

- Dual Ignitors and Continuos Ignition in Jet EnginesDocument5 pagesDual Ignitors and Continuos Ignition in Jet Enginesa_sharafieh100% (1)

- M2150 MultiCab Elevator Controller Installation Instructions Issue 1.2Document2 pagesM2150 MultiCab Elevator Controller Installation Instructions Issue 1.2Anonymous IQJwSTNo ratings yet

- Dell Precision R5500 Server Spec SheetDocument2 pagesDell Precision R5500 Server Spec SheetTim ChegeNo ratings yet