Professional Documents

Culture Documents

Nanocrystalline Silicon Thin Film Transistor (Nc-SiH TFTS) - A Device

Uploaded by

IAEME PublicationOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Nanocrystalline Silicon Thin Film Transistor (Nc-SiH TFTS) - A Device

Uploaded by

IAEME PublicationCopyright:

Available Formats

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 115

Nanocrystalline Silicon Thin Film Transistor (nc-Si:H TFTs)-A Device

for Display Panels

Prachi Sharma

1

, Navneet Gupta

2

Department of Electrical & Electronics Engineering, Birla Institute of Technology and Science

Pilani, Rajasthan, India

1

prachi.sharma@pilani.bits-pilani.ac.in,

2

ngupta@pilani.bits-pilani.ac.in

ABSTRACT: Nanocrystalline silicon (nc-Si:H) has recently emerged as a possible alternative to

both hydrogenated amorphous silicon and polycrystalline silicon for high speed large area

displays. In this paper, a global overview is presented on the nanocrystalline silicon TFT

technology, which includes TFT structure, operation, channel materials, characteristics and

device performance. The various physical effects involved in the conduction mechanism of nc-

Si:H are also discussed.

KEYWORDS: Nanocrystalline silicon (nc-Si:H), Thin-film transistors (TFTs), Threshold-voltage

shift (VT), Density of states (DOS), Hydrogenated amorphous silicon (a-Si:H), Polycrystalline

silicon (poly-Si)

I. INTRODUCTION

From the mid-1980s the silicon-based thin film transistors (TFTs) are used as switching

elements and for fabrication of their peripheral driving circuits in large area electronics [1-3].

Large- area electronics involves various applications in which low speed, micrometer size

transistors are sufficient in spite of sophisticated transistors. The aim of these applications is to

spread electronic components over large area substrate at low fabrication cost. Active matrix

liquid crystal displays (AMLCDs) [1], organic light-emitting diode displays (OLEDs) [2], radio-

frequency identification (RFID) tags [3], medical X-ray imager [4] are the important

applications of large area electronics. The most beneficial aspect of TFT technology is a

separate transistor for each pixel on the display. As each transistor is small, the amount of

charge needed to control it is also small. This allows for very fast re-drawing of the display.

For fabricating thin film transistors, different materials are used as an active layer. The

commonly used materials are amorphous hydrogenated silicon (a-Si:H) and polycrystalline

silicon (poly-Si). The main advantage of a-Si:H is the possibility for deposition over large area

at relatively low temperature (below 450C) [5]. Plasma Enhanced Chemical Vapour Deposition

(PECVD) is commonly used for the deposition of amorphous silicon over large area at low

temperatures. The material obtained by PECVD is a-Si:H. The a-Si:H is an amorphous silicon

INTERNATIONAL JOURNAL OF ELECTRONICS AND

COMMUNICATION ENGINEERING & TECHNOLOGY (IJECET)

ISSN 0976 6464(Print)

ISSN 0976 6472(Online)

Special Issue (November, 2013), pp. 115-127

IAEME: www.iaeme.com/ ijecet.asp

Journal Impact Factor (2013): 5.8896 (Calculated by GISI)

www.jifactor.com

IJECET

I A E M E

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 116

alloy with incorporated hydrogen atoms. However the disadvantages of a-Si:H are low electron

mobility and instability. The low temperature PECVD process used for a-Si:H deposition as well

as the amorphous nature of non-crystalline substrate (like glass), lead to the formation of

amorphous material having missing atoms. Deep defect states in the forbidden energy gap of

the a-Si:H are associated with these missing atoms, i.e. dangling bonds. Deep defect states are

also associated with the deviation in bond length and angle which results in states below the

conduction band, known as band tail states. The density of states (DOS) in a-Si:H is in the range

10

15

-10

18

cm

-3

eV

-1

. The electrons are frequently trapped into and released from these band tail

states leading to the low mobility. Thus a-Si:H has electron mobility as low as 0.1-1 cm

2

V

-1

s

-1

[6] and hole mobility is so low that the p-type devices are not used in any application. Although

this low electron mobility is sufficient for pixel switch applications and LCDs [7].

In addition to low electron mobility, a-Si:H also suffers from bias stress induced degradation

and light induced degradation. As a consequence, the electrical characteristics of TFTs (like VT,

field effect mobility and sub threshold slope) change and this damages the overall device

performance [9, 10]. As TFTs in LCD and X-ray imager pixel devices are not subject to

prolonged gate voltages thus for these devices instability is not a major issue.

When a-Si:H goes under annealing process, it can be transformed into poly-Si. Poly-Si is having

low hydrogen atoms in large grained silicon films and thus poly-Si is not called as

hydrogenated. The main advantages of poly-Si are high electron mobility and better stability.

Since poly-Si is a network of randomly oriented crystalline grains interconnected by thin grain

boundaries, the defects in poly-Si are concentrated in the grain boundaries whereas in a-Si:H

materials they are uniformly distributed in the bulk. In case of poly-Si, large grains are

preferred, as the larger grain size results in lesser grain boundaries across the channel. This

results in lower density of defect states [11] in poly-Si, leading to lesser trapping of carriers at

grain boundaries and hence higher mobility (~100 cm

2

V

-1

s

-1

) [7] than a-Si:H materials. Poly-Si

TFTs provide sufficient electron and hole mobility in n-type and p-type devices for CMOS

(complementary metal oxide semiconductor) operation. Due to high mobility, poly-Si can also

be applicable to peripheral circuits like multiplexers etc. The main problem with poly-Si is that

the crystallization process requires a much higher temperature (usually higher than 300C)

than the a-Si:H deposition temperature. In addition to this problem, poly-Si also suffers from

poor spatial uniformity as random positioning of grain boundaries causes irregularity across

the channel. This results in mobility and threshold voltage non-uniformity over large area

substrate [7, 12].

Nanocrystalline silicon (nc-Si:H) has been proposed as a promising alternative material to a-

Si:H and poly-Si. The advantages of nc-Si:H over a-Si:H are high carrier mobility and better

stability. It can have higher field effect mobility than a-Si:H due to the presence of higher silicon

crystallites [13] as well as increased doping efficiency. For top gated devices, field effect

mobility (FET) is in range of 40 cm

2

/ Vs [14] to 150 cm

2

/ Vs [15] and for bottom gate, it is in

the range of 0.5-3 cm

2

/ Vs [16,17].Due to the presence of lower hydrogen concentration, nc-

Si:H have improved stability under bias and illumination stress [13] than a-Si:H. The

advantages of nc-Si:H over poly-Si are low processing temperatures (as low as 150C), low

manufacturing cost and better uniformity [18]. Hot wire chemical vapour deposition (HWCVD)

allow direct obtainment of nc-Si:H at very low substrate temperature over large area and at

high deposition rates (about 1nm/ s) [18].The resulting nc-Si:H film consists of small silicon

crystallites than poly-Si, with an average grain size of a few nanometers, embedded into a-Si.

However, the main problem with nc-Si TFT is that it is affected from high drain leakage

currents, i.e. off-current.

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 117

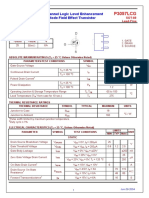

Attribute a-Si:H nc-Si:H Poly-Si

Mobility Low Much higher than a-Si:H High

Circuit type NMOS NMOS/PMOS NMOS/PMOS

Stability Issue More stable than a-Si:H Stable

Drive capacity (I

ON

) Large W/L

to reduce V

G

Small W/L

at small V

G

Small W/L

at small V

G

V

T

uniformity High High Improving

Mobility uniformity High Potentially high Improving

Manufacturability Mature RF PECVD New

Cost Low Low High

Table 1: Comparison between different materials used for the TFT fabrication

II. DEVICE STRUCTURE AND OPERATION

The TFTs consist of three electrodes (i.e. source, drain and gate), gate insulator, and thin

semiconductor layer. These elements can be arranged in many ways. Based on the level of the

gate electrode, the TFTs are divided into two types, top gate TFT and bottom gate TFT. In top

gated TFT, the gate electrode is located above the semiconductor layer whereas in bottom

gated TFT, the gate electrode is located below the semiconductor layer. These two types are

further subdivided into coplanar and staggered devices, giving a total of four types of basic

TFTs structures. The term coplanar/ staggered describes the location of source and drain

electrodes with respect to the gate electrode. In coplanar case, the source and drain electrodes

are located at the same side as the gate electrode while in staggered case, the source and drain

electrodes are located at the opposite side to the gate electrode separated with the

semiconductor layer.

Fig. 1: Illustration of different TFT structures [19]

III. ELECTRICAL INSTABILITY OF TFTS

The a-Si:H and nc-Si TFTs are generally suffers from bias stress degradation due to two major

instability mechanisms i.e. defect creation in the a-Si:H active layer and charge trapping in the

gate dielectric. The creation of defect states leads to an increasing of the density of states in the

band-gap of the channel material and also causes the degradation of electrical characteristics

like increasing of the threshold voltage and decreasing of the sub-threshold slope. When defect

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 118

state creation take place, it is necessary to apply thermal or bias annealing in order to recover

the initial device performance [20, 21]. When charge trapping occurs in the gate insulator or at

the channel/ insulator interface, then the threshold voltage increases under positive stress and

decreases under negative stress. Annealing under special thermal and/ or bias conditions is

necessary to release the trapped charge from the gate insulator whereas when charge trapped

at the channel/ insulator interface, it can be released at room temperature without need of

annealing. The interface trapped charge has the similar effect on the characteristics as the

charge trapped in the bulk of the insulator. The only difference is that the charge trapped in the

interface requires less energy in order the charge to be released.

Various authors [22, 23] presented the model for carrier-induced defect creation and proposed

that hydrogen atom that is available in the channel material diffuses to the weak Si-Si bond and

participate in the process where upon the breakage of the weak bond, two dangling bonds are

created which one of them is passivated by the hydrogen. Hydrogen diffusion has been found

to follow stretched-exponential time dependence and to be dispersive. Authors examined that

the resulting dispersive motion of the hydrogen leads to the stretched-exponential time

dependence of carrier-induced creation of defects and consequently, the shift in the threshold

voltage. Thus authors assumed that defect state creation is the dominant mechanism of the

shift in threshold voltage.

I

1

=C _1 cxp_[

t

:

[

__ (1)

Where C VGS - VT0, VGS is the applied gate-source voltage, also called gate bias stress, VTO is the

threshold voltage at time t = 0, and and are a time constant and tting exponent,

respectively. The parameter has been found to be around 0.5 at room temperature [22, 23].

IV. DRAIN LEAKAGE CURRENT OR OFF-CURRENT

A. Top-Gated TFT

Various authors examined the leakage current in the top-gated nc-Si:H TFT at various

temperatures. Authors proposed that under high I

uS

and high I

S

(=10V), the behaviour is

reminiscent of the Poole-Frenkel emission in the drain depletion region and Eacontinues to

decrease as I

uS

increase upto 10V [24].

I

PP

=I

PP0

exp([E

PK

) (2)

Where, I

PP0

is the generation current at zero electric field. E

PK

is the peak electric field [25].

E

PK

= |I

uS

I

S

I

PB

|

s

cx

t

cx

s

si

(3)

[is the PF coefficient [25]

[ = q

3

2

/ ne

s

KI (4)

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 119

And under high I

uS

(>0V) and low I

S

(=5V), the leakage current can be attributed to the

thermal emission of trapped carriers present at the mid-gap grain boundary states and Ea

becomes independent of I

uS

.The value of Ea i.e. 0.720.002eV is retrieved from the average and

standard deviation between I

uS

=0V and 10V

I

1L

= I

1L0

cxp [

L

c

k1

(5)

WhereI

1L0

is independent of temperature and constant.

Lee et. al. [25] also proposed that under low gate bias, the leakage current is mainly due to the

ohmic conduction through the bulk nc-Si:H channel layer and IL has a weaker gate and drain

bias dependence. The increase in resistive leakage current with I

uS

can be referring to the

increase in peak holes concentration in the bulk. This is the main reason behind the decrement

of activation energy from 0.77 to 0.72eV for I

S

=5V.

B. Bottom-Gated TFT

Authors examined the leakage current in n-channel nc-Si TFTs and proposed that when a high

drain voltage (Vds>0) is applied, the large electric field generated at the reverse n

+

-p drain

junction. This electric field would assist the electrons in the valence band to travel by band to

band tunnelling. The use of a-Si and nc-Si double layer beneath the n

+

a-Si drain contact is

required in order to reduce the leakage current since the a-Si:H has the larger band gap as

compare to nc-Si [26]. According to the tunnelling theory, at large drain bias voltages, the

tunnelling leakage current is given as [24]

I

L

=AF exp[

L

0

P

(6)

Where, A is constant in AcmV

-1

.

F is the maximum electric field at the drain junction [27]

F =

v

dg

-v

]b

t

i

(s

s

-s

i

)

+

v

d

w

(7)

Where I

]b

is the flat band voltage,I

dg

=Vd-Vg. e

and t

is the permittivity and thickness of SiNX,

respectively and w is the depletion region of the p-n junction [24]

E

0

=

4(2m

r

)

1/ 2

L

g

3/ 2

3qh

(8)

Where h is the Plancks constant divided by 2n, mr is the tunnelling effective electron mass and

Egis the energy gap of the silicon.

At low electric fields (E<2.2 MV/ cm) [28], the leakage current is dominated by PF conduction.

V. PERFORMANCE OF NC-SI:H TFT

Various stochastic effects which affect the performance of nc-Si:H TFT and thus changes the

characteristic of the device are:

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 120

A. Temperature

The defect state creation and thus the shift in the threshold voltage are a function of time and

temperature. When device operating temperature increases, the rate of hydrogen diffusion

increases which results in an increase in VT. The hydrogen dependence is reflected in the

parameter as

=

0

cxpj

L

A

k

B

1

[ (9)

Where 0 has been found to be around 10

-10

sec and EA=0.95eV is the activation energy [22].

Various authors [29] compared the threshold voltage shift of the nc-Si TFTs with that of the a-

Si:H counterpart, under similar operation conditions. For example, they electrically stressed

the TFTs under constant drain currents of 2, 10, and 15 A at two temperatures of 22 and 75

C

for 50 hours. And found two fundamental differences in the behavior of nc-Si TFTs compared

to that of the a-Si:H TFTs. First, VT in nc-Si TFT saturates at prolonged stress times, but that of

a-Si:H TFT does not. Second, VT in nc-Si TFT is weakly temperature dependent, in contrast to

that of a-Si:H device. For example, after 50 hours stressing at 15 A, VT in nc-Si TFT is 3 V and

4 V at 22 and 75

C, respectively, whereas that for the a-Si:H TFT is 7.6 V and 21 V, respectively.

The observed behavior of VT indicates absence of defect state creation in the nc-Si TFTs. Its

weak temperature dependence is consistent with the mechanism proposed by Powell et al.

[20], implying that the instability mechanism is charge trapping in the nitride. The kinetics of

VT does also follow the stretched exponential time dependence predicted for charge trapping

[30, 31].

To further support the conclusion that defect creation is absent in nc-Si TFTs, authors [29]

investigated the other attribute of the charge trapping, i.e. its reversibility. It is known that

charge trapping is reversible, but defect creation is indenitely stable and irreversible at room

temperature. Authors performed the relaxation test, in which nc-Si TFT was electrically

stressed for some time to induce some shift in its threshold voltage. Subsequently, the TFT was

relaxed, i.e. bias voltages were removed and device was turned off. From time to time, authors

performed a quick test to retrieve its I-V characteristics to see whether the induced VT was

disappeared and initial I-V curves were obtained. Authors found that after 5 days relaxation at

room temperature, the initial I-V curves can be obtained. This observation is an another

evidence indicating that charge trapping in the nitride causes VT in nc-Si TFTs. If defect

creation were the source of instability, it may take around a year at room temperature to

anneal the created defects and retrieve the initial I-V curves.

B. Grain Size

Mao [32] proposed a model for the shift of valence and conduction band edges and proposed

that valence or conduction band edges are affected by grain size which in turn affects the

barrier height at nc-Si/ SiO2 interface. This is because it equals to the difference between the

barrier height at the bulk-Si/ SiO2 interface for electrons and the shift of conduction band edge.

E

c

(J) =

L

g

_1+

m

c

m

h

]

=

3.4382

dX10

9

+

1.1483

(dX10

9

)

2

_1+

m

c

m

h

]

(eV) (10)

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 121

E

(J) =

L

g

[1+

m

h

m

c

=

3.4382

dX10

9

+

1.1483

(dX10

9

)

2

[1+

m

h

m

c

(eV) (11)

According to above equations [32], the edge of the conduction band or valance band will be

shifted by the grain size. Thus barrier height will decrease.

The gate leakage current of nc-Si TFTs strongly depends on the silicon-grain size. This results

from the large change in the band gap and dielectric constant due to size effects. The screening

dielectric constant of nc-Si can be theoretically calculated with the formula [33] below,

e

nc-S

(J) = 1+

10.4

1+[

1.38

d10

9

1.3

(12)

In above equation, the unit of d is meter.

The model of quantum confinement, within the effective mass approximation predicts a shift of

the valence band edge with size i.e. the valence band edge shifts to larger binding energy in

smaller cluster. This shift corresponds to a narrowing of the valence band and correlates well

with the optical measurements of band gap broadening. The experimental data of the band gap

of nc-Si obey with the formula [34] below,

E

g

=E

g

(J) E

g

() =

3.4382

d10

9

+

1.1483

(d10

9

)

2

(cI) (13)

WhereEg(d) is the quantum-dot band gap as a function of radius and Eg() is the bulk band

gap.

Various authors [35] examined the impact of the grain size of nc-Si on the surface potential of

doped nc-Si TFTs and proposed that the change in both dielectric constant and band gap of nc-

Si caused by quantum size effects can largely affect on the channel surface potential in nc-Si

TFTs. The surface potential affected by the crystal size also has an effect on the tunneling

current under a given gate voltage [32].

Mao [35] calculated the surface potential with the formula below,

(E(

S

))

2

=

2q

_1+

10.4

1+_

1.38

dX10

9

]

1.3

_s

0

[N

Au

-

+

N

ST

d

s

+

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 122

1

N

Ac

-

4K1(2nk1)

3

(m

c

m

h

)

3/ 2

h

6

cxp_

L

g

()+q_

3.4382

dX10

9

+

1.1483

(dX10

9

)

2

_

k1

_kI [exp[

qq

s

k1

1 +

N

ST

k1

d

ln

1+0.5cxp

-

qq

s

+ 0.SE

g

()+0.Sq_

3.4382

dX10

9

+

1.1483

(dX10

9

)

2

_-E

TA

-qq

F0

KT

1+0.5cxp

-

0.SE

g

()+0.Sq_

3.4382

dX10

9

+

1.1483

(dX10

9

)

2

_-E

TA

-qq

F0

KT

(14)

It was proposed that the surface potential of nc-Si TFTs is largely affected when the diameter of

nc-Si is smaller than 10 nm because the corresponding dielectric constant of nc-Si largely

changes with its diameter. At the same time, the surface potential of nc-Si TFTs is little affected

by the change in the band gap when the diameter of nc-Si is smaller than 6 nm. This implies

that the effects of grain-boundary traps on the surface potential of nc-Si TFTs become more

and more important due to the rapid increase of the area of grain-boundary. Thus the change

in the surface potential due to the band gap of nc-Si can be neglected, compared to the change

caused by grain-boundary traps.

Fig. 2: Comparison of surface potential for an nc-Si TFT [35]

Mao [36] proposed that the threshold voltage in nc-Si TFTs is also strongly depends on the size

of silicon grain when the size of silicon grain is less than 20 nm. It was analyzed and proposed

that the size of silicon grain impacts on the threshold voltage weakly dependent on the active

dopant density and is mainly depends on the change in bandgap and dielectric constant due to

the quantum size effects. The threshold voltage or turn-on voltage is defined as the voltage at

which strong inversion occurs [37].Strong inversion begins at

s

2

p

2

k1

q

ln _

N

cc

-

+2

N

ST

d

n

i

_ (15)

Thus the threshold voltage is given as [36]

I

1

=

I

PB

+2

P

+

s

nc-si

s

cx

t

ox

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 123

_

2q

s

nc-si

_[N

uu

-

+

N

ST

d

(2

p

) + n

0

kI [cxp[

2qq

p

k1

1 +

N

ST

k1

d

ln _

1+cxp_-

2qq

p

+(E

i

-E

TA

F0

)

kT

]

1+cxp_-

(E

i

-E

TA

F0

)

kT

]

__

(16)

By using the assumption that the q

s

and E

E

1A

q

P0

are much larger than of kT, the

threshold voltage can be given as [36]

I

1

=I

PB

+2

P

+

s

nc-si

s

cx

t

ox

_

2q

s

nc-si

_[N

uu

-

+

N

ST

d

(2

p

) + n

0

kI_cxp[

2qq

p

k1

]_ (17)

C. Contact Resistance

The nc-Si:H TFTs made by plasma-enhanced chemical vapor deposition have higher carrier

mobilities than a-Si:H TFTs. However, the contact resistance limits the effective carrier

mobilities as it reduces the voltage drop across the channel of nc-Si TFT and distorts the

injected current [38]. Contact resistance from source to drain has been attributed to a number

of mechanisms such as current crowding [39], constant parasitic resistance,defects at the

contact interface [40] and transport through barrier [41]. Contact resistance has a vital impact

on the TFTs transconductance and on the electrical characteristics of the device.

Some of the authors [42] determined the total resistance of nc-Si TFT by the following

equations

R

101

=2R

C

+ 2R

S

+R

CH

R

CH

= p I/ (wt) (18)

RTOT is the total resistance of nc-Si TFT, RC is the contact resistance between source/ drain and

metal, RS is the resistance of source/ drain, RCH is the channel resistance, is the resistivity of

nc-Si TFT channel, W, L are the width and length of nc-Si channel and t is the thickness of nc-Si

active layer. RS and RCis low. Authors analyzed that if t is increased and grain size is increased.

Then, is decreased and causes the reduction of RCH resulting in reduction of RTOT [42]. The

reduced RCH can increase the field effect mobility and off-state current. Authors [38] proposed

that the omission of contact resistance effects can result in an incorrect extraction of the

maximum FET by a factor of 2.

Some other authors [43] measured the total resistance RTOT =VDS/ IDS, composed of contact

resistance and channel resistance, across the TFTs output terminals. And proposed that the

contact resistance R0, composed of ohmic and non-ohmic components, is inversely

proportional to channel width W. However the channel resistance, RCH =rCH (L/ W) where L is

the channel length and rCH is the channel resistance per L/ W, in the linear regime follow a

purely ohmicbehaviour.

Authors [43] estimated the ohmic contact resistance from the intercept with the Y-axis when

RTOT W (Y -axis) is plotted versus L (X-axis) and the slope denotes rCH. The results show that

the source/ drain current at VDS =10 V becomes limited by the contact resistance when the L is

less than 10 m for n-channel and less than 25 m for p-channel. Authors also proposed that

the contact resistance is strongly depends on the gate voltage VGS.

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 124

Other authors [38] estimated the non-ohmic contact resistance using the current dependent

polynomial, from which the total voltage drop across the TFT can be calculated

I

S

=I

S

R

1otuI

=I

S

|R

ChunncI

+R

Contuct

0hmc

+ R

Contuct

Non-0hmc

] =I

S

|R

ChunncI

+R

Contuct

0hmc

+

( A

I

S

-1 n

=2

)] (19)

Here, I

S

represent the measured voltage drop, Ais the constant coefficients of a polynomial, IDS

the drain-source current, R

ChunncI

the channel resistance and R

Contuct

0hmc

onJR

Contuct

Non-0hmc

the

ohmic and non-ohmic components, respectively.

Contact resistance can also be due to transport over a barrier with electronic defect states

[41].As a gate voltage is applied the defects are filled and the barrier height changes. Authors

proposed that for low trap state density the mobility saturates. The combined effect of charge

accumulation in the channel and drop in the contact resistance can increase the trapping state

density and thus the mobility.

R

C

=R

c0

.Exp j

q

3

N

t

2

t

8sC

i

k1

1

v

G

-v

th

[ (20)

VI. CONCLUSION

The recent progress in nc-Si:H TFTs has been reviewed in this paper. The different type of

materials such as a-Si:H, poly-Si and nc-Si:H which are used as an active layer for the

fabrication of thin film transistors and also the various structures and operation of TFTs were

discussed in this review paper. In case of bottom-gated nc-Si:H TFT, the device performance is

determined by the quality of bottom layers of nc-Si, where the conduction channel is formed

whereas in case of top-gated nc-Si:H TFT, the conduction channel will be formed in the highly

crystalline part of the nc-Si lm. Hence, it is expected that top-gate nc-Si TFTs render better

performance than bottom-gate devices. The main limitations of the nc-Si:H TFTs are electrical

instability and the drain leakage current. Various physical parameters like temperature, grain

size and contact resistance affects the device performance and thus affects the device

characteristics. It was also discussed that defect state creation is the dominant mechanism of

the shift in threshold voltage.

REFERENCES

[1] Snell A. J., Mackenzie K. D., Spear W.E., Le Comber P. G. Application of amorphous silicon

field effect transistors in addressable liquid crystal display panels Applied Physics Letter.

1981, 24: 357-362.

[2] Mizukami M., Inukai K., Yamagata H., Konuma T., Nishi T., Koyama J., Yamazaki S., 6-bit

Digital VGA OLED, SID International Symposium Digest Technical Papers, 2000, 31: 912-915.

[3] Finkenzeller K. RFID Handbook: Fundamentals and Applications in Contactless Smart

Cards and Identication 2nd ed. John Wiley & Sons. Ltd., West Sussex, England. 2003.

[4] Street R. A. Technology and Applications of Amorphous Silicon Springer, Berlin

Heidelberg, New York. 2000.

[5] Easton B. C., Chapman J. A., Hill O. F., Powell M. J. The plasma-enhanced deposition of

hydrogenated amorphous silicon, Vacuum. 1984, 34: 371-76.

[6] Street R. A. Hydrogenated Amorphous Silicon Cambridge, New York, USA. 1991, 237-242.

[7] Kagan C. R., Andry P. Thin-Film Transistors Marcel Dekker, Inc., New York, Basel. 2003,

35-43.

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 125

[8] Karim. K. S., Pixel Architectures for Digital Imaging Using Amorhpous Silicon Technology

[Ph.d thesis], Universitiy of Waterloo, Waterloo, 2002.

[9] Rolland A., Richard J., Kleider J. P., Mencaraglia D. Electrical properties of amorphous

silicon transistors and MIS devices: comparative study of top nitride and bottom nitride

configuration Journal of Electrochemical Society. 1993, 140: 3679-3683.

[10]Powell M. J., Berkel C. V., Franklin A. R., Deane S. C., Milne W. I. Defect pool in amorphous-

silicon thin film transistors Physical Review B. 1992, 45: 4160-4170.

[11] Gupta N., Tyagi B. P. An analytical model of the inuence of grain size on the mobility and

transfer characteristics of polysilicon thin-film transistors (TFTs) PhysicaScripta. 2005, 71:

225228.

[12] Lih J. J., Sung C. F., Li C. H., Hsiao T. H., Lee H. H. Comparison of a-Si and poly-Si for

AMOLED displays Journal of the Society for Information Display. 2004, 12: 367-371.

[13] Shin K. W., Fabrication and Analysis of Bottom Gate Nanocrystalline Silicon Thin Film

Transistors [PhD thesis], University of Waterloo, Canada, 2008.

[14] Cheng I. C., Allen S., Wagner S. Evolution of Nanocrystalline Silicon Thin Film Transistor

Channel Layers Proceedings of the 20th International Conference on Amorphous and

Microcrystalline Semiconductors, Campos do Jordao, Brazil, 2003, August 24-29, 720-724.

[15] Lee C. H., Sazonov A., Nathan A. High-mobility nanocrystalline silicon thin-lm transistors

fabricated by plasma-enhanced chemical vapor deposition Applied Physics Letters. 2005, 86:

222106-1-3.

[16] Hatzopoulos A. T., Arpatzanis N., Tassis D. H., Dimitriadis C. A., Templier F., Oudwan M.,

Kamarinos G. Effect of channel width on the electrical characteristics of

amorphous/ nanocrystalline silicon bilayer thin-film transistors IEEE Transaction on Electron

Devices. 2007, 54: 1265-1269.

[17] Kasouit S., Cabarrocas P. R. I., Vanderhaghen R., Bonnassieux Y., Elyaakoubi M., French I. D.

Eects of Grain Size and Plasma-Induced Modication of the Dielectric on the Mobility and

Stability of Bottom Gate Microcrystalline Silicon TFTs Proceedings of the 20th International

Conference on Amorphous and Microcrystalline Semiconductors, Campos do Jordao, Brazil,

2003, August 24-29, 369-373.

[18] Kuo Y. Thin Film Transistors: Materials and Process 2nd vol., 1st ed., Kluwer Academic,

New York, USA, 2004, 120-126.

[19] Grant D. J., Physics and Modelling of Nanocrystalline Silicon Thin-Film Transistors [PhD

thesis], University of Waterloo, Canada, 2003.

[20] Powell M. J., Berkel C. V., Franklin A. R., Deane S.C., and Milne W.I., Defect pool in

amorphous-silicon thin film transistors Physical Review B. 1992, 454: 4160-70.

[21] Stannowski B. and Schropp R. E. I., Hot-wire amorphous silicon thin film transistors,

Thin Solid Films. 2001, 383: 125-128.

[22] Jackson W. B., Marshall J. M., and Moyer M. D., Role of hydrogen in the formation of

metastable defects in hydrogenated amorphous silicon, Physical Review B. 1989, 39:1164-

1179.

[23] Powell M. J., Berkel C. V., and Hughes J. R., Time and temperature dependence of

instability mechanisms in amorphous silicon thin-lm transistors, Applied Physics Letters.

1989, 54:1323-1325.

[24] Sze. S.M. Physics of semiconductor devices 2nd ed. Wiley, New York, 1981.

[25] Lee H. J., Sazonov A., Nathan A. Leakage current mechanisms in top-gate nanocrystalline

silicon thin lm transistors Applied Physics Letter. 2008, 92:083509-1-3.

[26] Esmaeili-Rad M. R., Sazonov A., Nathan A. Analysis of the off current in nanocrystalline

silicon bottom-gate thin-film transistors Journal of Applied Physics. 2008, 103: 074502-1-6.

[27] Nathan V. and Das N. C., Gate-induced leakage current in MOS devices IEEE Trans.

Electron Devices, 1993,40:18881890.

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 126

[28] Hatzopoulos A. T., Arpatzanis N., Tassis D. H., Dimitriadis C.A., Oudwan M., Templier F., and

Kamarinos G., Study of the drain leakage current in bottom-gated nanocrystalline silicon thin-

film transistors by conduction and low-frequency noise measurements IEEE Trans. Electron

Devices, 2007, 54:1076-1082.

[29] Esmaeili-Rad M. R., Sazonov A., Nathan A. Absence of defect state creation in

nanocrystalline silicon thin lm transistors deduced from constant current stress

measurements Applied Physics Letter. 2007, 91: 113511-1-3.

[30] Libsch F. R. and Kanicki J., Bias-stress-induced stretched-exponential time dependence of

charge injection and trapping in amorphous thin-lm transistors, Applied Physics Letters.

1993,62: 1286-1288.

[31] Bauza M., Ahnood A., Li F. M., Vygranenko Y., Esmaeili-Rad M. R, Chaji G., Sazonov A.,

Robertson J., Milne W. I., and Nathan A, Photo-induced instability of Nanocrystalline TFTs

Journal of Display Technology. 2010, 6: 589-591.

[32] Mao L. F., Effect of the size of silicon grain on the gate-leakage current in nanocrystalline

silicon thin film transistors Journal of Vacuum Science & Technology B. 2010, 28: 460-465.

[33] Wang L. W., Zunger A., "Dielectric constants of silicon quantum dots", Physical Review

Leter. 1994, 73:1039-1042.

[34] Peng X., Ganti S., Sharma P., Alizadeh A., Nayak S., and Kumar S., Novel Scaling Laws for

Band Gaps of Quantum Dots Journal of Computational and Theoretical Nanoscience. 2005,

2:469472.

[35] Mao L.F., The quantum size effects on the surface potential of Nanocrystalline silicon thin

film transistors Thin Film Solid. 2010, 518: 3396-3401.

[36] Mao L. F, Quantum size impacts on the threshold voltage in nanocrystalline silicon thin

lm transistors Microelectronics Reliability Elsevier, 2013, xx:1-5.

[37] Sze S.M., Kwok k. N. Physics of Semiconductor devices, 3rd ed. John Wiley, New Jersey,

2007.

[38] Ahnood A., Li F., Ghaffarzadeh K., Esmaeili-Rad M. R., Nathan A., Sazonov A., Servati P.

Non-ohmic contact resistance and eld-effect mobility in nanocrystalline silicon thin lm

transistors Applied Physics Letter. 2008, 93: 163503-1-3.

[39] Richards T. J. and Sirringhaus H., Analysis of the contact resistance in staggered, top-gate

organic field-effect transistors, Journal of Applied Physics, 2007, 102:094510.

[40] Street R. A. and Salleo A., Contact effects in polymer transistors, Applied Physics Letters,

2002, 81: 2887.

[41] Vinciguerra V., Rosa M. L., Nicolosi D., Sicurella G., and Occhipinti L., Modeling the gate

bias dependence of contact resistance in staggered polycrystalline organic thin film

transistors, Organic Electronics, 2009, 10:1074-1081.

[42] Kang D. W., Park J. H, Han S. M., and Han M. K. The Effects of Nanocrystalline Silicon Thin

Film Thickness on Top Gate Nanocrystalline Silicon Thin Film Transistor Fabricated at 180C

Journal of Semiconductor Technology and Science, 2008, 8:111-114.

[43] Cheng I. C., Wagner S. and Sauvain E. V. Contact Resistance in Nanocrystalline Silicon

Thin-Film Transistors IEEE Transaction on Electron Devices.2008, 5:373-377.

BIOGRAPHY

Prachi Sharma is currently pursuing PhD from Department of Electrical &

Electronics Engineering, Birla Institute of Technology and SciencePilani,

Rajasthan, India. She received M-Tech in VLSI Design in 2011 from Banasthali

University, Rajasthan and B-Tech in Electronics and Telecommunication in

2009 from UPTU, Lucknow. Her research interests are Semiconductor Device

Modelling, VLSI Design, Microelectronics.

International Journal of Electronics and Communication Engineering & Technology (IJECET),

ISSN 0976 6464(Print), ISSN 0976 6472(Online), Special Issue (November, 2013), IAEME

International Conference on Communication Systems (ICCS-2013) October 18-20, 2013

B K Birla Institute of Engineering & Technology (BKBIET), Pilani, India Page 127

Dr. Navneet Gupta obtained M.Sc. (Physics-Electronics) in 1995 from H.N.B

Garhwal Central University (HNBGU), Srinagar, India with first rank in the

University. He received M.Tech in Materials Technology in 1998 from Indian

Institute of Technology (IIT-BHU) (formerly IT-BHU). He did his Ph.D. in the

field of Semiconductor Devices in 2005 from HNBGU. Presently, he is Assistant

Professor and Convenor-Departmental Research Committee in Electrical and

Electronics Engineering Department, Birla Institute of Technology and

Science, Pilani, (BITS-Pilani) Rajasthan, India. He has guided 1 Ph.D. student and is currently

guiding 4 Ph.D. candidates. He is on doctoral advisory committee for 6 Ph.D. students. He

completed 2 sponsored research projects from UGC and DST. His research interests include

Semiconductor Device Modelling, RF-MEMS, Material Selection and Antenna Design. He is life

member of several international and national professional bodies. He has over 50 research

publications (of which 21 are in reputed peer reviewed international and national journals

with good impact factors, and 29 in conference proceedings.). He has published six books in the

areas of engineering physics and electronics engineering. He received the Bharat Jyoti Award

in 2011 by IIFS, New Delhi, India, DST Young Scientist Award (Fast track Scheme) in Physical

Sciences in 2007 and Gold Medal in M.Sc. His biography is included in Marquis Who's Who in

World and Marquis Who's Who in Science and Engineering. He is expert reviewer of over 5

International Journals. He reviewed three books of Oxford University Press, Pearson Education

and Tata McGraw Hill publishers.

You might also like

- A Study On The Reasons For Transgender To Become EntrepreneursDocument7 pagesA Study On The Reasons For Transgender To Become EntrepreneursIAEME PublicationNo ratings yet

- Determinants Affecting The User's Intention To Use Mobile Banking ApplicationsDocument8 pagesDeterminants Affecting The User's Intention To Use Mobile Banking ApplicationsIAEME PublicationNo ratings yet

- Visualising Aging Parents & Their Close Carers Life Journey in Aging EconomyDocument4 pagesVisualising Aging Parents & Their Close Carers Life Journey in Aging EconomyIAEME PublicationNo ratings yet

- Influence of Talent Management Practices On Organizational Performance A Study With Reference To It Sector in ChennaiDocument16 pagesInfluence of Talent Management Practices On Organizational Performance A Study With Reference To It Sector in ChennaiIAEME PublicationNo ratings yet

- Modeling and Analysis of Surface Roughness and White Later Thickness in Wire-Electric Discharge Turning Process Through Response Surface MethodologyDocument14 pagesModeling and Analysis of Surface Roughness and White Later Thickness in Wire-Electric Discharge Turning Process Through Response Surface MethodologyIAEME PublicationNo ratings yet

- Attrition in The It Industry During Covid-19 Pandemic: Linking Emotional Intelligence and Talent Management ProcessesDocument15 pagesAttrition in The It Industry During Covid-19 Pandemic: Linking Emotional Intelligence and Talent Management ProcessesIAEME PublicationNo ratings yet

- Impact of Emotional Intelligence On Human Resource Management Practices Among The Remote Working It EmployeesDocument10 pagesImpact of Emotional Intelligence On Human Resource Management Practices Among The Remote Working It EmployeesIAEME PublicationNo ratings yet

- Analyse The User Predilection On Gpay and Phonepe For Digital TransactionsDocument7 pagesAnalyse The User Predilection On Gpay and Phonepe For Digital TransactionsIAEME PublicationNo ratings yet

- Broad Unexposed Skills of Transgender EntrepreneursDocument8 pagesBroad Unexposed Skills of Transgender EntrepreneursIAEME PublicationNo ratings yet

- Voice Based Atm For Visually Impaired Using ArduinoDocument7 pagesVoice Based Atm For Visually Impaired Using ArduinoIAEME PublicationNo ratings yet

- A Study On The Impact of Organizational Culture On The Effectiveness of Performance Management Systems in Healthcare Organizations at ThanjavurDocument7 pagesA Study On The Impact of Organizational Culture On The Effectiveness of Performance Management Systems in Healthcare Organizations at ThanjavurIAEME PublicationNo ratings yet

- Gandhi On Non-Violent PoliceDocument8 pagesGandhi On Non-Violent PoliceIAEME PublicationNo ratings yet

- A Study On Talent Management and Its Impact On Employee Retention in Selected It Organizations in ChennaiDocument16 pagesA Study On Talent Management and Its Impact On Employee Retention in Selected It Organizations in ChennaiIAEME PublicationNo ratings yet

- A Study of Various Types of Loans of Selected Public and Private Sector Banks With Reference To Npa in State HaryanaDocument9 pagesA Study of Various Types of Loans of Selected Public and Private Sector Banks With Reference To Npa in State HaryanaIAEME PublicationNo ratings yet

- A Multiple - Channel Queuing Models On Fuzzy EnvironmentDocument13 pagesA Multiple - Channel Queuing Models On Fuzzy EnvironmentIAEME PublicationNo ratings yet

- EXPERIMENTAL STUDY OF MECHANICAL AND TRIBOLOGICAL RELATION OF NYLON/BaSO4 POLYMER COMPOSITESDocument9 pagesEXPERIMENTAL STUDY OF MECHANICAL AND TRIBOLOGICAL RELATION OF NYLON/BaSO4 POLYMER COMPOSITESIAEME PublicationNo ratings yet

- Various Fuzzy Numbers and Their Various Ranking ApproachesDocument10 pagesVarious Fuzzy Numbers and Their Various Ranking ApproachesIAEME PublicationNo ratings yet

- Role of Social Entrepreneurship in Rural Development of India - Problems and ChallengesDocument18 pagesRole of Social Entrepreneurship in Rural Development of India - Problems and ChallengesIAEME PublicationNo ratings yet

- Application of Frugal Approach For Productivity Improvement - A Case Study of Mahindra and Mahindra LTDDocument19 pagesApplication of Frugal Approach For Productivity Improvement - A Case Study of Mahindra and Mahindra LTDIAEME PublicationNo ratings yet

- Optimal Reconfiguration of Power Distribution Radial Network Using Hybrid Meta-Heuristic AlgorithmsDocument13 pagesOptimal Reconfiguration of Power Distribution Radial Network Using Hybrid Meta-Heuristic AlgorithmsIAEME PublicationNo ratings yet

- Knowledge Self-Efficacy and Research Collaboration Towards Knowledge Sharing: The Moderating Effect of Employee CommitmentDocument8 pagesKnowledge Self-Efficacy and Research Collaboration Towards Knowledge Sharing: The Moderating Effect of Employee CommitmentIAEME PublicationNo ratings yet

- A Proficient Minimum-Routine Reliable Recovery Line Accumulation Scheme For Non-Deterministic Mobile Distributed FrameworksDocument10 pagesA Proficient Minimum-Routine Reliable Recovery Line Accumulation Scheme For Non-Deterministic Mobile Distributed FrameworksIAEME PublicationNo ratings yet

- Quality of Work-Life On Employee Retention and Job Satisfaction: The Moderating Role of Job PerformanceDocument7 pagesQuality of Work-Life On Employee Retention and Job Satisfaction: The Moderating Role of Job PerformanceIAEME PublicationNo ratings yet

- Dealing With Recurrent Terminates in Orchestrated Reliable Recovery Line Accumulation Algorithms For Faulttolerant Mobile Distributed SystemsDocument8 pagesDealing With Recurrent Terminates in Orchestrated Reliable Recovery Line Accumulation Algorithms For Faulttolerant Mobile Distributed SystemsIAEME PublicationNo ratings yet

- Financial Literacy On Investment Performance: The Mediating Effect of Big-Five Personality Traits ModelDocument9 pagesFinancial Literacy On Investment Performance: The Mediating Effect of Big-Five Personality Traits ModelIAEME PublicationNo ratings yet

- Analysis On Machine Cell Recognition and Detaching From Neural SystemsDocument9 pagesAnalysis On Machine Cell Recognition and Detaching From Neural SystemsIAEME PublicationNo ratings yet

- Analysis of Fuzzy Inference System Based Interline Power Flow Controller For Power System With Wind Energy Conversion System During Faulted ConditionsDocument13 pagesAnalysis of Fuzzy Inference System Based Interline Power Flow Controller For Power System With Wind Energy Conversion System During Faulted ConditionsIAEME PublicationNo ratings yet

- Moderating Effect of Job Satisfaction On Turnover Intention and Stress Burnout Among Employees in The Information Technology SectorDocument7 pagesModerating Effect of Job Satisfaction On Turnover Intention and Stress Burnout Among Employees in The Information Technology SectorIAEME PublicationNo ratings yet

- Prediction of Average Total Project Duration Using Artificial Neural Networks, Fuzzy Logic, and Regression ModelsDocument13 pagesPrediction of Average Total Project Duration Using Artificial Neural Networks, Fuzzy Logic, and Regression ModelsIAEME PublicationNo ratings yet

- A Review of Particle Swarm Optimization (Pso) AlgorithmDocument26 pagesA Review of Particle Swarm Optimization (Pso) AlgorithmIAEME PublicationNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Magna: BUZ900 BUZ901Document4 pagesMagna: BUZ900 BUZ901rory957No ratings yet

- Transistor and MOSFET Multiple Choice QuestionsDocument23 pagesTransistor and MOSFET Multiple Choice Questionspoo235No ratings yet

- Digital System ImplementationDocument37 pagesDigital System ImplementationfernandofortunaNo ratings yet

- Field Effect Transistor PDFDocument2 pagesField Effect Transistor PDFChristinaNo ratings yet

- Computer Architecture A Quantitative Approach 5th Edition Hennessy Solutions ManualDocument7 pagesComputer Architecture A Quantitative Approach 5th Edition Hennessy Solutions Manualheidiwatsonwcjponqkai100% (14)

- Investigatory ProjectDocument16 pagesInvestigatory ProjectsuhaybNo ratings yet

- Gate Array Based DesignDocument6 pagesGate Array Based DesignSubir MaityNo ratings yet

- CMOS Process Technology OverviewDocument23 pagesCMOS Process Technology OverviewDikshaNo ratings yet

- Karakterisasi Dan Simulasi Dioda PN Mempergunakan Alat Uji Otomatis Berbasis Mikrokontroler Atmega8ADocument7 pagesKarakterisasi Dan Simulasi Dioda PN Mempergunakan Alat Uji Otomatis Berbasis Mikrokontroler Atmega8Aagel ridhoNo ratings yet

- Irf840 PDFDocument8 pagesIrf840 PDFAnonymous AssOOhqigNo ratings yet

- Footprint Expert Surface Mount FamiliesDocument39 pagesFootprint Expert Surface Mount FamiliesErkanNo ratings yet

- Silicon NPN Power Transistors: Inchange Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Inchange Semiconductor Product SpecificationdenitoNo ratings yet

- Aim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Document3 pagesAim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Jeyakumar VenugopalNo ratings yet

- An Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI TechnologyDocument4 pagesAn Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI Technologyapi-19668941No ratings yet

- Ultra Low Output Voltage Linear N-FET ControllerDocument1 pageUltra Low Output Voltage Linear N-FET ControllerDaniel Norberto DemariaNo ratings yet

- Comp ArchitectureDocument21 pagesComp ArchitectureHariPrasanth GovindarajuNo ratings yet

- Fast Recovery Diodes & Schottky DiodesDocument3 pagesFast Recovery Diodes & Schottky DiodesDan Jeric Arcega RustiaNo ratings yet

- Introduction To The Special Section On The 2018 IEEE BCICTS ConferenceDocument2 pagesIntroduction To The Special Section On The 2018 IEEE BCICTS ConferenceMarian Bogdan NeagoeNo ratings yet

- P3057LCG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect TransistorDocument4 pagesP3057LCG Niko-Sem: N-Channel Logic Level Enhancement Mode Field Effect Transistorlepicane7No ratings yet

- D1415 SchemacticDocument4 pagesD1415 SchemacticNghiaNguyentrungNo ratings yet

- 收到IC&燒錄資料登記表Document79 pages收到IC&燒錄資料登記表Yu FelixNo ratings yet

- Integrated Circuit Fabrication Process Study Notes For ECEDocument9 pagesIntegrated Circuit Fabrication Process Study Notes For ECEkrishnaav100% (1)

- Irf 5302Document6 pagesIrf 5302Yessenia PerezNo ratings yet

- Tutorials in Power ElectronicsDocument66 pagesTutorials in Power ElectronicsAbdullah Al AsikNo ratings yet

- Silicon NPN Power Transistor 2SD551: DescriptionDocument2 pagesSilicon NPN Power Transistor 2SD551: DescriptionOndalis LobaynaNo ratings yet

- Toshiba IGBT BCE0010 - CatalogDocument16 pagesToshiba IGBT BCE0010 - CatalogRosendo PeñaNo ratings yet

- Isc N-Channel MOSFET Transistor: IRF3205 IIRF3205Document2 pagesIsc N-Channel MOSFET Transistor: IRF3205 IIRF3205diegooliveiraEENo ratings yet

- Atria Institute's Silicon on Plastic TechnologyDocument12 pagesAtria Institute's Silicon on Plastic TechnologyManjunath Maddy100% (3)

- 320 Lecture 11Document8 pages320 Lecture 11keyboard2014No ratings yet

- GT45F122 PDFDocument16 pagesGT45F122 PDFSinkdna AmdNo ratings yet