Professional Documents

Culture Documents

DS1307 PDF

Uploaded by

dafegokOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DS1307 PDF

Uploaded by

dafegokCopyright:

Available Formats

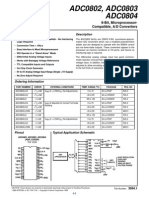

DS1307 64 x 8, Serial, I2C Real-Time Clock

GENERAL DESCRIPTION

The DS1307 serial real-time clock (RTC) is a lowpower, full binary-coded decimal (BCD) clock/calendar plus 56 bytes of NV SRAM. Address and data are 2 transferred serially through an I C, bidirectional bus. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The end of the month date is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12hour format with AM/PM indicator. The DS1307 has a built-in power-sense circuit that detects power failures and automatically switches to the backup supply. Timekeeping operation continues while the part operates from the backup supply.

FEATURES

Real-Time Clock (RTC) Counts Seconds, Minutes, Hours, Date of the Month, Month, Day of the week, and Year with Leap-Year Compensation Valid Up to 2100 56-Byte, Battery-Backed, General-Purpose RAM with Unlimited Writes 2 I C Serial Interface Programmable Square-Wave Output Signal Automatic Power-Fail Detect and Switch Circuitry Consumes Less than 500nA in Battery-Backup Mode with Oscillator Running Optional Industrial Temperature Range: -40C to +85C Available in 8-Pin Plastic DIP or SO Underwriters Laboratories (UL) Recognized

TYPICAL OPERATING CIRCUIT

VCC CRYSTAL VCC RPU RPU X1 X2 SCL CPU SDA GND

RPU = tr/Cb

VCC

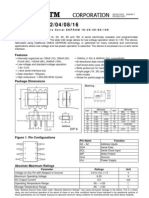

PIN CONFIGURATIONS

TOP VIEW

X1 X2

VCC SQW/OUT

VCC SQW/OUT SCL SDA SO (150 mils)

X1 X2 VBAT GND

VCC SQW/OUT SCL SDA

VBAT GND

PDIP (300 mils)

DS130

VBAT

ORDERING INFORMATION

PART DS1307+ DS1307N+ DS1307Z+ DS1307ZN+ DS1307Z+T&R DS1307ZN+T&R TEMP RANGE 0C to +70C -40C to +85C 0C to +70C -40C to +85C 0C to +70C -40C to +85C VOLTAGE (V) 5.0 5.0 5.0 5.0 5.0 5.0 PIN-PACKAGE 8 PDIP (300 mils) 8 PDIP (300 mils) 8 SO (150 mils) 8 SO (150 mils) 8 SO (150 mils) Tape and Reel 8 SO (150 mils) Tape and Reel TOP MARK* DS1307 DS1307N DS1307 DS1307N DS1307 DS1307N

+Denotes a lead-free/RoHS-compliant package. *A + anywhere on the top mark indicates a lead-free package. An N anywhere on the top mark indicates an industrial temperature range device.

1 of 14

REV: 100208

DS1307 64 x 8, Serial, I C Real-Time Clock

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to Ground ................................................................................ -0.5V to +7.0V Operating Temperature Range (Noncondensing) Commercial .......................................................................................................................... 0C to +70C Industrial ............................................................................................................................ -40C to +85C Storage Temperature Range......................................................................................................... -55C to +125C Soldering Temperature (DIP, leads) .................................................................................... +260C for 10 seconds Soldering Temperature (surface mount)...Refer to the JPC/JEDEC J-STD-020 Specification.

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

RECOMMENDED DC OPERATING CONDITIONS

(TA = 0C to +70C, TA = -40C to +85C.) (Notes 1, 2)

PARAMETER Supply Voltage Logic 1 Input Logic 0 Input VBAT Battery Voltage SYMBOL VCC VIH VIL VBAT CONDITIONS MIN 4.5 2.2 -0.3 2.0 3 TYP 5.0 MAX 5.5 VCC + 0.3 +0.8 3.5 UNITS V V V V

DC ELECTRICAL CHARACTERISTICS

(VCC = 4.5V to 5.5V; TA = 0C to +70C, TA = -40C to +85C.) (Notes 1, 2)

PARAMETER Input Leakage (SCL) I/O Leakage (SDA, SQW/OUT) Logic 0 Output (IOL = 5mA) Active Supply Current (f SCL = 100kHz) Standby Current VBAT Leakage Current Power-Fail Voltage (VBAT = 3.0V) SYMBOL ILI ILO VOL ICCA ICCS IBATLKG VPF 1.216 x VBAT (Note 3) 5 1.25 x VBAT CONDITIONS MIN -1 -1 TYP MAX 1 1 0.4 1.5 200 50 1.284 x VBAT UNITS A A V mA A nA V

DC ELECTRICAL CHARACTERISTICS

(VCC = 0V, VBAT = 3.0V; TA = 0C to +70C, TA = -40C to +85C.) (Notes 1, 2)

PARAMETER VBAT Current (OSC ON); SQW/OUT OFF VBAT Current (OSC ON); SQW/OUT ON (32kHz) VBAT Data-Retention Current (Oscillator Off) SYMBOL IBAT1 IBAT2 IBATDR CONDITIONS MIN TYP 300 480 10 MAX 500 800 100 UNITS nA nA nA

WARNING: Negative undershoots below -0.3V while the part is in battery-backed mode may cause loss of data.

2 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

AC ELECTRICAL CHARACTERISTICS

(VCC = 4.5V to 5.5V; TA = 0C to +70C, TA = -40C to +85C.)

PARAMETER SCL Clock Frequency Bus Free Time Between a STOP and START Condition Hold Time (Repeated) START Condition LOW Period of SCL Clock HIGH Period of SCL Clock Setup Time for a Repeated START Condition Data Hold Time Data Setup Time Rise Time of Both SDA and SCL Signals Fall Time of Both SDA and SCL Signals Setup Time for STOP Condition SYMBOL f SCL tBUF tHD:STA tLOW tHIGH tSU:STA tHD:DAT tSU:DAT tR tF tSU:STO 4.7 (Notes 5, 6) (Note 4) CONDITIONS MIN 0 4.7 4.0 4.7 4.0 4.7 0 250 1000 300 TYP MAX 100 UNITS kHz s s s s s s ns ns ns s

CAPACITANCE

(TA = +25C)

PARAMETER Pin Capacitance (SDA, SCL) Capacitance Load for Each Bus Line SYMBOL CI/O CB (Note 7) CONDITIONS MIN TYP MAX 10 400 UNITS pF pF

Note 1: Note 2: Note 3: Note 4: Note 5: Note 6: Note 7:

All voltages are referenced to ground. Limits at -40C are guaranteed by design and are not production tested. ICCS specified with VCC = 5.0V and SDA, SCL = 5.0V. After this period, the first clock pulse is generated. A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the VIH(MIN) of the SCL signal) to bridge the undefined region of the falling edge of SCL. The maximum tHD:DAT only has to be met if the device does not stretch the LOW period (tLOW ) of the SCL signal. CBtotal capacitance of one bus line in pF.

3 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

TIMING DIAGRAM

SDA tBUF tLOW tHD:STA tR tF

SCL t HD:STA STOP START tHD:DAT tHIGH

SU:DAT

tSU:STA tSU:STO REPEATED START

Figure 1. Block Diagram

SQW/OUT X1 1Hz/4.096kHz/8.192kHz/32.768kHz

CL

MUX/ BUFFER

1Hz X2

CL

Oscillator and divider CONTROL LOGIC POWER CONTROL

RAM (56 X 8)

VCC GND VBAT

DS1307

SCL SDA SERIAL BUS INTERFACE AND ADDRESS REGISTER

CLOCK, CALENDAR, AND CONTROL REGISTERS

USER BUFFER (7 BYTES)

4 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

TYPICAL OPERATING CHARACTERISTICS

(VCC = 5.0V, TA = +25C, unless otherwise noted.)

ICCS vs. VCC

IBAT vs. VBAT

400

SQW=32kHz

V BAT=3.0V

V CC = 0V

120 110 100 90

350

SUPPLY CURRENT (nA

SUPPLY CURRENT (uA

80 70 60 50 40 30 20 10 0 1.0 2.0 3.0 VCC (V) 4.0 5.0

300

250

SQW off

200 150 100 2.0 2.5 VBACKUP (V) 3.0 3.5

IBAT vs. Temperature

325.0

V CC=0V, V BAT=3.0

SQW/OUT vs. Supply Voltage

32768.5 32768.4

SQW=32kHz

SUPPLY CURRENT (nA

275.0

FREQUENCY (Hz)

SQW off

32768.3 32768.2 32768.1 32768 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 Supply (V)

225.0

175.0 -40 -20 0 20 40 60 80 TEMPERATURE (C)

5 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

PIN DESCRIPTION

PIN 1 NAME X1 FUNCTION Connections for Standard 32.768kHz Quartz Crystal. The internal oscillator circuitry is designed for operation with a crystal having a specified load capacitance (CL) of 12.5pF. X1 is the input to the oscillator and can optionally be connected to an external 32.768kHz oscillator. The output of the internal oscillator, X2, is floated if an external oscillator is connected to X1. Note: For more information on crystal selection and crystal layout considerations, refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks. Backup Supply Input for Any Standard 3V Lithium Cell or Other Energy Source. Battery voltage must be held between the minimum and maximum limits for proper operation. Diodes in series between the battery and the VBAT pin may prevent proper operation. If a backup supply is not required, VBAT must be grounded. The nominal power-fail trip point (VPF) voltage at which access to the RTC and user RAM is denied is set by the internal circuitry as 1.25 x VBAT nominal. A lithium battery with 48mAh or greater will back up the DS1307 for more than 10 years in the absence of power at +25C. UL recognized to ensure against reverse charging current when used with a lithium battery. Go to: www.maxim-ic.com/qa/info/ul/. 4 5 GND SDA Ground Serial Data Input/Output. SDA is the data input/output for the I2C serial interface. The SDA pin is open drain and requires an external pullup resistor. The pullup voltage can be up to 5.5V regardless of the voltage on VCC. 2 Serial Clock Input. SCL is the clock input for the I C interface and is used to synchronize data movement on the serial interface. The pullup voltage can be up to 5.5V regardless of the voltage on VCC. Square Wave/Output Driver. When enabled, the SQWE bit set to 1, the SQW/OUT pin outputs one of four square-wave frequencies (1Hz, 4kHz, 8kHz, 32kHz). The SQW/OUT pin is open drain and requires an external pullup resistor. SQW/OUT operates with either VCC or VBAT applied. The pullup voltage can be up to 5.5V regardless of the voltage on VCC. If not used, this pin can be left floating. Primary Power Supply. When voltage is applied within normal limits, the device is fully accessible and data can be written and read. When a backup supply is connected to the device and VCC is below VTP, read and writes are inhibited. However, the timekeeping function continues unaffected by the lower input voltage.

X2

VBAT

SCL

SQW/OUT

VCC

DETAILED DESCRIPTION

The DS1307 is a low-power clock/calendar with 56 bytes of battery-backed SRAM. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The DS1307 operates as a slave 2 device on the I C bus. Access is obtained by implementing a START condition and providing a device identification code followed by a register address. Subsequent registers can be accessed sequentially until a STOP condition is executed. When VCC falls below 1.25 x VBAT, the device terminates an access in progress and resets the device address counter. Inputs to the device will not be recognized at this time to prevent erroneous data from being written to the device from an out-of-tolerance system. When VCC falls below VBAT, the device switches into a lowcurrent battery-backup mode. Upon power-up, the device switches from battery to VCC when VCC is greater than VBAT +0.2V and recognizes inputs when VCC is greater than 1.25 x VBAT. The block diagram in Figure 1 shows the main elements of the serial RTC.

6 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

OSCILLATOR CIRCUIT

The DS1307 uses an external 32.768kHz crystal. The oscillator circuit does not require any external resistors or capacitors to operate. Table 1 specifies several crystal parameters for the external crystal. Figure 1 shows a functional schematic of the oscillator circuit. If using a crystal with the specified characteristics, the startup time is usually less than one second.

CLOCK ACCURACY

The accuracy of the clock is dependent upon the accuracy of the crystal and the accuracy of the match between the capacitive load of the oscillator circuit and the capacitive load for which the crystal was trimmed. Additional error will be added by crystal frequency drift caused by temperature shifts. External circuit noise coupled into the oscillator circuit may result in the clock running fast. Refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks for detailed information.

Table 1. Crystal Specifications*

PARAMETER Nominal Frequency Series Resistance Load Capacitance SYMBOL fO ESR CL MIN TYP 32.768 12.5 MAX 45 UNITS kHz k pF

*The crystal, traces, and crystal input pins should be isolated from RF generating signals. Refer to Application Note 58: Crystal Considerations for Dallas Real-Time Clocks for additional specifications.

Figure 2. Recommended Layout for Crystal

LOCAL GROUND PLANE (LAYER 2)

X1 CRYSTAL X2

GND

NOTE: AVOID ROUTING SIGNAL LINES IN THE CROSSHATCHED AREA (UPPER LEFT QUADRANT) OF THE PACKAGE UNLESS THERE IS A GROUND PLANE BETWEEN THE SIGNAL LINE AND THE DEVICE PACKAGE.

RTC AND RAM ADDRESS MAP

Table 2 shows the address map for the DS1307 RTC and RAM registers. The RTC registers are located in address locations 00h to 07h. The RAM registers are located in address locations 08h to 3Fh. During a multibyte access, when the address pointer reaches 3Fh, the end of RAM space, it wraps around to location 00h, the beginning of the clock space.

7 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

CLOCK AND CALENDAR

The time and calendar information is obtained by reading the appropriate register bytes. Table 2 shows the RTC registers. The time and calendar are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in the BCD format. The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on.) Illogical time and date entries result in undefined operation. Bit 7 of Register 0 is the clock halt (CH) bit. When this bit is set to 1, the oscillator is disabled. When cleared to 0, the oscillator is enabled. On first application of power to the device the time and date registers are typically reset to 01/01/00 01 00:00:00 (MM/DD/YY DOW HH:MM:SS). The CH bit in the seconds register will be set to a 1. The clock can be halted whenever the timekeeping functions are not required, which minimizes current (IBATDR). The DS1307 can be run in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12-hour or 24-hour mode-select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit (20 to 23 hours). The hours value must be re-entered whenever the 12/24-hour mode bit is changed. When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the 2 internal registers on any I C START. The time information is read from these secondary registers while the clock continues to run. This eliminates the need to re-read the registers in case the internal registers update during a 2 read. The divider chain is reset whenever the seconds register is written. Write transfers occur on the I C acknowledge from the DS1307. Once the divider chain is reset, to avoid rollover issues, the remaining time and date registers must be written within one second.

Table 2. Timekeeper Registers

ADDRESS 00h 01h 02h 03h 04h 05h 06h 07h 08h3Fh

0 = Always reads back as 0.

BIT 7 CH 0 0 0 0 0 OUT

BIT 6

BIT 5 BIT 4 10 Seconds 10 Minutes 10 12 Hour 10 Hour PM/ 24 AM 0 0 0 0 10 Date 10 0 0 Month 10 Year 0 0 SQWE

BIT 3

BIT 2 BIT 1 Seconds Minutes Hours

BIT 0

FUNCTION Seconds Minutes Hours Day Date Month

RANGE 0059 0059 112 +AM/PM 0023 0107 0131 0112 0099 00hFFh

DAY Date Month

Year RS1

RS0

Year Control RAM 56 x 8

8 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

CONTROL REGISTER

The DS1307 control register is used to control the operation of the SQW/OUT pin. BIT 7 OUT BIT 6 0 BIT 5 0 BIT 4 SQWE BIT 3 0 BIT 2 0 BIT 1 RS1 BIT 0 RS0

Bit 7: Output Control (OUT). This bit controls the output level of the SQW/OUT pin when the square-wave output is disabled. If SQWE = 0, the logic level on the SQW/OUT pin is 1 if OUT = 1 and is 0 if OUT = 0. On initial application of power to the device, this bit is typically set to a 0. Bit 4: Square-Wave Enable (SQWE). This bit, when set to logic 1, enables the oscillator output. The frequency of the square-wave output depends upon the value of the RS0 and RS1 bits. With the square-wave output set to 1Hz, the clock registers update on the falling edge of the square wave. On initial application of power to the device, this bit is typically set to a 0. Bits 1 and 0: Rate Select (RS[1:0]). These bits control the frequency of the square-wave output when the squarewave output has been enabled. The following table lists the square-wave frequencies that can be selected with the RS bits. On initial application of power to the device, these bits are typically set to a 1. RS1 0 0 1 1 X X RS0 0 1 0 1 X X SQW/OUT OUTPUT 1Hz 4.096kHz 8.192kHz 32.768kHz 0 1 SQWE 1 1 1 1 0 0 OUT X X X X 0 1

9 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

The DS1307 supports the I2C protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are referred to as slaves. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DS1307 2 operates as a slave on the I C bus.

2 Figures 3, 4, and 5 detail how data is transferred on the I C bus.

I2C DATA BUS

Data transfer can be initiated only when the bus is not busy. During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is high will be interpreted as control signals.

Accordingly, the following bus conditions have been defined: Bus not busy: Both data and clock lines remain HIGH. START data transfer: A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition. STOP data transfer: A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition. Data valid: The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data. Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit. Within the 2 I C bus specifications a standard mode (100kHz clock rate) and a fast mode (400kHz clock rate) are defined. The DS1307 operates in the standard mode (100kHz) only. Acknowledge: Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit. A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

10 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

Figure 3. Data Transfer on I2C Serial Bus

SDA

MSB

R/W DIRECTION BIT

ACKNOWLEDGEMENT SIGNAL FROM RECEIVER

ACKNOWLEDGEMENT SIGNAL FROM RECEIVER

SCL 1 START CONDITION 2 6 7 8 9 ACK 1 2 3-7 8 9 ACK REPEATED IF MORE BYTES ARE TRANSFERED STOP CONDITION OR REPEATED START CONDITION

Depending upon the state of the R/W bit, two types of data transfer are possible: 1. Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first. 2. Data transfer from a slave transmitter to a master receiver. The first byte (the slave address) is transmitted by the master. The slave then returns an acknowledge bit. This is followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a not acknowledge is returned. The master device generates all the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released. Data is transferred with the most significant bit (MSB) first.

11 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock The DS1307 can operate in the following two modes: 1. Slave Receiver Mode (Write Mode): Serial data and clock are received through SDA and SCL. After each byte is received an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Hardware performs address recognition after reception of the slave address and direction bit (see Figure 4). The slave address byte is the first byte received after the master generates the START condition. The slave address byte contains the 7-bit DS1307 address, which is 1101000, followed by the direction bit (R/W), which for a write is 0. After receiving and decoding the slave address byte, the DS1307 outputs an acknowledge on SDA. After the DS1307 acknowledges the slave address + write bit, the master transmits a word address to the DS1307. This sets the register pointer on the DS1307, with the DS1307 acknowledging the transfer. The master can then transmit zero or more bytes of data with the DS1307 acknowledging each byte received. The register pointer automatically increments after each data byte are written. The master will generate a STOP condition to terminate the data write. 2. Slave Transmitter Mode (Read Mode): The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit will indicate that the transfer direction is reversed. The DS1307 transmits serial data on SDA while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer (see Figure 5). The slave address byte is the first byte received after the START condition is generated by the master. The slave address byte contains the 7-bit DS1307 address, which is 1101000, followed by the direction bit (R/W), which is 1 for a read. After receiving and decoding the slave address the DS1307 outputs an acknowledge on SDA. The DS1307 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode the first address that is read is the last one stored in the register pointer. The register pointer automatically increments after each byte are read. The DS1307 must receive a Not Acknowledge to end a read.

Figure 4. Data WriteSlave Receiver Mode

<Slave Address>

<RW>

<Word Address (n)>

<Data(n)>

<Data(n+1)>

<Data(n+X)>

1101000

A XXXXXXXX

A XXXXXXXX

A XXXXXXXX

A ... XXXXXXXX

A P

S - Start A - Acknowledge (ACK) P - Stop

Master to slave Slave to master DATA TRANSFERRED (X+1 BYTES + ACKNOWLEDGE)

Figure 5. Data ReadSlave Transmitter Mode

<Slave Address>

<RW>

<Data(n)>

<Data(n+1)>

<Data(n+2)>

<Data(n+X)>

1101000

A XXXXXXXX

A XXXXXXXX

A XXXXXXXX

A ... XXXXXXXX

A P

S - Start A - Acknowledge (ACK) P - Stop A - Not Acknowledge (NACK)

Master to slave Slave to master

DATA TRANSFERRED (X+1 BYTES + ACKNOWLEDGE); NOTE: LAST DATA BYTE IS FOLLOWED BY A NOT ACKNOWLEDGE (A) SIGNAL)

12 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

Figure 6. Data Read (Write Pointer, Then Read)Slave Receive and Transmit

<Slave Address>

<RW>

<Word Address (n)>

<Slave Address>

<RW>

1101000

A XXXXXXXX

<Data(n+1)>

A Sr

1101000

A

<Data(n+X)>

<Data(n)>

<Data(n+2)>

XXXXXXXX

A XXXXXXXX

A XXXXXXXX

Master to slave Slave to master

A ... XXXXXXXX

A P

S - Start Sr - Repeated Start A - Acknowledge (ACK) P - Stop A - Not Acknowledge (NACK)

DATA TRANSFERRED (X+1 BYTES + ACKNOWLEDGE); NOTE: LAST DATA BYTE IS FOLLOWED BY A NOT ACKNOWLEDGE (A) SIGNAL)

PACKAGE INFORMATION

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages. PACKAGE TYPE PACKAGE CODE DOCUMENT NO. 8 PDIP 8 SO 21-0043 21-0041

13 of 14

DS1307 64 x 8, Serial, I C Real-Time Clock

REVISION HISTORY

REVISION DATE DESCRIPTION Moved the Typical Operating Circuit and Pin Configurations to first page. Removed the leaded part numbers from the Ordering Information table. Added an open-drain transistor to SQW/OUT in the block diagram (Figure 1). Added the pullup voltage range for SDA, SCL, and SQW/OUT to the Pin Description table and noted that SQW/OUT can be left open if not used. Added default time and date values on first application of power to the Clock and Calendar section and deleted the note that initial power-on state is not defined. Added default on initial application of power to bit info in the Control Register section. Updated the Package Information section to reflect new package outline drawing numbers. PAGES CHANGED 1 1 4 6 8 9 13

100208

14 of 14

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

M a x i m I n t e g r a t e d P r o d u c t s , 1 2 0 S a n G a b r i e l D r iv e , S u n n y v a le , C A 9 4 0 8 6 4 0 8- 7 3 7 - 7 6 0 0

2008 Maxim Integrated Products Maxim is a registered trademark of Maxim Integrated Products, Inc.

You might also like

- DS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesDocument14 pagesDS1307 64 X 8, Serial, I C Real-Time Clock: General Description FeaturesAn TrìnhNo ratings yet

- DS1307 Datasheet FullDocument15 pagesDS1307 Datasheet FulllamanzanadeadanNo ratings yet

- Extremely Accurate I C-Integrated RTC/TCXO/Crystal: General Description FeaturesDocument20 pagesExtremely Accurate I C-Integrated RTC/TCXO/Crystal: General Description FeaturesMilan Đokić100% (1)

- I C, 32-Bit, Binary Counter Clock With 64-Bit ID: General Description FeaturesDocument12 pagesI C, 32-Bit, Binary Counter Clock With 64-Bit ID: General Description FeaturesNur AzizahNo ratings yet

- Data SheetDocument22 pagesData SheetIeeeChannaNo ratings yet

- 24 LC 2561Document12 pages24 LC 2561ricardo_MassisNo ratings yet

- 24LC02BDocument26 pages24LC02Bjab_arx1No ratings yet

- Adc 0804 PDFDocument18 pagesAdc 0804 PDFCinthya VillenaNo ratings yet

- Ca3306 (A, C)Document17 pagesCa3306 (A, C)notaden1849No ratings yet

- 8-BIT SERIAL SHIFT REGISTERDocument6 pages8-BIT SERIAL SHIFT REGISTERenriquevagoNo ratings yet

- Cmos 24aa256 & 24LC256Document12 pagesCmos 24aa256 & 24LC256Someguy123551234512No ratings yet

- MK41T56 MKI41T56: 512 Bit (64b x8) Serial Access TIMEKEEPER SramDocument16 pagesMK41T56 MKI41T56: 512 Bit (64b x8) Serial Access TIMEKEEPER SramzdravkorrNo ratings yet

- LTC 1661Document14 pagesLTC 1661mneagu123No ratings yet

- 24 LC 16Document32 pages24 LC 16Jos RoNo ratings yet

- SPI Serial Memory: FeaturesDocument18 pagesSPI Serial Memory: Featuresoskita79No ratings yet

- Datasheet CY62146DV30LDocument11 pagesDatasheet CY62146DV30LedgarlibanioNo ratings yet

- Features Descriptio: LTC4301L Hot Swappable 2-Wire Bus Buffer With Low Voltage Level TranslationDocument12 pagesFeatures Descriptio: LTC4301L Hot Swappable 2-Wire Bus Buffer With Low Voltage Level TranslationjuenkkinNo ratings yet

- A 6275 EatDocument12 pagesA 6275 Eatn_t_162No ratings yet

- 24 LC 64Document12 pages24 LC 64achuthkumarNo ratings yet

- 24AA00/24LC00/24C00: 128 Bit I C Bus Serial EEPROMDocument18 pages24AA00/24LC00/24C00: 128 Bit I C Bus Serial EEPROMJuliano GriguloNo ratings yet

- FOR EEPROM DOCUMENTDocument9 pagesFOR EEPROM DOCUMENTIram Loya ValladaresNo ratings yet

- 93C66 Microwire EepromDocument13 pages93C66 Microwire EepromadrianramonNo ratings yet

- AT25F512AN 10SU 2.7 AtmelDocument6 pagesAT25F512AN 10SU 2.7 Atmelmirage0706No ratings yet

- ADC0804 DatasheetDocument48 pagesADC0804 DatasheetSaurabh AnmadwarNo ratings yet

- 24C02C SMDDocument16 pages24C02C SMDWalter RossiNo ratings yet

- CAT24C256 256 KB I C CMOS Serial Eeprom: DescriptionDocument18 pagesCAT24C256 256 KB I C CMOS Serial Eeprom: Descriptionjagadees21No ratings yet

- 40V Precision Low Power Operational Amplifiers: ISL28117, ISL28217 FeaturesDocument25 pages40V Precision Low Power Operational Amplifiers: ISL28117, ISL28217 FeaturesNikole Cueva CevallosNo ratings yet

- Datasheet STR 6757Document11 pagesDatasheet STR 6757Walter CarreroNo ratings yet

- SPI Serial Eeproms: FeaturesDocument16 pagesSPI Serial Eeproms: FeaturesBachi403No ratings yet

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDocument4 pages24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMcabalaestebanNo ratings yet

- DS3231Document25 pagesDS3231Muhammad Ajie PrastyoNo ratings yet

- CA3161EDocument4 pagesCA3161EAlejandro Borrego DominguezNo ratings yet

- Distributed byDocument42 pagesDistributed bydennyjoelNo ratings yet

- Quad 2-Input AND Gate: KK74HC08ADocument5 pagesQuad 2-Input AND Gate: KK74HC08Acatsoithahuong84No ratings yet

- ADC128S022Document20 pagesADC128S022Jorge WattesNo ratings yet

- 8K X 8 BIT CMOS SRAM Preliminary DocumentDocument13 pages8K X 8 BIT CMOS SRAM Preliminary DocumentntrscribeNo ratings yet

- MCP 79410Document34 pagesMCP 79410Krishna SinghNo ratings yet

- 24LC04BDocument22 pages24LC04BcarlosNo ratings yet

- 32kx8bit CMOS SRAM: HY62256B SeriesDocument9 pages32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsrieNo ratings yet

- At25f512a 844895Document19 pagesAt25f512a 844895mirage0706No ratings yet

- 74HC4852 (Driver Injector)Document16 pages74HC4852 (Driver Injector)el_george0079491No ratings yet

- ADC0802, ADC0803 ADC0804: Features DescriptionDocument17 pagesADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataNo ratings yet

- tsc2046 DsDocument32 pagestsc2046 DsBobby ChippingNo ratings yet

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument18 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesMarco MenezesNo ratings yet

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument17 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesJorge Luis Castillo GuarachiNo ratings yet

- Dap006 Dap6a DataDocument15 pagesDap006 Dap6a DataluisfeipezzNo ratings yet

- S 24 Cs 08Document34 pagesS 24 Cs 08mj15015100% (1)

- 74C373Document11 pages74C373Juan Orlando MontesNo ratings yet

- SPI Serial Eeprom: FeaturesDocument22 pagesSPI Serial Eeprom: FeaturesHmcc HoangNo ratings yet

- Ucn 5821 ADocument7 pagesUcn 5821 ACelso Conceição100% (1)

- DS1307 PDFDocument14 pagesDS1307 PDFririn suyatiNo ratings yet

- SN 761672 ADocument18 pagesSN 761672 AAda CsabaNo ratings yet

- 24lc08 EepromDocument27 pages24lc08 EepromIsmael Minchola CarhuasNo ratings yet

- DS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentDocument8 pagesDS1270W 3.3V 16Mb Nonvolatile SRAM: Features Pin AssignmentAndré CastroNo ratings yet

- Atmel 25F1024ADocument18 pagesAtmel 25F1024ALukeNo ratings yet

- CD 74 HCT 164 MDocument16 pagesCD 74 HCT 164 MfabriziocasNo ratings yet

- Hex Inverter Technical Data SheetDocument5 pagesHex Inverter Technical Data SheetIonut SimaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Embedded Systems Tutorial PDFDocument17 pagesEmbedded Systems Tutorial PDFShiv PatelNo ratings yet

- Audio signal conditioning circuits for Arduino platformsDocument5 pagesAudio signal conditioning circuits for Arduino platformspraveen_kodgirwarNo ratings yet

- How to use ESP32 BLE (Bluetooth Low EnergyDocument23 pagesHow to use ESP32 BLE (Bluetooth Low Energypraveen_kodgirwar100% (1)

- Touch Screen Wireless Industrial ControlDocument2 pagesTouch Screen Wireless Industrial Controlpraveen_kodgirwar0% (1)

- Android Voice Controlled WheelchairDocument2 pagesAndroid Voice Controlled Wheelchairpraveen_kodgirwarNo ratings yet

- How to use ESP32 BLE (Bluetooth Low EnergyDocument23 pagesHow to use ESP32 BLE (Bluetooth Low Energypraveen_kodgirwar100% (1)

- Air Quality With MQ135Document5 pagesAir Quality With MQ135praveen_kodgirwarNo ratings yet

- Ieee 2019-20 IotDocument7 pagesIeee 2019-20 Iotpraveen_kodgirwarNo ratings yet

- Flame DetectorDocument6 pagesFlame DetectoraavianiacNo ratings yet

- Digital Electronics PDFDocument224 pagesDigital Electronics PDFSruthy Arun100% (1)

- Audio signal conditioning circuits for Arduino platformsDocument5 pagesAudio signal conditioning circuits for Arduino platformspraveen_kodgirwarNo ratings yet

- Zigbee Based Surveillance RobotDocument3 pagesZigbee Based Surveillance Robotpraveen_kodgirwarNo ratings yet

- Zigbee Based Scrolling LED Notice BoardDocument2 pagesZigbee Based Scrolling LED Notice Boardpraveen_kodgirwarNo ratings yet

- Touch Screen Based Wireless RobotDocument2 pagesTouch Screen Based Wireless Robotpraveen_kodgirwarNo ratings yet

- Voice Controlled Robot Using Android ApplicationDocument3 pagesVoice Controlled Robot Using Android Applicationpraveen_kodgirwarNo ratings yet

- Wi-Fi Based Temp, Humidity MeasurementDocument2 pagesWi-Fi Based Temp, Humidity Measurementpraveen_kodgirwarNo ratings yet

- Voice Based Door Access Control Using AndroidDocument2 pagesVoice Based Door Access Control Using Androidpraveen_kodgirwarNo ratings yet

- Iot Based Parking ManagementDocument2 pagesIot Based Parking Managementpraveen_kodgirwarNo ratings yet

- Zigbee Based Wireless MessangerDocument2 pagesZigbee Based Wireless Messangerpraveen_kodgirwarNo ratings yet

- Self Balancing RobotDocument2 pagesSelf Balancing Robotpraveen_kodgirwarNo ratings yet

- Wi-Fi Based LED Scrolling Notice BoardDocument2 pagesWi-Fi Based LED Scrolling Notice Boardpraveen_kodgirwarNo ratings yet

- Obstacle Avoidance Autonomous RobotDocument2 pagesObstacle Avoidance Autonomous Robotpraveen_kodgirwarNo ratings yet

- Zigbee Based Token Number DisplayDocument2 pagesZigbee Based Token Number Displaypraveen_kodgirwarNo ratings yet

- Wireless Agriculture Environment Monitoring Using Zigbee TechnologyDocument2 pagesWireless Agriculture Environment Monitoring Using Zigbee Technologypraveen_kodgirwarNo ratings yet

- Zigbee Environment ControlDocument3 pagesZigbee Environment Controlpraveen_kodgirwarNo ratings yet

- Wi-Fi Based Home AutomationDocument3 pagesWi-Fi Based Home Automationpraveen_kodgirwarNo ratings yet

- Web Server Based Remote Real Time Sensor Monitoring SystemDocument2 pagesWeb Server Based Remote Real Time Sensor Monitoring Systempraveen_kodgirwarNo ratings yet

- Web Server Based Parking SystemDocument2 pagesWeb Server Based Parking Systempraveen_kodgirwarNo ratings yet

- Wi-Fi Based Water Level Monitoring & Motor Pump ControllerDocument2 pagesWi-Fi Based Water Level Monitoring & Motor Pump Controllerpraveen_kodgirwarNo ratings yet

- Wi-Fi Based Scheduling For Smart Plant Irrigation ControlDocument3 pagesWi-Fi Based Scheduling For Smart Plant Irrigation Controlpraveen_kodgirwarNo ratings yet