Professional Documents

Culture Documents

Informe

Uploaded by

Leo BurbanoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Informe

Uploaded by

Leo BurbanoCopyright:

Available Formats

TTULO OPERACIONES ARITMTICAS BINARIAS OBJETIVO: Familiarizar al estudiante con la utilizacin y funcionamiento de circuitos lgicos combinacionales que realizan

operaciones aritmticas binarias. TEORA: Todas las operaciones matemticas (sumas, restas, divisiones, etc.) que realiza la computadora estn basadas en la aritmtica binaria. SUMA BINARIA La aritmtica binaria es muy similar a la aritmtica decimal. Por ejemplo, para realizar una suma binaria hay que tener en cuenta la siguiente tabla:

Ejemplo 1: Para sumar los nmeros binarios 100102 y 1102 se puede escribir:

Para comprobar si la suma es correcta, podemos convertir los nmeros binarios a base 10. As pues, aplicando el Teorema Fundamental de la Numeracin (TFN) obtendremos: 1 Sumando 100102 = 124 + 023 + 022 + 121 + 020 = 16 + 0 + 0 + 2 + 0 = 1810 2 Sumando 1102 = 122 + 121 + 020 = 4 + 2 + 0 = 610 Resultado 110002 = 124 + 123 + 022 + 021 + 020 = 16 + 8 + 0 + 0 + 0 = 2410 y, efectivamente: 1810 + 610 = 2410 En forma similar a como realizamos las sumas en decimal, para realizarlas en otros sistemas es necesario aprender de memoria algunas sumas bsicas, especialmente las sumas de dgito con dgito; en decimal estas son 100 sumas (tablas de sumar), mientras que en binario son slo 4, puesto que en binario slo hay dos dgitos:

Cuando la tabla anterior se usa en una suma de cantidades de varios bits, se suma columna por columna de LSB a MSB y si aparece el caso 1+1, se anota el 0 y se acarrea el 1 a la siguiente columna.

RESTA BINARIA Si se quiere realizar una resta binaria se debe considerar la siguiente tabla:

Ejemplo 2: Para restar los nmeros binarios 1010012 y 10112 escribiremos:

El algoritmo de la resta, en binario, es el mismo que en el sistema decimal. Pero conviene repasar la operacin de restar en decimal para comprender la operacin binaria, que es ms sencilla. MULTIPLICACIN BINARIA Para efectuar una multiplicacin binaria se tiene que tener en cuenta la siguiente tabla:

Ejemplo 3: Para realizar el producto de los nmeros binarios 101012 y 1012 hay que realizar los siguientes clculos:

DIVISIN BINARIA En cuanto a las divisiones binarias, las reglas tambin son las mismas que en el Sistema Decimal, con la ventaja de que en binario slo se usan dos dgitos. Ejemplo 4: Para dividir 1100102 entre 102 los clculos son:

CUESTIONARIO: 1. Consulte el funcionamiento bsico y caractersticas generales de los circuitos integrados: 74264, 74182, 74282, 74882, 74181. Indique en resumen las aplicaciones de dichos circuitos integrados. 74264 (Look-ahead carry generators for counters) Este dispositivo fue diseado para realizar un anticipado carry al otro lado de cualquier nmero de n-bit, as incrementa la frecuencia del sistema de reloj. Un carry habilitado CE, y una salida carry RCOA y RCOB son proporcionados para conexin en cascada. El contador puede ser usado como un carry activo ALTO o activo BAJO. Para el carry activo alto, CE est activado ALTO, las entradas A y salidas RCOA son usadas, y las entradas B son conectadas a nivel lgico BAJO. Para el carry activo BAJO, CE es activado BAJO, las entradas B y salidas RCOB son usadas, y las entradas A son conectadas a nivel lgico ALTO. Caractersticas Voltage Vcc: Min: 4.5 V Mx.: 5.5 V Corriente: Salida en alto: -2 mA. Salida en bajo: 20 mA. Rango de temperatura de operacin: 0c 25c. 74182 Los SN54182, SN54S182, SN74182, y SN74S182 son de gran velocidad, look-ahead, generadores de carry, capaz de anticipar un carry por cuatro sumadores binarios o grupo de sumadores. Ellos son conectables en cascada para realizar un look-ahead completo por los sumadores de n-bits. Cuando son usados junto con la ALU 181, LS181, o S181, ste generador proporciona un carry de gran velocidad y capacidad de look-ahead para cualquier tamao de palabra. Multiniveles de adelanto al Funcionamiento de la alta velocidad de la Unidad Aritmtica por encima de las largas longitudes de los nmeros ingresados. Caractersticas Voltage Vcc:

Min: 4.5 V Mx.: 5.5 V Corriente: Salida en alto: -1 mA. Salida en bajo: 20 mA. Rango de temperatura de operacin: 0c 70c. Descripcin Funcional Los F182 aceptan a cuatro pares de seales carry propagadores activo BAJO (P0-P3) y Carry Generadores (G0-G3) y un carry de entrada activo ALTO (Cn) y proporciona anticipado activo-alto carry (Cn + x, Cn + y, Cn + z) por cuatro grupos de sumadoras binarias. Los F182 tambin tienen Carry Propagadores activo BAJO (P) y Carry Generador (G) de salida que puede usarse para los niveles extensos de adelanto. Las ecuaciones lgicas proporcionadas a las salidas son: Cn + x = G0 + P0Cn Cn + y = G1 + P1G0 + P1P0Cn Cn + z = G2 + P2G1 + P2P1G0 + P2P1P0Cn G = G3 + P3G2 + P3P2G1 + P3P2P1G0 P = P3P2P1P0 Tambin, los F182 pueden usarse con ALUs binarios de entradas de modo activo BAJO o activo-ALTO. 74282(Look-Ahead Carry Generator con selector de entradas Carry) Este es capaz de anticipar un carry a un grupo de 4 bits. Realizan conexin en cascada para un nmero de n-bits. Aqu la entrada carry es CnA, CnB, sus complementos CnA y CnB. Con una ALU, este generador provee una lata velocidad para el adelanto de carry para palabras mayores. Y las ecuaciones lgicas son: Cn + x = G0 + P0Cn Cn + y = G1 + P1G0 + P1P0Cn Cn + z = G2 + P2G1 + P2P1G0 + P2P1P0Cn G = G3 + P3G2 + P3P2G1 + P3P2P1G0 P = P3P2P1P0 Caractersticas Voltage Vcc: Min: 4.5 V Mx.: 5.5 V Corriente: Salida en alto: -2 mA. Salida en bajo: 20 mA. Rango de temperatura de operacin: 0c 70c. 74882 (32-bit Look-Ahead Carry Generator)

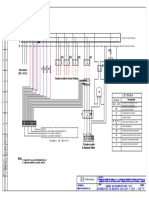

Este es capaz de anticipar un carry a un grupo de ocho de 4-bits permitiendo el diseo de implementar una anticipacin para una ALU de 32-bit, con un simple paquete o haciendo conexin cascada para n-bit. Las ecuaciones lgicas son: Cn + 8 = G1 + P1G0 + P1P0Cn Cn + 16 = G3 + P3G2 + P3P2G1 + P3P2P3G0 + P3P2P1P0Cn Cn + 24 = G5 + P5G4+P5P4G3 + P5P4P3G2 + P5P4P3P2G1 + P5P4P3P2P1G0 + P5P4P3P2P1P0Cn Cn + 32 = G7 + P7G6 + P7P6G5 + P7P6P5G4 + P7P6P5P4G3 + P7P6P5P4P3G2 + P7P6P5P4P3P2G1 + P7P6P5P4P3P2P1G0 + P7P6P5P4P3P2P1P0Cn Caractersticas Voltage Vcc: Min: 4.5 V Mx.: 5.5 V Corriente: Salida en alto: -2 mA. Salida en bajo: 20 mA. Rango de temperatura de operacin: 0c 70c. 74181 Las ALU MSI tienen operandos de4-bits y de tres a cinco entradas de seleccin de operaciones, permitiendo la realizacin de hasta 32 funciones diferentes. La siguiente figura muestra la distribucin de pines de la ALU 74LS181 de 4-bits. El tipo de operacin que realiza el CI-74181 se selecciona mediante la entrada M y las entradas de seleccin [S0, S1, S2, S3] como se indica en la siguiente tabla. Obsrvese que los identificadores A, B y F en la tabla se refieren a palabras de 4-bits [A0, A1, A2, A3],[B0, B1, B2, B3] y [F0, F1, F2, F3] y los smbolos. y + se refieren a las operaciones AND y OR lgicas. La entrada M del 181 selecciona entre las operaciones aritmticas y l gicas. Cuando M = 1, se seleccionan las operaciones lgicas y cada salida Fi es funcin slo de las correspondientes entradas de datos, Ai y Bi [bit-a-bit]. No se propagan los excesos [carry] entre las etapas y se ignora la entrada CN [carry in]. Las entradas [S0, S1, S2, S3] seleccionan una operacin lgica particular; puede seleccionarse cualquiera de las 16 operaciones combinacionales lgicas diferentes sobre dos variables.

Tabla de Funciones realizadas por la ALU 74LS181 de 4-bits. Cuando M = O, se seleccionan las operaciones aritmticas, se propagan los excesos entre las etapas y se usa el Ci como una entrada de exceso a la etapa ms significante. Para operaciones de ms de 4-bits, pueden conectarse varias ALU en cascada, con el exceso de salida [Co] de cada ALU conectado al exceso de entrada [Ci] de la etapa siguiente ms significante. Las mismas seales de seleccin de funcin [M, S3, S2, S1, S0+ se aplican a todos los 181 en la cascada. Para realizar una suma en complemento a dos, se usa [S3, S2, S1, S0+ para seleccionar la operacin A ms B ms Ci. La entrada Ci de la ALU menos significante est normalmente en 0 durante las operaciones de suma. Para realizar una resta en complemento a dos, se usa S3 y S0 para seleccionar la operacin A menos B menos 1 ms Ci. En este caso la entrada Ci de la ALU menos significante est en 1, ya que Ci acta como el complemento del carry durante la resta. El 181 proporciona otras operaciones aritmticas, como A menos 1 ms Ci, que son tiles en algunas aplicaciones [por ejemplo, decrementar en 1]. Tambin proporciona muchas operaciones aritmticas raras, como A.B ms (A + B) ms Ci, que casi nunca se usan en la prctica. Obsrvese que las entradas del operando [A3,A2,A1,A0] y [B3,B2,B1,B0] y las salidas de la funcin *F3,F2,F1,F0+ del 181 son activas bajas. El 181 tambin puede usarse con las entradas de los operandos y lassalidas de la funcin en activa alta. En este caso, debe construirse una versin diferente de la tabla de la funcin.Cuando M = 1, las operaciones lgicas an se realizan, pero para una combinacin de entrada dada en [S3, S2, S1, S0], la funcin obtenida es precisamente la dual de la listada en la tabla anterior. Cuando M = O, se realizan las operaciones aritmticas, pero la tabla de funcin es de nuevo diferente. 2. Consulte el funcionamiento bsico y caractersticas generales del circuito integrado 74385. Indique en resumen las aplicaciones de dicho circuito integrado. 74385 Los LS385 son un cudruples sumadores/restadores de propsito general y son particularmente tiles como una parte complementaria del SN54LS384/SN74LS384 multiplicador en complemento de dos. Los LS385 contienen cuatro elementos sumadores/restadores independientes con reloj y clear comunes. Este circuito integrado contiene cuatro independientes sumadores / restador con reloj borrador comn.

Cada uno de estos salidas () son reflejadas respectivamente de las entradas A y B controladas por el control S/ A . Cuando S/ A es ALTO la funcin es A menos B. Cuando S/ A es BAJO la funcin es A mas B. Caractersticas Voltaje Vcc: Min: 4.75 V Mx.: 5.25 V Corriente: Salida en alto: -400 uA. Salida en bajo: 8 mA. Frecuencia del reloj: 0 30 MHz Tiempo de retardo: 3 ns Tiempo de instalacin: 10 ns Rango de temperatura de operacin: 0c 70c. 3. Consulte el funcionamiento bsico y caractersticas generales de los circuitos integrados: 74261, 74284, 74285, 74384. Indique en resumen las aplicaciones de dichos circuitos integrados. 74261 Multiplicador Binario 2Bits por 4Bits El SN54/74261 es un circuito integrado que realiza la multiplicacin binaria en forma de complemento de dos, dos bits cada vez. Caractersticas Voltaje Vcc: Min: 4.75 V Mx.: 5.25 V Corriente: Salida en alto: -400 uA. Salida en bajo: 8 mA Tiempo de retardo: menor a 0 ns Tiempo de instalacin: menor a 15 y 17 ns Rango de temperatura de operacin: 0c 70c. Tabla de Funcin INPUTS LATCH MULTIPLIER CONTROL M2 M1 M0 L H H X L L X L L X L H OUTPUTS

Q4 Q 4o H

Q3

Q2

Q1

Q1o

L B2

Q0

Q3o

L B4

Q2o

L B3

Q0o

L B1

B4

H H H H H H

L L H H H H

H H L L H H

L H L H L H

B4 B4

B4 B4 B4 H

B4 B3

B3 B2

B2 B1

B1 B0

B3 B4 B4

L

B2 B3 B3

L

B1 B2 B2

L

B0 B1 B1

L

Circuito Integrado 74284 y 74285 El SN54/74284 y SN54/74285 son multiplicadores binarios de 4 por 4 bits paralelos. Generan el producto de 8 bits en aproximadamente 40 ns. Caractersticas Voltaje Vcc: Min: 4.75 V Mx.: 5.25 V Corriente: Salida en bajo: 16 nA Rango de temperatura de operacin: 0c 70c. Tabla de Funcin INPUT OUTPUT Co=0 A1 B1 A2 B2 1 A3 B3 A4 B4 3 0 0 0 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 2 4 0 0 0 1 1 1 1 0 1 1 1 0 0 0 0 1 C C=0 Co=1 C=1 C2 1 2 C2 C4 3 4 C4 0 1 0 0 0 0 0 0 0 0 1 0 0 0 1 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 1 1 1 0 0 0 1 0 0 0 0 1 1 1 0 0 0 0 1 1 1 0 1 1 1 1 1 1 1

Circuito Integrado 74384

8-bit por 1-bit Multiplicacin a Complemento Dos. Este diseado para multiplicaciones de dos nmeros en complemento dos y produce un producto en la forma complemento dos sin correccin externa. Este dispositivo acepta un multiplicando de 8-bit (entradas X) y guarda estos valores en 8 retardos internos. Estos retardos X son controlados por la entrada clear. Cuando la entrada clear es BAJO, los valores de X se borran para aceptar nuevos valores. El dato multiplicado es pasado a la entrada Y en una serie de corridas de bits. El bit menos significante primero. El producto es temporizado a la salida PROD, el menos significante primero. Tiene una entrada K par conexin en cascada. Caractersticas Voltaje Vcc: Min: 4.75 V Mx.: 5.25 V Corriente: Salida en alto: -400 uA. Salida en bajo: 8 mA Rango de temperatura de operacin: 0c 70c.

4. Disear un circuito generador de paridad par, de 4 bits de entrada. Comprobar su funcionamiento a travs de simulacin en el programa computacional Proteus 7 Professional. Adems consulte el funcionamiento bsico y caractersticas generales del circuito integrado 74286.

D 0 0 0 0 0 0

C 0 0 0 0 1 1

B 0 0 1 1 0 0

A 0 1 0 1 0 1

F 1 0 0 1 0 1

0 0 1 1 1 1 1 1 1 1

1 1 0 0 0 0 1 1 1 1

1 1 0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1 0 1

1 0 0 1 1 0 1 0 0 1

BA

DC

00 01 11 10

00 01 11 10 1 1 1 1 1 1 1 1

5. Consulte el funcionamiento y la introduccin a la programacin de los Arreglos Lgicos Programables o PLA (Programable Logic Array). En base a esto dibuje un PLA de dos variables de entrada para tres funciones F1, F2 y F3. Los dispositivos lgicos programables usados con mayor frecuencia para la implementacin lgica son la PAL y la GAL. PAL es una denominacin que originalmente utilizaba la compaa Monolithic Memories, Inc. Una PAL est formada por una matriz de puertas AND programable conectada a una matriz de puertas OR fija. Esta estructura permite implementar cualquier suma de productos 16gica con un nmero de variables definido. En la Figura se ilustra la estructura bsica de una PAL para dos variables una entrada y una salida, aunque la mayora de las PAL tiene muchas entradas y salidas. Como se sabe, una matriz programable es esencialmente una red de conductores ordenados en filas y columnas, con un fusible en cada punto de interseccin.

Cada punto de interseccin entre una fila y una columna se denomina celda y es el elemento programable de la PAL. Cada fila se conecta a la entrada de una puerta y cada columna a una variable de entrada o a su complemento. En funcin de la presencia o ausencia de las conexiones creadas por programacin, se puede aplicar cualquier combinacin de variables de entrada o sus complementos a una puerta para generar cualquier trmino producto que se desee. Implementacin de una suma de productos En su forma ms sencilla, cada celda de una matriz AND bsica est formada por un fusible que conecta una fila y una columna, como se representa en la Figura. Cuando se requiere la conexin entre una fila y una columna, el fusible queda intacto. Cuando dicha conexi6n no se requiere, el fusible se abre en el proceso de programacin. En la Figura se muestra un ejemplo de una matriz programada para generar el producto AB en la salida de la puerta AND superior, el producto AB en la funcin AND del centro y el producto A B en la puerta AND inferior. Como puede verse los fusibles quedan intactos para conectar las variables deseadas, o sus complementos a las entradas apropiadas de las puertas AND. Los fusibles se funden en los casos que las variables o sus complementos no se utilizan en el producto que se desea obtener. La salida de la puerta OR proporciona la suma de productos.

X AB AB A B

Smbolos simplificados Vamos a ver como se representa un pequeo segmento de una PAL tpica. Las PAL reales tienen muchas puertas AND y muchas puertas OR, adems de otra circuitera, y son capaces de manejar muchas variables de entrada y sus complementos. Puesto que las PAL son circuitos integrados muy complejos, los fabricantes han adoptado una notacin simplificada para eliminar los diagramas lgicos arrolladoramente complicados.

Buffers de entrada Para evitar cargar con la gran cantidad de entradas de puertas AND a las que se pueden conectar una variable 0 su complemento, se aade un buffer a las variables de entrada de la PAL. Un buffer inversor genera el complemento de una variable de entrada. EI smbolo que representa el circuito buffer, el cual genera la variable y su complemento en sus salidas, se muestra en la Figura, donde la salida con el crculo corresponde a la variable complementada.

Puertas AND Una matriz AND de una PAL tpica tiene una cantidad extremadamente grande de lneas de interconexi6n, y cada puerta AND tiene entradas mltiples El diagrama lgico de una PAL muestra cada puerta AND, que realmente tiene varias entradas, utilizando una sola lnea para representar a todas las lneas de entrada se indica en la Figura. Algunas veces, las lneas mltiples tambin se indican mediante una barra inclinada y el, numero de lneas, tal como se muestra en la puerta AND superior para el caso de cuatro lneas. Conexiones en una PAL Para obtener un diagrama lgico l0 ms sencillo posible los fusibles de una matriz AND programable se indican mediante una X en el de interseccin si el fusible queda intacto, y no se indica nada si el fusible est fundido. Lgica combinacional de salida de una PAL Existen varios tipos bsicos de circuitos lgicos de salida para una PAL, que permiten configurar el dispositivo para una aplicacin especfica. En la Figura se muestran tres tipos bsicos de lgica combinacional de salida con salidas de tres estados y la puerta OR asociada. Los tipos de lgica de salida de una PAL son: Salida combinacional. Esta salida se usa para una suma de productos y, usualmente, la salida puede ser activa a nivel ALTO 0 BAJO. Entrada/salida combinacional. Esta salida se usa cuando la funcin de salida debe realimentarse a una entrada de la matriz, 0 cuando el pin de E/S se usa solo como entrada.

Salida de polaridad programable. Esta salida se usa para seleccionar la funcin de salida o su complemento, programando la puerta OR-exclusiva para realizar la inversin o no. El fusible de la entrada de la puerta OR-exclusiva se funde en el caso de inversin, y queda intacto en el caso de no inversin. Para la realizacin de un sumador completo se tiene: Implantamos la suma de mintrminos de un sumador completo en un modelo a compuertas:

La implantacin en un diagrama PLA es la siguiente:

El correspondiente en mintrminos para el sumador est determinado por:

f1 x 1 x 2 x 3 x 1 x 2 x 3 x 1 x 2 x 3 x 1 x 2 x 3

f2 x1x 2 x 3 x1x 2 x 3 x1x 2 x 3 x1x 2 x3

Cada expresin contiene cuatro mintrminos, uno de los cuales es compartido. Podemos establecer una correspondencia entre los siete mintrminos distintos (compuertas AND de tres entradas) y una fila del PLA. Observe que a cada fila se le proporcionan las variables de entrada en forma verdadera y complementada, una de las cuales est conectada a la fila (indicado con un x en el punta de cruce) y la otra esta desconectada. Si se programan los puntos de cruce de manera apropiada, se puede lograr que la fila genere cualquier mintrmino deseado o, de manera ms general, cualquier producto deseado de un mximo de tres variables. Por ejemplo, la primera fila del plano AND de la figura superior tiene conexiones con las entradas primarias x 1 , x 2 , x 3 y por ende genera el mintrmino:

m5 x 1 x 2 x 3

La segunda fila tiene conexiones a x 1 , x 2 , x 3 , produciendo:

m6 x 1 x 2 x 3

Cada una de las primeras siete filas del PLA representa un mintrmino m1: m7; no se requiere la ltima fila. Si pasamos al plano OR de la figura superior, observamos que la primera columna est conectada nicamente a las primeras cuatro filas y por lo tanto calcula la funcin de cuatro trminos (acarreo).

f 1 m 5 m6 m 3 m 7 x 1 x 2 x 3 x 1 x 2 x 3 x 1 x 2 x 3 x 1 x 2 x 3

La otra funcin (suma) f2 se implanta en forma similar como una suma 16gica de cuatro de sus mintrminos. Observe cmo se comparte el mintrmino m7 entre las dos funciones de salida.

6. Programe el PLA del numeral anterior a fin de ejecutar las siguientes funciones: ( La tabla de verdad: ) ( ) ( ) ( ) ( ) ( )

0 0 1 1

0 1 0 1

0 0 0 1

1 0 0 1

1 1 1 0

CONCLUSIONES: Se implemento circuitos lgicos que realizan operaciones aritmticas binarias y se logro comprobar su funcionamiento. Los circuitos combinacionales permiten realizar operaciones aritmticas a partir del diseo de los respectivos circuitos lgicos conociendo la tabla de verdad de la operacin a realizarse.

El diseo de estos circuitos puede realizarse en complemento a1 o complemento a2, considerando un ajuste decimal en el caso de un cdigo BCD. Los circuitos integrados que realizan operaciones aritmticas binarias son el circuito 7483 que es un medio sumador y el circuito integrado 74283 que es un sumador completo, con la utilizacin de estos circuitos se pueden implementar sumadores del cualquier nmero de bits. Esta prctica ha sido muy interesante por el hecho que nos ha dado la oportunidad de trabajar con tipos diferentes de circuitos sumadores. Tambin nos ha hecho conocer la manera de convertir el sumador 7483 que es sumador binario en un sumador BCD, para esto se utilizo un circuito llamado ajuste decimal. Conocimos tambin el CI-74181 que es un circuito que puede realizar muchas operaciones, para utilizarlo necesitamos conocer muy bien su tabla de funcionamiento porque es un circuito que tiene cuatro selectores ms dos selectores Cn y M que se deben de manejar de manera correcta para su funcionamiento adecuado.

BIBLIOGRAFIA: http://www.cs.mun.ca/~paul/cs3724/material/web/notes/node10.html Ronald Tocci, Sistemas Digitales Principios y Aplicaciones, 5. Edicin, Prentice Hall, Captulo 6, Pg. 281-282 M. Morris Mano, Diseo Digital, Prentice Hall Hispanoamericana, Mxico 1987. Motorola Inc. Fast and ls TTl data. Motorola inc, quinta edicin, 1992. Novillo M., Carlos; Sistemas Digitales, Circuitos MSI, Pgs. 61 - 67, EPN, Quito, Ecuador, 2003.

You might also like

- Qdoc - Tips Sistemas-Digitales PDFDocument35 pagesQdoc - Tips Sistemas-Digitales PDFLuisa FernandaNo ratings yet

- Sistemas DigitalesDocument35 pagesSistemas DigitalesDione Huaman Borda100% (1)

- Circuitos+Integrados+MSI Parte1Document53 pagesCircuitos+Integrados+MSI Parte1Ssj IngJuan Diego Quishpi LuceroNo ratings yet

- Practicas PLDDocument20 pagesPracticas PLDAna DelgadoNo ratings yet

- Calculadora en Fpga Con Circuitos LógicosDocument10 pagesCalculadora en Fpga Con Circuitos LógicosJhon Abraham Bonilla100% (1)

- Practicas PLDDocument20 pagesPracticas PLDJesus GarciaNo ratings yet

- Circuitos Aritméticos 5Document14 pagesCircuitos Aritméticos 5John QueralesNo ratings yet

- Controlar Display de 7 Segmentos Con Shift RegisterDocument27 pagesControlar Display de 7 Segmentos Con Shift RegisterPOLLO45100% (1)

- Informe de Un Restador en PROTOBOARDDocument10 pagesInforme de Un Restador en PROTOBOARDIvan Crispin PaucarNo ratings yet

- Circuitos Aritméticos 4Document10 pagesCircuitos Aritméticos 4John QueralesNo ratings yet

- SD GR12 Cueva Prieto Informe 8Document5 pagesSD GR12 Cueva Prieto Informe 8Jose CuevaNo ratings yet

- Sumador-Restador de 4 bits con visualización en displays 7 segmentosDocument9 pagesSumador-Restador de 4 bits con visualización en displays 7 segmentosalbertwillyNo ratings yet

- Sistema Binario PDFDocument25 pagesSistema Binario PDFJuan ReyesNo ratings yet

- Tema5 2Document10 pagesTema5 2FerchoNo ratings yet

- Controlar Display de 7 Segmentos Con Shift RegisterDocument20 pagesControlar Display de 7 Segmentos Con Shift RegisterfelipeneyraNo ratings yet

- Alu 74181Document10 pagesAlu 74181Carlos AlbertoNo ratings yet

- Lab 06 Circuitos Digitales UNMSMDocument10 pagesLab 06 Circuitos Digitales UNMSMDianaNo ratings yet

- Práctica 8Document7 pagesPráctica 8buanastareasbetovazquezNo ratings yet

- Registro Acumulador y Transferencia SerialDocument8 pagesRegistro Acumulador y Transferencia SerialHoracio Fernández JiménezNo ratings yet

- Diseño Sumador RestdorDocument10 pagesDiseño Sumador RestdorRamiro David MNo ratings yet

- Ebook RobóticaDocument15 pagesEbook RobóticaOmar.l.No ratings yet

- Calculadora de 4 BitsDocument20 pagesCalculadora de 4 BitsArmando SaldañaNo ratings yet

- Sumador Binario de 4 BitsDocument10 pagesSumador Binario de 4 BitsBere Ramírez AguileraNo ratings yet

- Informe 2 Electrónica DigitalDocument4 pagesInforme 2 Electrónica DigitalRicardo Urrego GamboaNo ratings yet

- Sesion 3 A 4Document62 pagesSesion 3 A 4Hugo Quezada AlegríaNo ratings yet

- Arquitectura de Computadoras: Universidad de El SalvadorDocument30 pagesArquitectura de Computadoras: Universidad de El SalvadorRONALD GALDAMEZNo ratings yet

- El Circuito Integrado 74HCTLS192Document6 pagesEl Circuito Integrado 74HCTLS192Blanca TNo ratings yet

- Sumador Binario N BitsDocument9 pagesSumador Binario N BitsCamilo A. InfanteNo ratings yet

- Practica - 6 Sumadores y RestadoresDocument10 pagesPractica - 6 Sumadores y RestadoresDIEGO ARMANDO COLQUE BAUTISTANo ratings yet

- Tarea 7 DiseñodelprogramadeuncontadorDocument8 pagesTarea 7 DiseñodelprogramadeuncontadorEstefania Rodriguez SanchezNo ratings yet

- Cuestionario Previo 9 PDFDocument9 pagesCuestionario Previo 9 PDFROBERTO GASPAR ESCOBEDO CONTRERASNo ratings yet

- Circuitos CombinacionalesDocument33 pagesCircuitos Combinacionalesgerln2No ratings yet

- Practica 5Document10 pagesPractica 5Lenin Pardo SalazarNo ratings yet

- Analógicas vs digitales, conversiones binarias, circuitos lógicosDocument16 pagesAnalógicas vs digitales, conversiones binarias, circuitos lógicosluisNo ratings yet

- Prac13 Contador Ascendente DescendenteDocument8 pagesPrac13 Contador Ascendente DescendenteStiva DarcyNo ratings yet

- Practica 8 74193Document7 pagesPractica 8 74193nohe_lemusNo ratings yet

- TEMA 7 Lgical Combinacional 07 08Document36 pagesTEMA 7 Lgical Combinacional 07 08Soto LuisNo ratings yet

- Practica 9 Sumador y Restador BinariosDocument13 pagesPractica 9 Sumador y Restador BinariosDaniel Galván Cabrera100% (1)

- Sumador Con Shift RegistersDocument4 pagesSumador Con Shift RegistersJorge L CalizayaNo ratings yet

- Cont AdoresDocument9 pagesCont AdoresSprawlgraffeNo ratings yet

- Aritmetica para ComputadorasDocument11 pagesAritmetica para ComputadorasVictor Alonso MontoyaNo ratings yet

- Informe 4Document35 pagesInforme 4Dimitri IanNo ratings yet

- Señales Diitales y AnalogicasDocument10 pagesSeñales Diitales y AnalogicasJesús López LópezNo ratings yet

- Contador binario de 0 a 255 con dos 74LS193Document9 pagesContador binario de 0 a 255 con dos 74LS193Ricardo salasNo ratings yet

- Arapa Aquino Victor AugustoDocument25 pagesArapa Aquino Victor AugustoVictor ArapaNo ratings yet

- Reporte Banda TransportadoraDocument21 pagesReporte Banda TransportadoraAlejandro VillaseñorNo ratings yet

- Practica 2Document6 pagesPractica 2Vin Doyle BravoNo ratings yet

- Controlar Display de 7 Segmentos Con Shift RegisterDocument20 pagesControlar Display de 7 Segmentos Con Shift RegisterfelipeneyraNo ratings yet

- Act 11 Sistemas Digitales SecuencialesDocument9 pagesAct 11 Sistemas Digitales SecuencialesAleks ChukizanNo ratings yet

- ALUDocument5 pagesALUGabriel FiallosNo ratings yet

- Practica 5Document10 pagesPractica 5HomeroOjedaNo ratings yet

- Electronica Digital CXTX 2015Document13 pagesElectronica Digital CXTX 2015Gustavo Leonardo Castañeda MartinezNo ratings yet

- Diseño de multiplicadores en VHDLDocument8 pagesDiseño de multiplicadores en VHDLJose Lopez AlvarezNo ratings yet

- Multiplicador BinarioDocument9 pagesMultiplicador BinarioJulioMarinNo ratings yet

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiFrom EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiRating: 5 out of 5 stars5/5 (1)

- Ejercicios de Integrales de Línea, Superficie y VolumenFrom EverandEjercicios de Integrales de Línea, Superficie y VolumenRating: 4 out of 5 stars4/5 (2)

- Prac 2 CD 2014ADocument5 pagesPrac 2 CD 2014ALeo BurbanoNo ratings yet

- Proyecto SimulinkDocument6 pagesProyecto SimulinkLeo BurbanoNo ratings yet

- MATLAB Ejemplos de Gráficas en Dos y Tres Dimensiones MedianteDocument13 pagesMATLAB Ejemplos de Gráficas en Dos y Tres Dimensiones MedianteLeo BurbanoNo ratings yet

- INFORME2 Lab - ElectrónicosDocument12 pagesINFORME2 Lab - ElectrónicosLeo BurbanoNo ratings yet

- Trabajo Desafíos Del Mundo ActualDocument3 pagesTrabajo Desafíos Del Mundo ActualLeo BurbanoNo ratings yet

- INFORME5 Lab - ElectrónicosDocument8 pagesINFORME5 Lab - ElectrónicosLeo BurbanoNo ratings yet

- Consulta ReguladoresDocument8 pagesConsulta ReguladoresLeo BurbanoNo ratings yet

- Diseño en JFETDocument5 pagesDiseño en JFETLeo BurbanoNo ratings yet

- Diseño en JFETDocument5 pagesDiseño en JFETLeo BurbanoNo ratings yet

- Examen Energia y ElectricidadDocument23 pagesExamen Energia y ElectricidadSantiago FernandezNo ratings yet

- Ejercicios UD3Document2 pagesEjercicios UD3clase claseNo ratings yet

- L12 PDFDocument1 pageL12 PDFDavid Aurora MendozaNo ratings yet

- SistemaTeleprocesoDocument8 pagesSistemaTeleprocesoCarlos Eduardo PáezNo ratings yet

- Diseño de Banco de Pruebas para Alternadores de 12 VoltiosDocument124 pagesDiseño de Banco de Pruebas para Alternadores de 12 Voltioscristian raul aguilar fernandez100% (2)

- Lab 2.5 Exp 22 ImpedanciaDocument15 pagesLab 2.5 Exp 22 ImpedanciaMauricioNo ratings yet

- 2-Electricidad Portero Eléctrico PDFDocument12 pages2-Electricidad Portero Eléctrico PDFEmi Rodriguez LeottaNo ratings yet

- React Disper Info Imp.Document8 pagesReact Disper Info Imp.Alex SalasNo ratings yet

- BaseDocument27 pagesBasejuan gallardoNo ratings yet

- Diseño 1Document26 pagesDiseño 1Miguel MGNo ratings yet

- Implementación de Un Inversor de 220v Ac A 12v DC de 100w Contando Con El Circuito Elevador de Volataje DCDocument16 pagesImplementación de Un Inversor de 220v Ac A 12v DC de 100w Contando Con El Circuito Elevador de Volataje DCEderson Jorge Paraguay0% (1)

- DM200125 B ES ModulosDocument14 pagesDM200125 B ES Modulosferpriss100% (1)

- Libro 3ESO 30 Agosto 2022Document207 pagesLibro 3ESO 30 Agosto 2022Encarnación García ArizaNo ratings yet

- Arbol EquiposDocument218 pagesArbol EquiposCeirSanchezCalderonNo ratings yet

- Convertidores de Frecuencia ACS480Document154 pagesConvertidores de Frecuencia ACS480RodrigoOrtegaPerochenaNo ratings yet

- Mapa Mental de Celda GalvánicaDocument1 pageMapa Mental de Celda GalvánicaAdonny GeovannyNo ratings yet

- FabricaciónDocument55 pagesFabricaciónHenry Max Kevin Grados CasanaNo ratings yet

- P 7 3 Etapas Apagado IndependienteDocument9 pagesP 7 3 Etapas Apagado IndependienteKevin DanielNo ratings yet

- Guia 05 RC y RLCDocument3 pagesGuia 05 RC y RLCPaolo RoberthNo ratings yet

- Eeid Eeid-210 Malla T005Document3 pagesEeid Eeid-210 Malla T005Denis CotrinaNo ratings yet

- Glosario Tecnologia Gpon y HFCDocument5 pagesGlosario Tecnologia Gpon y HFCJorge Alvarado MendozaNo ratings yet

- Práctica Calificada 2Document6 pagesPráctica Calificada 2Alex Caruajulca Tiglla100% (1)

- Reguladores de CargaDocument13 pagesReguladores de CargaDiógenes Diego Contreras ValdebenitoNo ratings yet

- Diseño de circuito de fuente de alimentación en ProteusDocument9 pagesDiseño de circuito de fuente de alimentación en ProteusAlfonzo TorresNo ratings yet

- Fichas Tecnicas Del Fabricante de Transformador TMCDocument4 pagesFichas Tecnicas Del Fabricante de Transformador TMCAlexander KurosakiNo ratings yet

- Proyecto Instalaciones Hotel JordanDocument22 pagesProyecto Instalaciones Hotel JordanDreyber ChoqueNo ratings yet

- Planillas de Mantenimiento PreventivoDocument10 pagesPlanillas de Mantenimiento PreventivoNelson Lopez Cuestas100% (1)

- Manual Control PunteadoraDocument150 pagesManual Control PunteadoraodysseoNo ratings yet

- Micrófonos-Carlos GonzalezDocument6 pagesMicrófonos-Carlos GonzalezCarlos Tomas Gonzalez AyalaNo ratings yet

- Calculo de AlimentadoresDocument6 pagesCalculo de AlimentadoreswilliamII0% (1)