Professional Documents

Culture Documents

5988 8470en

Uploaded by

Eduardo WalkerOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

5988 8470en

Uploaded by

Eduardo WalkerCopyright:

Available Formats

HMPP-3865 MiniPAK PIN Diode High Isolation SPDT Switch Design for 1.9 GHz and 2.

45 GHz Applications

Application Note 1330

Introduction

PORT 3

The Avago Technologies HMPP-3865 parallel diode pair combines low inductance, low capacitance and low package parasitics, increasing the maximum frequency at which silicon PIN diode switches may be used. The HMPP-3865 offers the industry leading performance in terms of the critical parameters of insertion loss, return loss and isolation high isolation and low resistance increases the efficiency of the switching circuit, resulting in longer battery life in portable equipment. This application note will look at techniques used to minimize the effects of the package parasitics even further by resonating out the diode capacitance to produce a switch design with typically greater than 35 dB of isolation and an insertion loss of 0.5 dB. The design technique is then used to illustrate two High Isolation, SPDT switches at 1.9 GHz and 2.45 GHz. The Avago Technologies MiniPak package is only 1.4 mm x 1.2 mm, permitting smaller circuit boards. It is only 0.7 mm high, allowing closer board spacing, and offers improved thermal conductivity for higher power dissipation than other surface-mount packages. It is lead-free for compliance with emerging environmental requirements. In addition to the HMPP-3865 parallel diode pair, Avago Technologies also offers the HMPP-3860 single PIN diode and HMPP-3862 anti-parallel diode pair in the MiniPak package.

L1

C1

L2

L2

C2

C2

PORT 1

C3

C3

PORT 2

L3 C4 C4

L3

R1 C5 C5

R1

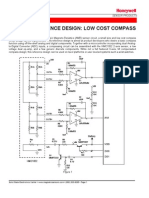

Figure 1. Single Pole Double Throw (SPDT) Switch using HMPP3865 PIN Diode

6311-01 AN 1330

Description

20 fF 0.20 pF

The switch is operated by applying bias current to the diode in series with port 1 and the antenna, bringing it to a low resistance state. This connects port 1 to the antenna port. The bias current to the second diode is held off, making the diode high resistance. The use of a low series resistance and low series inductance PIN diode ensures low loss in the through path and is also good for high isolation. The equivalent circuit model for the HMPP-3865 is shown in Figure 2. This can be used in linear simulations by adjusting the two resistor values between 5 K ohms, the unbiased value, and 2.5 ohms the biased value with 5 10 mA applied. Refer to the RF Resistance vs. Forward Bias Current graph in the data sheet for other bias conditions. Alternatively, the PIN diode APLAC model can be used to replace the parallel capacitor and resistor in the model, as shown in Figure 3. The APLAC model is used to model the PIN diode die. More on this in the next section.

0.05 nH

0.5 nH

0.5 nH

2.5

0.05 nH

30 fF 0.05 nH 0.5 nH

12 fF 0.5 nH 5000

30 fF 0.05 nH

0.20 pF 20 fF

Figure 2. Equivalent circuit of HMPP-3865 using resistor/ capacitor model

20 fF

0.05 nH

APLAC DIE MODEL 0.5 nH 0.5 nH 0.05 nH

6311-02 AN 1330

30 fF 0.05 nH 0.5 nH 12 fF 0.5 nH APLAC DIE MODEL 30 fF 0.05 nH

20 fF

Figure 3. Equivalent circuit of HMPP-3865 using APLAC Die model

6311-03 AN 1330

Table 1. APLAC PIN Diode Parameters for HMPP-386x Die Type.

Parameter, Units Rmax, ohms Rmin, ohms K A L, nH C, pF Is A N TT nsec Unit Description Value Maximum r.f. resistance 5000 Minimum r.f. resistance 1.5 Resistance curve fitting exponent 0.9327 Resistance curve fitting exponent 0.0183 Connection inductance 2 Diode capacitance at r.f. frequency 0.2 Diode saturation current 1.49E-09 Diode ideality factor 2.022 =Transit Time (carrier lifetime) 500

HMPP-386x Limited APLAC Model

10,000

The APLAC PIN model consists of a current controlled resistor and a SPICE model for a diode. The APLAC PIN diode model is shown in Figure 5. D1 uses the standard SPICE diode model, and is described by IS, N, and TT. RS, in the standard model, is replaced by the external network of Rmin, Rmax, and Rvar. The parameters shown in Table 1 are for a single diode. Care should be taken not to include L, connection inductance, when used in conjunction with the package model. Parameters apply to the individual diodes within multiple diode configurations. The APLAC model is able to predict the RF resistance verses forward bias current. Figure 4 shows the RF resistance over a 1 A to 100 mA range. At 100 MHz the RF resistance is approximately 700 Ohms at 0.01 mA and 1.5 Ohms at 100 mA. The results of the simulation can be checked against the characterization data shown in the HMPP-386x data sheet. The APLAC model assumes the R vs. I curve can be approximated using three resistors:

RESISTANCE (OHMS)

1,000

100

10

1 0.001

0.01

0.1 1 BIAS CURRENT (mA)

10

100

Figure 4. RF Resistance vs. forward bias current @ 100 MHz using APLAC model

Rmax, Rmin, and Rvar. Where Rvar = A / Id K

6311-04 AN 1330

In this case the parameters A and K are shown in Table 1. In Avago Technologies' Advanced Design System (ADS), the current controlled resistor is implemented with a symbolically defined device (SDD). For more information on how to use these devices, refer to the Circuit Simulation manuals in ADS.

L n1

RMIN

RVAR

D1 n2

RVAR = A/IdK RMAX

Figure 5. APLAC Die Model

6311-05 AN 1330

C C C=C

DC_BLOCK DC_BLOCK1

L L L=L

R RMIN R = RMIN

SDD1P SDDNP1 I[ 1, 0] = (_v1)/(A/((1e-26)+_c1)**K) C[1] = Id R RMAX R = RMAX

DIODE DIODE1 MODEL = DIODEM1 PERIPH = TEMP = MY TEMP

DC_FEED DC_FEED1

VAR EQU DIODE_MODEL DIODEM1 Is = 1.49nA N = 2.022 Tt= 500 nsec Cjo= 0.36 pF

VAR VAR1 RMIN = 1.5 RMAX = 5000 A = 0.0183 K = 0.9327 L = 0 nH C = 0.2 pF

I_PROBE Id

Figure 6. PIN Diode Model implementation in Agilent ADS using the published APLAC parameters

Figure 6 shows the full implementation of the PIN diode model in ADS. The parameters for the SPICE diode model can be extracted from the measured DC IV curve and are also shown in Table 1. The final model includes the diode capacitance and connection inductance as shown in Figure 5. This model is valid for forward bias only when operated at frequencies above 10 Fc.

Where, Fc = 1 / 2 is the minority carrier lifetime. The figure for carrier lifetime () is an approximation for transit time (Tt). At 10 Fc and above the PIN diode behaves reliably as a variable resistor. The model will not correctly predict harmonics, however, it is useful in predicting RF resistance and the DC IV curves. This makes the APLAC model ideal for simulating PIN Diode switch and attenuator designs, where the RF resistance is varying with bias current. The APLAC model equation requires a small value of bias current in order to work. This is provided by the 1e-26 term in the symbolically defined device (SDD). If the term is omitted from the equation, the simulator will try to divide by zero and the equation will not be solved or will give an invalid result.

6311-06 AN 1330

Demo Board Design

Figure 7 shows the RF Layout of a demo board designed to allow SPDT switches to be built over a wide frequency range. Component values and results for two examples are given in this application note, at 1900 MHz and 2.45 GHz. The assembly drawing for the board is shown in Figure 8. The switch design requires a high degree of isolation between one diode and the other. To facilitate this, the high isolation, PCB pad layout for the MiniPAK has been used. The pattern uses three via holes connecting the tee-shape ground pattern to the ground plane of the board. The pattern also has the desired effect of reducing the package capacitance. A dimensioned drawing for the ground pattern may be found in the assembly information section of the HMPP386x data sheet. The initial component values for these designs were determined from the linear simulation. Avago Technologies ADS EDA was chosen as the simulator. The circuit components can then be added to the simulation circuit. The more detailed the simulation the more accurate the results will be. An accurate circuit simulation can provide the appropriate first step to a successful switch design. The transmission line section can be modeled with various micro-strip and strip-line elements available in the component library. In this case, all micro-strip sections assumed a 0.8 mm (0.031-inch) thick board and GETEC RG200D material. The inductance associated with the chip capacitors and resistors was also included in the simulation. Where possible, models were chosen from the ADS SMT component library. Models of SMT components can also be obtained from the manufacturers web sites. Manufacturing tolerances in both the active and passive components often prohibit perfect correlation.

IP 2-01

SP DT

780 MIL (19.8 mm)

1000 MIL (25.4 mm)

Figure 7. RF Layout for demo board

The model for the HMPP-3865 was created and the create/edit schematic symbol function was used from the view menu in ADS. R1 was chosen to be 390 ohms. From a 3 volts supply, R1 sets the diode bias current to approximately 5 mA. When using the APLAC die model, in the simulation, the effect of increasing or decreasing the bias current can easily be observed. The capacitors used were from ROHM MCH18 range and the inductors were TOKO types LL1105. The TOKO inductors offer high Q, with typical values of 6311-07 AN 1330 30 at 800 MHz. The printed board is designed to accept edge-mounting SMA connectors such as Johnson Components, Inc., Model 142-0701- 881. These connectors are designed to slip over the edge of 0.8 mm (0.031-inch) thick circuit boards and obviate the need to mount PCBs on a metal base plate for testing.

IP 2- 01

C1 L2

SP DT

L1 L2 C3 C2 L3 R1 C5

C2 L3

C3

C4

C4 R1 C5

Figure 8. Assembly drawing for SPDT switch

Table 2. Component Parts List for the two frequencies.

Frequency C1 C2 C3, C4 C5 L1 L2 L3 R1 Diode 1.9 GHz 2.45 GHz 5.6 pF 0402 Chip Capacitor 5.6 pF 0402 Chip Capacitor 1.0 pF 0402 Chip Capacitor 1.0 pF 0402 Chip Capacitor 6.8 pF 0402 Chip Capacitor 6.8 pF 0402 Chip Capacitor 10 nF 0402 Chip Capacitor 10 nF 0402 Chip Capacitor 33 nH LL1005-FH33N 22 nH LL1005-FH22N 18 nH LL1005-FH18N 12 nH LL1005-FH12N 27 nH LL1005-FH27N 33 nH LL1005-FH33N 390 390 HMPP-3865 HMPP-3865

The switch design uses L2 to resonate out the diode capacitance. By adjusting the value of L2 the circuit can be tuned for high isolation over a range of 100 MHz typically. Higher values of L2 can be used to move the switch maximum isolation to lower frequencies and lower values can be used to move the maximum isolation to higher frequencies. Typical values for the 1.9 GHz and 2.45 GHz design are shown in Table 2. For 1.8 GHz applications L2 would be 22 nH and for 2.3 GHz applications L2 would be 15 nH.

0 INSERTION LOSS AND ISOLATION (dB) -5 -10 -15 -20 -25 -30 -35 -40 -45 -50 1.0 1.2 1.4 1.6 1.8 2.0 2.2 2.4 2.6 FREQUENCY (GHz) INSERTION LOSS, dB ISOLATION, dB 2.8 3.0 3.2 3.4 3.6

Results

Results from the simulation of the 1.9 GHz and 2.45 GHz example are shown in Figures 9 and 10 respectively. Measured results are shown in Table 3.

Figure 9. Simulation results for 1.9 GHz High Isolation switch

0 INSERTION LOSS AND ISOLATION (dB) -5

-10 -15 -20 -25 -30 -35 -40 -45 1.0 1.2 1.4 INSERTION LOSS, dB ISOLATION, dB 1.6 1.8 2.0 2.2 2.4 2.6 FREQUENCY (GHz) 2.8 3.0 3.2 3.4 3.6

Figure 10. Simulation results for 2.45 GHz High Isolation switch

6311-09 AN 1330

6311-10 AN 1330

Table 3. Measured Insertion Loss, Isolation and Switching Speed Results.

Frequency 1.9 GHz 2.45 GHz Port1 - Port3 Insertion Loss, dB 0.5 0.6 Port1 - Port2 Isolation, dB 40 36.5 Port1 and Port3 Return Loss, dB 17, 18 17, 19 Switching speed, On/Off, nS 180/360 180/360 Output 3rd Order Intercept Point, dBm 45 45 Port 2 Return Loss, dB 0.3 0.5

Summary

0 INSERTION LOSS AND ISOLATION (dB) -5 -10 -15 -20 -25 -30 -35 -40 -45 -50 1.0 1.2 1.4 1.6 1.8 2.0 2.2 2.4 2.6 FREQUENCY (GHz) INSERTION LOSS, dB ISOLATION, dB S11, dB S33, dB 2.8 3.0 3.2 3.4 3.6

The results obtained from the demo board described in the note show the potential use of the MiniPAK HMPP-3865 in a high Isolation SPDT switch design. Low insertion loss and high isolation compare with more costly RFIC GaAs switch solutions. Example applications are GSM1800, PCS, DECT cordless phones, SDARS and 802.11b WLAN applications. Table 3 shows the typical measured results for the switch, with port 1 connected to port 3. Measured circuit results for the switch using the evaluation board for the 1.9 GHz and 2.45 GHz examples are shown in Figures 11 and 12 respectively.

References

Figure 11. Measured results for 1.9 GHz High Isolation switch

Compact HSMP-389V Transmit/Receive Switch Design, Application Note 1163 - A.R. Rixon

INSERTION LOSS AND ISOLATION (dB)

0 -5 -10 -15 -20 -25 -30 -35 -40 -45 -50 1.0 1.2 1.4

6311-11 AN 1330

Applications for the HSMP-3890 Surface Mount Switching PIN Diode, Application Note 1072 APLAC (Analysis Program for Linear Active Circuits) - Department of Electrical and Communications Engineering of the Helsinki University of Technology. Avago Technologies' Eesof Advanced Design System (ADS) electronic design automation (EDA) software for system, RF, and DSP designers who develop communications products. More information about Avago Technologies' EDA software may be found on http://www.avagotech.com. Performance data for Avago Technologies' HMPP-386x Series MiniPak Surface Mount RF PIN Diodes may be found on http://www.avagotech.com.

INSERTION LOSS, dB ISOLATION, dB S11, dB S33, dB 1.6 1.8 2.0 2.2 2.4 2.6 FREQUENCY (GHz) 2.8 3.0 3.2 3.4 3.6

Figure 12. Measured results for 2.45 GHz High Isolation switch

6311-12 AN 1330

For product information and a complete list of distributors, please go to our web site: www.avagotech.com Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies, Pte. in the United States and other countries. Data subject to change. Copyright 2006 Avago Technologies Pte. All rights reserved. 5988-8470EN - June 21, 2006

You might also like

- Designing Loop AntennasDocument18 pagesDesigning Loop AntennasCesar AvilaNo ratings yet

- Linear Amps For Mobile OperationDocument10 pagesLinear Amps For Mobile OperationIan McNairNo ratings yet

- An 762 Rev 0Document10 pagesAn 762 Rev 0Diego MotoqueroNo ratings yet

- A 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanDocument4 pagesA 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanSunil PandeyNo ratings yet

- Design and Implementation of A 10 Bit SAR ADCDocument4 pagesDesign and Implementation of A 10 Bit SAR ADCVipul ChauhanNo ratings yet

- IEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFDocument3 pagesIEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFQuoc Thang TranNo ratings yet

- Application Note 91 October 2002: Note 1: This Method Has Been Tested With The LTC4401-1 and TheDocument8 pagesApplication Note 91 October 2002: Note 1: This Method Has Been Tested With The LTC4401-1 and TheHahdNo ratings yet

- An 8-Bit 200-Msample/S Pipelined Adc With Mixed-Mode Front-End S/H CircuitDocument11 pagesAn 8-Bit 200-Msample/S Pipelined Adc With Mixed-Mode Front-End S/H CircuittkbattulaNo ratings yet

- AV02-2211EN AN - 5442 MGA-17516 07apr2011,0 PDFDocument24 pagesAV02-2211EN AN - 5442 MGA-17516 07apr2011,0 PDFAnh Bien NguyenNo ratings yet

- 130nm CMOS Technology Design of Passive UHF RFID Tag inDocument4 pages130nm CMOS Technology Design of Passive UHF RFID Tag inDuc DucNo ratings yet

- A 12-Bit 40 MS/s Pipelined ADC With Over 80 DB SFDR: Wei Qi, Yin Xiumei, Han Dandan, and Yang HuazhongDocument5 pagesA 12-Bit 40 MS/s Pipelined ADC With Over 80 DB SFDR: Wei Qi, Yin Xiumei, Han Dandan, and Yang HuazhongfirpealNo ratings yet

- MDLX Atc App Note Pi 026Document0 pagesMDLX Atc App Note Pi 026david_benavidez_3No ratings yet

- AN282 Systemizing RF Power Amplifier DesignDocument6 pagesAN282 Systemizing RF Power Amplifier DesignfahkingmoronNo ratings yet

- Motorola AN758Document16 pagesMotorola AN758xavir111No ratings yet

- AN943A Practical PICmicro Oscillator Analysis and DesignDocument14 pagesAN943A Practical PICmicro Oscillator Analysis and DesignbagopercyNo ratings yet

- A 100MHz To 500MHz Low Noise Feedback Amplifier Using ATF-54143 (AN5057 Avago)Document8 pagesA 100MHz To 500MHz Low Noise Feedback Amplifier Using ATF-54143 (AN5057 Avago)XollloXNo ratings yet

- CN0350Document7 pagesCN0350Narayan ApteNo ratings yet

- Transformer-Coupled Front-End For Wideband A/D Converters: Primary SecondaryDocument4 pagesTransformer-Coupled Front-End For Wideband A/D Converters: Primary SecondaryAvinash SharmaNo ratings yet

- Unipolar To Bipolar Analog Voltage ConversionDocument20 pagesUnipolar To Bipolar Analog Voltage ConversionGautam MonipatroNo ratings yet

- An-779 Low-Distortion 1.6 To 30 MHZ SSB Driver DesignsDocument10 pagesAn-779 Low-Distortion 1.6 To 30 MHZ SSB Driver DesignsEdward YanezNo ratings yet

- EB-104 Get 600 Watts RF From Four Power FETsDocument9 pagesEB-104 Get 600 Watts RF From Four Power FETsEdward YanezNo ratings yet

- 2010SOVC A 1V 11fJ-Conversion-Step 10bit 10MS-s A Synchronous SAR ADC in 0.18um CMOSDocument2 pages2010SOVC A 1V 11fJ-Conversion-Step 10bit 10MS-s A Synchronous SAR ADC in 0.18um CMOSDivya SivaNo ratings yet

- A High Performance 90 NM CMOS SAR ADC With HybridDocument8 pagesA High Performance 90 NM CMOS SAR ADC With HybridSounakDuttaNo ratings yet

- 20116052-Lica Term ProjectDocument12 pages20116052-Lica Term ProjectH052 Rajesh Komaravalli ECENo ratings yet

- 13.56 MHZ, Class D Push-Pull, 2KW RF GeneratorDocument17 pages13.56 MHZ, Class D Push-Pull, 2KW RF GeneratorettorepellegriniNo ratings yet

- Modelling and Simulation of Sigma-Delta ADCs in VHDL-AMSDocument5 pagesModelling and Simulation of Sigma-Delta ADCs in VHDL-AMSVitu VituNo ratings yet

- An0002 Efm32 Hardware Design ConsiderationsDocument16 pagesAn0002 Efm32 Hardware Design ConsiderationsRam SakthiNo ratings yet

- Application Note 13.56 MHZ, Class D Push-Pull, 2Kw RF Generator With Microsemi Drf1300 Power Mosfet HybridDocument28 pagesApplication Note 13.56 MHZ, Class D Push-Pull, 2Kw RF Generator With Microsemi Drf1300 Power Mosfet Hybridsatheesh_tejaaNo ratings yet

- Voltage Drop Calculation Typical CasesDocument4 pagesVoltage Drop Calculation Typical CasesKhaled ZayedNo ratings yet

- Sizing of Protective Earthing Conductor - Electrical Installation GuideDocument2 pagesSizing of Protective Earthing Conductor - Electrical Installation GuideWassim HelouNo ratings yet

- A Complete Narrow-Band Power Line Communication Node For AMRDocument6 pagesA Complete Narrow-Band Power Line Communication Node For AMRSudheer KakaniNo ratings yet

- Panasonic Inverter ManualDocument8 pagesPanasonic Inverter Manualsamernet2100% (1)

- Optimizing P-Channels for Switching and RectificationDocument5 pagesOptimizing P-Channels for Switching and RectificationTim PriceNo ratings yet

- Forward Design 300W STmicroelectronics App NoteDocument10 pagesForward Design 300W STmicroelectronics App Notecristi7521No ratings yet

- Op To CouplerDocument5 pagesOp To CouplersamponNo ratings yet

- AC Current Monitor by LM358Document14 pagesAC Current Monitor by LM358wlen2012No ratings yet

- Measuring DC Voltage in the Presence of AC SignalsDocument6 pagesMeasuring DC Voltage in the Presence of AC SignalsRangga Kusuma NegaraNo ratings yet

- Printed Circuit Board TechniquesDocument6 pagesPrinted Circuit Board TechniquesA. VillaNo ratings yet

- 1.8 V - 100 MHZ CMOS Programmable Gain AmplifierDocument4 pages1.8 V - 100 MHZ CMOS Programmable Gain AmplifierKienha LuongNo ratings yet

- Hfe1209 FreyDocument3 pagesHfe1209 Freyarunkr1No ratings yet

- Reference Design Low Cost CompassDocument4 pagesReference Design Low Cost CompassHany MaximousNo ratings yet

- P M D-A A: Martin Pospisilik, Jiri Kasacek, Michaela Mikulicova, Milan AdamekDocument6 pagesP M D-A A: Martin Pospisilik, Jiri Kasacek, Michaela Mikulicova, Milan Adamekisauro yardani altamiranda martinezNo ratings yet

- Two Wire Transmitter 4-20maDocument11 pagesTwo Wire Transmitter 4-20maEdgar MuñozNo ratings yet

- An-593 Broadband Linear Power Amplifiers Using Push-Pull TransistorsDocument13 pagesAn-593 Broadband Linear Power Amplifiers Using Push-Pull TransistorsEdward YanezNo ratings yet

- Design Note: Optimizing Performance in Uc3854 Power Factor Correction ApplicationsDocument42 pagesDesign Note: Optimizing Performance in Uc3854 Power Factor Correction ApplicationsidsufixNo ratings yet

- QRP Magnetic Loop Tuner 80-20mDocument5 pagesQRP Magnetic Loop Tuner 80-20mAnonymous yd3nqGC100% (2)

- Reduce Standby Power Drains With Ultra-Low-Current, Pulse-Frequency-Modulated (PFM) DC-DC ConvertersDocument8 pagesReduce Standby Power Drains With Ultra-Low-Current, Pulse-Frequency-Modulated (PFM) DC-DC Converterssoft4gsmNo ratings yet

- S I 4 0 1 0 A I M N G: Ntenna Nterface AND Atching Etwork UideDocument36 pagesS I 4 0 1 0 A I M N G: Ntenna Nterface AND Atching Etwork Uidehyu2123No ratings yet

- A 2GS/s 9-Bit 8-12x Time-Interleaved Pipeline-SAR ADC For A PMCW Radar in 28nm CMOSDocument4 pagesA 2GS/s 9-Bit 8-12x Time-Interleaved Pipeline-SAR ADC For A PMCW Radar in 28nm CMOSburakgonenNo ratings yet

- 90W Smps For Monitors With Constant Power Limiting Function: AN1133 Application NoteDocument11 pages90W Smps For Monitors With Constant Power Limiting Function: AN1133 Application NoteMadein ChinaNo ratings yet

- RectennaDocument4 pagesRectennarkhanna1965No ratings yet

- An436 Application NoteDocument9 pagesAn436 Application NoteEdgar MuñozNo ratings yet

- Low Swing Signaling Using A Dynamic Diode-Connected DriverDocument4 pagesLow Swing Signaling Using A Dynamic Diode-Connected DriverAkash RaykarNo ratings yet

- DiDocument6 pagesDipani256No ratings yet

- Class D TheoryDocument10 pagesClass D TheorymushabagnrNo ratings yet

- An 8-Bit 200-MSample-s Pipelined ADC With Mixed-Mode Front-End S-H CircuitDocument12 pagesAn 8-Bit 200-MSample-s Pipelined ADC With Mixed-Mode Front-End S-H CircuitMohsen Vafaei ZadehNo ratings yet

- 06616415Document5 pages06616415jitu_4No ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet