Professional Documents

Culture Documents

Latches and Flip-Flops: Experiment E10

Uploaded by

Resy ApolinarioOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Latches and Flip-Flops: Experiment E10

Uploaded by

Resy ApolinarioCopyright:

Available Formats

EXPERIMENT E10 LATCHES AND FLIP-FLOPS E10.1.

OBJECTIVE

In the present experiment, the student will experimentally verify the truth table of: an SR latch synthesized using the 7400 IC NAND gates only; and a positive-edge triggered D flip-flop using one of the two D flip-flops on the 74HC74A IC which contains two positive-edge triggered D flip-flops with clear and preset inputs The 7474 IC is a generic IC manufactured by various manufacturers. The pin diagram of the 74HC74 IC is provided in the attached portions of the spec sheets from Fairchild Semiconductor as well as Motorola. For detailed spec sheets, visit, for instance, the Fairchild Semiconductor web site (http://www.fairchildsemi.com/ds/DM/)

E10.2.

INTRODUCTION

You have learnt in the class that gates provide a building block for combinational circuits, i.e., deterministic circuits in which, once the inputs are specified, the outputs can be directly determined. Thus, combinational circuits contain no memory. The other class of logic circuits are the sequential circuits, where the output or next state of the circuit depends not only on the inputs but also on the present state of the circuit. The sequential circuits thus contain memory elements. The building blocks of sequential circuits are the latches and the flip-flops. The difference between a latch and a flip-flop is that a latch does not have a clock signal input while a flip-flop does. A latch is thus an asynchronous bistable circuit whose output or next state depends purely on the inputs (which are basically SET and RESET entities) and the present state of the circuit. A flip-flop, on the other hand, is a synchronous circuit in which the output changes state only when triggered by the clock signal, i.e., the changes in the output occur in synchronization with the clock signal. The flip-flop is usually one of the following: positive-edge-triggered (as in the presently used 74HC74A D flip-flops) where changes in the output happen only at the positive edges (or rising edges) of the clock 1

signal, depending additionally, of course, on the values of the inputs just prior to the positive edges of the clock signal negative-edge-triggered (here the changes in the output happen only at the negative edges (or falling edges) of the clock signal, depending on the values of the inputs just prior to the negative edges) level-triggering where the inputs of the flip-flop cause changes in the output only when the clock signal is HIGH, as in the simple case of clocked or gated SR flip-flop examined in the present experiment [A more practical type of level-triggered flip-flop is called pulse-triggered or master-slave which actually consists of two flip-flops in tandem, with the resulting property of the circuit being that the circuit responds to the values of the inputs just prior to the positive edge of the clock signal, but changes in the output happen only at the following negative edge of the clock signal. A discussion of the master-slave flip-flop is beyond the scope of the present course] Most computer and digital circuits are synchronous, i.e., all of the constituent sequential circuits respond only to a master clock signal. In this way, complications arising from the delay time in going through each component in the circuit are avoided.

E10.3.

E10.3.1.

PRE-LAB

In the class, you were shown how to synthesize an SR latch using NOR gates, with the

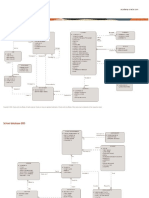

inputs being S (or SET) and R (or RESET) and the outputs being Q and and its complement Q. Note that in the diagrams a bar on top of a symbol is used to represent the complement function. In Fig. E10.1, you are given an alternative synthesis of an SR latch using only NAND gates. While the inputs are shown as the complement functions S and R, clearly, if you want the inputs to be S and R, all you have to do is to put inverters in front of the S and R terminals. In the present prelab, you are required to derive the truth table of the circuit in Fig. E10.1 and demonstrate that it is the same as the one derived in class for the SR latch made using NOR gates only. E10.3.2. Derive the truth table for the SR latch in Fig. E10.1 using Electronics Workbench,

making sure to SET or RESET the latch depending on whether you want the present state of Q to be 2

1 or 0, respectively, before applying the new inputs. Use a 5V battery to simulate a logic 1 value for an input quantity and a ground to simulate a logic 0 for an input quantity.

Fig, E10.1. Basic SR flip-flop with inverted inputs

Fig. E10.2. Clocked SR flip-flop

E10.3. Timing diagram for SR flip-flop of Fig. 10.2.

E10.3.3.

Complete the timing diagram in Fig. E10.3 for S1, R1, and Q for the clocked SR

flip-flop of Fig. E10.2, assuming the flip-flop to be initially RESET. Note that S1 and R1 are the inputs of the SR latch which follows the outputs of AND gates that are obtained when the inversion circles are separated out from the input NAND gates in Fig. E10.2. In other words, S1 is the output of the AND gate component of the NAND gate with inputs S and CLK (clock signal).

E10.4.

BREADBOARDING LAB

a) Connect up the SR latch circuit shown in Fig. E10.4, which is the same as the circuit in Fig. E10.1 except that it also has a simple circuitry for applying logic 0 and 1 inputs to the SR latch. The two switches shown are normally open (NO) debounced switches. Experimentally verify the truth table for the SR latch. Note that, when an NO switch is closed, the input terminal of the SR latch to which the switch is connected is grounded, i.e., it is at logic level 0. If, on the other hand, the switch 4

is open, the same terminal is at 5V (since no current is drawn by the gate and, thus, the potential drop across the resistor is zero) or at logic level 1.

Fig. E10.4. Circuit showing how logic inputs are applied to the SR latch b) Carefully study the pin diagram and truth table (or function table) in the attached specs sheets for the 74HC74A dual D flip-flop IC. Notice that the flip-flops have PRESET and CLEAR inputs, which can override the D input to the flip-flop. The synthesis of a positive-edge-triggered D flip-flop using gates is quite complex as shown in the manufacturer-supplied circuit shown in Fig. E10.5. The D flip-flop will be used in the present experiment with the PRESET terminal (PIN 4 or 10 of the IC) and CLEAR terminal (PIN 4 or 10) both connected to +5V. The PRESET and CLEAR inputs are then disabled, i.e., they are as good as not being present. By disabling these inputs, the remaining inputs are D and the CLOCK signal. From the general truth table for the D flip-flop given in the specs, obtain the simplified truth table that applies for the case where the PRESET and CLEAR inputs are disabled. Note that the D flip-flop is positive-edge-triggered, i.e., changes in the value of the flipflop output Q happen only at the positive edges of the clock signal, with the value of D 5

just prior to the positive edge of the clock signal becoming the value of output Q immediately after the positive edge of the clock signal. Experimentally verify the truth table for the D flip flop for the simplified case where the PRESET and CLEAR inputs are disabled. Apply the D and clock inputs to the flip-flop using the same scheme as in Fig. E10.4 except that you will use a normally closed (NC) switch for the clock input, thereby creating a positive edge when the switch is opened. When the switch is closed, the clock signal is at 0V; when the switch is opened, the clock signal is at +5V. The vertical edge of the clock signal which changes the value of the clock signal from 0V to +5V is called the positive edge, while the vertical edge which changes the value of the clock signal from +5V to 0V is called the negative edge. The circuit for determining the truth table for the D flip-flop is shown in Fig. E10.6

Fig. E10.5. Expanded logic diagram for one of the D flip-flops of the 74HC74A IC

Fig. E10.6. Circuit for obtaining the truth table for the positive-edge-triggered D flip flop with CLEAR (or RESET) and SET inputs disabled

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Final Demo ICT Semi-Detailed Lesson PlanDocument6 pagesFinal Demo ICT Semi-Detailed Lesson PlanJo Stream80% (45)

- Sequential CircuitsDocument53 pagesSequential CircuitsbrsreddyNo ratings yet

- 555 Timer Monostable OperationDocument13 pages555 Timer Monostable OperationGrigore ManNo ratings yet

- Neural Networks Desing - Martin T. Hagan - 2nd EditionDocument1,013 pagesNeural Networks Desing - Martin T. Hagan - 2nd EditionYeisson Muñoz100% (1)

- SAE ProjectDocument200 pagesSAE ProjectKhai Huynh100% (3)

- Sap HR FaqDocument36 pagesSap HR FaqAnonymous 5mSMeP2jNo ratings yet

- Fundamentals of Switching TheoryDocument245 pagesFundamentals of Switching TheoryMichelle Arellano100% (1)

- Oracle Apps Technical Interview Questions Answers GuideDocument7 pagesOracle Apps Technical Interview Questions Answers GuideJohn StephensNo ratings yet

- Sap IntertrDocument28 pagesSap IntertrAnonymous 4PnhkGJ0PNo ratings yet

- The Data Centric Security ParadigmDocument10 pagesThe Data Centric Security ParadigmLuke O'ConnorNo ratings yet

- Digital LabDocument51 pagesDigital LabBala SubramanianNo ratings yet

- Access the new Azure Portal and view subscription information in the dashboardDocument2 pagesAccess the new Azure Portal and view subscription information in the dashboardSaikrishNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Er Sacchu SrivastavaNo ratings yet

- Report 1 (D2, Digital)Document10 pagesReport 1 (D2, Digital)Kian YingNo ratings yet

- Chapter 4 Flip Flop-ROBIAHDocument50 pagesChapter 4 Flip Flop-ROBIAHIqmal Shah Putra50% (2)

- Chapter 4 Flip Flop-ROBIAHDocument50 pagesChapter 4 Flip Flop-ROBIAHKelvin YipNo ratings yet

- D Flip-FlopDocument35 pagesD Flip-FlopSwati Kasht100% (1)

- Experiment 9 (Flip Flops)Document7 pagesExperiment 9 (Flip Flops)groupidb3100% (3)

- Technological Studies: Applied Electronics (AH) Sequential Logic DevicesDocument116 pagesTechnological Studies: Applied Electronics (AH) Sequential Logic DevicesPham PunNo ratings yet

- Flip FlopsDocument60 pagesFlip FlopsA10-14Rajat KumarNo ratings yet

- Lab Manual FOR Computer Organization LabDocument13 pagesLab Manual FOR Computer Organization Labhifzan786No ratings yet

- SSN College of Engineering, It Highway, KALAVAKKAM-603 110: Lab RecordDocument93 pagesSSN College of Engineering, It Highway, KALAVAKKAM-603 110: Lab RecordKarthikai SelviNo ratings yet

- Fundamentals of FlipflopsDocument52 pagesFundamentals of FlipflopskanchiNo ratings yet

- Flip-Flops: Introduction - Basic Flip-Flop CircuitDocument11 pagesFlip-Flops: Introduction - Basic Flip-Flop Circuitniharika6431No ratings yet

- Sequential CircuitsDocument134 pagesSequential CircuitsRajat KumarNo ratings yet

- Flip Flop Mealy and Moore ModelDocument25 pagesFlip Flop Mealy and Moore Modelsurajpb1989100% (1)

- Ade Unit 5Document41 pagesAde Unit 5KUMAR SNo ratings yet

- Chp1 - Latches and Flip-FlopsDocument44 pagesChp1 - Latches and Flip-FlopsAbnen OngNo ratings yet

- CSE 1203 Introduction To Sequential Circuits and FFDocument27 pagesCSE 1203 Introduction To Sequential Circuits and FFgbikornoNo ratings yet

- Laboratory Experiment # 4 "An Introduction To The 555 Integrated Circuit Timer"Document26 pagesLaboratory Experiment # 4 "An Introduction To The 555 Integrated Circuit Timer"Moris MascariñasNo ratings yet

- MultivibratorsDocument22 pagesMultivibratorsNGOUNENo ratings yet

- Introduction to Sequential DevicesDocument62 pagesIntroduction to Sequential DevicesSarath Chandra SNo ratings yet

- Ontrollability and Observability of Flip-Flops: Set Reset ClockDocument22 pagesOntrollability and Observability of Flip-Flops: Set Reset ClockShashank S KudlurNo ratings yet

- cs302 Short Notes and Subjetive Paper For MidtermDocument52 pagescs302 Short Notes and Subjetive Paper For MidtermchashmanmuneerNo ratings yet

- Sequential CircuitsDocument22 pagesSequential CircuitsBaeNo ratings yet

- CounterDocument22 pagesCounterMahesh MahiNo ratings yet

- CS302 Mid Term Solved PapersDocument51 pagesCS302 Mid Term Solved PapersattiqueNo ratings yet

- Logic Gates & AmplifiersDocument103 pagesLogic Gates & AmplifiersAnusha NatarajanNo ratings yet

- Unit 4Document98 pagesUnit 4Shinigami DandyNo ratings yet

- D and JK FFDocument22 pagesD and JK FFRawan AyyoubNo ratings yet

- Flip-Flops: The Building Block of Sequential Logic CircuitsDocument90 pagesFlip-Flops: The Building Block of Sequential Logic CircuitsXkip DoomzNo ratings yet

- Multiplexer, Decoder and FlipflopDocument10 pagesMultiplexer, Decoder and FlipflopShachi P GowdaNo ratings yet

- Flip-Flop LabDocument7 pagesFlip-Flop Labjose mirandaNo ratings yet

- Test 1Document6 pagesTest 1kavana a ganigaNo ratings yet

- Conversion of FlipDocument13 pagesConversion of FlipJohn Brix BalisterosNo ratings yet

- DTE Question Bank SolutionDocument15 pagesDTE Question Bank SolutionkhantaukirhasanNo ratings yet

- 555 Timer Lab: Astable and Monostable MultivibratorsDocument10 pages555 Timer Lab: Astable and Monostable Multivibratorsmanaj_mohapatra2041No ratings yet

- Programmable Array Logic VHDL EnotesDocument15 pagesProgrammable Array Logic VHDL Enotesshrikant_talawarNo ratings yet

- Unit II DpcoDocument41 pagesUnit II DpcoSunil Anandh ITNo ratings yet

- 555 Timer Astable Circuit Frequency CalculatorDocument8 pages555 Timer Astable Circuit Frequency CalculatorManuel BalasbasNo ratings yet

- Astable Multivibrator Using 555 TimerDocument12 pagesAstable Multivibrator Using 555 TimerΔημητριος ΣταθηςNo ratings yet

- UNIT III Practice3Document12 pagesUNIT III Practice3Charly Moo AyalaNo ratings yet

- CSE231 Lecture 6Document31 pagesCSE231 Lecture 6Rayhan Amin 2212830042No ratings yet

- How Flip Flops Work as Basic Memory UnitsDocument6 pagesHow Flip Flops Work as Basic Memory UnitsSriharsha Pidaparthi100% (1)

- Sequential Logic Circuits ExplainedDocument56 pagesSequential Logic Circuits ExplainedBonsa100% (1)

- Name of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabDocument7 pagesName of The Experiment: Sequential Circuit Design - Latch, Flip Flop and Registers Important: Submit Your Prelab at The Beginning of The LabAurongo NasirNo ratings yet

- DDCO QBDocument20 pagesDDCO QB333jayanth333No ratings yet

- Digital Logic Design Chapter 6.... FullDocument36 pagesDigital Logic Design Chapter 6.... FullOkezaki TemoyoNo ratings yet

- Arithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitDocument22 pagesArithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitBadrul Afif ImranNo ratings yet

- Co Lab ManualDocument22 pagesCo Lab ManualSachin Saxena100% (2)

- Computer Architecture 1Document39 pagesComputer Architecture 1ARAFAT GaamanNo ratings yet

- Timers PDFDocument43 pagesTimers PDFDeepak S SNo ratings yet

- Mak 439E Computer Controlled System Design Experiment 1. Digital Electronic Circuits and Logic DesignDocument7 pagesMak 439E Computer Controlled System Design Experiment 1. Digital Electronic Circuits and Logic DesignIndumathy ThanikachalamNo ratings yet

- Introduction To Logic Gates Exp2Document11 pagesIntroduction To Logic Gates Exp2Tamim ANo ratings yet

- Lab05 Flip FlopsDocument8 pagesLab05 Flip Flopskhanjamil12No ratings yet

- BistabileDocument11 pagesBistabileRazvan IonutNo ratings yet

- Physics Laboratory Report: Experiment#4Document14 pagesPhysics Laboratory Report: Experiment#4M Salman RyanNo ratings yet

- Comex Advisory 2014 05Document3 pagesComex Advisory 2014 05Eli Benjamin Nava TaclinoNo ratings yet

- Loi 33-2012e-Library - PNP Document Management SystemDocument6 pagesLoi 33-2012e-Library - PNP Document Management SystemResy Apolinario100% (3)

- Introduction Power Supply Rev7 22Document19 pagesIntroduction Power Supply Rev7 22Resy ApolinarioNo ratings yet

- Chapter 07Document35 pagesChapter 07api-26103409No ratings yet

- 5 Band Graphic EqualiserDocument2 pages5 Band Graphic EqualiserDhivya SureshKumarNo ratings yet

- Job VacancyDocument1 pageJob VacancyResy ApolinarioNo ratings yet

- Om0076 2014Document4 pagesOm0076 2014Resy ApolinarioNo ratings yet

- (Ymya) 5-Band Graphic EqualizerDocument1 page(Ymya) 5-Band Graphic EqualizerDivyanshu YadavNo ratings yet

- Computer Health and SafetyDocument6 pagesComputer Health and SafetyResy ApolinarioNo ratings yet

- Pag-IBIG Branch Areas of CoverageDocument3 pagesPag-IBIG Branch Areas of CoverageResy ApolinarioNo ratings yet

- Introduction Power Supply Rev7 22Document19 pagesIntroduction Power Supply Rev7 22Resy ApolinarioNo ratings yet

- a) 30° = π/6 radiansb) 1 = 2π radians c) 120° = 2π/3 radiansd) 3π/4 radians = 135°e) 2 = 4π radiansf) 4π/3 radians = 240° g) 270° = 3π/2 radiansh) -1 = -2π radiansi) -π/2 radians = -90Document39 pagesa) 30° = π/6 radiansb) 1 = 2π radians c) 120° = 2π/3 radiansd) 3π/4 radians = 135°e) 2 = 4π radiansf) 4π/3 radians = 240° g) 270° = 3π/2 radiansh) -1 = -2π radiansi) -π/2 radians = -90Resy ApolinarioNo ratings yet

- IP Address ClassesDocument2 pagesIP Address ClassesDouglas MoodyNo ratings yet

- Fundamentals of Logic Design 6th Edition Chapter 11Document3 pagesFundamentals of Logic Design 6th Edition Chapter 11Jessica Garner50% (2)

- Fundamentals of Logic Design 6th Edition Chapters 16-18Document20 pagesFundamentals of Logic Design 6th Edition Chapters 16-18Resy ApolinarioNo ratings yet

- Algebra 1 End-of-Course and Geometry End-of-Course Assessments Reference SheetDocument2 pagesAlgebra 1 End-of-Course and Geometry End-of-Course Assessments Reference SheetResy Apolinario100% (1)

- Trig 1Document32 pagesTrig 1Resy ApolinarioNo ratings yet

- Ip Addressing TutorDocument69 pagesIp Addressing Tutorb_y4uNo ratings yet

- Kirchoffs Law With Cramers RuleDocument14 pagesKirchoffs Law With Cramers RuleRoy BernardNo ratings yet

- Basics of TrigonometryDocument11 pagesBasics of TrigonometryMuralikrishna SingamaneniNo ratings yet

- MemoryDocument62 pagesMemoryLKNo ratings yet

- a) 30° = π/6 radiansb) 1 = 2π radians c) 120° = 2π/3 radiansd) 3π/4 radians = 135°e) 2 = 4π radiansf) 4π/3 radians = 240° g) 270° = 3π/2 radiansh) -1 = -2π radiansi) -π/2 radians = -90Document39 pagesa) 30° = π/6 radiansb) 1 = 2π radians c) 120° = 2π/3 radiansd) 3π/4 radians = 135°e) 2 = 4π radiansf) 4π/3 radians = 240° g) 270° = 3π/2 radiansh) -1 = -2π radiansi) -π/2 radians = -90Resy ApolinarioNo ratings yet

- Photoelectric EXP84Document5 pagesPhotoelectric EXP84Resy ApolinarioNo ratings yet

- Do's & Dont's N Assemblng PCDocument1 pageDo's & Dont's N Assemblng PCResy ApolinarioNo ratings yet

- Types of RAM and ROMDocument6 pagesTypes of RAM and ROMTinu Elza Vinu100% (1)

- Types of RAM and ROMDocument6 pagesTypes of RAM and ROMTinu Elza Vinu100% (1)

- 2 Fundamentals of Electronic DevicesDocument77 pages2 Fundamentals of Electronic DevicesResy ApolinarioNo ratings yet

- Libros Vs EbooksDocument19 pagesLibros Vs EbooksOscarito ArriagadaNo ratings yet

- Dynamic ProgrammingDocument52 pagesDynamic ProgrammingattaullahchNo ratings yet

- Fundamentals of Programming: Course OutlineDocument32 pagesFundamentals of Programming: Course OutlineAngelina Febriany SimarmataNo ratings yet

- OCCAM2DDocument12 pagesOCCAM2Daoeuaoeu8No ratings yet

- Nemo File Format 2.19Document456 pagesNemo File Format 2.19Ignacio Alonso Montenegro Pizarro100% (2)

- Key Office 2013Document4 pagesKey Office 2013Mas GunawanNo ratings yet

- SamDocument21 pagesSamPrateek SharanNo ratings yet

- Scilab Recipe 3 - Xcos Blocks Seasoning - Scilab NinjaDocument8 pagesScilab Recipe 3 - Xcos Blocks Seasoning - Scilab NinjaWendell Kim LlanetaNo ratings yet

- Data Structure Practical - MCA Idol Shree Ram CollegeDocument65 pagesData Structure Practical - MCA Idol Shree Ram CollegeUnknownNo ratings yet

- Nota de Aplicacion - PicoPower BasicsDocument7 pagesNota de Aplicacion - PicoPower Basicsgusti072No ratings yet

- Nexpose Enterprise Edition: Vulnerability Management To Combat Today's ThreatsDocument2 pagesNexpose Enterprise Edition: Vulnerability Management To Combat Today's ThreatsWaqasMirzaNo ratings yet

- Add String ExtensionsDocument6 pagesAdd String Extensionsinfo.glcom5161No ratings yet

- Morphology PaperDocument11 pagesMorphology PaperAndre Desra IlhamNo ratings yet

- PLSQL Schema ERD and Table DesignsDocument8 pagesPLSQL Schema ERD and Table DesignsSoham GholapNo ratings yet

- hw2 AnsDocument5 pageshw2 AnsJIBRAN AHMEDNo ratings yet

- Pei-Bai Zhou - Numerical Analysis of Electromagnetic FieldsDocument418 pagesPei-Bai Zhou - Numerical Analysis of Electromagnetic FieldsTienRienNo ratings yet

- Johnson's Algorithm For Optimal Scheduling Of Multi-Machine SystemsDocument8 pagesJohnson's Algorithm For Optimal Scheduling Of Multi-Machine SystemsBabyCoder HvhNo ratings yet

- Problems On Poisson DistributionDocument4 pagesProblems On Poisson DistributionMomanyi IvyNo ratings yet

- Temperature Controlled Fan Using PIC 16F877A - GadgetronicxDocument8 pagesTemperature Controlled Fan Using PIC 16F877A - Gadgetronicxdevchandar100% (1)

- Zenith ERP Solutions for Staffing, Real Estate and Telecom IndustriesDocument16 pagesZenith ERP Solutions for Staffing, Real Estate and Telecom IndustriesChinmay MohapatraNo ratings yet

- Antonius Steven Dimas Prasetya Sinaga - Tugas11Document4 pagesAntonius Steven Dimas Prasetya Sinaga - Tugas11Steven SinagaNo ratings yet

- GHG Protocol Guidance for Assessing Emissions from ICT Products and ServicesDocument6 pagesGHG Protocol Guidance for Assessing Emissions from ICT Products and ServicesNikhil AnandNo ratings yet