Professional Documents

Culture Documents

Max7426 Max7427

Uploaded by

ridzim4638Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Max7426 Max7427

Uploaded by

ridzim4638Copyright:

Available Formats

19-1710; Rev 0; 4/00

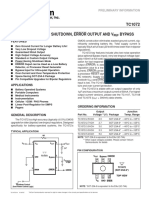

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters

General Description

The MAX7426/MAX7427 5th-order, lowpass, elliptic, switched-capacitor filters (SCFs) operate from a single +5V (MAX7426) or +3V (MAX7427) supply. The devices draw only 0.8mA of supply current and allow corner frequencies from 1Hz to 12kHz, making them ideal for low-power post-DAC filtering and anti-aliasing applications. They can be put into a low-power mode, reducing supply current to 0.2A. Two clocking options are available: self-clocking (through the use of an external capacitor) or external clocking for tighter cutoff-frequency control. An offset-adjust pin allows for adjustment of the DC output level. The MAX7426/MAX7427 deliver 37dB of stopband rejection and a sharp rolloff with a transition ratio of 1.25. Their fixed response limits the design task to selecting a clock frequency. o 5th-Order, Elliptic Lowpass Filters o Low Noise and Distortion: -80dB THD + Noise o Clock-Tunable Corner Frequency (1Hz to 12kHz) o Single-Supply Operation +5V (MAX7426) +3V (MAX7427) o Low Power 0.8mA (Operating Mode) 0.2A (Shutdown Mode) o Available in 8-Pin MAX/PDIP Packages o Low Output Offset: 4mV

Features

MAX7426/MAX7427

Applications

ADC Anti-Aliasing Post-DAC Filtering CT2 Base Stations Speech Processing

PART MAX7426CUA MAX7426CPA MAX7426EUA MAX7426EPA MAX7427CUA MAX7427CPA MAX7427EUA MAX7427EPA

Ordering Information

TEMP. RANGE 0C to +70C 0C to +70C -40C to +85C -40C to +85C 0C to +70C 0C to +70C -40C to +85C -40C to +85C PIN-PACKAGE 8 MAX 8 Plastic DIP 8 MAX 8 Plastic DIP 8 MAX 8 Plastic DIP 8 MAX 8 Plastic DIP

Selector Guide

PART MAX7426 MAX7427 TRANSITION RATIO r = 1.25 r = 1.25 OPERATING VOLTAGE (V) +5 +3

Typical Operating Circuit

VSUPPLY

Pin Configuration

TOP VIEW

0.1F VDD INPUT IN SHDN OUT OUTPUT COM 1 IN 2 GND COM GND OS 0.1F 3 8 7 CLK SHDN OS OUT

MAX7426 MAX7427

CLOCK CLK

MAX7426 MAX7427

6 5

VDD 4

MAX/PDIP

________________________________________________________________ Maxim Integrated Products

For free samples and the latest literature, visit www.maxim-ic.com or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters MAX7426/MAX7427

ABSOLUTE MAXIMUM RATINGS

VDD to GND ..............................................................-0.3V to +6V IN, OUT, COM, OS, CLK, SHDN ................-0.3V to (VDD + 0.3V) OUT Short-Circuit Duration.......................................................1s Continuous Power Dissipation (TA = +70C) 8-Pin MAX (derate 4.1mW/C above +70C) .............330mW 8-Pin PDIP (derate 6.90mW/C above +70C).............552mW Operating Temperature Ranges MAX742 _C_A ....................................................0C to +70C MAX742 _E_A .................................................-40C to +85C Storage Temperature Range .............................-65C to +160C Lead Temperature (soldering, 10s) .................................+300C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICSMAX7426

(VDD = +5V, filter output measured at OUT, 10k || 50pF load to GND at OUT, SHDN = VDD, OS = COM, 0.1F from COM to GND, fCLK = 100kHz, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25C.) PARAMETER FILTER Corner-Frequency Range Clock-to-Corner Ratio Clock-to-Corner Tempco Output Voltage Range Output Offset Voltage DC Insertion Gain with Output Offset Removed Total Harmonic Distortion plus Noise Offset Voltage Gain THD+N AOS VOFFSET VIN = VCOM = VDD / 2 VCOM = VDD / 2 (Note 2) fIN = 200Hz, VIN = 4Vp-p, measurement bandwidth = 22kHz OS to OUT Input, COM externally driven COM Voltage Range VCOM Output, COM internally driven Input Voltage Range at OS Input Resistance at COM Clock Feedthrough Resistive Output Load Drive Maximum Capacitive Load at OUT Input Leakage Current at COM Input Leakage Current at OS CLOCK Internal Oscillator Frequency Clock Output Current (internal oscillator mode) Clock Input High Clock Input Low fOSC ICLK VIH VIL 4.5 0.5 COSC = 1000pF (Note 3) 13.5 17.5 8 21.5 12.5 kHz A V V RL CL SHDN = GND, VCOM = 0 to VDD VOS = 0 to VDD VOS RCOM TA = +25C 10 50 Measured with respect to COM 90 VDD - 0.5 2 VDD - 0.2 2 0 0.25 4 0.2 -81 +1 VDD 2 VDD 2 0.1 130 5 1 500 0.2 0.2 10 10 VDD + 0.5 2 V VDD + 0.2 2 V k mVp-p k pF A A fC fCLK/fC (Note 1) 0.001 to 9 100:1 10 VDD - 0.25 25 0.4 ppm/C V mV dB dB V/V kHz SYMBOL CONDITIONS MIN TYP MAX UNITS

_______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters

ELECTRICAL CHARACTERISTICSMAX7426 (continued)

(VDD = +5V, filter output measured at OUT, 10k || 50pF load to GND at OUT, SHDN = VDD, OS = COM, 0.1F from COM to GND, fCLK = 100kHz, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25C.) PARAMETER POWER REQUIREMENTS Supply Voltage Supply Current Shutdown Current Power-Supply Rejection Ratio SHUTDOWN SHDN Input High SHDN Input Low SHDN Input Leakage Current VSDH VSDL V SHDN = 0 to VDD 0.2 4.5 0.5 10 V V A VDD IDD I SHDN PSRR Operating mode, no load SHDN = GND Measured at DC 4.5 0.8 0.2 70 5.5 1.0 1 V mA A dB SYMBOL CONDITIONS MIN TYP MAX UNITS

MAX7426/MAX7427

ELECTRICAL CHARACTERISTICSMAX7427

(VDD = +3V, filter output measured at OUT pin, 10k || 50pF load to GND at OUT, SHDN = VDD, OS = COM, 0.1F from COM to GND, fCLK = 100kHz, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25C.) PARAMETER FILTER CHARACTERISTICS Corner-Frequency Range Clock-to-Corner Ratio Clock-to-Corner Tempco Output Voltage Range Output Offset Voltage DC Insertion Gain with Output Offset Removed Total Harmonic Distortion plus Noise Offset Voltage Gain COM Voltage Range Input Voltage Range at OS Input Resistance at COM Clock Feedthrough Resistance Output Load Drive Maximum Capacitive Load at OUT Input Leakage Current at COM Input Leakage Current at OS RL CL SHDN = GND, VCOM = 0 to VDD VOS = 0 to VDD THD+N AOS VCOM VOS RCOM TA = +25C 10 50 Measured with respect to COM 90 VOFFSET VIN = VCOM = VDD / 2 VCOM = VDD / 2 (Note 2) fIN = 200Hz, VIN = 2.5Vp-p, measurement bandwidth = 22kHz OS to OUT VDD - 0.1 2 0 0.25 4 0.2 -79 +1 VDD 2 0.1 130 3 1 500 0.2 0.2 10 10 VDD + 0.1 2 fC fCLK/fC (Note 1) 0.001 to 12 100:1 10 VDD - 0.25 25 0.4 ppm/C V mV dB dB V/V V V k mVp-p k pF A A kHz SYMBOL CONDITIONS MIN TYP MAX UNITS

_______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters MAX7426/MAX7427

ELECTRICAL CHARACTERISTICSMAX7427 (continued)

(VDD = +3V, filter output measured at OUT pin, 10k || 50pF load to GND at OUT, SHDN = VDD, OS = COM, 0.1F from COM to GND, fCLK = 100kHz, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25C.) PARAMETER CLOCK Internal Oscillator Frequency Clock Output Current (internal oscillator mode) Clock Input High Clock Input Low POWER REQUIREMENTS Supply Voltage Supply Current Shutdown Current Power-Supply Rejection Ratio SHUTDOWN SHDN Input High SHDN Input Low SHDN Input Leakage Current VSDH VSDL V SHDN = 0 to VDD 0.2 2.5 0.5 10 V V A VDD IDD I SHDN PSRR Operating mode, no load SHDN = GND Measured at DC 2.7 0.75 0.2 70 3.6 1.0 1 V mA A dB fOSC ICLK VIH VIL COSC = 1000pF (Note 3) VCLK = 0 or 3V 2.5 0.5 13.5 17.5 7.5 21.5 12.5 kHz A V V SYMBOL CONDITIONS MIN TYP MAX UNITS

ELLIPTIC FILTER CHARACTERISTICS (r = 1.25)

(VDD = +5V for MAX7426, VDD = +3V for MAX7427, filter output measured at OUT, 10k || 50pF load to GND at OUT, SHDN = VDD, VCOM = VOS = VDD / 2, fCLK = 100kHz, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25C.) (Note 3) PARAMETER fIN = 0.38fC fIN = 0.68fC fIN = 0.87fC Insertion Gain with DC Gain Error Removed (Note 4) fIN = 0.97fC fIN = fC fIN = 1.25fC fIN = 1.43fC fIN = 3.25fC CONDITIONS MIN -0.4 -0.4 -0.4 -0.4 -0.7 TYP -0.2 0.2 -0.2 0.2 -0.2 -38.5 -37.2 -37.2 MAX 0.4 0.4 0.4 0.4 0.2 -34 -35 -35 dB UNITS

Note 1: The maximum fC is defined as the clock frequency fCLK = 100 fC at which the peak SINAD drops to 68dB with a sinusoidal input at 0.2fC. Note 2: DC insertion gain is defined as VOUT / VIN. Note 3: fOSC (kHz) 17.5 103 / COSC (COSC in pF). Note 4: The input frequencies, fIN, are selected at the peaks and troughs of the ideal elliptic frequency responses.

_______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters MAX7426/MAX7427

Typical Operating Characteristics

(VDD = +5V for MAX7426, VDD = +3V for MAX7427, fCLK = 100kHz, SHDN = VDD, VCOM = VOS = VDD / 2, TA = +25C, unless otherwise noted.)

FREQUENCY RESPONSE

MAX7426/27-02

PASSBAND FREQUENCY RESPONSE

MAX7426/27-04

PHASE RESPONSE

-50 PHASE SHIFT (DEGREES) -100 -150 -200 -250 -300 -350 -400 fC = 1kHz r = 1.25

MAX7426/27-06

10 0 -10 GAIN (dB) fC = 1kHz r = 1.25

0.4 0.2 0 GAIN (dB) -0.2 -0.4 -0.6 -0.8 -1.0 fC = 1kHz r = 1.25 0 0.2 0.4 0.6 0.8

-20 -30 -40 -50 -60 -70 0 1 2 3 4 5 INPUT FREQUENCY (kHz)

1.0

0.2

0.4

0.6

0.8

1.0

1.2

INPUT FREQUENCY (kHz)

INPUT FREQUENCY (kHz)

SUPPLY CURRENT vs. SUPPLY VOLTAGE

MAX7426/27-07

SUPPLY CURRENT vs. TEMPERATURE

0.86 0.84 SUPPLY CURRENT (mA) 0.82 0.80 0.78 0.76 0.74 0.72 0.70 VDD = +3V VDD = +5V

MAX7426/27-08

0.82 0.80 SUPPLY CURRENT (mA) 0.78 0.76 0.74 0.72 0.70 2.5 3.0 3.5 4.0 4.5 5.0

0.88

0.68 5.5 -60 -40 -20 0 20 40 60 80 100 SUPPLY VOLTAGE (V) TEMPERATURE (C)

_______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters MAX7426/MAX7427

Typical Operating Characteristics (continued)

(VDD = +5V for MAX7426, VDD = +3V for MAX7427, fCLK = 100kHz, SHDN = VDD, VCOM = VOS = VDD / 2, TA = +25C, unless otherwise noted.)

MAX7426 TOTAL HARMONIC DISTORTION PLUS NOISE vs. INPUT SIGNAL AMPLITUDE

-10 -20 THD + NOISE (dB) -30 -40 -50 -60 -70 -80 -90 0 1 2 A 3 4 5 B SEE TABLE 1.

MAX7426/27-10

MAX7427 TOTAL HARMONIC DISTORTION PLUS NOISE vs. INPUT SIGNAL AMPLITUDE

-10 -20 THD + NOISE (dB) -30 -40 -50 -60 -70 -80 -90 0 0.5 1.0 1.5 2.0 2.5 3.0 AMPLITUDE (Vp-p) B A SEE TABLE 1.

MAX7426/27-12

AMPLITUDE (Vp-p)

Table 1. THD + Noise Test Conditions

LABEL A B fIN (Hz) 200 1k fC (kHz) 1 5 fCLK (kHz) 100 500 MEASUREMENT BANDWIDTH (kHz) 22 80

_______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor MAX7426/MAX7427

Typical Operating Characteristics (continued)

(VDD = +5V for MAX7426, VDD = +3V for MAX7427, fCLK = 100kHz, SHDN = VDD, VCOM = VOS = VDD / 2, TA = +25C, unless otherwise noted.)

INTERNAL OSCILLATOR PERIOD vs. SMALL CAPACITANCE (IN pF)

MAX7426/27-13

INTERNAL OSCILLATOR PERIOD vs. LARGE CAPACITANCE (IN nF)

18 OSCILLATOR PERIOD (ms) 16 14 12 10 8 6 4 2 VDD = +3V VDD = +5V

MAX7426/27-14

200 VDD = +5V OSCILLATOR PERIOD (s) 150 VDD = +3V 100

20

50

0 0 500 1000 1500 2000 2500 3000 3500 CAPACITANCE (pF)

0 0 50 100 150 200 250 300 350 CAPACITANCE (nF)

INTERNAL OSCILLATOR FREQUENCY vs. SUPPLY VOLTAGE

MAX7426/27-15

INTERNAL OSCILLATOR FREQUENCY vs. TEMPERATURE

MAX7426/27-16

17.5 OSCILLATOR FREQUENCY (kHz)

18.0 OSCILLATOR FREQUENCY (kHz)

17.6

VDD = +3V

17.4

17.2

VDD = +5V

17.3

16.8

17.2 COSC = 1000pF 17.1 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 SUPPLY VOLTAGE (V)

16.4 COSC = 1000pF 16.0 -40 -20 0 20 40 60 80 100 TEMPERATURE (C)

DC OFFSET VOLTAGE vs. TEMPERATURE

MAX7426/27-17

DC OFFSET VOLTAGE vs. SUPPLY VOLTAGE

-0.5 DC OFFSET VOLTAGE (mV) -1.0 -1.5 -2.0 -2.5 -3.0 -3.5 -4.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

MAX7426/27-18

0 -0.5 DC OFFSET VOLTAGE (mV) -1.0 -1.5 -2.0 -2.5 -3.0 -3.5 -40 -20 0 20 40 60 80 VDD = +5V VDD = +3V

100

TEMPERATURE (C)

SUPPLY VOLTAGE (V)

_______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters MAX7426/MAX7427

Pin Description

PIN 1 2 3 4 5 6 7 8 NAME COM IN GND VDD OUT OS SHDN CLK FUNCTION Common Input Pin. Biased internally at midsupply. Bypass externally to GND with a 0.1F capacitor. To override internal biasing, drive with an external supply. Filter Input Ground Positive Supply Input, +5V for MAX7426 or +3V for MAX7427 Filter Output Offset Adjust Input. To adjust output offset, bias OS with a resistive voltage-divider between an external supply and ground. Connect OS to COM if no offset adjustment is needed. Shutdown Input. Drive low to enable shutdown mode; drive high or connect to VDD for normal operation. Clock Input. Connect an external capacitor (COSC) from CLK to GND to set the internal oscillator frequency. To override the internal oscillator, connect to an external clock.

Detailed Description

The MAX7426/MAX7427 family of 5th-order, elliptic, lowpass filters provides sharp rolloff with good stopband rejection. All parts operate with a 100:1 clock-tocorner frequency ratio. Most SCFs are designed with biquadratic sections. Each section implements two pole-zero pairs, and the sections can be cascaded to produce higher-order filters. The advantage to this approach is ease of design. However, this type of design is highly sensitive to component variations if any sections Q is high. The MAX7426/MAX7427 use an alternative approach, which is to emulate a passive network using switched-capacitor integrators with summing and scaling. The passive network may be synthesized using CAD programs or may be found in many filter books. Figure 1 shows a basic 5th-order ladder elliptic filter structure. A switched-capacitor filter that emulates a passive ladder filter retains many of the same advantages. The component sensitivity of a passive ladder filter is low when compared to a cascaded biquadratic design, because each component affects the entire filter shape rather than a single pole-zero pair. In other words, a

C2 C4

mismatched component in a biquadratic design has a concentrated error on its respective poles, while the same mismatch in a ladder filter design spreads its error over all poles.

Elliptic Characteristics

Lowpass elliptic filters such as the MAX7426/MAX7427 provide the steepest possible rolloff with frequency of the four most common filter types (Butterworth, Bessel, Chebyshev, and elliptic). The high Q value of the poles near the passband edge combined with the stopband zeros allow for the sharp attenuation characteristic of elliptic filters, making these devices ideal for anti-aliasing and post-DAC filtering in single-supply systems (see the Anti-Aliasing and Post-DAC Filtering section). In the frequency domain (Figure 2), the first transmission zero causes the filters amplitude to drop to a minimum level. Beyond this zero, the response rises as the frequency increases until the next transmission zero. The stopband begins at the stopband frequency, fS. At frequencies above fS, the filters gain does not exceed the gain at fS. The corner frequency, fC, is defined as the point where the filter output attenuation falls just below the passband ripple. The transition ratio (r) is defined as the ratio of the stopband frequency to the corner frequency: r = fS / fC The MAX7426/MAX7427 have a transition ratio of 1.25 and typically 37dB of stopband rejection.

RS + -

L2 C3

L4 C5

VIN C1

RL

Clock Signal

External Clock These SCFs are designed for use with external clocks that have a 40% to 60% duty cycle. When using an external clock, drive the CLK pin with a CMOS gate

Figure 1. 5th-Order Ladder Elliptic Filter Network 8

_______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters MAX7426/MAX7427

VSUPPLY RIPPLE 0.1F fC GAIN (dB) VDD f TRANSITION RATIO = S fC fS INPUT IN SHDN OUT COM 0.1F OUTPUT 50k

MAX7426 MAX7427

CLOCK CLK GND OS 0.1F 50k 50k

PASSBAND fC fS

STOPBAND FREQUENCY

Figure 2. Elliptic Filter Response

Figure 3. Offset Adjustment Circuit

powered from 0 to VDD. Varying the rate of the external clock adjusts the corner frequency of the filter: f fC = CLK 100 Internal Clock When using the internal oscillator, the capacitance (COSC) on CLK determines the oscillator frequency: fOSC (kHz) = 17.5 103 COSC (pF)

Estimate the input impedance of the filter by using the following formula: ZIN = 1 fCLK CIN

where fCLK = clock frequency and CIN = 1pF.

Low-Power Shutdown Mode

The MAX7426/MAX7427 have a shutdown mode that is activated by driving SHDN low. In shutdown mode, the filter supply current reduces to 0.2A, and the output of the filter becomes high impedance. For normal operation, drive SHDN high or connect to VDD.

Since COSC is in the low picofarads, minimize the stray capacitance at CLK so that it does not affect the internal oscillator frequency. Varying the rate of the internal oscillator adjusts the filters corner frequency by a 100:1 clock-to-corner frequency ratio. For example, an internal oscillator frequency of 100kHz produces a nominal corner frequency of 1kHz.

Applications Information

Offset (OS) and Common-Mode (COM) Input Adjustment

COM sets the common-mode input voltage and is biased at midsupply with an internal resistor-divider. If the application does not require offset adjustment, connect OS to COM. For applications where offset adjustment is required, apply an external bias voltage through a resistor-divider network to OS, as shown in Figure 3. For applications that require DC level shifting, adjust OS with respect to COM. (Note: Do not leave OS unconnected.) The output voltage is represented by these equations: VOUT = (VIN VCOM ) + VOS V VCOM = DD (typical) 2 where (VIN - VCOM) is lowpass filtered by the SCF and OS is added at the output stage. See the Electrical

Input Impedance vs. Clock Frequencies

The MAX7426/MAX7427s input impedance is effectively that of a switched-capacitor resistor (see the following equation), and is inversely proportional to frequency. The input impedance values determined by the equation represent the average input impedance, since the input current is not continuous. As a rule, use a driver with an output resistance less than 10% of the filters input impedance.

_______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters MAX7426/MAX7427

V+

VDD INPUT IN

SHDN OUT COM

* OUTPUT

For either single-supply or dual-supply operation, drive CLK and SHDN from GND (V- in dual-supply operation) to V DD . Use the MAX7427 for 2.5, and use the MAX7426 for 1.5V. For 5V dual-supply applications, refer to the MAX291/MAX292/MAX295/MAX296 and MAX293/MAX294/MAX297 data sheets.

Input Signal Amplitude Range

The optimal input signal range is determined by observing the voltage level at which the signal-to-noise plus distortion (SINAD) ratio is maximized for a given corner frequency. The Typical Operating Characteristics show the THD + Noise response as the input signals peak-topeak amplitude is varied.

V+ V-

MAX7426 MAX7427

CLOCK CLK OS 0.1F GND 0.1F

Anti-Aliasing and Post-DAC Filtering

When using the MAX7426/MAX7427 for anti-aliasing or post-DAC filtering, synchronize the DAC (or ADC) and the filter clocks. If the clocks are not synchronized, beat frequencies may alias into the desired passband.

V*CONNECT SHDN TO V- FOR LOW-POWER SHUTDOWN MODE.

Figure 4. Dual-Supply Operation

Harmonic Distortion

Harmonic distortion arises from nonlinearities within the filter. These nonlinearities generate harmonics when a pure sine wave is applied to the filter input. Table 2 lists typical harmonic distortion values with a 10k load at TA = +25C.

Characteristics table for the input voltage range of COM and OS. Changing the voltage on COM or OS significantly from midsupply reduces the dynamic range.

Power Supplies

The MAX7426 operates from a single +5V supply, and the MAX7427 operates from a single +3V supply. Bypass VDD to GND with a 0.1F capacitor. If dual supplies are required, connect COM to the system ground and GND to the negative supply. Figure 4 shows an example of dual-supply operation. Singlesupply and dual-supply performance are equivalent.

Chip Information

TRANSISTOR COUNT: 1457 PROCESS: BiCMOS

Table 2. Typical Harmonic Distortion

FILTER fCLK (kHz) 500 MAX7426 100 500 MAX7427 100 200 200 1k 2 -90 -87 -90 -90 fIN (Hz) 1k 4 -88 -87 -86 -86 -92 -90 -88 -90 VIN (Vp-p) TYPICAL HARMONIC DISTORTION (dB) 2nd -71 3rd -73 4th -90 5th -82

10

______________________________________________________________________________________

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters

________________________________________________________Package Information

8LUMAXD.EPS

MAX7426/MAX7427

______________________________________________________________________________________

11

5th-Order, Lowpass, Elliptic, Switched-Capacitor Filters MAX7426/MAX7427

Package Information (continued)

PDIPN.EPS

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 ____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 2000 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

You might also like

- Max7490 Max7491Document18 pagesMax7490 Max7491xo9o6No ratings yet

- 5th-Order, Lowpass, Switched-Capacitor Filters: General Description FeaturesDocument12 pages5th-Order, Lowpass, Switched-Capacitor Filters: General Description FeaturesGustavo PalaciosNo ratings yet

- MAX9947ETE+ Marking Code AHFDocument17 pagesMAX9947ETE+ Marking Code AHFZamir HussainNo ratings yet

- Low-Cost, Triple, 8-Bit Voltage-Output Dacs With Serial InterfaceDocument16 pagesLow-Cost, Triple, 8-Bit Voltage-Output Dacs With Serial InterfaceBboubrahim BbnnNo ratings yet

- 10Mhz To 1050Mhz Integrated RF Oscillator With Buffered OutputsDocument11 pages10Mhz To 1050Mhz Integrated RF Oscillator With Buffered OutputsmadhukirNo ratings yet

- MAX038Document17 pagesMAX038Javier Edinson Perez HerreraNo ratings yet

- Max 8654Document17 pagesMax 8654Alfredo Valencia RodriguezNo ratings yet

- FDocument24 pagesFrotenolabsNo ratings yet

- Features Description: LTC2368-16 16-Bit, 1Msps, Pseudo-Differential Unipolar SAR ADC With 94.7dB SNRDocument24 pagesFeatures Description: LTC2368-16 16-Bit, 1Msps, Pseudo-Differential Unipolar SAR ADC With 94.7dB SNRrotenolabsNo ratings yet

- Single-Chip Global Positioning System Receiver Front-End: General Description FeaturesDocument9 pagesSingle-Chip Global Positioning System Receiver Front-End: General Description FeaturesMohit AnandNo ratings yet

- Max 5541Document9 pagesMax 5541rohitkiranbrNo ratings yet

- Max038 Generador de FuncionesDocument17 pagesMax038 Generador de FuncionesLuis Rodolfo Reyes JimenezNo ratings yet

- MAX038Document16 pagesMAX038fabirznNo ratings yet

- LMV721 22Document16 pagesLMV721 22Brzata PticaNo ratings yet

- Max 2981Document13 pagesMax 2981Jamila RobinsonNo ratings yet

- CD4047Document15 pagesCD4047mohankumarktvrNo ratings yet

- Description Features: CMOS Low-Power Monostable/Astable MultivibratorDocument15 pagesDescription Features: CMOS Low-Power Monostable/Astable Multivibratorதினேஷ் குமார்No ratings yet

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LDocument36 pages3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858Ljnax101No ratings yet

- 300mA LDO REGULATOR RP114x SERIES DATA SHEETDocument28 pages300mA LDO REGULATOR RP114x SERIES DATA SHEETSol De GabrielNo ratings yet

- 9-0-9 Step Down TransformerDocument20 pages9-0-9 Step Down TransformerSarthak JoshiNo ratings yet

- Ad7730 7730LDocument52 pagesAd7730 7730LDa Q ShaNo ratings yet

- Micro: Description FeaturesDocument20 pagesMicro: Description FeaturespopcriNo ratings yet

- MAX038Document17 pagesMAX038Brane PetkoskiNo ratings yet

- Max 8729Document26 pagesMax 8729lagreta55No ratings yet

- 2.35 V To 5.25 V, 1 MSPS, 12-/10-/8-Bit Adcs in 6-Lead Sc70: A MaxDocument24 pages2.35 V To 5.25 V, 1 MSPS, 12-/10-/8-Bit Adcs in 6-Lead Sc70: A MaxNatthaphob NimpitiwanNo ratings yet

- MCP3040 DatasheetDocument40 pagesMCP3040 Datasheetjiajun898No ratings yet

- Ks8803B 10/15 CH PLLDocument11 pagesKs8803B 10/15 CH PLLTopaz ReyesNo ratings yet

- LTC2440 PDFDocument28 pagesLTC2440 PDFyusufwpNo ratings yet

- Data Sheet TC 14433Document20 pagesData Sheet TC 14433Heriberto Flores AmpieNo ratings yet

- TLC 2934Document9 pagesTLC 2934Carlos DanielNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- Max3160 Max3162Document23 pagesMax3160 Max3162jb2015831No ratings yet

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LDocument32 pages3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LJodelCamarinNo ratings yet

- 11.3Gb/s Full-Band Tunable Super-X2 Transceiver: TL8000 SeriesDocument10 pages11.3Gb/s Full-Band Tunable Super-X2 Transceiver: TL8000 SeriesmofiwNo ratings yet

- Medical Ecg Ina326Document23 pagesMedical Ecg Ina326ronny5525No ratings yet

- Ad 421Document14 pagesAd 421Vishal Devrao JadhavNo ratings yet

- AK5358A 96kHz 24-Bit ΔΣ ADCDocument18 pagesAK5358A 96kHz 24-Bit ΔΣ ADCAlver TuizaNo ratings yet

- 12-Bit ADC AD1674Document12 pages12-Bit ADC AD1674anjanbsNo ratings yet

- Max 5304Document12 pagesMax 5304tabassam7801No ratings yet

- +2.7V, Low-Power, 12-Bit Serial Adcs in 8-Pin SoDocument16 pages+2.7V, Low-Power, 12-Bit Serial Adcs in 8-Pin Sojnax101No ratings yet

- 4 X 25W Quad Bridge Car Radio Amplifier: DescriptionDocument11 pages4 X 25W Quad Bridge Car Radio Amplifier: DescriptionJose Juan Cuevas DiazNo ratings yet

- DatasheetDocument24 pagesDatasheetRafael PavanNo ratings yet

- DTMF Receiver HM 9270C/DDocument10 pagesDTMF Receiver HM 9270C/DCarlos Javier Solano GuzmánNo ratings yet

- 2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial InterfaceDocument20 pages2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial Interfacejoseleomi_limaNo ratings yet

- Can Bus Transceiver: DescriptionDocument8 pagesCan Bus Transceiver: DescriptionNasiri65No ratings yet

- TCM3105DWL, TCM3105JE, TCM3105JL TCM3105NE, TCM3105NL FSK ModemDocument12 pagesTCM3105DWL, TCM3105JE, TCM3105JL TCM3105NE, TCM3105NL FSK ModemSetya AgusNo ratings yet

- MCP4921, MCP4922 12bit Serial DACDocument42 pagesMCP4921, MCP4922 12bit Serial DACBloj FlorinNo ratings yet

- TC1072 50ma Cmos Ldo With Shutdown, Error Output and V BypassDocument12 pagesTC1072 50ma Cmos Ldo With Shutdown, Error Output and V BypassΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- High Speed Can Bus Transceiver: DescriptionDocument9 pagesHigh Speed Can Bus Transceiver: Descriptionsweety987No ratings yet

- HS-2420RH - Fast Sample and HolDocument8 pagesHS-2420RH - Fast Sample and HolDeepa DevarajNo ratings yet

- Iso122sensor de TensionDocument15 pagesIso122sensor de TensionRichard ZerpaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Caracteristici Otel BetonDocument2 pagesCaracteristici Otel Betonridzim4638No ratings yet

- SatelitDocument1 pageSatelitridzim4638No ratings yet

- 1Document4 pages1ridzim4638No ratings yet

- Beginning Vibration Analysis FundamentalsDocument96 pagesBeginning Vibration Analysis FundamentalsromadhinhoNo ratings yet

- L1Document1 pageL1ridzim4638No ratings yet

- Watermarked Fa 3 Mini Chrome TransmitterDocument1 pageWatermarked Fa 3 Mini Chrome Transmitterridzim4638No ratings yet

- Finepix s2980 Manual enDocument144 pagesFinepix s2980 Manual enaya mikageNo ratings yet

- Safe Overload: 150% F.S. Ultimate Overload: 200% F.S.Document5 pagesSafe Overload: 150% F.S. Ultimate Overload: 200% F.S.ridzim4638No ratings yet

- Magnetic Examinations of Wire Ropes Quantified Using Hall-Effect SensorsDocument10 pagesMagnetic Examinations of Wire Ropes Quantified Using Hall-Effect Sensorsridzim4638No ratings yet

- 5962 7276eDocument88 pages5962 7276eridzim4638No ratings yet

- ReadmeDocument2 pagesReadmeridzim4638No ratings yet

- AS4324.1-1995 Standard For Design of Bulk Materials Handling MachinesDocument8 pagesAS4324.1-1995 Standard For Design of Bulk Materials Handling Machinesridzim4638100% (1)

- CDocument123 pagesCridzim4638No ratings yet

- Kurowski Cosmosworks 2005Document248 pagesKurowski Cosmosworks 2005ridzim4638No ratings yet

- Diction AreDocument1 pageDiction Areridzim4638No ratings yet

- Validating Oenological Analysis MethodsDocument92 pagesValidating Oenological Analysis Methodsridzim4638No ratings yet

- LicenseDocument6 pagesLicensemerrysun22No ratings yet

- NTN Bearing Bpfo&BpfiDocument61 pagesNTN Bearing Bpfo&BpfishantanusamajdarNo ratings yet

- 3 2 ISO TC 16 Committee Draft QualVal March 2011v2Document12 pages3 2 ISO TC 16 Committee Draft QualVal March 2011v2ridzim4638No ratings yet

- Two Plane Bal ReadmeDocument1 pageTwo Plane Bal Readmeridzim4638No ratings yet

- Charge Amplifiers: Instruction ManualDocument19 pagesCharge Amplifiers: Instruction Manualridzim4638No ratings yet

- Max7426 Max7427Document12 pagesMax7426 Max7427ridzim4638100% (1)

- 2 Plane BalanceDocument6 pages2 Plane BalanceitaryNo ratings yet

- ReadmeDocument1 pageReadmeridzim4638No ratings yet

- BeanDevice AX 3DDocument7 pagesBeanDevice AX 3Dridzim4638No ratings yet

- Comparative Study of Fatigue Damage Models Using Different Number of Classes Combined With The Rainflow MethodDocument6 pagesComparative Study of Fatigue Damage Models Using Different Number of Classes Combined With The Rainflow MethodjeanpremierNo ratings yet

- FourPointBalance WophaseDocument1 pageFourPointBalance WophaseMark FrascaNo ratings yet

- NouDocument12 pagesNouridzim4638No ratings yet

- A Multipurpose VibDocument10 pagesA Multipurpose Vibridzim4638No ratings yet

- 53 Bevel Gear Support DrawDocument1 page53 Bevel Gear Support DrawFelipe KnorstNo ratings yet

- IIR FilterDesignDocument20 pagesIIR FilterDesignHassan ShehadiNo ratings yet

- A Filter Primer (MXM AN733)Document20 pagesA Filter Primer (MXM AN733)Carlos GamioNo ratings yet

- Finals DSP WithMinimalErrors PDFDocument64 pagesFinals DSP WithMinimalErrors PDFanembam putobungbongNo ratings yet

- Lab 5. FIR & IIR Filters in Matlab: Filter DesignDocument12 pagesLab 5. FIR & IIR Filters in Matlab: Filter DesignDrakshayaniMurgodNo ratings yet

- Unit-4 - Design of Digital FilterDocument107 pagesUnit-4 - Design of Digital Filterchandrani deyNo ratings yet

- Design and Analysis of Analog FiltersDocument453 pagesDesign and Analysis of Analog Filterspouty567100% (4)

- Filter DesignDocument33 pagesFilter Designnilanka_costa2638No ratings yet

- DigfiltDocument238 pagesDigfiltNeamt CatalinNo ratings yet

- EE247 - Lecture 2 FiltersDocument27 pagesEE247 - Lecture 2 FiltersHassan FarssiNo ratings yet

- Diseño de Filtros IIR y FIRDocument11 pagesDiseño de Filtros IIR y FIRacajahuaringaNo ratings yet

- Pratical FIR Filter Design in MatlabDocument32 pagesPratical FIR Filter Design in Matlabnonelit54100% (3)

- Tiv200 IDocument4 pagesTiv200 IdantenocturnoNo ratings yet

- Elliptic High Pass FilterDocument59 pagesElliptic High Pass FilterAngela ReyesNo ratings yet

- Analog and RF Filters Design Manual:: A Filter Design Guide by and For WMU StudentsDocument42 pagesAnalog and RF Filters Design Manual:: A Filter Design Guide by and For WMU StudentsThevesteNo ratings yet

- 8 Endaq Shock Vibration Overview Ebook Guía Rápida VibracionesDocument69 pages8 Endaq Shock Vibration Overview Ebook Guía Rápida VibracionesAndres Felipe Rodriguez JimenezNo ratings yet

- Chapter 4Document39 pagesChapter 4Shoaib MughalNo ratings yet

- Active and Passive Filter Synthesis Using MATLABDocument11 pagesActive and Passive Filter Synthesis Using MATLABNurSalahuddinNo ratings yet

- Practical Introduction To Digital Filter Design - MATLAB ExampleDocument12 pagesPractical Introduction To Digital Filter Design - MATLAB ExampleEdsonNo ratings yet

- Madsen - Efficient Architectures For Exactly Realizing Optical Filters With Optimum Bandpass DesignsDocument3 pagesMadsen - Efficient Architectures For Exactly Realizing Optical Filters With Optimum Bandpass DesignsGreta GarboNo ratings yet

- IIR Filter Design With MATLABDocument13 pagesIIR Filter Design With MATLABseemabNo ratings yet

- The Design of Active Crossovers (Douglas Self)Document699 pagesThe Design of Active Crossovers (Douglas Self)Cristiano LONo ratings yet

- Diplexer For UHF Military Applications (Master's Thesis)Document76 pagesDiplexer For UHF Military Applications (Master's Thesis)wearoleNo ratings yet

- DSP LAB ManualCompleteDocument64 pagesDSP LAB ManualCompleteHamzaAliNo ratings yet

- EllipticDocument5 pagesEllipticinertia116647No ratings yet

- Ca4 - Designing and Implementing FiltersDocument9 pagesCa4 - Designing and Implementing Filtersapi-223721455No ratings yet

- EEE321L - Presentation DSP LDocument24 pagesEEE321L - Presentation DSP LABDULLAH AL BAKINo ratings yet

- Filtros Analogicos Con MatlabDocument10 pagesFiltros Analogicos Con MatlabacajahuaringaNo ratings yet

- Analyzing Analog and Digital FiltersDocument177 pagesAnalyzing Analog and Digital Filterszhitao wangNo ratings yet

- Home Work For Enginners ADSPDocument16 pagesHome Work For Enginners ADSPlankyrckNo ratings yet

- IIR Filter Designing Using MATLABDocument5 pagesIIR Filter Designing Using MATLABali khanNo ratings yet