Professional Documents

Culture Documents

HW 3

Uploaded by

jameelahmadOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HW 3

Uploaded by

jameelahmadCopyright:

Available Formats

Brown University Division of Engineering EN1600 Design and Implementation of VLSI Systems. Spring 2008. Prof.

Sherief Reda Assignment #3. Due Date: Friday, February 22nd. Points [60 points]

1. [10 points] Generate the I-V characteristics of the following congurations (at temp=70 C): a. [1 point] A W=4, L=2 NMOS transistor using TSMC 180nm, and AMI 0.5micron process technology SPICE models. Remember to adjust your supply voltage according to the process (3.3V @ 0.5micron and 1.8V @ 180nm). b. [2 points] Calculate the threshold voltages for the different process technologies. c. [1 points] Repeat (a) but instead use W=4, L=2 PMOS transistor. How do you compare the PMOS currents to the NMOS currents at the same input voltages? d. [2 points] Repeat (a) using W=6 and 8 (just use 0.5 micron models). What is the impact of width on the current? e. [2 points] Repeat (a) using L=4 , 6 , 8 (just use 0.5 micron models). What is the impact of increasing the length of the transistor? f. [2 points] Repeat (a) with body biases (+0.2, +0.1V and -0.1V, -0.2V) using 0.5 micron models. What is the impact of the body bias on the threshold voltage and saturation current? 2. [20 points] To model the operation of the transistor, we have considered in class two models: the Shockley model and the alpha-law model. The objective of this exercise is to test the accuracy of these two models in comparison to SPICE results. This question ultimately seeks to produce similar plots as in Figure 2.17 of your textbook or as in Slide 6 of lecture 8. For this problem, assume VDD=3.3V, electron mobility (U0) is 447 cm2/V, oxide thickness (tox) 14.1 nm, temperature = 27 C, W = 1 micron, and L = 0.5 micron. SiO2 permittivity is 3.4 times that of free space. a. [4 points] Write down the Shockley model and the alpha-law model. Explain the shortcomings of the Shockley model and describe the main motivations behind the alpha model. b. [2 points] Use SPICE to plot the IV characteristics of an NMOS transistor of W = 1 micron and L = 0.5 micron using the SPICE models of the AMI 0.5 micron process. Plot the results using a sweep from Vgs = 0V to Vgs = 3.3V in steps of 0.3V. c. [6 points] Use the Shockley model to predict and plot the IV characteristics of the the same NMOS transistor of part (b) at Vgs = 3.3V and Vgs = 2.4V. You might like to use a tool like MATLAB to automate the plot generation process. To compare the results of the Shockley model versus the SPICE results, it would be ideal if you can superimpose your Shockley model plots on the plots form part (b) (similar to Figure 2.17). Comment on the accuracy of the Shockley model.

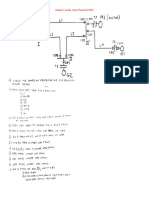

d. [8 points] To use the alpha model, you need to empirically determine its various parameters (e.g., alpha, Pc, ..., etc). Use the SPICE results from part (b) to estimate the various parameters of the alpha model. Plot the alpha-model IV results at Vgs = 3.3V and Vgs = 2.4V, and compare its predictions against the Shockley model. It would be ideal if you impose your plots on the ones from parts (b) and (c). 2. [30 points] Compact layout of complex gates is important for total area minimization. Assuming horizontal power (VDD and GND) lines, and vertical polysilicon lines for the inputs: a. [6 points] Draw the stick diagram of the gate x = (a + b) c using the following two different polysilicon input orderings: (a c b) and (a b c). b. [2 points]. How many uninterrupted active diffusion strips are required for each ordering? c. [2 points]. Which input ordering uses less gate area? d. [4 points]. Construct the layout that gives the minimum area using Tanner LEdit. Report the layout, dimensions and the DRC results. e. [4 points]. Extract the circuit layout to SPICE and verify the functionality of the circuit by simulating all possible input combinations in SPICE and report the input and output waveforms. The answers to the previous subquestions demonstrate that input ordering impacts the number of uninterrupted diffusion strips and consequently the area of the gate. It is always best to nd the optimal input ordering that leads to the minimum gate area. To achieve this goal, we will use some techniques from graph theory. A graph is a set of nodes and a set of edges. The edges connect the nodes; i.e., each edge connects two nodes. To nd the optimal input ordering, construct a graph where the vertices represent the nodes (or signals) of the circuit given by x and the edges represent the transistors. d. [4 points] Draw the pull-up graph and the pull-down graph for x separately. e. [4 points] A path in a graph is a sequence of edges such that no edge is repeated. What is the characteristic of the path(s) that leads to the optimal ordering of inputs? f. [4 points] Without drawing the stick diagram of the function, nd the optimal input ordering that minimizes the area of gate y y = ab + cd .

You might also like

- Optimization TechniquesDocument10 pagesOptimization TechniquesjameelahmadNo ratings yet

- Elsevier Multipulse Converters Simulation in MATLABDocument11 pagesElsevier Multipulse Converters Simulation in MATLABjameelahmadNo ratings yet

- Edge Computing in Autonomous DrivingDocument20 pagesEdge Computing in Autonomous DrivingjameelahmadNo ratings yet

- Islam and The StateDocument15 pagesIslam and The StatejameelahmadNo ratings yet

- 1 Cost ModelsDocument10 pages1 Cost ModelsjameelahmadNo ratings yet

- Lecture 2 - Power System BasicsDocument81 pagesLecture 2 - Power System BasicsjameelahmadNo ratings yet

- Week1b 7oct 4upDocument11 pagesWeek1b 7oct 4upjameelahmadNo ratings yet

- Lec-1 Scope of Power ConvertersDocument26 pagesLec-1 Scope of Power Convertersjameelahmad100% (1)

- Assignment On Battery Charging-SOLUTIONDocument1 pageAssignment On Battery Charging-SOLUTIONjameelahmadNo ratings yet

- Low-Power Split-Radix FFT Processors Using Radix-2 Butterfly UnitsDocument5 pagesLow-Power Split-Radix FFT Processors Using Radix-2 Butterfly UnitsjameelahmadNo ratings yet

- (A) For Transient Response, We Have 4 Specifications:: (A) T - Rise TimeDocument54 pages(A) For Transient Response, We Have 4 Specifications:: (A) T - Rise TimejameelahmadNo ratings yet

- Buchholz Relay NotesDocument7 pagesBuchholz Relay NotesjameelahmadNo ratings yet

- Homework-1 Due Date: Class On Thursday Feb 16,2017Document1 pageHomework-1 Due Date: Class On Thursday Feb 16,2017jameelahmadNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Roofing Shingles in KeralaDocument13 pagesRoofing Shingles in KeralaCertainteed Roofing tilesNo ratings yet

- TOPIC I: Moral and Non-Moral ProblemsDocument6 pagesTOPIC I: Moral and Non-Moral ProblemsHaydee Christine SisonNo ratings yet

- CH Folk Media and HeatlhDocument6 pagesCH Folk Media and HeatlhRaghavendr KoreNo ratings yet

- Ivler vs. Republic, G.R. No. 172716Document23 pagesIvler vs. Republic, G.R. No. 172716Joey SalomonNo ratings yet

- TugasFilsS32019.AnthoniSulthanHarahap.450326 (Pencegahan Misconduct)Document7 pagesTugasFilsS32019.AnthoniSulthanHarahap.450326 (Pencegahan Misconduct)Anthoni SulthanNo ratings yet

- Evidentiary Value of NarcoDocument2 pagesEvidentiary Value of NarcoAdv. Govind S. TehareNo ratings yet

- Supporting References in Release 12 SLA PDFDocument8 pagesSupporting References in Release 12 SLA PDFsoireeNo ratings yet

- MOA Agri BaseDocument6 pagesMOA Agri BaseRodj Eli Mikael Viernes-IncognitoNo ratings yet

- What Is Thesis Plural FormDocument8 pagesWhat Is Thesis Plural Formtracyjimenezstamford100% (2)

- 2nd Form Sequence of WorkDocument7 pages2nd Form Sequence of WorkEustace DavorenNo ratings yet

- Communication and Globalization Lesson 2Document13 pagesCommunication and Globalization Lesson 2Zetrick Orate0% (1)

- The Personal Law of The Mahommedans, According To All The Schools (1880) Ali, Syed Ameer, 1849-1928Document454 pagesThe Personal Law of The Mahommedans, According To All The Schools (1880) Ali, Syed Ameer, 1849-1928David BaileyNo ratings yet

- Trigonometry Primer Problem Set Solns PDFDocument80 pagesTrigonometry Primer Problem Set Solns PDFderenz30No ratings yet

- Chapter 3 - the-WPS OfficeDocument15 pagesChapter 3 - the-WPS Officekyoshiro RyotaNo ratings yet

- Introduction To Public HealthDocument54 pagesIntroduction To Public HealthKristelle Marie Enanoria Bardon50% (2)

- Easter in RomaniaDocument5 pagesEaster in RomaniaDragos IonutNo ratings yet

- BhattacharyaDocument10 pagesBhattacharyavoraciousvNo ratings yet

- HG G5 Q1 Mod1 RTP PDFDocument11 pagesHG G5 Q1 Mod1 RTP PDFKimberly Abilon-Carlos100% (1)

- Action List 50Document4 pagesAction List 50hdfcblgoaNo ratings yet

- 25 ConstitutionDocument150 pages25 ConstitutionSaddy MehmoodbuttNo ratings yet

- Site Master S113C, S114C, S331C, S332C, Antenna, Cable and Spectrum AnalyzerDocument95 pagesSite Master S113C, S114C, S331C, S332C, Antenna, Cable and Spectrum AnalyzerKodhamagulla SudheerNo ratings yet

- Oldham Rules V3Document12 pagesOldham Rules V3DarthFooNo ratings yet

- Capstone Report FormatDocument11 pagesCapstone Report FormatAnkush PalNo ratings yet

- SpellsDocument86 pagesSpellsGypsy580% (5)

- Marcelo H Del PilarDocument8 pagesMarcelo H Del PilarLee Antonino AtienzaNo ratings yet

- Deed of Power of Attorney To Sell SharesDocument8 pagesDeed of Power of Attorney To Sell SharesridhofauzisNo ratings yet

- Discussion #3: The Concept of Culture Learning ObjectivesDocument4 pagesDiscussion #3: The Concept of Culture Learning ObjectivesJohn Lery SurellNo ratings yet

- Designing A Peace Building InfrastructureDocument253 pagesDesigning A Peace Building InfrastructureAditya SinghNo ratings yet

- Hibbeler, Mechanics of Materials-BendingDocument63 pagesHibbeler, Mechanics of Materials-Bendingpoom2007No ratings yet

- Conversational Maxims and Some Philosophical ProblemsDocument15 pagesConversational Maxims and Some Philosophical ProblemsPedro Alberto SanchezNo ratings yet