Professional Documents

Culture Documents

ALDEC 16450 IP Core Data Sheet: Table 1: Core Signal Pinout

Uploaded by

Deepa DevarajOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ALDEC 16450 IP Core Data Sheet: Table 1: Core Signal Pinout

Uploaded by

Deepa DevarajCopyright:

Available Formats

ALDEC 16450 IP Core Data Sheet

April 11, 2006 (version 1.0)

Overview

The 16450 core is the HDL synthesizable model of industry standard 16450 Universal Asynchronous Receiver/Transmitter.

Features

Functionally based on the 16450 device Transmission of programmable word length (5, 6, 7, 8) and stop bits (1,1.5, or 2) Even, odd, force, or no parity generation and detection Possibility to remove selected parts of the core, e.g. receiver or transmitter (one of them is required), baud generator, modem controller, interrupt controller, scratch patch register

Pinout

Table 1: Core Signal Pinout Name CLK RD WR CE MR CS0 Direction Input Input Input Input Input Input Polarity Low/High Low/High Low/High Low/High Low/High Low/High Description Transmitter and receiver clock input Read signal Write signal Clock Enable signal for the CLK input Reset. The active state on this pin resets the internal registers and all outputs. Chip select 0. The active state on all chip select inputs causes UART to respond to RD and WR signals. Chip select 1. The active state on all chip select inputs causes UART to respond to RD and WR signals. Chip select 2. The active state on all chip select inputs causes UART to respond to RD and WR signals. Chip select out. The active state on this output indicates that the UART has been enabled by the chip select inputs. Clear to send. Logic 0 on the CTS pin indicates that the modem or data set is ready to accept data from the UART. Status can be tested by reading MSR bit 4. This pin has no effect on the UARTs transmit or receive operations. Carrier Detect. Logic 0 on this pin indicates that a carrier has been detected by the modem. This pin has no effect on the UARTs transmit or receive operation.

CS1

Input

Low/High

CS2

Input

Low/High

CSOUT

Output

Low/High

CTS

Input

Low

DCD

Input

Low

www.aldec.com

2006 Aldec, Inc. All rights reserved

Aldec 16450 Core Data Sheet Data Set Ready. A logic 0 on this pin indicates that the modem or data set is powered-on and ready for data exchange with the UART. This pin has no effect on the UARTs transmit or receive operation. Ring Indicator. Logic 0 on this pin indicates that the modem has received a ring signal from the telephone line. Logic 1 transition on this input pin will generate interrupt. This pin has no effect on the UARTs transmit or receive operation. Address bus. Selects internal registers address. Data in bus. Drive Disable. This pin goes to the active state when external CPU is reading data from the UART. Interrupt Request. Interrupt requests are indicated by the active state of this output pin. Serial input. This pin provides the serial input channel to the UART. During the local loop-back mode the SIN pin is disconnected and SOUT data is internally connected to the UART SIN input. Serial output. This pin provides the serial output channel from UART. During the local loop-back mode, the SOUT pin is disconnected, and SOUT data is internally connected to the UART SIN input. Data Terminal Ready. Logic 0 on this pin indicates that the UART is powered-on and ready. This pin can be controlled via the MCR register. Writing a logic 1 to MCR bit -0 will set the DTR output to logic 0, enabling the modem. This pin will be a logic 1 after writing a logic 0 to MCR bit -0. This pin has no effect on the UARTs transmit or receive operation. Output 1. The function of this pin is user defined. Writing to MCR bit 2 will set this pin to 0. This pin has no effect on the UARTs transmit or receive operation. Output 2. The function of this pin is user defined. Writing to MCR bit 3 will set this pin to 0. This pin has no effect on the UARTs transmit or receive operation. Ready To Send. Logic 0 on the RTS pin indicates the transmitter has data ready and waiting to send. Writing a logic 1 in the MCR bit 1 will set this pin to a logic 0 indicating data is available. This pin has no effect on the UARTs transmit or receive operation. Data out bus.

DSR

Input

Low

RI

Input

Low

A [2:0] DATA_IN [7:0] DDIS INT

Input Input

Low -

Output Output

Low/High Low/High

SIN

Input

SOUT

Output

DTR

Output

Low

OUT1

Output

Low

OUT2

Output

Low

RTS

Output

Low

DATA_OUT [7:0]

Output

www.aldec.com

2006 Aldec, Inc. All rights reserved

Aldec 16450 Core Data Sheet Notes: 1) Bi directional DATA bus is defined in the core interface as two separated ports DATA_IN and DATA_OUT. 2) The additional CE (Clock Enable) port has been added for the CLK input. This port allows to divide the frequency of the clock input (CLK). 3) The external clock port of the receiver and external clock output from the baud generator has been removed. The receiver uses the same clock signal as the transmitter. 4) The latches in the address port A and the ADS port used to drive the latches have been removed. 5) The doubled write (WR) and read (RD) input has been removed.

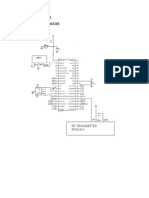

Block Diagram

CS0 CS1 CS2 MD RD

Receiver

SIN CLK CE

Registers

WR DDIS CSOUT A [2:0] D [7:0]

Transmitter

SOUT CLK CE

CE OUT Baud Generator CLK

OUT1 OUT2 RTS Modem DTR Controller CTS DSR DCD RI

Interrupt Controller

INTR

Figure 1: Core Structure

www.aldec.com

2006 Aldec, Inc. All rights reserved

Aldec 16450 Core Data Sheet

Deliverables

Available at No Cost: Verilog and/or VHDL Simulation Model (Encrypted for Aldec simulator only) Data Sheet Application Notes Available Upon ordering: VHDL/Verilog source code Technology-dependent EDIF and VHDL/Verilog netlists Verification Test Bench source code RTL Source compilation and simulation scripts Synthesis scripts User-Guide

Ordering Information

Aldec, Inc. 2260 Corporate Circle Henderson, NV 89074 Tel: 702-990-4400 Fax: 702-990-4414 Email: ipcores@aldec.com http://www.aldec.com

www.aldec.com

2006 Aldec, Inc. All rights reserved

You might also like

- Unit 6 2Document25 pagesUnit 6 2Venkatesh RachaNo ratings yet

- XR16C854/854D: General DescriptionDocument55 pagesXR16C854/854D: General DescriptionAnonymous QakmLc3kTINo ratings yet

- H8250 UartDocument7 pagesH8250 Uartananth22290No ratings yet

- Bidirectional Visitor CounterDocument17 pagesBidirectional Visitor CounterPankaj KumarNo ratings yet

- Microprocessor & Interfacing Tittle: Interfacing Pheripheral 8251 With 8086Document19 pagesMicroprocessor & Interfacing Tittle: Interfacing Pheripheral 8251 With 8086odaNo ratings yet

- Micro Converter (Analog Device) 12-Bit Adcs and Dacs With Embedded High Speed 62-Kb Flash McuDocument20 pagesMicro Converter (Analog Device) 12-Bit Adcs and Dacs With Embedded High Speed 62-Kb Flash McushaileshNo ratings yet

- Metal Detector Robotic Vehicle: Submitted byDocument25 pagesMetal Detector Robotic Vehicle: Submitted byDarshan ParmarNo ratings yet

- Remote Controlled Digital Audio Processor - Full Project AvailableDocument3 pagesRemote Controlled Digital Audio Processor - Full Project AvailableK Raja SekarNo ratings yet

- Experiment No. 1 (B) : Interfacing UART of LPC2148 To Transmit and Receive MessageDocument4 pagesExperiment No. 1 (B) : Interfacing UART of LPC2148 To Transmit and Receive MessageJohn FarandisNo ratings yet

- SCC2691 UART DatasheetDocument24 pagesSCC2691 UART DatasheetMstr BlinkyNo ratings yet

- 16-B D S P A/D C: FeaturesDocument60 pages16-B D S P A/D C: FeatureskrajasekarantutiNo ratings yet

- Sinclair QL Service Manual - Sinclair ResearchDocument45 pagesSinclair QL Service Manual - Sinclair Researchabo alasrarNo ratings yet

- Circuit Diagram Wireless TransmitterDocument17 pagesCircuit Diagram Wireless Transmitterumaiya1990100% (2)

- Ns16C552, Pc16552D: Pc16552D Dual Universal Asynchronous Receiver/Transmitter With FifosDocument24 pagesNs16C552, Pc16552D: Pc16552D Dual Universal Asynchronous Receiver/Transmitter With FifosNeimar HahmeierNo ratings yet

- Industrial Fault Indication System With Over Voltage Over TemperatureDocument46 pagesIndustrial Fault Indication System With Over Voltage Over Temperaturedivanshu16decNo ratings yet

- File 1406270302Document25 pagesFile 1406270302rupeshNo ratings yet

- Pin Description and Signals of 8085 MicroprocessorDocument9 pagesPin Description and Signals of 8085 MicroprocessorKripanand JhaNo ratings yet

- W83787FDocument123 pagesW83787Fguerrero_rjNo ratings yet

- Unit3 MicroprocessorDocument27 pagesUnit3 MicroprocessorAshishNo ratings yet

- All 8251 8255 852Document124 pagesAll 8251 8255 852Sunil KumarNo ratings yet

- TRISC 0 // Set Direction To Be Output 0 Output 1 InputDocument7 pagesTRISC 0 // Set Direction To Be Output 0 Output 1 Inputiri_scribdNo ratings yet

- MC Unit 4Document42 pagesMC Unit 4Kalai VaniNo ratings yet

- MCP23008/MCP23S08 8-Bit I/O Expander With Serial Interface - 21919eDocument44 pagesMCP23008/MCP23S08 8-Bit I/O Expander With Serial Interface - 21919eGuillermo Hernandez100% (3)

- HCTL 2017Document12 pagesHCTL 2017ivancho1070No ratings yet

- 73M2921 Advanced Single Chip Modem: Description FeaturesDocument42 pages73M2921 Advanced Single Chip Modem: Description FeaturesRicardo MercadoNo ratings yet

- Serial Communications: ObjectivesDocument26 pagesSerial Communications: ObjectivesAmy OliverNo ratings yet

- 8251A USART - Programmable Communication InterfaceDocument15 pages8251A USART - Programmable Communication InterfaceShreerama Samartha G BhattaNo ratings yet

- Cip 8Document4 pagesCip 8hthusithNo ratings yet

- 8088Document34 pages8088chandrasekarNo ratings yet

- Unit IIIDocument42 pagesUnit IIISoundarrajan RajanNo ratings yet

- Mpmcnotesunit IIIDocument34 pagesMpmcnotesunit IIIAmy OliverNo ratings yet

- QL ServiceManualDocument98 pagesQL ServiceManualOscar Arthur KoepkeNo ratings yet

- 8251A USART - Programmable Communication InterfaceDocument15 pages8251A USART - Programmable Communication InterfaceselvaNo ratings yet

- System Controllers: A Navya Vishnu 1210410304Document33 pagesSystem Controllers: A Navya Vishnu 1210410304Ananda KrishnaNo ratings yet

- An Efficient Monitering of Substation Using RF: Voltage Current TemperatureDocument38 pagesAn Efficient Monitering of Substation Using RF: Voltage Current TemperatureVamshi Kumar Reddy MNo ratings yet

- 09 - I2C Serial CommunicationsmDocument10 pages09 - I2C Serial CommunicationsmSorabh DungNo ratings yet

- 8255 Programmable Peripheral InterfaceDocument27 pages8255 Programmable Peripheral InterfaceSivaprakasam KarthikeyanNo ratings yet

- Vehicle Speed Control System Using RF CommunicationDocument20 pagesVehicle Speed Control System Using RF CommunicationRaina John100% (2)

- Chapter 1. OverviewDocument58 pagesChapter 1. OverviewmgitecetechNo ratings yet

- ID-LA-IsO Series Low Cost RFID Reader Module Used Animal Tagging LF ISO11785Document10 pagesID-LA-IsO Series Low Cost RFID Reader Module Used Animal Tagging LF ISO11785AbleIDLtdNo ratings yet

- Pic Microcontroller 2.1 Pic It Is A Family of Modified Harvard Architecture Microcontrollers MadeDocument16 pagesPic Microcontroller 2.1 Pic It Is A Family of Modified Harvard Architecture Microcontrollers MadeSuresh KumarNo ratings yet

- TPS12 Encoder Decfsdlmfoder CODEC Data ManualDocument5 pagesTPS12 Encoder Decfsdlmfoder CODEC Data ManualSikandar MirzaNo ratings yet

- Lecture12-Using PIC Micro Controller 16F877ADocument57 pagesLecture12-Using PIC Micro Controller 16F877ADoodee Mohammed100% (4)

- Abstract 2. Circuit Diagram 3. Explanation 4. Working 5. Program Code 6. PCB Layout Fabrication and Assembly 8. Conclusion 9. Reference 10. DatasheetDocument22 pagesAbstract 2. Circuit Diagram 3. Explanation 4. Working 5. Program Code 6. PCB Layout Fabrication and Assembly 8. Conclusion 9. Reference 10. Datasheetaditya_pundirNo ratings yet

- MCP2016 16 Bit I-O I2C PDFDocument38 pagesMCP2016 16 Bit I-O I2C PDFwhynot05No ratings yet

- Tda 10021 DatasheetDocument17 pagesTda 10021 DatasheetWilly DacoNo ratings yet

- Mpa Question Bank1Document16 pagesMpa Question Bank1Sharon FrancisNo ratings yet

- UG - EC303 DSP Part-6 On-Chip Peripherals-Print PDFDocument20 pagesUG - EC303 DSP Part-6 On-Chip Peripherals-Print PDFapuurvaNo ratings yet

- At91sam7s64 DsDocument491 pagesAt91sam7s64 DsLord_JoelNo ratings yet

- LS7366 PulseCounter PDFDocument10 pagesLS7366 PulseCounter PDFJoan WascNo ratings yet

- Document On Interfacing ADC With 8051 MicrocontrollerDocument5 pagesDocument On Interfacing ADC With 8051 MicrocontrollerSrideviKumaresanNo ratings yet

- Intelligent Water Control System Using 8051 (AT89C51) : Project ReportDocument12 pagesIntelligent Water Control System Using 8051 (AT89C51) : Project ReportNadeem AnjumNo ratings yet

- Z3 2 4Document104 pagesZ3 2 4Vu Duc Hoan100% (1)

- ST14Document6 pagesST14Adam LopezNo ratings yet

- RTL 8186Document50 pagesRTL 8186Maria Alejandra DalcolmoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Systems Advantages of 1553Document8 pagesSystems Advantages of 1553Deepa DevarajNo ratings yet

- Tina Ti Spice ModelsDocument17 pagesTina Ti Spice Modelsdragos_bondNo ratings yet

- Spec - Dappro 16Mb SRAM - 5V - QFP68Document23 pagesSpec - Dappro 16Mb SRAM - 5V - QFP68Deepa DevarajNo ratings yet

- Standard Wire Gauge ListDocument3 pagesStandard Wire Gauge ListDeepa DevarajNo ratings yet

- Vehicle Rto Exam FaqDocument1 pageVehicle Rto Exam FaqDeepa DevarajNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDeepa DevarajNo ratings yet

- 2N6849 LP PMOS IR For Neg SupplyDocument7 pages2N6849 LP PMOS IR For Neg SupplyDeepa DevarajNo ratings yet

- 2 N 5153Document3 pages2 N 5153Deepa DevarajNo ratings yet

- NPN 2N5671 - 2N5672: H I G H C U R R e N T F A S T S W I T C H I N G A P P L I C A T I o N SDocument0 pagesNPN 2N5671 - 2N5672: H I G H C U R R e N T F A S T S W I T C H I N G A P P L I C A T I o N SDeepa DevarajNo ratings yet

- 2N5672Document13 pages2N5672Deepa DevarajNo ratings yet

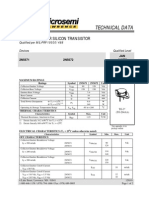

- Technical Data: NPN High Power Silicon TransistorDocument2 pagesTechnical Data: NPN High Power Silicon TransistorDeepa DevarajNo ratings yet

- 2N3637Document0 pages2N3637Deepa DevarajNo ratings yet

- Technical Data: PNP High Power Silicon TransistorDocument3 pagesTechnical Data: PNP High Power Silicon TransistorDeepa DevarajNo ratings yet

- Eatures Jan, Jantx, and Jantxv D B S P CDocument1 pageEatures Jan, Jantx, and Jantxv D B S P CDeepa DevarajNo ratings yet

- SpecificationsDocument4 pagesSpecificationsDeepa DevarajNo ratings yet

- Description Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDocument0 pagesDescription Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDeepa DevarajNo ratings yet

- 1N4565 4584aDocument3 pages1N4565 4584aDeepa DevarajNo ratings yet

- Startup Design and Analysis NoteDocument6 pagesStartup Design and Analysis NoteDeepa DevarajNo ratings yet

- 1N4620Document4 pages1N4620Deepa DevarajNo ratings yet

- Epson TM t82Document2 pagesEpson TM t82lalukurniawanNo ratings yet

- Scissor LiftDocument27 pagesScissor LiftKalai100% (1)

- Technical Documentation - Regulation (EU) N. 2281 - 2016 - NECS 1314 - 3218 SEERDocument59 pagesTechnical Documentation - Regulation (EU) N. 2281 - 2016 - NECS 1314 - 3218 SEERAlexandru GNo ratings yet

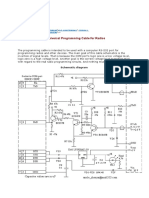

- A Universal Programming Cable For Radios: Schematic DiagramDocument60 pagesA Universal Programming Cable For Radios: Schematic Diagrambairt1972No ratings yet

- 1 Computer Basic Input Devices, Output Devices, System Unit, ProcessorDocument58 pages1 Computer Basic Input Devices, Output Devices, System Unit, ProcessorAbhishek MittalNo ratings yet

- VW (Cod Eroare Diagnostic) - 982691461210 - 20220923143809Document2 pagesVW (Cod Eroare Diagnostic) - 982691461210 - 20220923143809Marius ButaciuNo ratings yet

- Rev1 Sew Gear MotorDocument248 pagesRev1 Sew Gear MotorWirote DewilaiNo ratings yet

- Carrier Detect Installation Manual With RSM (r0)Document4 pagesCarrier Detect Installation Manual With RSM (r0)Rodrigues MillsNo ratings yet

- PW M Generator Curso e Faça Voce MesmoDocument6 pagesPW M Generator Curso e Faça Voce MesmoEcoteck TécnicaNo ratings yet

- Price List 2022 WhatsAppDocument72 pagesPrice List 2022 WhatsAppVrijesh RathodNo ratings yet

- GamBar Kerja LKS 2011 JatimDocument7 pagesGamBar Kerja LKS 2011 JatimDidikIswantoNo ratings yet

- Environment Monitoring and Device Control Using Arm Based Embedded Controlled Sensor NetworkDocument4 pagesEnvironment Monitoring and Device Control Using Arm Based Embedded Controlled Sensor Networkhamed razaNo ratings yet

- Gek 113386BDocument656 pagesGek 113386Bmohammed aliNo ratings yet

- VRV X CatalogueDocument54 pagesVRV X CatalogueTamNo ratings yet

- RB600 PDFDocument8 pagesRB600 PDFJoseAugustoOsteicoecheaNo ratings yet

- Caterpillar Cat GC45K SWB Forklift Lift Trucks Service Repair Manual SN AT87-00001 and Up PDFDocument35 pagesCaterpillar Cat GC45K SWB Forklift Lift Trucks Service Repair Manual SN AT87-00001 and Up PDFfjkskekmdmme50% (2)

- GT Seal Oil System StartupDocument5 pagesGT Seal Oil System StartupHamid AliNo ratings yet

- Recuperar Driver GhostDocument3 pagesRecuperar Driver GhostainhoazalaNo ratings yet

- M52TU Throttle Valve CodesDocument3 pagesM52TU Throttle Valve Codeswicka3No ratings yet

- Third Periodical Test in English and Science 6Document16 pagesThird Periodical Test in English and Science 6aiko idio100% (2)

- CLG835 Deutz EngineDocument72 pagesCLG835 Deutz EngineLinio Calixto De JesusNo ratings yet

- Systems Operation Sistema Electrico 2301Document26 pagesSystems Operation Sistema Electrico 2301Victor Timana SilvaNo ratings yet

- VW Tiguan 2 Propshaft Rear Final Drive EngDocument87 pagesVW Tiguan 2 Propshaft Rear Final Drive Engjose reirizNo ratings yet

- Kto12TLE-ICT Computer Hardware ServicingDocument84 pagesKto12TLE-ICT Computer Hardware ServicingJanus SalinasNo ratings yet

- Annunciator: Key BenefitsDocument3 pagesAnnunciator: Key BenefitsJohn GarnetNo ratings yet

- Mass of AirDocument11 pagesMass of AirThiago SouzaNo ratings yet

- A Modular Multilevel Inverter For Automotive Drive Trains With Transformer-Based Submodule Voltage BalancingDocument326 pagesA Modular Multilevel Inverter For Automotive Drive Trains With Transformer-Based Submodule Voltage BalancingRodovarNo ratings yet

- LM392Document6 pagesLM392Brzata PticaNo ratings yet

- 1207A & 1207 ManualDocument70 pages1207A & 1207 ManualNILTON MORNo ratings yet

- Supreme MV Power Cable PDFDocument68 pagesSupreme MV Power Cable PDFFreddy Suhartono100% (3)