Professional Documents

Culture Documents

HS-2420RH - Fast Sample and Hol

Uploaded by

Deepa DevarajOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HS-2420RH - Fast Sample and Hol

Uploaded by

Deepa DevarajCopyright:

Available Formats

HS-2420RH

Data Sheet February 2003 FN3554.3

Radiation Hardened Fast Sample and Hold

The HS-2420RH is a radiation hardened monolithic circuit consisting of a high performance operational amplifier with its output in series with an ultra-low leakage analog switch and MOSFET input unity gain amplifier. With an external hold capacitor connected to the switch output, a versatile, high performance sample-and-hold or track-andhold circuit is formed. When the switch is closed, the device behaves as an operation amplifier, and any of the standard op amp feedback networks may be connected around the device to control gain, frequency response, etc. When the switch is opened the output will remain at its last level. Performance as a sample-and-hold compares very favorably with other monolithic, hybrid, modular, and discrete circuits. Accuracy to better than 0.01% is achievable over the temperature range. Fast acquisition is coupled with superior droop characteristics, even at high temperatures. High slew rate, wide bandwidth, and low acquisition time produce excellent dynamic characteristics. The ability to operate at gains greater than 1 frequently eliminates the need for external scaling amplifiers. The device may also be used as a versatile operational amplifier with a gated output for applications such as analog switches, peak holding circuits, etc. Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed here must be used when ordering. Detailed Electrical Specifications for these devices are contained in SMD 5962-95669. A hot-link is provided on our website for downloading.

Features

Electrically Screened to SMD # 5962-95669 QML Qualified per MIL-PRF-38535 Requirements Maximum Acquisition Time - 10V Step to 0.1% . . . . . . . . . . . . . . . . . . . . . . . . . . 4s - 10V Step to 0.01% . . . . . . . . . . . . . . . . . . . . . . . . . 6s Maximum Drift Current . . . . . . . . . . . . . . . . . . . . . . . 10nA (Maximum Over Temperature) TTL Compatible Control Input Power Supply Rejection . . . . . . . . . . . . . . . . . . . . . 80dB Total Dose . . . . . . . . . . . . . . . . . . . . . 100 krad(Si) (Max) No Latch-Up

Applications

Data Acquisition Systems D to A Deglitcher Auto Zero Systems Peak Detector Gated Op Amp

Ordering Information

ORDERING NUMBER 5962R9566901VCC INTERNAL MKT. NUMBER HS1B-2420RH-Q TEMP. RANGE (oC) -55 to 125

Functional Diagram

OFFSET ADJUST 3 1 + 2 4 V+ 5

Pinout

14 LEAD METAL-SEALED SIDE-BRAZED CERAMIC DIP MIL-STD-1835, CDIP2-T14 TOP VIEW

14 SAMPLE/HOLD CONTROL 13 GND 12 NC 11 HOLD CAPACITOR 10 NC 9 V+ 8 NC SAMPLE/ HOLD CONTROL

- INPUT

+ INPUT

7 OUTPUT

IN- 1 IN+ 2 OFFSET ADJUST 3 OFFSET ADJUST 4 V- 5 NC 6 OUTPUT 7

14

HS-2420RH

13 5 11 GND VHOLD CAPACITOR

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 2003. All Rights Reserved All other trademarks mentioned are the property of their respective owners.

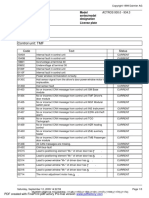

HS-2420RH Test Circuits

VDC ALL RESISTORS = 1% ALL CAPACITORS = 10% 100k 10k +VCC -VCC S2 2 S/H

S7

1 S4 GND S5 1 OPEN 3 2 100k + NULL AMP X1 X-1 BUFFER

DUT

50 2 1 S1 2 S6

1 2

S7

1 50

CH = 1000pF

S3 3

1 50pF

2k

+VCC 1M VAC 50 + ILOAD

AOUT 4 3 EOUT S8 1 2

FIGURE 1. TEST FIXTURE SCHEMATIC (SWITCH POSITIONS S1 - S8 DETERMINE CONFIGURATION)

+5V SINEWAVE INPUT IN2 IN1 IN3 IN4 IN5 IN6 IN7 IN8 A2 A1 EN +15V -15V +15V -15V

OUT VIN

+ DUT 2k CH = 1000pF

VOUT 50pF 50

DUT + 2k S/H CH = 1000pF

VOUT 50pF

A0

SAMPLE/HOLD CONTROL INPUT

NOTE: Compute Hold Mode Feedthrough Attenuation from the Formula: V OUT HOLD FeedthroughAttenuation = 20 log ------------------------------- V IN HOLD Where VOUT HOLD = Peak-Peak Value of Output Sinewave during the Hold Mode. FIGURE 2. HOLD MODE FEEDTHROUGH ATTENUATION

NOTE: GBWP is the Frequency of VINPUT at which: V OUT 20 log -------------------- = 3dB V INPUT

FIGURE 3. GAIN BANDWIDTH PRODUCT

HS-2420RH Test Circuits

(Continued)

SEND SAMPLE COMMAND

SET t2 TO 7s INITIALLY

COURSE tACQ MEASUREMENT LOOP

FINE tACQ MEASUREMENT LOOP

DIGITIZE V1 AT t1 (10s)

INCREMENT t2 BY 50ns (50ns LONGER DELAY)

DIGITIZE V2 AT t2

DECREMENT t2 BY 50ns

DIGITIZE V1 AT t1 (10s) CALCULATE V1 - V2 IS V 0.01%? YES DIGITIZE V2 AT t2

NO DECREMENT t2 BY 50ns RECORD tACQ

YES CALCULATE V1 - V2 IS V 0.01%?

NO

NOTE: See Test Diagram, Timing Diagram FIGURE 4. ACQUISITION TIME (tACQ TO 0.01% IS SHOWN, tACQ TO 0.1% IS DONE IN THE SAME MANNER)

t1

HS-2420RH

V1 V1 DIGITIZER

+ +10V 0V OR 0V -10V S/H CONTROL

+ 50pF 2k 1000pF t1 V2 V2 DIGITIZER

COMPUTER CONTROLLER

10s

DELAY t2 VARIABLE DELAY

t2 DELAY CONTROL

FIGURE 5.

HS-2420RH Timing Waveforms

10V

VIN (POS tACQ CASE) S/H CONTROL

0V 2V 0V 0.01% OR 0.1% ENVELOPE 10V

DUT OUTPUT (POS tACQ CASE) t1

0V (t1 DIGITIZER COMMAND)

t1 10s

t2

(t2 DIGITIZER COMMAND)

t2

FIGURE 6. TIMING DIAGRAM FOR ACQUISITION TIME, (POSITIVE tACQ CASE)

+V

0V

VPEAK 90%

VFINAL 10%

INPUT 10% 0V +OS, tR -OS, tF -V tR tF 90% VFINAL VPEAK

FIGURE 7A.

FIGURE 7B.

FIGURE 7. OVERSHOOT, RISE AND FALL TIME WAVEFORMS

+V

+V

+V 75%

+V 25%

INPUT 25% -V +SL -SL -V -V t t 75% -V

FIGURE 8A. FIGURE 8. SLEW RATE WAVEFORMS

FIGURE 8B.

HS-2420RH Typical Performance Curves

1000 DRIFT DURING HOLD AT 25oC mV/s

VSUPPLY = 15VDC , TA = 25oC, CH = 1000pF, Unless Otherwise Specified

1000 LOWER 3dB FREQUENCY = 10Hz OUTPUT NOISE HOLD MODE HOLD STEP OFFSET ERROR (mV) 100 mVRMS EQUIV. INPUT NOISE SAMPLE MODE - 100K SOURCE RESISTANCE 10 EQUIV. INPUT NOISE SAMPLE MODE - 0K SOURCE RESISTANCE 1.0mF 1 10 100 1K 10K 100K 1M

100 UNITY GAIN PHASE MARGIN (DEG) 10

1.0

0.1

UNITY GAIN BANDWIDTH (MHz) MIN SAMPLE TIME SLEW RATE/ FOR 0.1% ACCURACY CHARGE RATE 10V SWINGS (ms) V/(ms) 100pF 1000pF 0.01mF 0.1mF

0.01 10pF

CH VALUE

BANDWIDTH

FIGURE 9. TYPICAL SAMPLE AND HOLD PERFORMANCE vs HOLDING CAPACITOR

1000 OPEN LOOP VOLTAGE GAIN (dB)

FIGURE 10. BROADBAND NOISE CHARACTERISTICS

100 80 60 40 20 0 -20 10 100 1K 10K 100K 1M 10M 100M CH = 1.0F CH = 0.1F CH = 0.01F CH = 100pF CH = 1000pF

100 ID (pA) 10 1 -50 -25 0 25 50 TEMPERATURE (oC) 75 100 125

FREQUENCY (Hz)

FIGURE 11. DRIFT CURRENT vs TEMPERATURE

FIGURE 12. OPEN LOOP FREQUENCY RESPONSE

-30 -40 ATTENUATION (dB) -50 -60 -70 -80 -90

OPEN LOOP PHASE ANGLE (DEGREES)

0 20 40 60 80 100 120 140 160 180 200 220 240 10 100

CH = 0.01F CH =1000pF

CH = 1.0F CH = 0.1F

CH 100pF

100

1K

10K

100K

1M

10M

1K

10K

100K

1M

10M

100M

10V SINUSOIDAL INPUT FREQUENCY (Hz)

FREQUENCY (Hz)

FIGURE 13. HOLD MODE FEEDTHROUGH ATTENUATION CH = 1000pF

FIGURE 14. OPEN LOOP PHASE RESPONSE

HS-2420RH Burn-In Circuit

HS-2420RH CERDIP

-IN +IN OFF ADJ OFF ADJ -V NC OUT S/H CTL 14 GND 13 NC 12 HOLD CAP 11 NC 10 +V NC +15V 9 8 D1 C1 6 7 9 8 V1 V2 GND

Irradiation Circuit

1 2 R1 3 4 -15V 5 C2 D2 6 7

1 R 2 3 4 5

14 13 12 GND 11 10

NOTES: R1 = 100k 5% (per socket) C1 = C2 = 0.1F (one per row) or 0.01F (one per socket) D1 = D2 = 1N4002 or equivalent (per board)

NOTES: V1 = +15V V2 = -15V R = 100k

HOLD STEP VOLTAGE (V) +10

S/H CONTROL V+

+5 -10 -5 +5 +10

CH

-5 -10

DC INPUT VOLTAGE (V) CH = 0.1F CH = 10,000pF

+ HS-2420RH

-15 -20 -25 -30 -35

CH = 1000pF

-IN CH = 100pF

+IN

V-

OUT

100k OFFSET TRIM (25mV RANGE)

FIGURE 15. HOLD STEP vs INPUT VOLTAGE

FIGURE 16. BASIC SAMPLE-AND-HOLD (TOP VIEW)

0.002RF RF

INPUT +IN HS-2420RH OUT OUTPUT

INPUT RI -IN HS-2420RH OUT +IN S/H CONTROL RI OUTPUT

-IN RF

S/H CONTROL

S/H CONTROL INPUT

0.002RI S/H CONTROL INPUT -RF GAIN ~ RI GAIN ~ I +

-RF RI

FIGURE 17. INVERTING CONFIGURATION

FIGURE 18. NONINVERTING CONFIGURATION

HS-2420RH Offset and Gain Adjustment

Offset Adjustment

The offset voltage of the HS-2420RH may be adjusted using a 100k trim pot, as shown in Figure 15. The recommended adjustment procedure is: 1. Apply 0V to the sample-and-hold input, and a square wave to the S/H control. 2. Adjust the trim pot for 0V output in the hold mode.

Gain Adjustment

The linear variation in pedestal voltage with sample-and-hold input voltage causes a -0.06% gain error (CH = 1000pF). In some applications (D/A deglitcher, A/D converter) the gain error can be adjusted elsewhere in the system, while in other applications it must be adjusted at the sample-and-hold. The two circuits shown below demonstrate how to adjust gain error at the sample-and-hold. The recommended procedure for adjusting gain error is: 1. Perform offset adjustment. 2. Apply the nominal input voltage that should produce a +10V output. 3. Adjust the trim pot for +10V output in the hold mode. 4. Apply the nominal input voltage that should produce a -10V output. 5. Measure the output hold voltage (V-10 NOMINAL). Adjust the trim pot for an output hold voltage of:

( V-10 NOMINAL ) + ( 10V ) ----------------------------------------------------------------------2

HS-2420RH Die Characteristics

DIE DIMENSIONS: 97 mils x 61 mils x 19 mils METALLIZATION: Type: Al Thickness: 16k 2k GLASSIVATION: Type: Silox Thickness: 14k 2k WORST CASE CURRENT DENSITY: 2.0 x 105A/cm2 TRANSISTOR COUNT: 78 PROCESS: Bipolar-Di

Metallization Mask Layout

HS-2420RH

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporations quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com 8

You might also like

- Applications Features: 1988 Burr-Brown Corporation PDS-837E Printed in U.S.A. October, 1997Document10 pagesApplications Features: 1988 Burr-Brown Corporation PDS-837E Printed in U.S.A. October, 1997Arjuna Ajita Ananta VijayaNo ratings yet

- NCP 2171Document19 pagesNCP 2171mari_casuNo ratings yet

- Energy Metering IC With On-Chip Fault Detection: 8% (30 PPM/ C Typical)Document16 pagesEnergy Metering IC With On-Chip Fault Detection: 8% (30 PPM/ C Typical)saandoNo ratings yet

- CD4047Document15 pagesCD4047mohankumarktvrNo ratings yet

- Ultralow Noise, High Speed, Bifet Op Amp: 冑Hz At 10 Khz V P-P, 0.1 Hz To 10 Hz 冑Hz Current Noise At 1 Khz S Slew RateDocument12 pagesUltralow Noise, High Speed, Bifet Op Amp: 冑Hz At 10 Khz V P-P, 0.1 Hz To 10 Hz 冑Hz Current Noise At 1 Khz S Slew RateVasily KorolevNo ratings yet

- FN 7925Document14 pagesFN 7925praveen_banthiNo ratings yet

- OpAmp - MCP6244Document38 pagesOpAmp - MCP6244Ludwig SchmidtNo ratings yet

- MCP3040 DatasheetDocument40 pagesMCP3040 Datasheetjiajun898No ratings yet

- MCP 3201Document28 pagesMCP 3201Nacer MezghicheNo ratings yet

- Max7490 Max7491Document18 pagesMax7490 Max7491xo9o6No ratings yet

- Applications FeaturesDocument12 pagesApplications FeatureseduardofelisNo ratings yet

- Description Features: CMOS Low-Power Monostable/Astable MultivibratorDocument15 pagesDescription Features: CMOS Low-Power Monostable/Astable Multivibratorதினேஷ் குமார்No ratings yet

- Tda 7293Document16 pagesTda 7293Gerson FelipeNo ratings yet

- Ad 811Document16 pagesAd 811srboghe651665No ratings yet

- LC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778Document12 pagesLC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778tarpinoNo ratings yet

- OPA128Document11 pagesOPA128अमरेश झाNo ratings yet

- 6 - Digit Multimeter: Ordering InformationDocument5 pages6 - Digit Multimeter: Ordering Informationakv_303No ratings yet

- CD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionDocument10 pagesCD4047BC Low Power Monostable/Astable Multivibrator: General DescriptionWillianNo ratings yet

- PWM Module Drv101Document20 pagesPWM Module Drv101DTPHawkNo ratings yet

- High Speed, Monolithic D/A Converter With Reference FeaturesDocument10 pagesHigh Speed, Monolithic D/A Converter With Reference FeaturessohcahtoaNo ratings yet

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DNo ratings yet

- Datasheet AD549Document14 pagesDatasheet AD549Trần Hồng VănNo ratings yet

- CA3059, CA3079: Description FeaturesDocument12 pagesCA3059, CA3079: Description FeaturesMiltongrimi GrimilNo ratings yet

- DRV 103Document24 pagesDRV 103Rahul SharmaNo ratings yet

- 7555 CNDocument9 pages7555 CNdsdsds4No ratings yet

- Datasheet LTC1298 LTC1286 PDFDocument24 pagesDatasheet LTC1298 LTC1286 PDFletterniNo ratings yet

- 2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial InterfaceDocument20 pages2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial Interfacejoseleomi_limaNo ratings yet

- Ca3130, Ca3130aDocument17 pagesCa3130, Ca3130aproctepNo ratings yet

- Max3080 Max3089Document21 pagesMax3080 Max3089Peter BirdNo ratings yet

- AA AA AA AA A A A A A A A: 12-Bit 100 KSPS A/D Converter AD1674Document13 pagesAA AA AA AA A A A A A A A: 12-Bit 100 KSPS A/D Converter AD1674Iancu CiocioiNo ratings yet

- Features Applications: SBOS141Document11 pagesFeatures Applications: SBOS141eslovenitNo ratings yet

- Tda 7294Document17 pagesTda 7294Abubakar SidikNo ratings yet

- XTR 117Document16 pagesXTR 117Compañero DanielqjNo ratings yet

- Difet: Features ApplicationsDocument9 pagesDifet: Features ApplicationsodipasNo ratings yet

- Features Description: D D D D D D D D D D D DDocument16 pagesFeatures Description: D D D D D D D D D D D D1eugen1No ratings yet

- 2.7V Dual Channel 12-Bit A/D Converter With SPI Serial InterfaceDocument34 pages2.7V Dual Channel 12-Bit A/D Converter With SPI Serial InterfaceManjunatha Ac100% (1)

- AD815Document16 pagesAD815jnax101No ratings yet

- Ad 7524Document8 pagesAd 7524Giovanny ContrerasNo ratings yet

- Opa 277Document27 pagesOpa 277Wahyu PalanchoiNo ratings yet

- Ad 421Document14 pagesAd 421Vishal Devrao JadhavNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- Hall SenzorDocument15 pagesHall SenzorfelixmosNo ratings yet

- Precision, Low Cost, High Speed, Bifet Op Amp: Ⴞ0.01% In 1.0 S S Min Slew Rate (Ad711J)Document16 pagesPrecision, Low Cost, High Speed, Bifet Op Amp: Ⴞ0.01% In 1.0 S S Min Slew Rate (Ad711J)egrumelNo ratings yet

- Discontinued Product: Ratiometric Linear Hall Effect Sensor Ics For High-Temperature OperationDocument13 pagesDiscontinued Product: Ratiometric Linear Hall Effect Sensor Ics For High-Temperature OperationceferrruNo ratings yet

- OPA277Document9 pagesOPA277Ahtesham KhanNo ratings yet

- ADC0802, ADC0803 ADC0804: Features DescriptionDocument17 pagesADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataNo ratings yet

- Uc2854b EpDocument13 pagesUc2854b EpBruno NascimentoNo ratings yet

- MCP3202 PDFDocument28 pagesMCP3202 PDFblue11111No ratings yet

- Max3160 Max3162Document23 pagesMax3160 Max3162jb2015831No ratings yet

- 1.25, Dual SPST, CMOS Analog Switches: General Description FeaturesDocument12 pages1.25, Dual SPST, CMOS Analog Switches: General Description FeaturesStefan GlaserNo ratings yet

- DAC0808 DatasheetDocument12 pagesDAC0808 DatasheetRicky CoxNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Standard Wire Gauge ListDocument3 pagesStandard Wire Gauge ListDeepa DevarajNo ratings yet

- Systems Advantages of 1553Document8 pagesSystems Advantages of 1553Deepa DevarajNo ratings yet

- Spec - Dappro 16Mb SRAM - 5V - QFP68Document23 pagesSpec - Dappro 16Mb SRAM - 5V - QFP68Deepa DevarajNo ratings yet

- 2N6849 LP PMOS IR For Neg SupplyDocument7 pages2N6849 LP PMOS IR For Neg SupplyDeepa DevarajNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument3 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDeepa DevarajNo ratings yet

- Tina Ti Spice ModelsDocument17 pagesTina Ti Spice Modelsdragos_bondNo ratings yet

- Vehicle Rto Exam FaqDocument1 pageVehicle Rto Exam FaqDeepa DevarajNo ratings yet

- 2 N 5153Document3 pages2 N 5153Deepa DevarajNo ratings yet

- 2N5672Document13 pages2N5672Deepa DevarajNo ratings yet

- Technical Data: NPN High Power Silicon TransistorDocument2 pagesTechnical Data: NPN High Power Silicon TransistorDeepa DevarajNo ratings yet

- 2N3637Document0 pages2N3637Deepa DevarajNo ratings yet

- NPN 2N5671 - 2N5672: H I G H C U R R e N T F A S T S W I T C H I N G A P P L I C A T I o N SDocument0 pagesNPN 2N5671 - 2N5672: H I G H C U R R e N T F A S T S W I T C H I N G A P P L I C A T I o N SDeepa DevarajNo ratings yet

- Technical Data: PNP High Power Silicon TransistorDocument3 pagesTechnical Data: PNP High Power Silicon TransistorDeepa DevarajNo ratings yet

- Description Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDocument0 pagesDescription Appearance: Surface Mount Voidless-Hermetically-Sealed Ultra Fast Recovery Glass RectifiersDeepa DevarajNo ratings yet

- Eatures Jan, Jantx, and Jantxv D B S P CDocument1 pageEatures Jan, Jantx, and Jantxv D B S P CDeepa DevarajNo ratings yet

- 1N4565 4584aDocument3 pages1N4565 4584aDeepa DevarajNo ratings yet

- SpecificationsDocument4 pagesSpecificationsDeepa DevarajNo ratings yet

- 1N4620Document4 pages1N4620Deepa DevarajNo ratings yet

- Startup Design and Analysis NoteDocument6 pagesStartup Design and Analysis NoteDeepa DevarajNo ratings yet

- 2016 EXPT Blu1718,1719Document1 page2016 EXPT Blu1718,1719Toto MidgleyNo ratings yet

- DMW 3305 30116 1 3305 602 - Is00Document1 pageDMW 3305 30116 1 3305 602 - Is00nuramirah2023No ratings yet

- Nissan Primera Engine Control SystemDocument1,794 pagesNissan Primera Engine Control SystemMarek100% (2)

- PV45 0 811 405 096 Amplifier Card Bosch Manual 1 PDFDocument8 pagesPV45 0 811 405 096 Amplifier Card Bosch Manual 1 PDFDennis Xenos20% (5)

- Install A Crisscross With Any Leg Vise Hardware, Begin HereDocument24 pagesInstall A Crisscross With Any Leg Vise Hardware, Begin Herexx xxxNo ratings yet

- EN - Ditec EL34 Control Panel Technical Manual PDFDocument16 pagesEN - Ditec EL34 Control Panel Technical Manual PDFHildenira SousaNo ratings yet

- TH420 Operating Manual EnglishDocument64 pagesTH420 Operating Manual EnglishLeofler Laureta Aguinaldo0% (1)

- PL Feature - Boot Flash Loader - Um PDFDocument89 pagesPL Feature - Boot Flash Loader - Um PDFerradicaNo ratings yet

- Hino 700 Exhaust Brake-Engine Retarder WireingDocument2 pagesHino 700 Exhaust Brake-Engine Retarder Wireingg.shien5150100% (1)

- BA SI 078 07 18 EN Motorpumpe Sigma X S1Cb EN PDFDocument120 pagesBA SI 078 07 18 EN Motorpumpe Sigma X S1Cb EN PDFmanoj_sitecNo ratings yet

- Open Development EnvironmentDocument16 pagesOpen Development EnvironmentMihaiNeacsuNo ratings yet

- Current Fault Codes: Code Text StatusDocument3 pagesCurrent Fault Codes: Code Text StatusnaftaliNo ratings yet

- Flat Cables Ribbon Cables: Works Photo: HELUKABELDocument10 pagesFlat Cables Ribbon Cables: Works Photo: HELUKABELOzanNo ratings yet

- Arduino SHT15 HumidityDocument6 pagesArduino SHT15 Humiditypeterson_msc5No ratings yet

- ForkliftsDocument21 pagesForkliftsManual ForkliftNo ratings yet

- Leviton VRS05-1L Installation ManualDocument2 pagesLeviton VRS05-1L Installation ManualAlarm Grid Home Security and Alarm MonitoringNo ratings yet

- 1 Table of Contents 3 Before Starting: HM 460 HM 660Document22 pages1 Table of Contents 3 Before Starting: HM 460 HM 660Muzaffar shahidNo ratings yet

- CPSG 110 60hz en Cummins 6r5.9lDocument2 pagesCPSG 110 60hz en Cummins 6r5.9lErick Domínguez CansecoNo ratings yet

- GOT1000 HandbookDocument220 pagesGOT1000 HandbookREDDYGAARI ABBAYI100% (1)

- MF Tea20 Te20Document408 pagesMF Tea20 Te20Samuel Herren100% (2)

- 1001 Installation Operation ManualDocument69 pages1001 Installation Operation ManualArjunroyEdward100% (1)

- In 14 6TubeClock en V1.2Document14 pagesIn 14 6TubeClock en V1.2Enéas BaroneNo ratings yet

- Module IT COM1 Unit 4Document15 pagesModule IT COM1 Unit 4Joshua DalmacioNo ratings yet

- Codigo de Fallas CATERPILLAR c15Document6 pagesCodigo de Fallas CATERPILLAR c15Junior Lester78% (23)

- 33XR ManualDocument20 pages33XR ManualAbubacker SiddiqNo ratings yet

- Altronics de 3000 IOI 9 08Document85 pagesAltronics de 3000 IOI 9 08Felix ZavalaNo ratings yet

- D50 60 70S-5 (Sb1101e05)Document401 pagesD50 60 70S-5 (Sb1101e05)goxmad100% (1)

- Pistones SMCDocument72 pagesPistones SMCIsai AnguianoNo ratings yet

- Removing and Installing Parktronic System (PTS) Control ModuleDocument1 pageRemoving and Installing Parktronic System (PTS) Control Modulehellios8502No ratings yet

- MAN B&W S70ME-C8.2-TII: Project Guide Electronically Controlled Twostroke EnginesDocument387 pagesMAN B&W S70ME-C8.2-TII: Project Guide Electronically Controlled Twostroke EnginesСлавик Мосин100% (1)