Professional Documents

Culture Documents

Jntu Online Examinations (Dld-Mid-I) : Value

Uploaded by

Sai RamOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Jntu Online Examinations (Dld-Mid-I) : Value

Uploaded by

Sai RamCopyright:

Available Formats

www.jntuworld.

com

www.jwjobs.net

JNTU ONLINE EXAMINATIONS [DLD-MID-I]

1) 1.The number of zero bits precede the binary number will = Ans:-does not change its value 2) Group of four bits are called Ans:-nibbles 3) Group of sixteen bits are called Ans:- words 4) The byte can represent signed numbers in the range of = Ans:--128 .....+127 5) Inside today's computers, data is represented as Ans:-zeros = and ones 6) Most modern digital systems operate using a Ans:-binary = logic 7) Binary uses a powers of Ans:-2 8) To convert a binary number to decimal Ans:- for each '1' in = the binary string, add 2n 9) The decimal equivalent of 0000000111 is Ans:-7 10) The left most bit is typically called the Ans:- higher order = bit 11) Group of eight bits are called Ans:-bytes 12) The smallest unit of information which a computer can understand = is Ans:- bit 13) Convert the binary number 11.11 in to the decimal = Ans:-3.75 14) ( 2AC5.D)16 =3D ( ? )8 Ans:-10949. 8125 = 15) (623.77)8 =3D ( ?)16 Ans:- 193.FC 16) Going form binary to hexadecimal, grouping of four bits can be = obtained by Ans:added as zero padding on the MSB 17) Convert 172 in octal to decimal Ans:-122 18) The number of binary digits for each octal digit are = Ans:-3 19) Convert the binary number 001100111010 into octal number = Ans:-1472 20) Convert 15E hex to decimal Ans:-350 21) Convert the binary number 001100111010 to Hexadecimal number Ans:-33A 22) Octal is most useful when the binary sequence is multiples of = Ans:- three 23) Hexa decimal is most useful when the binary sequence is multiples = of Ans:-four 24) Taking the complement of a number twice leaves the Ans:-number = as it is 25) To find out the complement of an n digit number the following = relation is valid one Ans:- r's complement =3D rn -number 26) In signed magnitude representation the sign is represented by the Ans:-MSB 27) In the signed magnitude representation the MSB of the binary = number is 1 then the number is Ans:negative 28) In the signed magnitude representation -4 is represented as Ans:-1100 29) Complementary representations are used to denote the = Ans:-negative of a given number 30) Find the 1's complement of the binary number 0101 = Ans:-1010 31) Find the 2's complement of the binary number 0101 = Ans:-1011 32) Obtain the 9's complement of the decimal number 13469 = Ans:-86530 33) Obtain the 10's complement of the decimal number 90099 = Ans:-09901 34) The advantage of Gray code over the straight binary number = sequence is Ans:-only one bit changes when going from one number to the = next 35) The standard binary code for the alphanumeric characters is Ans:-ASCII 36) The Format effectors of ASCII code are characters that = Ans:-control the layout of printing 37) To detect the errors during transmission of information from one = location to another, the followi ng method is used Ans:-a parity bit is = added to the message 38) The number of circuit elements required to represent a binary = number of n digits are Ans:- n

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

39) Computers can understand information only in the form of Ans:-binary 40) The number of distinct combinations obtained from an n-bit binary = code is Ans:-2n 41) The bit combination of an n-bit code is determined from the count = in binary from Ans:0 to 2n-1 42) In BCD, the number of bits required to represent a number with 'n' = decimal digits is Ans:-4n 43) The sum of two BCD digits produces a carry, then the following = correction is required Ans:-add 0110 44) In BCD the minus sign is represented by Ans:-1001 45) The Excess-3 code for the decimal number 698 is Ans:-1001 1100 = 1011 46) The 9's complement of excess-3 code 0110 1100 1000 is = Ans:-1001 0011 0111 47) A register with 16 cells can store a binary number from Ans:-0 = to 216-1 48) When a key is struck, the control enters Ans:-an equivalent = eight-bit alphanumeric character code into the input register 49) The contents of a processor register are transferred into the = Ans:- memory register 50) The number of bits stored in a register with n cells are = Ans:-n 51) 1+1 in binary logic is equal to Ans:-1 52) 1+1 in binary arithmetic is equal to Ans:-10 53) Which of the following device possesses two stable states and is = capable of storing one bit of information Ans:-binary cell 54) A register is a group of Ans:-binary cells 55) The information from the input register is transferred into the Ans:-four least significant cells of a processor register 56) The difference between binary arithmetic and binary logic is = Ans:-An arithmetic variable designates a number consist of many digits and y = logic variable is always either 1 or 0 57) The multiplicative identity in Boolean algebra is Ans:-1 58) In Boolean algebra there is no subtraction or division operations = because Ans:-it does not have additive or multiplicative inverses 59) Reduce the Boolean expression A'C' + ABC + AC' to three literals Ans:-AB + C' 60) The additive identity in Boolean algebra is Ans:-0 61) Switching algebra means Ans:-a two valued Boolean algebra 62) Switching algebra can be represented by a electric circuit of Ans:-bistable 63) x + x' is equal to Ans:-1 64) The Boolean expression xyz + x'y + xyz' can be rep resented with a = number of literals of Ans:- y 65) x + ( y . z ) =3D Ans:-(x+y) . ( x+ z) 66) The complement of a Boolean x'yz' + x'y'z is Ans:-(x + y'+ z) = (x + y + z') 67) The Boolean function for the following circuit shown in = Fig.1 68) = Ans:-x'+y 69) Ans:70) The generalized form of DeMorgan's theorem states that = Ans:-the complement of a function is obtained by interchanging AND and OR = operators and complementing each literal 71) According to duality principle every algebraic expression = deducible from the p ostulates of Boolean algebra remains valid if Ans:-the = operators and identity elements are interchanged 72) If the dual of an algebraic expression is desired then Ans:-interchange OR and AND operators and

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

replace 1's by 0's and = 0's by 1's 73) A Boolean function described by an algebraic expression consists = of Ans:-binary variables, the constants 0 and 1, and the logic = operation symbols 74) For a given value of the binary variables, the Boolean function = can be equal to Ans:either 1 or 0 75) The number of rows in the truth table of a Boolean function with n = variables is Ans:-2n 76) A Boolean function can be transformed from an algebraic expression = into a circuit composed of Ans:logic gates 77) Express the Boolean function F=3Dxy+xz' in a Product of maxterm s Ans:F=3D(x+y+z)(x+y'+z)(x'+y+z)(x'+y+z') 78) Determine the complement of the function F(x,y,z) =3D( = 1,3,6,7) Ans:- F(x,y,z) =3D (0,2,4,5) 79) Maxterm is the complement of its corresponding = Ans:-minterm 80) Express the Boolean function F=3DA+B'C in a sum of minterms Ans:F=3DA'B'C+AB'C+AB'C+ABC'+ABC 81) The number of minterms formed from n variables are Ans:-2n = 82) The Minterm is obtained from Ans:-an AND term of the n = variables 83) The minterm is also called Ans:-standard product 84) The number of maxterms formed from n variables are Ans:-2n 85) The Maxterm is obtained from Ans:-an OR term of the n = variables 86) The maxterm is also called Ans:-standard sums 87) Boolean functions expressed as a sum of minterms or product of = maxterms are said to be in Ans:canonical form 88) The equivalence function is also called Ans:-XNOR 89) Example of MSI devices is Ans:-counter 90) The following logic family is preferred for high component density = Ans:-MOS 91) The buffer is circuit whi ch produces Ans:-the transfer = function 92) The expression in sum of products can be implemented with = Ans:-NAND gates only 93) The following circuit inverts the logic sense of a binary variable = Ans:-inverter 94) The function that is 1 when the two binary variables are equal is = called Ans:equivalence 95) The complement of Exclusive-OR is called Ans:-Equivalence 96) Negative logic system is defined as Ans:-Low =13level = represent logic 1 97) A positive logic AND gate can operate as a Ans:- negative = logic OR 98) Eight adjacent squares of k-map represent a term of Ans:-one literal 99) In the K-map any two adjacent squares differ by Ans:-only one = variable which is primed in one square and unprimed in the other 100) If a minterm in a square is covered by only one prime implicant, = that prime implicant is said to be Ans:-essential 101) The Boolean expression for the following map is 102) = Ans:-B'D' + A'CD' 103) The square in K-map represents a Ans:-min term 104) From K-map we can find a Boolean expression with a = Ans:-minimum number of terms and gates 105) The number of min terms for a three variable map is Ans:-8 = 106) The minterms of K-map are arranged in the form of a Ans:-gray = code 107) The variable Y in m5 and m7 which are the = two adjacent squares in the K-map then Ans:-Y is primed

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

in = m5 and unprimed in m7 108) The sum of two minterms in adjacent squares of three variable map = can be simplified to a Ans:-Single AND gate 109) The following is the adjacent cell for the cell 15 in five = variable K -map Ans:-31 110) The minimal Product of Sums expression for the following map is = 111) Ans:-f(w,x,y,z) =3D ( y + z)(y' + z')(w + x)(w '+ x') 112) The minimization of function expressed as product of sums is the = dual of that the Ans:-sum of product form 113) An incompletely specified function containing k don't care = combinations actually corresponds to a class of Ans:-2k distinct functions 114) Each don't care combination can be specified in Ans:-either of = 0 or 1 115) Which of the following is used to convert the sum of products to = product of sums Ans:DeMorgan's 116) The logical sum of minterms associated with a Boolean function = specifies the conditions under which the function is equal to Ans:-1 117) The don't care conditions can be used on a map to provide a Ans:-further simplification of the Boolean expressions 118) A don=19t care minterm is a combination of variables whose logical = value is Ans:not specified 119) To obtain a function in product of sums form from K -map the = following procedure is applied Ans:-Mark the empty squares by 0's and = combine them into valid adjacent squares 120) The NAND gate is also called as a Ans:-AND Invert 121) To convert a multilevel AND-OR diagram into an all NAND diagram = the following is used Ans:- covert all OR gates to Invert-OR gates and = all AND gates to AND-Invert gates 122) To implement any Boolean function using NOR gates, it must be in = the form of Ans:product of sums 123) The following symbol represent the gate called 124) Ans:-Invert - OR 125) Which of the following gate is the universal gate Ans:-NAND = 126) The NAND gate is also called as a Ans:- Invert-OR 127) The NOR gate is also called as a Ans:-OR Invert 128) To implement any Boolean function using NAND gates, it must be in = the form of Ans:-sum of products 129) Which of the following gates are equal Ans:-AND-Invert and = Invert OR 130) To convert a multilevel AND-OR diagram into an all NOR diagram the = following is used Ans:- covert all AND gates to Invert-AND gates and = all OR gates to OR-Invert gates 131) The ECL NOR gates, when tied together, perform the Ans:-wired = OR logic 132) Wired logic provide a specific logic by connecting = Ans:-outputs from two gates 133) The logic function implemented by the following circuit is = 134) Ans:-(AB +CD)' 135) NAND or NOR gates allow the possibility of a wire connection = between the outputs of two gates to provide a specific logic function. This type = of logic is called Ans:-wired logic

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

136) The open collector TTL NAND gates, when tied together, perform the = Ans:-wiredAND logic 137) The AND-NOR circuit can be equal to the following circuit Ans:-NAND-AND 138) The OR-NAND circuit can be equal to the following circuit = Ans:-NOR-OR 139) An AND-OR implementation requires an expression in the form of Ans:-Sum of products 140) An OR-AND-INVERT implementation requires an expression in the form = of Ans:Product of sums 141) The multiple variable exclusive -OR operation is defined as = Ans:-an odd function 142) An n-variable exclusive-OR function is an odd function defined as Ans:-the logical sum of 2n/2 minterms whose binary = numerical values have an odd number of 1s 143) Which of the following gate can perform the Boolean function = xy'+x'y Ans:-XOR 144) The complement of exclusive-OR gate is Ans:-exclusive-NOR 145) Ans:-x' 146) Ans:- x 147) Ans:-1 148) Ans:-0 149) Ans:150) The code converter is a circuit that makes the two different = binary code systems are Ans:compatible 151) The length of the various paths in a multilevel combinational = circuit are Ans:-not always constant 152) The output functions specified in the truth table gives the exact definition of the Ans:combinational circuits 153) A combinational circuit consists of logic gates whose outputs at = any time are determined from the Ans:-present combination of inputs 154) A combinational circuit consists of Ans:- logic gates, input = and output variables 155) A combinational circuit has a logic gates with Ans:-no feed = back paths 156) The following is used for logic simulation of combinational = circuit Ans:- verilog HDL 157) The Truth table defines the required relationship between = Ans:-inputs and outputs 158) The input columns of a truth table for a combinational circuit are = obtained from Ans:2n binary numbers for the n input = variables 159) Every combinational circuit corresponds a Boolean function which = describes the circuit Ans:- logical behavior 160) An n-bit binary adder requires ......... number of full adders = with each output carry connected to the ........ Ans:-n, input carry of the = next higher order full adder 161) The over flow occurs when the addition is perform , this problem = in digital computers takes care by using a Ans:-flip-flop 162) The longest propagation delay time in the adder will be the time = it takes Ans:-the carry to propagate through the full adders 163) An overflow occurs if the two numbers added are Ans:-both = positive or both negative 164) The basic arithmetic operation in digital computers is = Ans:-addition 165) A combinational circuit that performs the addition of two bits is = called a Ans:-half adder 166) A combinational circuit that performs the addition of three bits = is called a Ans:-full

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

adder 167) The full adder can be implemented using Ans:-two half = adders 168) To perform addition of two n bit numbers, required full adders are = Ans:-n 169) The output from the half adder is Ans:-sum =3D x'y +xy' , = carry =3Dxy 170) The output form the full adder is = Ans:-S=3Dxy'z'+x'yz'+xyz+x'y'z , C=3Dxy+x'yz+xy'z 171) To construct a Binary Multiplier with J multiplier bits and K = multiplicand bits the following are required Ans:-(J x K ) AND gates and (J-1) = K- bit adders 172) The following is the circuit for the 173) = Ans:-2 x 2 bit Binary multiplier 174) In the binary multiplier the successive partial products are Ans:-shifted one position to the left 175) In the Binary Multiplier the final product is obtained from the Ans:-sum of the partial products 176) BCD adder consists of Ans:-two binary adders and logic circuit = with AND and OR gates 177) In the Decoder the min term equivalent of the binary number = presently available in the input lines represent the Ans:-output whose value = is equal to 1 178) To generate a sum of min terms from n inputs and m outputs = combinational circuit the following is used. Ans:- n-to-2n-line = decoder and m OR gates 179) The combinational circuit that converts binary information from n = input lines to a maximum of 2n unique output lines is called Ans:-Decoder 180) The 3-to-8- line decoder means Ans:-3 inputs are decoded into = 8 outputs 181) Which of the following device is used to convert binary code into = octal Ans:-3-to-8 line Decoder 182) The basic gates required to construct a decoder are Ans:-AND = and NOT 183) In decoder the operation is controlled by the Ans:-enable = signals 184) To construct a 4 x 16 decoder how many 3 x 8 decoders are = required? Ans:-two 185) The Priority encoder produces a binary output code indicating = which of the input lines requesting service has the Ans:-highest priority 186) The operation of the priority encoder is such that , the input = having the highest priority will takeprecedence when the Ans:-two or more = inputs are equal to 1 at the same time 187) To implement any Boolean function of n variables with a = multiplexer requires Ans:-n1 selection inputs, 2n-1 data = inputs 188) In an encoder , when one or more inputs are equal to 1 then it is indicated by setting Ans:-valid bit to 1 189) The advantage of using a three state gates in a multiplexer is Ans:-reducing loading effects 190) A digital circuit that performs the inverse operation of a decoder = is Ans:-encoder 191) Which of the following device is used to convert octal code into = binary code Ans:-3to-8 line Decoder 192) An encoder has Ans:-2n input lines and n out = lines 193) An encoder circuits must establish an input priority to ensure = that Ans:-only one input is active at any given time 194) The number of selection lines required for a 2n input = lines multiplexer is Ans:-n

www.jntuworld.com

www.jntuworld.com

www.jwjobs.net

195) A multiplexer is also called a Ans:-data selector 196) In what way one module definition of verilog HDL can be = incorporated in another module Ans:-instantiating 197) What is the syntax for a output vector D with four bits 0 through = 3 in verilog HDL Ans:-output [0:3] D 198) How the unknown and high impedance are represented in verilog HDL = gate level model Ans:-x and z 199) The gate-level modeling in Verilog HDL describes the circuit by = specifying the Ans:gates and how they are connected with each other 200) The data flow modeling in Verilog HDL describes the circuit by = specifying the Ans:continuous assignment statements 201) The behavioral modeling in Verilog HDL describes the circuit by = specifying the Ans:procedural assignment statements 202) The number of operator types in verilog HDL are Ans:-30 203) In verilog HDL data flow model the 2-to-1 line multiplexer with = data inputs A and B, select input S, and output Y is described by = Ans:-assign Y=3D(A & S) | (B & J S) 204) The behavioral modeling of verilog HDL represents digital circuits = at a Ans:functional and algorithmic level 205) The gate level modeling of verilog HDL represents digital circuits = at a Ans:-gate level

www.jntuworld.com

You might also like

- DSP Assingmnet 1Document27 pagesDSP Assingmnet 1Info StudioNo ratings yet

- Digital Logic DesignDocument126 pagesDigital Logic Designmt21215015 Navdeep GuptaNo ratings yet

- Digital Logic Important Objective Questions Unit-2: 11101111111 1001000 011010 Ans-001100011 Ans-101001 Ans-1000011Document3 pagesDigital Logic Important Objective Questions Unit-2: 11101111111 1001000 011010 Ans-001100011 Ans-101001 Ans-1000011Soumen MitraNo ratings yet

- Capgemini Pseudo Code MCQsDocument10 pagesCapgemini Pseudo Code MCQsSristi KumariNo ratings yet

- DG Iqs FullDocument126 pagesDG Iqs FullShyamala Venkataramani100% (2)

- Sign Bit DetectorDocument11 pagesSign Bit DetectorkaranNo ratings yet

- Ans: DDocument10 pagesAns: DVishal FernandesNo ratings yet

- Co 2 Marks All Units Q & A Final PrintDocument10 pagesCo 2 Marks All Units Q & A Final PrintArun VijayNo ratings yet

- 2008oct FE AM QuestionsDocument31 pages2008oct FE AM QuestionsKhun Aung PaingNo ratings yet

- Assignment 7Document3 pagesAssignment 7ravichandrasadineniNo ratings yet

- CS 430 PROJECT - (V02) Introduction To AlgorithmsDocument5 pagesCS 430 PROJECT - (V02) Introduction To Algorithmspushpendra singhNo ratings yet

- 13 CS1FC16 AccuracyDocument6 pages13 CS1FC16 AccuracyAnna AbcxyzNo ratings yet

- C ProblemsDocument13 pagesC Problemspriyojit_hitkNo ratings yet

- Intro To HDL-PREMID-Q1-Q2Document16 pagesIntro To HDL-PREMID-Q1-Q2Ceasy Boy PeraltaNo ratings yet

- Sol 05Document8 pagesSol 05SonnySonniNo ratings yet

- Digital Data Representation and ArithmeticDocument97 pagesDigital Data Representation and ArithmeticshastryNo ratings yet

- Sec 33 BDocument1 pageSec 33 BroufixNo ratings yet

- GATE 2024 CSE Slot 1 Question Paper Feb 10Document8 pagesGATE 2024 CSE Slot 1 Question Paper Feb 10Aditya GuptaNo ratings yet

- 5/24/2014 02:05:00 PM Varuna V: BEL Old Question Paper With AnswersDocument15 pages5/24/2014 02:05:00 PM Varuna V: BEL Old Question Paper With AnswersUddipto SenNo ratings yet

- Dr.N.G.P. Institute's EC2203 Digital Electronics Two Mark QuestionsDocument30 pagesDr.N.G.P. Institute's EC2203 Digital Electronics Two Mark Questionskarthimegs100% (1)

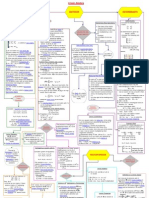

- CE206 MATLAB FundamentalsDocument43 pagesCE206 MATLAB FundamentalssjrokzNo ratings yet

- Laboratory Work #1 Researching Interface of The MATLAB, Working With Numbers and Arrays, Plotting 1d FunctionsDocument16 pagesLaboratory Work #1 Researching Interface of The MATLAB, Working With Numbers and Arrays, Plotting 1d FunctionsОлександр Андрійович КлименкоNo ratings yet

- Cyclic Error-Correcting Codes: Daniel F. Russell December 14, 2001 Dr. Edward Green, AdvisorDocument14 pagesCyclic Error-Correcting Codes: Daniel F. Russell December 14, 2001 Dr. Edward Green, Advisorኤርሚያስ ስለሺNo ratings yet

- Answer The QuestionsDocument7 pagesAnswer The QuestionsSatabdi DasNo ratings yet

- Two Mark & 12 Mark QuestionsDocument42 pagesTwo Mark & 12 Mark QuestionsAnas Ricky ANo ratings yet

- 2marks With AnswerDocument46 pages2marks With AnswerhariNo ratings yet

- Logic Circuits Design FundamentalsDocument52 pagesLogic Circuits Design FundamentalsMubeen NaeemNo ratings yet

- TPO Homework Spring 2013Document8 pagesTPO Homework Spring 2013Haja SheriefNo ratings yet

- Lesson 2 - Data in ComputerDocument78 pagesLesson 2 - Data in ComputerNguyễn Ngoc AnhNo ratings yet

- St. Joseph'S College of Engineering Department of Ece Multiple Choice Questions (MCQ) Subject: Ec 8553-Discrete Time Signal Processing (Unit I)Document65 pagesSt. Joseph'S College of Engineering Department of Ece Multiple Choice Questions (MCQ) Subject: Ec 8553-Discrete Time Signal Processing (Unit I)formyphdNo ratings yet

- True or False: StackDocument15 pagesTrue or False: StackAmro AbosaifNo ratings yet

- Solving systems of linear equationsDocument25 pagesSolving systems of linear equationsmvdurgadeviNo ratings yet

- Practice Set Python-Math Functions November 2021Document11 pagesPractice Set Python-Math Functions November 2021sujal viraniNo ratings yet

- Bài tập phân tích thiết kế giải thuậtDocument24 pagesBài tập phân tích thiết kế giải thuậtHiệp Sĩ GiấyNo ratings yet

- K22021 XLTH DSP (1) .Algorithms.for.Programmers 171to175 20182737 Nguyễn Hoàng Nhật QuangDocument6 pagesK22021 XLTH DSP (1) .Algorithms.for.Programmers 171to175 20182737 Nguyễn Hoàng Nhật QuangNhật QuangNo ratings yet

- K22021 XLTH DSP (1) .Algorithms.for.Programmers 171to175 20182737 Nguyễn Hoàng Nhật QuangDocument6 pagesK22021 XLTH DSP (1) .Algorithms.for.Programmers 171to175 20182737 Nguyễn Hoàng Nhật QuangNhật QuangNo ratings yet

- Project 2012f TipsDocument4 pagesProject 2012f TipsibnefenerNo ratings yet

- Syll Sample JRF (CS) (CSB) 2014Document60 pagesSyll Sample JRF (CS) (CSB) 2014prabhakargoliNo ratings yet

- Mathematics PQDocument11 pagesMathematics PQAlpha Mythical GamingNo ratings yet

- Lect - 1Document33 pagesLect - 1shivam007No ratings yet

- 1 Exercise HandoutDocument6 pages1 Exercise HandoutshreyasnbhamboreNo ratings yet

- Python For Wbsu 1st Sem.Document6 pagesPython For Wbsu 1st Sem.DIPON PAULNo ratings yet

- Assignment 4Document3 pagesAssignment 4Dinesh Jangid0% (1)

- Algorithms: Swapping, Counting, SummationDocument6 pagesAlgorithms: Swapping, Counting, SummationS PonmalarNo ratings yet

- Equally-Spaced Collinear Subset of A Set. The Algorithm Works by "Overlapping" All EquallyDocument11 pagesEqually-Spaced Collinear Subset of A Set. The Algorithm Works by "Overlapping" All EquallyHemesh SinghNo ratings yet

- 2 CS1FC16 Information RepresentationDocument4 pages2 CS1FC16 Information RepresentationAnna AbcxyzNo ratings yet

- Linear Algebra Flow Diagram 1Document1 pageLinear Algebra Flow Diagram 1stansmith1100% (1)

- Mat Lab SlidesDocument63 pagesMat Lab SlidesMarza Ihsan MarzukiNo ratings yet

- Digital Communications Solutions ManualDocument48 pagesDigital Communications Solutions ManualcasdeaNo ratings yet

- Binary Representations For IntegersDocument13 pagesBinary Representations For IntegerscriNo ratings yet

- Assignment#1 SolutionDocument4 pagesAssignment#1 SolutioneidmohdNo ratings yet

- Digital Computers and Information: (1.1 Through 1.6)Document36 pagesDigital Computers and Information: (1.1 Through 1.6)Abdul AzeezNo ratings yet

- 1 Methods For Solving Systems of Linear EquationsDocument21 pages1 Methods For Solving Systems of Linear EquationsNaimun SirajNo ratings yet

- Fe Am Exam Questions Batch 1Document3 pagesFe Am Exam Questions Batch 1Franch Maverick Arellano Lorilla100% (2)

- Delta XmcqsDocument5 pagesDelta XmcqsGitanjali NayakNo ratings yet

- Digital Electronics For Engineering and Diploma CoursesFrom EverandDigital Electronics For Engineering and Diploma CoursesNo ratings yet

- Department of Computer Science and Engineering: Main Project On Student Info SystemDocument4 pagesDepartment of Computer Science and Engineering: Main Project On Student Info SystemSai RamNo ratings yet

- HW 5 5131 Fall 2013 Due Sept 30Document2 pagesHW 5 5131 Fall 2013 Due Sept 30Sai RamNo ratings yet

- Digital Control Engineering by M GopalDocument451 pagesDigital Control Engineering by M GopalSai RamNo ratings yet

- SGPDocument22 pagesSGPSai RamNo ratings yet

- College Friends Mustafa's Encouragement Through StrugglesDocument1 pageCollege Friends Mustafa's Encouragement Through StrugglesSai RamNo ratings yet

- Jawaharlal Nehru Technological University: Kakinada KAKINADA-533003, Andhra Pradesh (India)Document17 pagesJawaharlal Nehru Technological University: Kakinada KAKINADA-533003, Andhra Pradesh (India)Sai RamNo ratings yet

- 355206585037Document2 pages355206585037Sai RamNo ratings yet

- Imp Questions of 8 Units.Document7 pagesImp Questions of 8 Units.Sai RamNo ratings yet

- 52Document9 pages52Sai RamNo ratings yet

- Evaru Lerani AnakuDocument1 pageEvaru Lerani AnakuSai RamNo ratings yet

- 09Document6 pages09Sai RamNo ratings yet

- 52Document9 pages52Sai RamNo ratings yet

- Instructions To The Dealers.: C-Form Utilization Excel File HelpDocument2 pagesInstructions To The Dealers.: C-Form Utilization Excel File HelpSai RamNo ratings yet

- A Solution To Remote Detection of Illegal Electricity Usage Via Power Line CommunicationsDocument13 pagesA Solution To Remote Detection of Illegal Electricity Usage Via Power Line CommunicationsSai RamNo ratings yet

- JNTUK B.Tech. I Sem Digital Logic Design SyllabusDocument6 pagesJNTUK B.Tech. I Sem Digital Logic Design SyllabusSai RamNo ratings yet

- Song medley from Telugu filmDocument14 pagesSong medley from Telugu filmSai RamNo ratings yet

- Safety Safetydriving 111Document27 pagesSafety Safetydriving 111Sai RamNo ratings yet

- Positive Attitude: Presented by Shaik - Mabu SubaniDocument26 pagesPositive Attitude: Presented by Shaik - Mabu SubaniSai RamNo ratings yet

- 1.hello Rammante: Music: Harris Jayraj Director: Bhaskar Producer: NagababuDocument17 pages1.hello Rammante: Music: Harris Jayraj Director: Bhaskar Producer: NagababuSai RamNo ratings yet

- Seven-Level Shunt Active Power Filter For High-Power Drive SystemsDocument8 pagesSeven-Level Shunt Active Power Filter For High-Power Drive SystemsDivya KoundinyaNo ratings yet

- Jawaharlal Nehru Technological University: Kakinada KAKINADA-533003, Andhra Pradesh (India)Document17 pagesJawaharlal Nehru Technological University: Kakinada KAKINADA-533003, Andhra Pradesh (India)Sai RamNo ratings yet

- Optimal Network Reconfiguration of Distribution System: D.V.A.Sairam IV B.Tech, EeeDocument21 pagesOptimal Network Reconfiguration of Distribution System: D.V.A.Sairam IV B.Tech, EeeSai RamNo ratings yet

- Happy Days title song rock versionDocument6 pagesHappy Days title song rock versionSai RamNo ratings yet

- College Friends Mustafa's Encouragement Through StrugglesDocument1 pageCollege Friends Mustafa's Encouragement Through StrugglesSai RamNo ratings yet

- Mukunda Mukunda Krishna Mukunda MukundaDocument1 pageMukunda Mukunda Krishna Mukunda MukundaSai RamNo ratings yet

- Dinaku DhinDocument3 pagesDinaku DhinSai RamNo ratings yet

- Varsham Munduga Mabbula GarshanaDocument2 pagesVarsham Munduga Mabbula GarshanaSai RamNo ratings yet

- Ye Maya ChesaveDocument7 pagesYe Maya ChesaveSai RamNo ratings yet

- Bharaa SongDocument2 pagesBharaa SongSai RamNo ratings yet

- Gas Dynamic Resonance Ignition For Repetitive StartsDocument8 pagesGas Dynamic Resonance Ignition For Repetitive StartsBrunno VasquesNo ratings yet

- Bresnen M. and Marshall N. 2000a Building Partnerships Case Studies of Client Contractor Collaboration in The UK Construction Industry'Document14 pagesBresnen M. and Marshall N. 2000a Building Partnerships Case Studies of Client Contractor Collaboration in The UK Construction Industry'VivianeLeuchtenbergPEspositoNo ratings yet

- Body Language and AttractionDocument21 pagesBody Language and Attractionpoiqwe1No ratings yet

- Soft Uni SolutionsDocument8 pagesSoft Uni Solutionsnrobastos1451No ratings yet

- Scherrer Equation - WikipediaDocument7 pagesScherrer Equation - WikipediaSilviu-Laurentiu BadeaNo ratings yet

- Purcell 10.2: Solutions To Problem Set 12Document5 pagesPurcell 10.2: Solutions To Problem Set 12Eugene YiNo ratings yet

- Plant SimulationDocument3 pagesPlant SimulationGrant Schorsch KalilNo ratings yet

- Millipore AcademicDocument93 pagesMillipore Academickron541No ratings yet

- Bb101 Chapter 1 Physical Quantities and MeasurementDocument14 pagesBb101 Chapter 1 Physical Quantities and MeasurementAidi AmarNo ratings yet

- Multiple Choice Questions from Past ExamsDocument31 pagesMultiple Choice Questions from Past Examsmasti funNo ratings yet

- IE 404 Mathematical Methods EconomicsDocument2 pagesIE 404 Mathematical Methods EconomicsNaveen GargNo ratings yet

- Electromagnetism WorksheetDocument3 pagesElectromagnetism WorksheetGuan Jie KhooNo ratings yet

- Miriael SabathielDocument1 pageMiriael SabathielPweggleNo ratings yet

- MANT Maintenance Check List For Simplex FL-16, Issue 6Document9 pagesMANT Maintenance Check List For Simplex FL-16, Issue 6hassan SardarNo ratings yet

- Database AdministrationDocument12 pagesDatabase AdministrationjayNo ratings yet

- Kone ErrorDocument2 pagesKone Errorrully hidayatullah50% (2)

- KEY - Unit 12 Test ReviewDocument4 pagesKEY - Unit 12 Test ReviewHayden MulnixNo ratings yet

- Bus Process Audit Toolkit V1.2 PDFDocument35 pagesBus Process Audit Toolkit V1.2 PDFspongebob11No ratings yet

- Postgresql Management and Automation With ClustercontrolDocument42 pagesPostgresql Management and Automation With ClustercontrolYiannisZormpas50% (2)

- Speed Control of Stepper MotorDocument63 pagesSpeed Control of Stepper MotorMohammad Ismail Hossain (Sujohn)100% (4)

- Mysterious Answers To Mysterious Questions - FlattenedDocument52 pagesMysterious Answers To Mysterious Questions - FlattenedKit LangtonNo ratings yet

- grr5504 1e Emeraldcity Playersguidev11Document94 pagesgrr5504 1e Emeraldcity Playersguidev11Kánya Zoltán100% (1)

- Chapter 1 - Purposive CommunicationDocument70 pagesChapter 1 - Purposive CommunicationEnola HolmesNo ratings yet

- Prospectus 2023-24Document11 pagesProspectus 2023-24Niranjan SahooNo ratings yet

- 1 PBDocument11 pages1 PBIyus MaisterNo ratings yet

- Inami, Problem Other MindsDocument19 pagesInami, Problem Other MindsfortyrrNo ratings yet

- Chem 315 - Lab 6 - Simple and Fractional DistilationDocument27 pagesChem 315 - Lab 6 - Simple and Fractional DistilationkNo ratings yet

- Aliceportman Com Septile SeriesDocument5 pagesAliceportman Com Septile SeriestratakNo ratings yet

- RS: Railway reservation systemDocument6 pagesRS: Railway reservation systemSaravana KumarNo ratings yet