Professional Documents

Culture Documents

Chapter5 Virtuoso

Uploaded by

mdzakir_hussainCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter5 Virtuoso

Uploaded by

mdzakir_hussainCopyright:

Available Formats

Chapter

Virtuoso Layout Editor

68

CHAPTER 5: Virtuoso Layout Editor

Figure 5.1: Inverter schematic

Figure 5.2: Inverter symbol

69

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.3: Dialog for creating a Layout View of the inverter cell

Figure 5.4: Initial nactive rectangle

70

CHAPTER 5: Virtuoso Layout Editor

Figure 5.5: nactive rectangle with measurement rulers

71

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.6: Create contact dialog box

72

CHAPTER 5: Virtuoso Layout Editor

Figure 5.7: nactive showing source and drain connections

Figure 5.8: Nmos transistor 3 wide and 0.6 long

73

Figure 5.9: A pmos transistor 6 wide and 0.6 long

74

CHAPTER 5: Virtuoso Layout Editor

Figure 5.10: A pmos transistor inside of an NWELL region

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.11: Extra features dialog box in move mode

75

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.12: Dialog box for the path command

76

CHAPTER 5: Virtuoso Layout Editor

Figure 5.13: Inverter layout with input and output connections made

77

Figure 5.14: Inverter layout with power supply connections

78

CHAPTER 5: Virtuoso Layout Editor

Figure 5.15: Inverter layout with well and substrate connections

79

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.16: Shape pin dialog box

80

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.17: Final inverter layout

81

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.18: Layout with four inverter instances

82

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.19: Layout with four inverter instances expanded to see all levels of layout

83

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.20: Submit Plot dialog box

84

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.21: Plot Options dialog box

Figure 5.22: Nmos transistor layout (with DRC errors)

85

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.23: DIVA DRC control window

86

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.24: Results from the DRC in the CIW window

Figure 5.25: Nmos transistor layout (with DRC errors agged)

87

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.26: Explanation of DRC violation

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.27: Finding all DRC violations

88

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.28: DIVA extraction control window

89

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.29: DIVA extraction special switches

90

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.30: DIVA extraction result in the CIW

91

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.31: Extracted view of the inverter

92

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.32: DIVA LVS control window

93

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.33: DIVA LVS Control Form

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.34: NCSU form to modify LVS rules

94

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.35: DIVA LVS completion indication

95

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.36: DIVA LVS output

96

CHAPTER 5: Virtuoso Layout Editor

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.37: DIVA LVS output (scrolled)

97

(Copyright c 2005, 2010, Cadence Design Systems, Inc. All rights reserved worldwide. Reprinted with permission.)

Figure 5.38: DIVA LVS Run Information window

98

CHAPTER 5: Virtuoso Layout Editor

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (120)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- DSpace TutorialDocument55 pagesDSpace TutorialCristobalPonceSalazar100% (1)

- SS6800 - Line Management System Manual Second RevDocument62 pagesSS6800 - Line Management System Manual Second RevGonza Pf0% (1)

- 02 - OrCAD PSpice System Solution and Industry Application - v3 - HandoutsDocument40 pages02 - OrCAD PSpice System Solution and Industry Application - v3 - HandoutsRicky GNo ratings yet

- Digital System EngineeringDocument635 pagesDigital System Engineeringkakoli_bhatt9091% (11)

- Introduction To Digital AgeDocument5 pagesIntroduction To Digital AgeRylleMatthanCorderoNo ratings yet

- RIS Format Specifications PDFDocument9 pagesRIS Format Specifications PDFFabio GoncalvesNo ratings yet

- Impact of DPU 2017Document6 pagesImpact of DPU 2017mdzakir_hussainNo ratings yet

- EE584 (Fall 2006) Introduction To VLSI CAD ProjectDocument23 pagesEE584 (Fall 2006) Introduction To VLSI CAD Projectmdzakir_hussainNo ratings yet

- Vlsi Manual - 2017-18 PDFDocument97 pagesVlsi Manual - 2017-18 PDFgopalgeniusNo ratings yet

- Switching Circuits and Logic Design - Unit 9 - Week 8Document7 pagesSwitching Circuits and Logic Design - Unit 9 - Week 8mdzakir_hussainNo ratings yet

- Latest From CadenceDocument20 pagesLatest From Cadencemdzakir_hussainNo ratings yet

- Digital LogicDocument197 pagesDigital Logicmdzakir_hussainNo ratings yet

- Switching Circuits and Logic Design - Unit 9 - Week 8Document7 pagesSwitching Circuits and Logic Design - Unit 9 - Week 8mdzakir_hussainNo ratings yet

- Keil MicrovisionDocument157 pagesKeil MicrovisionM Praveen KumarNo ratings yet

- Course Code Course Title Core/Elective Es 933 Ec Electronic Engineering-I Core Contacts Hours Per Week Cie See Credits L T D P NIL 3 0 0 0 30 70 3Document2 pagesCourse Code Course Title Core/Elective Es 933 Ec Electronic Engineering-I Core Contacts Hours Per Week Cie See Credits L T D P NIL 3 0 0 0 30 70 3mdzakir_hussainNo ratings yet

- Systems With GatesDocument191 pagesSystems With Gatesmdzakir_hussainNo ratings yet

- Operational Amplifiers and LinearI Cs - 3EDocument591 pagesOperational Amplifiers and LinearI Cs - 3Emaxwell_eulerNo ratings yet

- M.tech. - Vlsid & VlsiDocument30 pagesM.tech. - Vlsid & VlsiSravan KumarNo ratings yet

- MAT Lab ManualDocument60 pagesMAT Lab ManualjaideepsaiNo ratings yet

- Floating Point Multipliers: Simulation & Synthesis Using VHDLDocument40 pagesFloating Point Multipliers: Simulation & Synthesis Using VHDLmdzakir_hussainNo ratings yet

- AICTE-NPTEL Online Faculty Development ProgrammeDocument10 pagesAICTE-NPTEL Online Faculty Development Programmemdzakir_hussainNo ratings yet

- HDL DesignerDocument754 pagesHDL Designermdzakir_hussainNo ratings yet

- Introducing Deep Learning With MATLABDocument15 pagesIntroducing Deep Learning With MATLABFranco Armando Piña GuevaraNo ratings yet

- FFT Tutorial 121102Document28 pagesFFT Tutorial 121102mdzakir_hussainNo ratings yet

- VivadoHLS Overview PDFDocument43 pagesVivadoHLS Overview PDFAhmedAlazzawiNo ratings yet

- Vivado HLXDocument8 pagesVivado HLXmdzakir_hussainNo ratings yet

- Electronic Lab ManualDocument31 pagesElectronic Lab Manualmdzakir_hussainNo ratings yet

- M.tech. - VLSI System DesignDocument72 pagesM.tech. - VLSI System Designmdzakir_hussainNo ratings yet

- Fir Filter Design ConsiderationsDocument67 pagesFir Filter Design ConsiderationsJohn NashNo ratings yet

- Chapter 5Document48 pagesChapter 5mdzakir_hussainNo ratings yet

- Modified Booth Multiplier and Accumulator PDFDocument9 pagesModified Booth Multiplier and Accumulator PDFmdzakir_hussainNo ratings yet

- Cpe626 MultipliersDocument37 pagesCpe626 Multipliersmdzakir_hussainNo ratings yet

- Lut 7Document5 pagesLut 7rohit_cedt_iiscNo ratings yet

- Data Link Communications Description and OperationDocument1 pageData Link Communications Description and Operation08088338No ratings yet

- Rigol: Data SheetDocument8 pagesRigol: Data SheetFabrizio GiordanoNo ratings yet

- Discover Audio Panning Basics Pro Techniques For Electronic Music ProducersDocument9 pagesDiscover Audio Panning Basics Pro Techniques For Electronic Music Producersbonzborneo71No ratings yet

- Advanced Signals and Systems - Hilbert Transform: Gerhard SchmidtDocument24 pagesAdvanced Signals and Systems - Hilbert Transform: Gerhard SchmidtvondutchlgNo ratings yet

- Getting Started Wp-8xx7Document199 pagesGetting Started Wp-8xx7Pedro BortotNo ratings yet

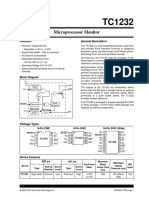

- TC1232Document24 pagesTC1232efremofeNo ratings yet

- CMS 356 Technical Data ENUDocument2 pagesCMS 356 Technical Data ENUKent RenemberNo ratings yet

- 30 LG LED TV Case HistoriesDocument8 pages30 LG LED TV Case Historiesluispider74No ratings yet

- Bruker: RXC Service ManualDocument42 pagesBruker: RXC Service ManualFer GuNo ratings yet

- Time Base GeneratorDocument3 pagesTime Base Generatorsai kishoreNo ratings yet

- BitvoicerDocument7 pagesBitvoicerSusetyo RomadhoniNo ratings yet

- HTS-32 Panasonic Feature - ManualDocument80 pagesHTS-32 Panasonic Feature - ManualWaldirNo ratings yet

- ETAP Report (Modified - 4pages)Document4 pagesETAP Report (Modified - 4pages)daniel.cabasa2577No ratings yet

- AVH-P4400BH AVH-P3400BH AVH-P2400BT AVH-P1400DVD: Owner's ManualDocument112 pagesAVH-P4400BH AVH-P3400BH AVH-P2400BT AVH-P1400DVD: Owner's ManualKevin WatwoodNo ratings yet

- DFT DSM WhitePaper 020510Document17 pagesDFT DSM WhitePaper 020510VeadeshNo ratings yet

- TAL Dub II User Manual ENDocument6 pagesTAL Dub II User Manual ENjohnnyNo ratings yet

- Mobile Radio Communication With Various Digital MoDocument7 pagesMobile Radio Communication With Various Digital MoMohamed FayedNo ratings yet

- Datasheet IXOCAT-enDocument3 pagesDatasheet IXOCAT-enAldo RahmadNo ratings yet

- 1244153Document86 pages1244153Caétano B MascarénhasNo ratings yet

- 93096v00 Beamforming Whitepaper PDFDocument22 pages93096v00 Beamforming Whitepaper PDFEmre KilcioğluNo ratings yet

- MX25L8006E, 3V, 8Mb, v1.2Document53 pagesMX25L8006E, 3V, 8Mb, v1.2Md. Nahid AlamNo ratings yet

- Valley People 610Document2 pagesValley People 610cognis8917No ratings yet

- Simpledsp: A Fast and Flexible DSP Processor Model: (Extended Abstract)Document6 pagesSimpledsp: A Fast and Flexible DSP Processor Model: (Extended Abstract)Alex ObrejanNo ratings yet

- Bn68-09016a-01 QNQ8CB Asia Eng 180406.0Document24 pagesBn68-09016a-01 QNQ8CB Asia Eng 180406.0Parveen ArifNo ratings yet

- LTE PlanningDocument30 pagesLTE Planningkammola2011No ratings yet

- 3.RC Phase ShiftDocument3 pages3.RC Phase ShiftpoojaNo ratings yet

- LZR - I100/ - I110: Laser Scanners For Industrial DoorsDocument12 pagesLZR - I100/ - I110: Laser Scanners For Industrial DoorsMarkos StavropoulosNo ratings yet