Professional Documents

Culture Documents

L16a1616t 1

Uploaded by

vetchboyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

L16a1616t 1

Uploaded by

vetchboyCopyright:

Available Formats

L16A1616T

LCM 200/183/166/143 MHz 3.3 VOLT, 4K REFRESH

ULTRA HIGH PERFORMANCE

1M X 16 SDRAM 2 BANKS X 512Kbit X 16

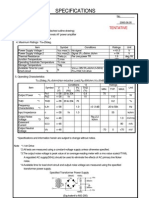

L16A1616T -5 -55 -6 -7 Unit

Clock Frequency (tCK) 200 183 166 143 MHz

Latency 3 3 3 3 clocks

Cycle Time (tCK) 5 5.5 6 7 ns

Access Time (tAC ) 5 5.3 5.5 5.5 ns

Features Description

■ JEDEC Standard 3.3V Power Supply The L16A1616T is a 16,777,216 bits synchro-

■ The L16A1616T is ideally suited for high per- nous high data rate DRAM organized as 2 x

formance graphics peripheral applications 524,288 words by 16 bits. The device is designed to

■ Single Pulsed RAS Interface comply with JEDEC standards set for synchronous

■ Programmable CAS Latency: 2, 3 DRAM products, both electrically and mechanically.

■ All Inputs are sampled at the positive going edge Synchronous design allows precise cycle control

of clock with the system clock. The CAS latency, burst

■ Programmable Wrap Sequence: Sequential or length and burst sequence must be programmed

Interleave into device prior to access operation.

■ Programmable Burst Length: 1, 2, 4, 8 and Full

Page for Sequential and 1, 2, 4, 8 for Interleave

■ UDQM & LDQM for byte masking

■ Auto & Self Refresh

■ 4K Refresh Cycles/64 ms

■ Burst Read with Single Write Operation

Rev.2.9 September 2001

LCM L16A1616T

50 Pin Plastic TSOP-II Pin Names

PIN CONFIGURATION

CLK Clock Input

Top View

CKE Clock Enable

CS Chip Select

VCC 1 50 VSS

I/O1 2 49 I/O16 RAS Row Address Strobe

I/O2 3 48 I/O15

CAS Column Address Strobe

VSSQ 4 47 VSSQ

I/O3 5 46 I/O14 WE Write Enable

I/O4 6 45 I/O13

VCCQ 7 44 VCCQ A0–A10 Address Inputs

I/O5 8 43 I/O12

I/O6 9 42 I/O11 BA Bank Select

VSSQ 10 41 VSSQ

I/O1–I/O16 Data Input/Output

I/O7 11 40 I/O10

I/O8 12 39 I/O9 LDQM, UDQM Data Mask

VCCQ 13 38 VCCQ

LDQM 14 37 NC VCC Power (+3.3V)

WE 15 36 UDQM

CAS 16 35 CLK VSS Ground

RAS 17 34 CKE

CS 18 33 NC VCCQ Power for I/O’s (+3.3V)

BA 19 32 A9 VSSQ Ground for I/O’s

A10 20 31 A8

A0 21 30 A7 NC Not connected

A1 22 29 A6

A2 23 28 A5

A3 24 27 A4

VCC 25 26 VSS

Rev. 2.9 September 2001 2

Block Diagram

Write

Control MUX

Logic

Buffer

Input

DQMi

UDQM

Column Decoder

Column Decoder

LDQM I/O1-I/O16

Sense Amplifier

Sense Amplifier

Memory Array Memory Array

CLK

Bank 0 Bank 1

CKE

512k x 16 512k x 16

CS

Output

Buffer

Register

RAS

Timing

CAS

WE Row Row

Decoder Decoder

DQMi

Row Address Refresh

Buffer Counter

Column Address

Counter

A0-A10, BA

Programming

CLK

Burst Length

Latency 8

Register

Row Addresses

Column Address

Buffer

Address

A0-A7, BA

Column Addresses

Rev.2.9 September 2001 3

LCM L16A1616T

Signal Pin Description

Pin Name Input Function

CLK Clock Input System clock input. Active on the positive rising edge to sample all inptus

CKE Clock Enable Activates the CLK signal when high and deactivates the CLK when low.

CKE low initiates the power down mode, suspend mode, or the self

refresh mode

CS Chip Select Disables or enables device operation by masking or enabling all inputs

except CLK, CKE and DQMi

RAS Row Address Strobe Latches row addresses on the positive edge of CLK with RAS low.

Enables row access & precharge

CAS Column Address Strobe Latches column addresses on the positive edge of CLK with CAS low.

Enables column access

WE Write Enable Enables write operation

A0-A10 Address During a bank activate command, A0-A10 defines the row address.

During a read or write command, A0-A7 defines the column address. In

addition to the column address A10 is used to invoke auto precharge BA

define the bank to be precharged. A10 is low, auto precharge is disabled

during a precharge cycle, If A10 is high, both bank will be precharged ,

if A10 is low, the BA is used to decide which bank to precharge. If A10 is

high, all banks will be precharged.

BA Bank Select Selects which bank to activate. BA low select bank A and high selects

bank B

I/O1-I/O16 Data Input/Output Data inputs/output are multiplexed on the same pins

UDQM, LDQM Data Input/Output Mask Makes data output Hi-Z. Blocks data input when DQM is active

VDD/VSS Power Supply/Ground Power Supply. +3.3V ± 0.3V/ground

VDDQ/VSSQ Data Output Power/Ground Provides isolated power/ground to DQs for improved noise immunity

NC No Connection

Rev.2.9 September 2001 4

LCM L16A1616T

Package Diagram

50-Pin Plastic TSOP-II (400 mil)

0.039 ± 0.002 +0.003

[1 ± 0.05] 0.4 ± 0.005 0.006 –0.001

0.004±0.002 0.047 Max [10.16 ± 0.13] +0.08

0.15 –0.03

[0.1±0.05] [1.2 Max]

0.020±0.004

0.031 [0.8] 0.004 [0.1] [0.5 ± 0.1]

0.016 +0.002

–0.004 0.008 [0.2] M 44x 0.463±0.008

0.4 +0.05 [11.76 ± 0.2]

–0.1

50 26

1 25

1

0.825±0.005

[20.95±0.13] Unit in inches [mm]

1 Does not include plastic or metal protrusion of 0.010 [0.25] max. per side

Rev.2.9 September 2001 20

You might also like

- EtronTech EM638165TS 4M x 16 bit SDRAM Memory DeviceDocument51 pagesEtronTech EM638165TS 4M x 16 bit SDRAM Memory DeviceElnino HartonoNo ratings yet

- Em63a165ts v1Document51 pagesEm63a165ts v1api-432313169No ratings yet

- EOL Product: HM5216165 SeriesDocument52 pagesEOL Product: HM5216165 SeriesfurqanhamidNo ratings yet

- 1M X 16 Sdram: 512K X 16bit X 2 Banks Synchronous DRAM LVTTLDocument42 pages1M X 16 Sdram: 512K X 16bit X 2 Banks Synchronous DRAM LVTTLvetchboyNo ratings yet

- EM63B165TS - Rev 2.0Document53 pagesEM63B165TS - Rev 2.0silva_marcosrNo ratings yet

- Samsung 1mx16 k4s161622d-Tc70Document43 pagesSamsung 1mx16 k4s161622d-Tc70vetchboyNo ratings yet

- K6X4016C3F Family Cmos Sram: Document TitleDocument10 pagesK6X4016C3F Family Cmos Sram: Document TitledarezenaNo ratings yet

- 128Mb Synchronous DRAM Specification: A3V28S40JTPDocument40 pages128Mb Synchronous DRAM Specification: A3V28S40JTPCarlos Alonso Gonzalez VazquesNo ratings yet

- Description: CMOS 2-Bank 524,288-Word 16 Bit Synchronous Dynamic Random AccessDocument43 pagesDescription: CMOS 2-Bank 524,288-Word 16 Bit Synchronous Dynamic Random AccessvetchboyNo ratings yet

- EM48AM1684VTH EorexDocument17 pagesEM48AM1684VTH EorexErasmo FrancoNo ratings yet

- 64Mb Synchronous DRAM Specification: A3V64S40GTPDocument40 pages64Mb Synchronous DRAM Specification: A3V64S40GTPJeferson AndradeNo ratings yet

- A-Data ADS6616A4A 1M x 16 Bit x 4 Banks Synchronous DRAMDocument9 pagesA-Data ADS6616A4A 1M x 16 Bit x 4 Banks Synchronous DRAMJim LiebNo ratings yet

- DSA2AE0000535 Hermes LikeDocument12 pagesDSA2AE0000535 Hermes LikeFethileaksNo ratings yet

- Toshiba Confidential Tc58Nvg5D2Fta00: DescriptionDocument65 pagesToshiba Confidential Tc58Nvg5D2Fta00: DescriptionNoel Alejandro Cordova RangelNo ratings yet

- 4M (512K 8/256K 16) BIT: Flash MemoryDocument55 pages4M (512K 8/256K 16) BIT: Flash MemorytecrgoNo ratings yet

- CXP740096 Sony CorporationDocument31 pagesCXP740096 Sony CorporationGlenn Ian BislumbreNo ratings yet

- Description: 1G BIT (128M 8 Bit) Cmos Nand E PromDocument52 pagesDescription: 1G BIT (128M 8 Bit) Cmos Nand E PromLuis SantosNo ratings yet

- 8-Bit Flash Microcontroller AT89C51RD2 AT89C51ED2: FeaturesDocument137 pages8-Bit Flash Microcontroller AT89C51RD2 AT89C51ED2: FeaturesCarlos BaezNo ratings yet

- AN93Document307 pagesAN93AhmedNo ratings yet

- CMOS 8-Bit Single Chip Microcomputer: CXP83408/83412/83416 CXP83409/83413/83417Document24 pagesCMOS 8-Bit Single Chip Microcomputer: CXP83408/83412/83416 CXP83409/83413/83417HerwinTorresNo ratings yet

- 8-Bit Microcontroller With 16K/ 32K Bytes Flash AT89C51RB2 AT89C51RC2Document127 pages8-Bit Microcontroller With 16K/ 32K Bytes Flash AT89C51RB2 AT89C51RC2MNPRAWINNo ratings yet

- NM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesNM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- CXP82052 Sony CorporationDocument22 pagesCXP82052 Sony CorporationHoàng ĐiểnNo ratings yet

- Tc58dvm92a5ta00 ToshibaDocument38 pagesTc58dvm92a5ta00 ToshibaLorenzo TorresNo ratings yet

- Introduction and AVR ArchitectureDocument31 pagesIntroduction and AVR ArchitecturedaraNo ratings yet

- FM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)Document13 pagesFM93C66A 4K-Bit Serial CMOS EEPROM (MICROWIRE™ Synchronous Bus)insomnium86No ratings yet

- BK4802N - IC Radio PDFDocument19 pagesBK4802N - IC Radio PDFpatolin_123No ratings yet

- Calcutta 10-ct10 MP Ti 6050a2357502-A01-Er-Toshiba c600-pdf.6011Document56 pagesCalcutta 10-ct10 MP Ti 6050a2357502-A01-Er-Toshiba c600-pdf.6011oppo cloud007No ratings yet

- M5M51008CFP MitsubishiElectricSemiconductorDocument7 pagesM5M51008CFP MitsubishiElectricSemiconductorErasmo FrancoNo ratings yet

- Description: 1G BIT (128M 8 Bit) Cmos Nand E PromDocument52 pagesDescription: 1G BIT (128M 8 Bit) Cmos Nand E PromLademir FerreiraNo ratings yet

- Introduction and AVR ArchitectureDocument31 pagesIntroduction and AVR Architecturewilhelmus89No ratings yet

- Brown Goods TV Sets 29" 1xscart 5N11 Chassis: Service ManualDocument30 pagesBrown Goods TV Sets 29" 1xscart 5N11 Chassis: Service ManualgondifNo ratings yet

- TC58NVG2S3ETA00Document70 pagesTC58NVG2S3ETA00Freddy AmayaNo ratings yet

- 24AA16/24LC16B: 16K I C Serial EEPROMDocument25 pages24AA16/24LC16B: 16K I C Serial EEPROMDaniel VásquezNo ratings yet

- TC58NVG0S3ETA00Document65 pagesTC58NVG0S3ETA00Freddy AmayaNo ratings yet

- Ecm 0555 080 0703Document17 pagesEcm 0555 080 0703Anderson megusta el juegoNo ratings yet

- Document Title Revision History: 128Mb Synchronous DRAM Based On 2M X 4bank x16 I/ODocument13 pagesDocument Title Revision History: 128Mb Synchronous DRAM Based On 2M X 4bank x16 I/OregulateNo ratings yet

- 80C51 Core Architecture 256 Bytes of On-Chip RAM 2048 BytesDocument197 pages80C51 Core Architecture 256 Bytes of On-Chip RAM 2048 BytesBASEER AHMADNo ratings yet

- Toshiba Osaka NM-CS1 200400329 TC7778zba000 6050A0059801-MB-A01 SchematicDocument55 pagesToshiba Osaka NM-CS1 200400329 TC7778zba000 6050A0059801-MB-A01 Schematicdeppa lannaNo ratings yet

- Description: 2 GBIT (256M × 8 Bit) Cmos Nand E PromDocument65 pagesDescription: 2 GBIT (256M × 8 Bit) Cmos Nand E PromLuis SantosNo ratings yet

- TC58NVG1S3BFT00 - TC58NVG1S8BFT00Document37 pagesTC58NVG1S3BFT00 - TC58NVG1S8BFT00Freddy AmayaNo ratings yet

- Toshiba 2 Gbit CMOS NAND E2PROMDocument51 pagesToshiba 2 Gbit CMOS NAND E2PROMjan ZielinskiNo ratings yet

- Synclock V3Document17 pagesSynclock V3Americo HuertaNo ratings yet

- Absolut - MV2 Build 6050a2162301 A04-1Document61 pagesAbsolut - MV2 Build 6050a2162301 A04-1CiprianIfrimNo ratings yet

- 8-Bit Microcontroller With 2K/4K Bytes In-System Programmable Flash AT90S2333 AT90LS2333 AT90S4433 AT90LS4433 PreliminaryDocument103 pages8-Bit Microcontroller With 2K/4K Bytes In-System Programmable Flash AT90S2333 AT90LS2333 AT90S4433 AT90LS4433 Preliminaryapi-19831863No ratings yet

- Ts80C52X2: 8-Bit Cmos Microcontroller 0-60 MHZDocument54 pagesTs80C52X2: 8-Bit Cmos Microcontroller 0-60 MHZAgung RamdaniNo ratings yet

- 29lv160abtc 90 PDFDocument66 pages29lv160abtc 90 PDFjohnel ruszkiNo ratings yet

- 89c51cc02ca UmDocument159 pages89c51cc02ca UmpiotreNo ratings yet

- EM6AB160TSADocument61 pagesEM6AB160TSAKiều Hoàng AnhNo ratings yet

- Sdram 2M X 16 Bit X 4 Banks: M12L128168A (2L)Document45 pagesSdram 2M X 16 Bit X 4 Banks: M12L128168A (2L)geniunetNo ratings yet

- midas3.0_bmDocument139 pagesmidas3.0_bmMirosław WalasikNo ratings yet

- 8051 DatasheetDocument105 pages8051 Datasheetvarsha muthyalaNo ratings yet

- Datashet Etron TechDocument54 pagesDatashet Etron TechAndres OrjuelaNo ratings yet

- Arm7Tdmi - Based Microcontroller AT91RM3400: FeaturesDocument30 pagesArm7Tdmi - Based Microcontroller AT91RM3400: Featureshancu georgeNo ratings yet

- TC58NVG3S0FTA00Document73 pagesTC58NVG3S0FTA00varimasrNo ratings yet

- Controlador CAN MC33389Document49 pagesControlador CAN MC33389Jorge Martinez PerezNo ratings yet

- Toshiba 8GB NAND TC58NVG3S0FTAI0 PDFDocument73 pagesToshiba 8GB NAND TC58NVG3S0FTAI0 PDFMilan MilenovicNo ratings yet

- Hy5du561622ftp d43Document31 pagesHy5du561622ftp d43yhomerNo ratings yet

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Document16 pagesCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyNo ratings yet

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDocument10 pages2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalNo ratings yet

- Audio Tda8569q Spec enDocument20 pagesAudio Tda8569q Spec envetchboyNo ratings yet

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsDocument14 pagesDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyNo ratings yet

- Tda 7296Document14 pagesTda 7296Mayra GonzálezNo ratings yet

- Audio Tda8567q Spec enDocument20 pagesAudio Tda8567q Spec envetchboyNo ratings yet

- Audio Tda8567q Spec enDocument20 pagesAudio Tda8567q Spec envetchboyNo ratings yet

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionDocument10 pages4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNo ratings yet

- Audio Tda8510j Spec enDocument16 pagesAudio Tda8510j Spec envetchboyNo ratings yet

- 4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionDocument12 pages4 X 30W Quad Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNo ratings yet

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDocument9 pagesTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaNo ratings yet

- Tda 7313Document15 pagesTda 7313jordachadiNo ratings yet

- TDA 2822M CircuitoDocument11 pagesTDA 2822M CircuitoDATA24No ratings yet

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDocument13 pages120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyNo ratings yet

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionDocument14 pagesDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyNo ratings yet

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDocument18 pagesTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyNo ratings yet

- Tda7294 PDFDocument16 pagesTda7294 PDFRoger NunesNo ratings yet

- Tda 7269aDocument7 pagesTda 7269aAlexa DanNo ratings yet

- TDA1554Q 44W Audio AmplifierDocument11 pagesTDA1554Q 44W Audio Amplifiersava7698No ratings yet

- 30W Bridge Car Radio Amplifier: DescriptionDocument10 pages30W Bridge Car Radio Amplifier: DescriptionvetchboyNo ratings yet

- Tda 2004Document11 pagesTda 2004Diana Belen Rodriguez HernandezNo ratings yet

- Tda 7265 2 x25 WDocument12 pagesTda 7265 2 x25 WJavier CanaviriNo ratings yet

- Amplificador 20W RMS TDA2003 Con Placa PCBDocument15 pagesAmplificador 20W RMS TDA2003 Con Placa PCBEnya Andrea Ribba Hernandez100% (5)

- Audio Tas5100a Spec enDocument15 pagesAudio Tas5100a Spec envetchboyNo ratings yet

- 10W Car Radio Audio Amplifier: DescriptionDocument11 pages10W Car Radio Audio Amplifier: DescriptionvetchboyNo ratings yet

- Low Power Quad Operational Amplifiers: LM124 LM224 - LM324Document13 pagesLow Power Quad Operational Amplifiers: LM124 LM224 - LM324vetchboyNo ratings yet

- Audio Tda2002 Spec enDocument2 pagesAudio Tda2002 Spec envetchboyNo ratings yet

- Description: Angus Electronics Company LimitedDocument9 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- STK442-110 70W Audio Power Amplifier SpecificationsDocument4 pagesSTK442-110 70W Audio Power Amplifier SpecificationsIvan AsimovNo ratings yet

- Description: Angus Electronics Company LimitedDocument13 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- NS Industrial Electronics N3 4-15 May 2020Document4 pagesNS Industrial Electronics N3 4-15 May 2020Carol Cido ShaiNo ratings yet

- Manual For 3050C: Zhengzhou Audley Digital Control Equipments Co., LTDDocument28 pagesManual For 3050C: Zhengzhou Audley Digital Control Equipments Co., LTDnagm nagmNo ratings yet

- AlisonDocument2 pagesAlisonMaiChiVuNo ratings yet

- OBIA 11 1 1 8 1 Upgrade GuideDocument106 pagesOBIA 11 1 1 8 1 Upgrade GuideRajendarNo ratings yet

- OSN9800 M05 Power Supply ManagementDocument11 pagesOSN9800 M05 Power Supply ManagementAlexander PischulinNo ratings yet

- Adafruit Agc Electret Microphone Amplifier Max9814Document11 pagesAdafruit Agc Electret Microphone Amplifier Max9814Atyla ManciniNo ratings yet

- Lecture 2 - Introduction To Flutter and DartDocument38 pagesLecture 2 - Introduction To Flutter and DartMuhammad Umer Farooq100% (1)

- Home Automation System Using ArduinoDocument55 pagesHome Automation System Using ArduinoNguyễn Anh Tuấn94% (17)

- Flash Samsung Galaxy S Plus Using OdinDocument13 pagesFlash Samsung Galaxy S Plus Using Odinender40No ratings yet

- Arash 3 1 Years of Experions in TestingDocument3 pagesArash 3 1 Years of Experions in TestingVishnu Vardhan PadidalaNo ratings yet

- Service Manual FE-2: KV-29LS40B KV-29LS40E KV-29LS40KDocument49 pagesService Manual FE-2: KV-29LS40B KV-29LS40E KV-29LS40KGabi StrejtNo ratings yet

- User Manual: Product Type: Switching Power Supply Model Name: HG2, HP2, PSM, PSLDocument17 pagesUser Manual: Product Type: Switching Power Supply Model Name: HG2, HP2, PSM, PSLotrupon melliNo ratings yet

- C-LANGUAGE Guide: Constants, Data Types, Operators & MoreDocument37 pagesC-LANGUAGE Guide: Constants, Data Types, Operators & MorePrashanthNo ratings yet

- Control HB70 Data Sheet EngDocument8 pagesControl HB70 Data Sheet Engeliasmontes1986No ratings yet

- Nevion Product Catalog - 2013Document116 pagesNevion Product Catalog - 2013Marcellin OMORESNo ratings yet

- Control & InstrumentationDocument3 pagesControl & InstrumentationmkoelrealNo ratings yet

- Technical Note ASEM System Manager TN0012Document16 pagesTechnical Note ASEM System Manager TN0012iGNAZIO WebtronicaNo ratings yet

- FortiOS 7.2.1 Administration GuideDocument2,827 pagesFortiOS 7.2.1 Administration GuideAristides LimaNo ratings yet

- Operating System LabDocument33 pagesOperating System LabCasey MoralesNo ratings yet

- Circuitbreaker Testsystems Operatingmanual: Enviado Por: Qualitrol Support Portal, 09/21Document176 pagesCircuitbreaker Testsystems Operatingmanual: Enviado Por: Qualitrol Support Portal, 09/21Josefina ReyesNo ratings yet

- Oppo 6750 EMMC Storage LayoutDocument11 pagesOppo 6750 EMMC Storage Layoutfaisal anas0% (4)

- Instruction Set of 8086Document47 pagesInstruction Set of 8086Mohammed Dyhia AliNo ratings yet

- Crypto TLSDocument11 pagesCrypto TLSAuliya RusyidaNo ratings yet

- NeelaDocument3 pagesNeelaabbas7778No ratings yet

- Acm Ark SurvivalDocument3 pagesAcm Ark SurvivaljosemariplNo ratings yet

- 15 Tips and Tricks Jupyter NotebookDocument12 pages15 Tips and Tricks Jupyter NotebookEvelyn OrtizNo ratings yet

- Hantek Tekway DSO v1.03Document15 pagesHantek Tekway DSO v1.03dirk13No ratings yet

- Application Control Environment Rapid Restart Upgrade Tool User's Guide EPDOC-X404-en-501ADocument32 pagesApplication Control Environment Rapid Restart Upgrade Tool User's Guide EPDOC-X404-en-501ASebastian AlarconNo ratings yet

- Introduction To Computer Network: by Ajay Singh Meena Class: Xii-E Roll No.: 04Document30 pagesIntroduction To Computer Network: by Ajay Singh Meena Class: Xii-E Roll No.: 04Ajay Singh MeenaNo ratings yet

- Zetron Acom EVO Console Datasheet - 005-1402A - March 2011 PDFDocument4 pagesZetron Acom EVO Console Datasheet - 005-1402A - March 2011 PDFwipi12No ratings yet