Professional Documents

Culture Documents

Análisis de respuesta en frecuencia de circuito JFET

Uploaded by

Jhonny Sotelo CanelasOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Análisis de respuesta en frecuencia de circuito JFET

Uploaded by

Jhonny Sotelo CanelasCopyright:

Available Formats

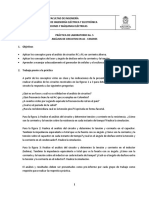

UMSS - FCyT INGS. ELCTRICA - ELECTRNICA ELECTRNICA ANALGICA II 2014007 LABORATORIO No 1 SEMESTRE 2/12 Docente: Ing.

. Arturo Saramani Aguilar Email: asa.lla@gmail.com OBJETIVOS O1. Determinar la respuesta en frecuencias de un transistor JFET. O2. Manejar el Pspice como herramienta de anlisis y simulacin de circuitos electrnicos. PRCTICA - Circuitos de estudio:

Figura 1

Figura 2

Figura 3

- Datos de Laboratorio: Vi, Ri, Vdd. PREINFORME P1. Utilizando las curvas caractersticas de entrada y de salida del Jfet 2N3819 o su equivalente, hallar por simulacin (utilizando el Pspice) los puntos de trabajo. Tomar como referencia el circuito de la Figura 1. P2. Obtenidas las curvas y los puntos de trabajo de P1, tanto para la caracterstica de entrada como para la de salida, polarizar el Jfet en DC segn la Figura 2, y AC para mxima excursin de seal, segn la Figura 3. P3. Con referencia al circuito de la Figura 3, realizar el anlisis terico y el diseo para una respuesta con una ganancia Av=10+2(x+y)/5 [dB] y Bw=10(57-x-3y) [KHz] , donde x corresponde al prefijo da (01 lunes 815-945, 02 lunes 1115-1245 , 03 mircoles 945-1115), en tanto que y al nmero de grupo. Av debe hallarse con una tolerancia de 1dB y Bw con 30 KHz. P4. Considerar los componentes ms usuales con valores comerciales que tengan una tolerancia de 5%. Con los datos calculados, comprobar el funcionamiento va simulacin y redisear si fuera el caso para un comportamiento deseado. LABORATORIO L1. Montar el circuito de la figura 3 previamente simulado en el preinforme, con los valores comerciales de resistores y capacitores obtenidos. L2. Realizar una tabla que muestre los resultados tericos, resultados de simulacin y resultados prcticos, tanto para las tensiones y corrientes DC, como para los valores de componentes presentes en el circuito. L3. Cambiar Cx de manera que se pueda obtener una variacin del punto de corte en altas en 10% de su valor fijado. Anotar los resultados obtenidos. INFORME I1. Describir sintticamente los aspectos tericos de la respuesta en frecuencia de un circuito transistorizado con JFet.. I2. Explicar los criterios y clculos de polarizacin, tericos y prcticos, empleados para desarrollar P2. Mostrar las rectas de carga en DC y AC respectivos. I3. Mostrar el diseo y clculos realizados para hallar la ganancia y las frecuencias de corte en bajas y altas correspondiente a P3. I4. Mostrar los resultados obtenidos, tanto tericos, en simulacin, como prcticos, debido a la variacin de Cx, segn L3. I5. Mostrar la tabla de resultados tericos, de simulacin y prcticos, con los valores obtenidos del circuito de la Fig. 3 I6. Realizar el anlisis de errores (basado en el mtodo de Montecarlo del Pspice) y explicar las divergencias existentes en la tabla construida en I5. I7. Detallar las conclusiones a que arribaron al trmino de la prctica. BIBLIOGRAFA Schilling Belove: Circuitos Electrnicos. Discretos e Integrados

Rashid Muhammad H.: Circuitos Microelectrnicos. Anlisis y diseo

You might also like

- Metodología básica de instrumentación industrial y electrónicaFrom EverandMetodología básica de instrumentación industrial y electrónicaRating: 4 out of 5 stars4/5 (12)

- Pre-1 Analogica 2Document2 pagesPre-1 Analogica 2Onofre DanielNo ratings yet

- Lab1 2014007Document2 pagesLab1 2014007harlen ledezma vargasNo ratings yet

- Experiencias sobre circuitos eléctricos en serie operados por corriente directaFrom EverandExperiencias sobre circuitos eléctricos en serie operados por corriente directaNo ratings yet

- lb01Document1 pagelb01FavioRivadeneiraNo ratings yet

- Lab3 2014007Document1 pageLab3 2014007Jhonny Sotelo CanelasNo ratings yet

- Guia 06 PDFDocument6 pagesGuia 06 PDFJei VegaNo ratings yet

- 5 - Labep2018 Ii 1 1Document11 pages5 - Labep2018 Ii 1 1NickNo ratings yet

- Amplificador Clase DDocument4 pagesAmplificador Clase DDiego tapiaNo ratings yet

- Informe 2 l2Document9 pagesInforme 2 l2sergiocuellar7No ratings yet

- Guia LaboratorioDocument2 pagesGuia Laboratoriok-eza Araya FloresNo ratings yet

- PRAC 01 Circuitos de Polarización Con BJTDocument5 pagesPRAC 01 Circuitos de Polarización Con BJTCristhianRodriguezNo ratings yet

- l03Document1 pagel03Marcos GomezNo ratings yet

- Relación de Ejercicios de Seminario de Simulación de Circuitos Electrónicos de Potencia Con OrCAD PSpiceDocument33 pagesRelación de Ejercicios de Seminario de Simulación de Circuitos Electrónicos de Potencia Con OrCAD PSpicejaguilarpenaNo ratings yet

- 3 Practica Ing ControlDocument5 pages3 Practica Ing ControlArmando LópezNo ratings yet

- Guia 1 de Circuitos Electronicos II 2021Document4 pagesGuia 1 de Circuitos Electronicos II 2021CanalDTodoUnPoco PCNo ratings yet

- Amplificador Operacional: Descripción, Circuitos y AnálisisDocument6 pagesAmplificador Operacional: Descripción, Circuitos y AnálisisSantiago OrdoñezNo ratings yet

- UMSS FCYT Lab 4 BJT JFET Curves AmplificationDocument1 pageUMSS FCYT Lab 4 BJT JFET Curves AmplificationArandia Luna Luis ArturoNo ratings yet

- Practica 3 Laboratorio de Electronica IDocument9 pagesPractica 3 Laboratorio de Electronica IErick AvilaNo ratings yet

- 01 Recortadores y SujetadoresDocument5 pages01 Recortadores y SujetadoresChristian AvilaNo ratings yet

- Dispositivos Lab2 PEREZDocument8 pagesDispositivos Lab2 PEREZJoséPérezCamposNo ratings yet

- Respuesta en frecuencia circuitos 1er 2do ordenDocument3 pagesRespuesta en frecuencia circuitos 1er 2do ordenAndrésVásconezNo ratings yet

- Practica 1Document22 pagesPractica 1Jonathan Mauricio Paucay GarayNo ratings yet

- Informe Práctica 5 - Amplificador SumadorDocument8 pagesInforme Práctica 5 - Amplificador SumadorByronJorqueNo ratings yet

- Practica 3 PDFDocument6 pagesPractica 3 PDFjunmechNo ratings yet

- 02 RectificadoresDocument6 pages02 Rectificadoresduiliogabo1 variedadNo ratings yet

- Final IDocument8 pagesFinal IMathias Chero MendozaNo ratings yet

- TP3 EaiiDocument2 pagesTP3 EaiiJose Ignacio Gonzalez BeltramoNo ratings yet

- ELECTRONICA II Practica 4 Intergrador y DerivadorDocument6 pagesELECTRONICA II Practica 4 Intergrador y DerivadorMian Chauca ApazaNo ratings yet

- 02 Rectificadores y FiltrosDocument8 pages02 Rectificadores y FiltrosChristian AvilaNo ratings yet

- Guia 2 de Circuitos Electronicos II 2018Document5 pagesGuia 2 de Circuitos Electronicos II 2018Anonymous IF6VmhNo ratings yet

- Informe Laboratorio 2 AnalogaDocument12 pagesInforme Laboratorio 2 AnalogaFabián Andrés Salgado MejíaNo ratings yet

- Guia de Practicas - N°8-Retroalimentacion PositivaDocument5 pagesGuia de Practicas - N°8-Retroalimentacion PositivaJordy Tmpr HtcNo ratings yet

- CP Dispo9Document4 pagesCP Dispo9Anonymous tJgIbVzpNo ratings yet

- 3 OpamDocument9 pages3 OpamKatherine María Zambrano CasasNo ratings yet

- AO integrador y derivadorDocument10 pagesAO integrador y derivadorLalo SanchezNo ratings yet

- Guia de Practicas - N°8-Retroalimentacion PositivaDocument5 pagesGuia de Practicas - N°8-Retroalimentacion PositivaWilson Steeven Trávez CruzNo ratings yet

- Lab1 ORCAD MODIFICADO1Document15 pagesLab1 ORCAD MODIFICADO1Jonathan PolaniaNo ratings yet

- Informe Lab4 3817 Barreno Herrera Montenegro PDFDocument28 pagesInforme Lab4 3817 Barreno Herrera Montenegro PDFMikael MontenegroNo ratings yet

- Hoja Guía Electrónica Básica-8Document9 pagesHoja Guía Electrónica Básica-8Manuel TuzaNo ratings yet

- Informe 1 - Electronica de PotenciaDocument10 pagesInforme 1 - Electronica de PotenciaMauricio Cala AriasNo ratings yet

- P9 FundamentosDocument3 pagesP9 Fundamentosjaime serranoNo ratings yet

- Practica 1 PDFDocument7 pagesPractica 1 PDFsamir ernesto duran ortegaNo ratings yet

- Lab 07Document5 pagesLab 07Juan CuervoNo ratings yet

- Laboratorio 1 Instrumentación Ao Comparador 1S.2021Document12 pagesLaboratorio 1 Instrumentación Ao Comparador 1S.2021Diego PinzonNo ratings yet

- SIS 421 Electrónica II-16 PDFDocument21 pagesSIS 421 Electrónica II-16 PDFmarcos_socratesNo ratings yet

- Practica 3Document1 pagePractica 3Luis Del Rosario100% (1)

- Práctica 06 Lab Electrónica II 19-19Document6 pagesPráctica 06 Lab Electrónica II 19-19Miguel AngelNo ratings yet

- Guia4 AEL115 2022Document11 pagesGuia4 AEL115 2022Samuel Elias Osorto RiveraNo ratings yet

- Comparativa de parámetros reales vs ideales de OpAmps LM324 y TL084Document3 pagesComparativa de parámetros reales vs ideales de OpAmps LM324 y TL084Breyner StevensNo ratings yet

- Laboratorio Analisis Circuitos ACDocument5 pagesLaboratorio Analisis Circuitos ACDaniel Santiago Polanía RodriguezNo ratings yet

- Práctica 05 Electrónica I 21ADocument7 pagesPráctica 05 Electrónica I 21AJoffre EstradaNo ratings yet

- Amplificador cascada configuraciónDocument11 pagesAmplificador cascada configuraciónDiego Chinguel JimenezNo ratings yet

- Tarea 2 ELO102 Matias SandovalDocument6 pagesTarea 2 ELO102 Matias SandovalmatiasNo ratings yet

- Practica 1 PDFDocument4 pagesPractica 1 PDFJose Andres Sanchez RobayoNo ratings yet

- Practica FasorDocument3 pagesPractica FasorNicolas Steven Garay GutierrezNo ratings yet

- Practica Circuito Rectificador Media Onda, Completa y Tap CentralDocument4 pagesPractica Circuito Rectificador Media Onda, Completa y Tap CentralAlexis XavierNo ratings yet

- Guía de Laboratorio 2Document5 pagesGuía de Laboratorio 2jonescaiNo ratings yet

- Guias de Practicas de Laboratorios de Electronica DigitalDocument29 pagesGuias de Practicas de Laboratorios de Electronica DigitalAlex Dhax Huamani RamosNo ratings yet

- Rafo 01Document1 pageRafo 01Jhonny Sotelo CanelasNo ratings yet

- Trabajo 4Document1 pageTrabajo 4Jhonny Sotelo CanelasNo ratings yet

- UNIDAD I Bases Teóricas Del Modelo Por Competencias RDocument25 pagesUNIDAD I Bases Teóricas Del Modelo Por Competencias RJhonny Sotelo CanelasNo ratings yet

- Mapa Solar CbbaDocument10 pagesMapa Solar CbbaJhonny Sotelo CanelasNo ratings yet

- El CurrículoDocument40 pagesEl CurrículoJhonny Sotelo CanelasNo ratings yet

- Teorema de Green en El PlanoDocument10 pagesTeorema de Green en El PlanoJhonny Sotelo CanelasNo ratings yet

- Actitudes y MotivaciónDocument5 pagesActitudes y MotivaciónJhonny Sotelo CanelasNo ratings yet

- Planta Baja Cableado TomasDocument1 pagePlanta Baja Cableado TomasJhonny Sotelo CanelasNo ratings yet

- Cauchy GoursatDocument8 pagesCauchy GoursatJhonny Sotelo CanelasNo ratings yet

- Informe Lab01Document10 pagesInforme Lab01Jhonny Sotelo CanelasNo ratings yet

- Lab2 2014007Document1 pageLab2 2014007Jhonny Sotelo CanelasNo ratings yet

- EL00100CDocument7 pagesEL00100CJhonny Sotelo CanelasNo ratings yet

- Guia OrCAD 9 1Document62 pagesGuia OrCAD 9 1teo37No ratings yet

- Problemas Resueltos de LimitesDocument52 pagesProblemas Resueltos de Limitesarcangel90000No ratings yet

- Filtros activos circuitos acoplados formulas diseñoDocument4 pagesFiltros activos circuitos acoplados formulas diseñoJhonny Sotelo CanelasNo ratings yet

- Problemas de Electrónica AnalógicaDocument92 pagesProblemas de Electrónica AnalógicaJulio Cesar Rodriguez Velez100% (1)

- 1.mecanica Basica para Maquinaria Pesada Julio 2018Document42 pages1.mecanica Basica para Maquinaria Pesada Julio 2018Fabián AlbertoNo ratings yet

- Informe de Física IDocument4 pagesInforme de Física INATALIA CHIRINOS ARÉVALONo ratings yet

- 2022 - Percival Scientific - Model DR 41VL - Drosophila Chamber - En.esDocument2 pages2022 - Percival Scientific - Model DR 41VL - Drosophila Chamber - En.esLenin SanchezNo ratings yet

- CUESTIONES ENLACE QUÍMICO 4 EsoDocument2 pagesCUESTIONES ENLACE QUÍMICO 4 EsoCristy100% (2)

- Transformador de DistribuciónDocument2 pagesTransformador de DistribuciónFredy ricaurteNo ratings yet

- Vega Star 22 VS - 197ee0300 - R.1 06-2016 - SpaDocument30 pagesVega Star 22 VS - 197ee0300 - R.1 06-2016 - SpadiedantonNo ratings yet

- Silabo SistemasDeControlClasicoDocument7 pagesSilabo SistemasDeControlClasicoCarolina CaceresNo ratings yet

- Prueba Corta 2Document26 pagesPrueba Corta 2Estefania Rojas RayoNo ratings yet

- DIAPOSITIVAS - Trabajo, Energía y PotenciaDocument14 pagesDIAPOSITIVAS - Trabajo, Energía y PotenciaFiorella Valentina Giraldo MontesNo ratings yet

- Monografia ElectricidadDocument5 pagesMonografia ElectricidadFrank CondoriNo ratings yet

- Press BoardDocument1 pagePress BoardWinstonNo ratings yet

- Procesos de Acabados SuperficialesDocument49 pagesProcesos de Acabados SuperficialesRodrigo Chávez100% (7)

- BA ICP IPP IPS Espagnol D09841Document48 pagesBA ICP IPP IPS Espagnol D09841GuzmanNo ratings yet

- Teorema Fundamental Del Cálculo Integral y Teorema Del Valor Medio para Integrales.Document8 pagesTeorema Fundamental Del Cálculo Integral y Teorema Del Valor Medio para Integrales.Ariel Horta LoeraNo ratings yet

- Carga y descarga condensador circuito RCDocument5 pagesCarga y descarga condensador circuito RCMario Martin CerezoNo ratings yet

- 1 LCB 355024Document90 pages1 LCB 355024liliana martin meloNo ratings yet

- Instrumentos de Medición Automotriz Usado en El Mercado NacionalDocument1 pageInstrumentos de Medición Automotriz Usado en El Mercado NacionalJeanpool Javier Arratea Medina50% (2)

- Cerro VerdeDocument57 pagesCerro VerdeNivardo Vila muchaNo ratings yet

- 01-Las 5 Fallas Más Típicas en Aire Acondicionado Split y Cómo Resolverlas - Primera ParteDocument3 pages01-Las 5 Fallas Más Típicas en Aire Acondicionado Split y Cómo Resolverlas - Primera ParteDaniel NavarroNo ratings yet

- Clásicos Del Mazmorreo - Intriga en La Corte Del CaosDocument42 pagesClásicos Del Mazmorreo - Intriga en La Corte Del CaosWorld SmithersNo ratings yet

- El Punto Del Diablo y La Canción de La Duna..... El CerDocument8 pagesEl Punto Del Diablo y La Canción de La Duna..... El CerAtacama59No ratings yet

- Ecuación de Bernoulli y flujo de fluidosDocument13 pagesEcuación de Bernoulli y flujo de fluidosOMXR TAREASNo ratings yet

- TP 1 Amplificadores de PotenciaDocument2 pagesTP 1 Amplificadores de PotenciaRegencia TécnicaNo ratings yet

- Informe de La Boratorio 6Document2 pagesInforme de La Boratorio 6paola veraNo ratings yet

- Proyecto Final Fenomenos de TransporteDocument14 pagesProyecto Final Fenomenos de TransportevictorNo ratings yet

- 8vo Básico Clase 21 de AgostoDocument21 pages8vo Básico Clase 21 de Agosto5211241No ratings yet

- Norma Coguanor NTG 41006 Astm c125 PDFDocument15 pagesNorma Coguanor NTG 41006 Astm c125 PDFHugo TurckheimNo ratings yet

- Ficha Tecnica - Manguera Antiestatica KuritecDocument2 pagesFicha Tecnica - Manguera Antiestatica KuritecCARLOS100% (1)

- Modulo #10 HidrostáticaDocument4 pagesModulo #10 HidrostáticaSilvioChávezNo ratings yet