Professional Documents

Culture Documents

07a80305 Computerorganizationandarchitecture

Uploaded by

Sharanya ThirichinapalliOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

07a80305 Computerorganizationandarchitecture

Uploaded by

Sharanya ThirichinapalliCopyright:

Available Formats

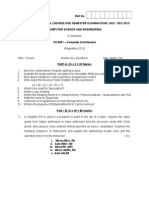

Code No: 07A80305

R07

Set No. 2

IV B.Tech II Semester Examinations,APRIL 2011 COMPUTER ORGANIZATION AND ARCHITECTURE Common to Mechanical Engineering, Automobile Engineering Time: 3 hours Max Marks: 80 Answer any FIVE Questions All Questions carry equal marks

1. Show the value of all bits of a 12-bit register that hold the number equivalent to decimal 215 in:

(a) Binary

(b) Binary-coded octal (c) Binary - coded hexadecimal. [16]

2. (a) Consider a single-transistor dynamic memory cell. Assume that C = 50 fentofarads and the leakage current through the transistor is about 9 pico amperes. The voltage across the capacitor when it is fully charged is equal to 4.5V. The cell must be refreshed before this voltage drops below 3V. Estimate the minimum refresh rate. (b) Discuss in detail about various features of ROM, PROM and EPROM.[6+10]

3. (a) Dene the term Parallel Processing and explain the need of it with an example. (b) Discuss in detail about the four major groups according to the Flynns classication with respect to Parallel Processing. [8+8] 4. (a) What is Symbolic micro program, explain? (b) Taking an example design a control unit. [8+8]

5. (a) Discuss in detail about the various processes involved in Multiport memory with a neat block diagram consisting of inter connections for four CPUs and four memory modules. (b) The 88 omega switching network has three stages with four switches in each stage, for a total of 12 switches. How many stages amd switches per stage are needed in an n nomega switching network? [10+6] 6. (a) Explain in detail about the operation of a universal asynchronous receiver transmitter with a neat diagram. (b) Draw the timing diagram and expalin about asynchronous serial transmission. [11+5] 7. The content of PC in the basic computer is 3AF (all numbers are in hexadecimal). The content of AC is 7EC3. The content of memory at address 3AF is 932E. The content of memory at address 32E is 09AC. The content of memory at address 9AC is 8B9F. 1

Code No: 07A80305

R07

Set No. 2

(a) What is the instruction that will be fetched and executed next? (b) Show the binary operation that will be performed in the AC when the instruction is executed. (c) Give the contents of registers PC, AR, DR, AC and IR in hexadecimal and the values of E, I and the sequence counter SC in binary at the end of the instruction cycle. [16] 8. Given the 16 bit value 1001101011001101. What operation must be performed in order to? (a) Clear to 0 the rst eight bits (b) Set to 1 the last eight bits (c) Complement the middle eight bits. [16]

Code No: 07A80305

R07

Set No. 4

IV B.Tech II Semester Examinations,APRIL 2011 COMPUTER ORGANIZATION AND ARCHITECTURE Common to Mechanical Engineering, Automobile Engineering Time: 3 hours Max Marks: 80 Answer any FIVE Questions All Questions carry equal marks

1. Dierentiate the RISC and CISC processor characteristics.

[16]

2. (a) What is the function of a Multiprocessor system and list out the various characteristics of Multiprocessors?

(b) Explain how the Multiprocessors are classied based on way their memory organization. [10+6]

3. (a) Explain asynchronous data transfer modes.

(b) Identify the standard binary code for the alphanumeric characters and explain about them with examples. [9+7]

4. With respect to the performance considerations, discuss about the following: (a) Write buer (b) Prefetching

(c) Lock up-Free cache.

[5+6+5]

5. (a) Draw and explain a space-time diagram for a six-segment pipeline showing the time it takes to process eight tasks. (b) With an example, demonstrate the pipeline organization. 6. (a) Explain the stages of pipelining in detail. (b) What is micro program sequencer in micro programmed control organization? [8+8] 7. A basic computer is starting to perform instruction ADD 100 I. Given preconditions are (values are hex decimals): PC = 190 AC = 3 M[100] = 200 M[200] = fe (a) Describe what happens during the instruction cycle. Include all phases from fetch to execute. (b) If an I/O device requests for an interrupt during the instruction cycle, what happens? Describe the events starting from the fetch phase of the current instruction until the machine is ready to branch to the interrupt subroutine of the I/O device. [16] 3 [8+8]

Code No: 07A80305

R07

Set No. 4

8. Derive the circuits for a 3-bit parity generator and 4bit parity checker using an even parity bit. [16]

Code No: 07A80305

R07

Set No. 1

IV B.Tech II Semester Examinations,APRIL 2011 COMPUTER ORGANIZATION AND ARCHITECTURE Common to Mechanical Engineering, Automobile Engineering Time: 3 hours Max Marks: 80 Answer any FIVE Questions All Questions carry equal marks

1. (a) Parallel Processing can be viewed from various levels of complexity. Explain the statement with necessary reasons.

(b) List out and explain various advantages of a parallel processing system.[6+10]

2. (a) With a neat diagram, discuss in detail about the possible address assignment for a byte-addressable 32-bit computer. (b) Draw the block diagram showing various connections of the main memory to the CPU. Also, explain about issues related to their bus structures. [7+9] 3. (a) How many characters per second can be transmitted over a 1200-baud line in each of the following modes? (Assume a character code of eight bits): i. Synchronous serial transmission ii. Asynchronous serial transmission with two stop bits iii. Asynchronous serial transmission with one stop bit.

(b) List out the salient features of First-In, First-Out Buer. [6+10]

4. Show the bit conguration of a 24-bit register when its content represents the decimal equivalent of 400:

(a) in binary

(b) in BCD (c) in ASCII using eight bits with even parity. [16]

5. (a) What is the dierence between microprocessor and micro program?Is it possible to design a microprocessor without a micro program? Are all micro programmed computers also microprocessor? (b) Explain the dierence between hardwired control and micro programmed control. Is it possible to have a hardwired control associated with a control memory? [8+8] 6. (a) What are the dierent addressing modes, explain in detail with example? (b) What are Berkeley RISC I instruction formats, explain? [8+8]

7. The following control inputs are active in the bus system, For each case, specify the register transfer that will be executed during the next clock transition. [16]

Code No: 07A80305

R07

Set No. 1

a) b) c) d)

S2 S1 S0 value S LD(x) Memory Adder 1 1 1 =7 IR READ 1 1 0 =6 PC 1 0 0 =4 DR WRITE 0 0 0 =0 AC ADD

8. (a) Draw a diagram showing the structure of a four-dimentional hypercube network. List all the paths available from node 7 to node 9 that use the minimum number of intermediate nodes. (b) Compare parallel and serial arbitration procedure? [10+6]

Code No: 07A80305

R07

Set No. 3

IV B.Tech II Semester Examinations,APRIL 2011 COMPUTER ORGANIZATION AND ARCHITECTURE Common to Mechanical Engineering, Automobile Engineering Time: 3 hours Max Marks: 80 Answer any FIVE Questions All Questions carry equal marks

operation ii) Micro instructions iii) Micro program iv) Micro code. 1. (a) (a)Define: Given i) a Micro 9bit micro operation eld for the following micro operation: (b) Explain how the mapping from an instruction code to microinstruction address can be i. AC < - AC + 1, DR < - DR+1 done by means of a read-only memory. [8+8] ii. PC < - PC +1, DR < - M[AR]. iii. Dierence between hardwire control and micro programmed control.[8+8]

2. (a) What are the functions of an array processor? (b) Dierentiate between Attached and SIMD Array Processors with respect to any six parameters. (c) Compare Vector and Array Processings. [4+6+6]

3. Design a 4bit combinational circuit decrementer using four full adder circuits. [16] 4. (a) Explain in detail about the impact of the cache on the overall performance of the computer with respect to hit rate and hiss rate. (b) List out the salient features of memory inter learning. [12+4]

5. (a) What are dierent types of memories, which is the fastest and slowest of all, which is cheapest and which is costly, memory. (b) Is a WLAN connectivity an IO system, if yes which part of memory is associated to this interface. [8+8] 6. Show the bit conguration of a 24-bit register when its content represents the decimal equivalent of 295: (a) in binary (b) in BCD (c) in ASCII using eight bits with even parity. [16]

7. (a) Give at least six status conditions for the setting of individual bits in the status register of an asynchronous communication interface. (b) How many bits are there in the transmitter shift register of a UART when the interface is attached to a terminal that needs one stop bit? List the bits in the shift register when the letter W is transmitted using ASCII with even parity. [6+12] 8. (a) Bringout the dierences between the cross bar switch and multistage switching networks. 7

Code No: 07A80305

R07

Set No. 3

(b) Construct a diagram for a 4 4 omega switching network. Show the switch setting required to connect input 3 to output 1. [8+8]

You might also like

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Computer Architecture and OrganizationDocument6 pagesComputer Architecture and OrganizationRahmantic SwatzNo ratings yet

- Supplier & Supplier Sites Interface&ConversionDocument19 pagesSupplier & Supplier Sites Interface&ConversionSuneelTejNo ratings yet

- Java Web Services Using Apache Axis2Document24 pagesJava Web Services Using Apache Axis2kdorairajsgNo ratings yet

- Industrial Safety Question PaperDocument7 pagesIndustrial Safety Question Paperbhaskar5377100% (2)

- Environment Lighting 3DSMaxDocument84 pagesEnvironment Lighting 3DSMaxsaletebasto100% (9)

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCFrom EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNo ratings yet

- R07 Set No. 2Document7 pagesR07 Set No. 2Mothilal KaramtothuNo ratings yet

- bt31R07 P1 10 11 2009rahulDocument31 pagesbt31R07 P1 10 11 2009rahulashok1261No ratings yet

- 07a80402 EmbeddedandrealtimesystemsDocument6 pages07a80402 EmbeddedandrealtimesystemsSharanya ThirichinapalliNo ratings yet

- Co Unitwise Questions NewDocument13 pagesCo Unitwise Questions NewSai VenkateshNo ratings yet

- 2019-20 Supple CoaDocument2 pages2019-20 Supple Coanaveenk1999nk99No ratings yet

- Computer Organization Jun 2010Document2 pagesComputer Organization Jun 2010Prasad C MNo ratings yet

- Vlsi QP 1Document6 pagesVlsi QP 1Sailesh PosaniNo ratings yet

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071No ratings yet

- VI Sem, Jan, Feb 2005Document4 pagesVI Sem, Jan, Feb 2005Veeresh NicolyteNo ratings yet

- NR Set No. 2Document4 pagesNR Set No. 2adddataNo ratings yet

- TE 2003&2008 PatternDocument623 pagesTE 2003&2008 PatternAshashwatmeNo ratings yet

- Rr310501 Interfacing Through MicroprocessorsDocument8 pagesRr310501 Interfacing Through MicroprocessorsSRINIVASA RAO GANTANo ratings yet

- Rr322203 Microprocessors MicrocontrollersDocument8 pagesRr322203 Microprocessors Microcontrollersgeddam06108825No ratings yet

- Computer System OrganizationDocument4 pagesComputer System OrganizationIjjada VivekanandaNo ratings yet

- JNTUK Computer Organization Nov 2015 Question PaperDocument4 pagesJNTUK Computer Organization Nov 2015 Question PaperTSRKNo ratings yet

- R07 Set No. 2Document5 pagesR07 Set No. 2Krishna MoorthyNo ratings yet

- R5210505 Computer OrganizationDocument1 pageR5210505 Computer OrganizationsivabharathamurthyNo ratings yet

- 07a5ec07 ComputerorganizationDocument6 pages07a5ec07 ComputerorganizationRam KrishNo ratings yet

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankaniprahalNo ratings yet

- Third Homework AssignmentDocument4 pagesThird Homework AssignmentTara Shankar ChakrabortyNo ratings yet

- Rr411403 Computer OrganisationDocument6 pagesRr411403 Computer OrganisationSRINIVASA RAO GANTANo ratings yet

- rr310501 Interfacing Through MicroprocessorsDocument7 pagesrr310501 Interfacing Through MicroprocessorsSRINIVASA RAO GANTANo ratings yet

- 07A80305 COMPUTERORGANIZATIONANDARCHITECTUREfr 7607Document8 pages07A80305 COMPUTERORGANIZATIONANDARCHITECTUREfr 7607Pulihora Kat RajaNo ratings yet

- r05320402 Vlsi DesignDocument4 pagesr05320402 Vlsi DesignSRINIVASA RAO GANTANo ratings yet

- Ignou MCS 14Document5 pagesIgnou MCS 14Abhishek MandalNo ratings yet

- Model MCDocument2 pagesModel MCAkilen MahalingamNo ratings yet

- Computer Organization Dec 2010Document2 pagesComputer Organization Dec 2010Prasad C MNo ratings yet

- rr312001 Microprocessors and InterfacingDocument8 pagesrr312001 Microprocessors and InterfacingSRINIVASA RAO GANTANo ratings yet

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankMalk Malik0% (1)

- Co ImpDocument7 pagesCo ImpG09Deviprasad N shettyNo ratings yet

- Ca 13Document3 pagesCa 13krishnasankar95No ratings yet

- 08AB303 - DIGITAL LOGIC CIRCUITSDocument3 pages08AB303 - DIGITAL LOGIC CIRCUITSChandru RamaswamyNo ratings yet

- Ec2203 Digital Electronics r8Document3 pagesEc2203 Digital Electronics r8jenifar777No ratings yet

- Computer Organization and Design (CSE-201) (Makeup)Document2 pagesComputer Organization and Design (CSE-201) (Makeup)damoy28211No ratings yet

- RA CS3121 Interfacing Through MicroprocessorsDocument2 pagesRA CS3121 Interfacing Through MicroprocessorssivabharathamurthyNo ratings yet

- Set No: 1: Code No: V3219/R07Document4 pagesSet No: 1: Code No: V3219/R07Gopi Pavan JonnadulaNo ratings yet

- R7310201-Computer System OrganizationDocument4 pagesR7310201-Computer System OrganizationsivabharathamurthyNo ratings yet

- 07a81901 AdvancedcomputerarchitectureDocument4 pages07a81901 AdvancedcomputerarchitectureSharanya ThirichinapalliNo ratings yet

- Printed Pages : 3 ADCA / MCA (III Year) 7t' Term-End Examination December, 2011 CS-12 : COMPUTER ARCHITECTUREDocument3 pagesPrinted Pages : 3 ADCA / MCA (III Year) 7t' Term-End Examination December, 2011 CS-12 : COMPUTER ARCHITECTUREhaider_ali980No ratings yet

- 7 Dec09-Jan10 DSP Al and Arch.Document2 pages7 Dec09-Jan10 DSP Al and Arch.suresha vNo ratings yet

- C0-R4.B4 Page 1 of 2 January, 2019 (6+6+6)Document2 pagesC0-R4.B4 Page 1 of 2 January, 2019 (6+6+6)sanjay sheeNo ratings yet

- Microprocessors (CSE 206) (Makeup)Document2 pagesMicroprocessors (CSE 206) (Makeup)Vishal VimalkumarNo ratings yet

- End Semester Examination: January, 2022 Digital Electronics and Computer OrganizationDocument3 pagesEnd Semester Examination: January, 2022 Digital Electronics and Computer OrganizationFFFNo ratings yet

- Computer Organization May 2008 Question PaperDocument4 pagesComputer Organization May 2008 Question Paperelimelek100% (1)

- T.E. (E&TC) : Time:3 Hours) (Max. Marks:100 Instructions To The CandidatesDocument3 pagesT.E. (E&TC) : Time:3 Hours) (Max. Marks:100 Instructions To The Candidatesaniruddhaphatak93No ratings yet

- APJ Abdul Kalam Tech University CS405 Exam QuestionsDocument3 pagesAPJ Abdul Kalam Tech University CS405 Exam QuestionsCigi ManojNo ratings yet

- CRC of BCA (2) Assignment (Revised Syllabus)Document17 pagesCRC of BCA (2) Assignment (Revised Syllabus)BshrinivasNo ratings yet

- MCS 012dec22Document4 pagesMCS 012dec22kk2760057No ratings yet

- GSM SMS EEPROM LPC2148 T.E. Advanced ProcessorsDocument2 pagesGSM SMS EEPROM LPC2148 T.E. Advanced Processorsharshad lokhandeNo ratings yet

- Electronic Structure Calculations on Graphics Processing Units: From Quantum Chemistry to Condensed Matter PhysicsFrom EverandElectronic Structure Calculations on Graphics Processing Units: From Quantum Chemistry to Condensed Matter PhysicsRoss C. WalkerNo ratings yet

- Attainable Region Theory: An Introduction to Choosing an Optimal ReactorFrom EverandAttainable Region Theory: An Introduction to Choosing an Optimal ReactorNo ratings yet

- Architecture-Aware Optimization Strategies in Real-time Image ProcessingFrom EverandArchitecture-Aware Optimization Strategies in Real-time Image ProcessingNo ratings yet

- 07a82101 AircraftsystemsandinstrumentsDocument4 pages07a82101 AircraftsystemsandinstrumentsSharanya ThirichinapalliNo ratings yet

- 07a82103 Advanced Computational AerodynamicsDocument4 pages07a82103 Advanced Computational AerodynamicsSharanya ThirichinapalliNo ratings yet

- 07a81905 Data Warehousing and Data MiningDocument4 pages07a81905 Data Warehousing and Data MiningSharanya ThirichinapalliNo ratings yet

- 07a82104 HelicopterengineeringDocument7 pages07a82104 HelicopterengineeringSharanya ThirichinapalliNo ratings yet

- 07a81903 InformationsecurityDocument6 pages07a81903 InformationsecuritySharanya ThirichinapalliNo ratings yet

- IpqDocument5 pagesIpqUmesh MorankarNo ratings yet

- 07a81803 SuperalloysDocument4 pages07a81803 SuperalloysSharanya ThirichinapalliNo ratings yet

- 07a81901 AdvancedcomputerarchitectureDocument4 pages07a81901 AdvancedcomputerarchitectureSharanya ThirichinapalliNo ratings yet

- 07a81701 OpticalcommunicationsDocument8 pages07a81701 OpticalcommunicationsSharanya ThirichinapalliNo ratings yet

- 07a81904 ElectronicsmeasurementsandinstrumentationDocument7 pages07a81904 ElectronicsmeasurementsandinstrumentationSharanya ThirichinapalliNo ratings yet

- 07a81801 CompositematerialsDocument4 pages07a81801 CompositematerialsSharanya ThirichinapalliNo ratings yet

- 07a81802 Nuclear MetallurgyDocument4 pages07a81802 Nuclear MetallurgySharanya ThirichinapalliNo ratings yet

- 07a81402 Flexible Manufacturing SystemsDocument4 pages07a81402 Flexible Manufacturing SystemsSharanya ThirichinapalliNo ratings yet

- 07a81202 NetworkmanagementsystemsDocument4 pages07a81202 NetworkmanagementsystemsSharanya ThirichinapalliNo ratings yet

- 07a81204 Bio InformaticsDocument4 pages07a81204 Bio InformaticsSharanya ThirichinapalliNo ratings yet

- 07a81203 BiometricsDocument4 pages07a81203 BiometricsSharanya ThirichinapalliNo ratings yet

- 07a80809 OperationsresearchDocument11 pages07a80809 OperationsresearchSharanya ThirichinapalliNo ratings yet

- 07a81205 PatternrecognitionDocument7 pages07a81205 PatternrecognitionSharanya ThirichinapalliNo ratings yet

- 07a81005 TelemetryandtelecontrolDocument4 pages07a81005 TelemetryandtelecontrolSharanya ThirichinapalliNo ratings yet

- 07a81102 BiomaterialsDocument4 pages07a81102 BiomaterialsSharanya ThirichinapalliNo ratings yet

- 07a81201 MultimediadatabasesDocument5 pages07a81201 MultimediadatabasesSharanya ThirichinapalliNo ratings yet

- 07a81001 IndustrialelectronicsDocument6 pages07a81001 IndustrialelectronicsSharanya ThirichinapalliNo ratings yet

- 07a80806 Energy EngineeringDocument4 pages07a80806 Energy EngineeringSharanya ThirichinapalliNo ratings yet

- 07a81101 BiomemsDocument4 pages07a81101 BiomemsSharanya ThirichinapalliNo ratings yet

- 07a81004 ManagementinformationsystemsDocument4 pages07a81004 ManagementinformationsystemsSharanya ThirichinapalliNo ratings yet

- 07a81002 RoboticsandautomationDocument8 pages07a81002 RoboticsandautomationSharanya ThirichinapalliNo ratings yet

- 07a81003 MicrocontrolersandapplicationsDocument4 pages07a81003 MicrocontrolersandapplicationsSharanya ThirichinapalliNo ratings yet

- 07a80805 OptimizationofchemicalprocessesDocument8 pages07a80805 OptimizationofchemicalprocessesSharanya ThirichinapalliNo ratings yet

- 07a80801 IndustrialpollutioncontrolengineeringDocument4 pages07a80801 IndustrialpollutioncontrolengineeringSharanya ThirichinapalliNo ratings yet

- Survey On Stereovision Based Disparity Map Using Sum of Absolute DifferenceDocument2 pagesSurvey On Stereovision Based Disparity Map Using Sum of Absolute DifferenceInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- State Polytechnic of Jember: The Exercises of File System Chapter 10Document15 pagesState Polytechnic of Jember: The Exercises of File System Chapter 10Dwi Rifki NoviantoNo ratings yet

- Creating Vagrant BoxesDocument8 pagesCreating Vagrant BoxesRamanuj SinghNo ratings yet

- F-DS037 - Graph Pack Software DatasheetDocument2 pagesF-DS037 - Graph Pack Software Datasheetab_s5036No ratings yet

- Add 16-bit Numbers Using 8085 MicroprocessorDocument125 pagesAdd 16-bit Numbers Using 8085 MicroprocessorsurekadeepuNo ratings yet

- Opmanager Plus Product Information Sheet 1Document49 pagesOpmanager Plus Product Information Sheet 1Nghiêm Sỹ Tâm PhươngNo ratings yet

- Crusoe Microprocessor Designed for Low Power Mobile ComputingDocument25 pagesCrusoe Microprocessor Designed for Low Power Mobile ComputingsravanpasunooriNo ratings yet

- Smart Labors: Final Year Project Task 2Document3 pagesSmart Labors: Final Year Project Task 2Misbah NaveedNo ratings yet

- Solution: Option (B)Document3 pagesSolution: Option (B)Shikha AryaNo ratings yet

- Bidirectional Bubble Sort Approach To Improving The Performance of Introsort in The Worst Case For Large Input SizeDocument8 pagesBidirectional Bubble Sort Approach To Improving The Performance of Introsort in The Worst Case For Large Input SizeAI Coordinator - CSC JournalsNo ratings yet

- Chapter 5 - Cisco IOSDocument24 pagesChapter 5 - Cisco IOS0260480981No ratings yet

- MicroVAX 3100 Maintenance GuideDocument8 pagesMicroVAX 3100 Maintenance GuideGary ParkerNo ratings yet

- WCCA ProgRef en-US PDFDocument1,352 pagesWCCA ProgRef en-US PDFjbaltazar77No ratings yet

- Architectural Challenges in Agile PracticeDocument4 pagesArchitectural Challenges in Agile PracticePranab PyneNo ratings yet

- Lab ManualDocument17 pagesLab ManualHamza Malik50% (2)

- AudioCaptureRaw WalkthroughDocument12 pagesAudioCaptureRaw WalkthroughoguzhanoozkanNo ratings yet

- Canon Hard DrivesDocument2 pagesCanon Hard Driveschrisser11No ratings yet

- Planning UtilsDocument65 pagesPlanning UtilsKrishna TilakNo ratings yet

- Lab Answer Key - Module 2 - Using Visual Basic Programming ConstructsDocument42 pagesLab Answer Key - Module 2 - Using Visual Basic Programming ConstructsJoemarco BernabeNo ratings yet

- Mike Nelson Resume 2008Document2 pagesMike Nelson Resume 2008api-12184182No ratings yet

- Operational Management – Numerical OptimizationDocument4 pagesOperational Management – Numerical OptimizationGhina ShaikhNo ratings yet

- Automated Attendance System Using Biometrics With Embedded WebserverDocument4 pagesAutomated Attendance System Using Biometrics With Embedded Webserversanthosh_s_17100% (1)

- JNCIA SyllabusDocument2 pagesJNCIA SyllabusAshish KhairnarNo ratings yet

- Phishing Attack Types & Mitigation StrategiesDocument7 pagesPhishing Attack Types & Mitigation Strategiessarim.khawajaNo ratings yet

- LC Install 101Document203 pagesLC Install 101bowosampahNo ratings yet

- RMT NotesDocument31 pagesRMT NotessherlinsamNo ratings yet

- How To Install Linux, Apache, Mysql, PHP (Lamp) Stack On UbuntuDocument9 pagesHow To Install Linux, Apache, Mysql, PHP (Lamp) Stack On UbuntuMada BaskoroNo ratings yet