Professional Documents

Culture Documents

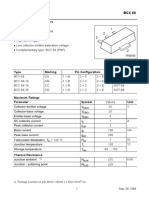

D08BE7 ETRX Bvlsi

Uploaded by

aniket-mhatre-164Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

D08BE7 ETRX Bvlsi

Uploaded by

aniket-mhatre-164Copyright:

Available Formats

--- -

g.~X!P~D-7 L RPiv)

-toX.

B(L!lL6 0{- .VL~

(REVISED COURSE) (3 Hours) [Total

[ 7 } 12-}fJ-8

'Con. 5711-08.

RC-7244(

Marks:

100

N.B. : (1) Question No.1 is compulsory. (2) Attempt any four questions out of remaining six questions. (3) Assume suitable data wherever necessary and state clearly. 1. (a) Compare Resistive load, Depletion load and Enhancement load 10 inverters. Also write their merits, demerits and applications. (b) Explain the operation of CMOS inverter with clearly mentioning the 10 five cases given below :-

,.

(i)

,

V.in < V TO,n

Vin = VIL

Vin = V1H

(ii)

(iii)

(iv)

Vin > VDD + VTO,p

(V) Vin = V TH(Inverter

Threshold).

2. (a) For the CMOS inverter, let the supply voltage VDD= I.SV; the threshold 10 voltage for both NMOS and PMOS transistor Vth = O.5V. Both the transistors are. matched exactly such that f3n= f3p' Find the unity gain points (the values of input voltages V1L'V1Hand corresponding output Vout) of the inverter characteristics assuming that the inverter is not loaded. (b) Explain the latch up in CMOS. What are the remedies to avoid the 10 latch up ? 3. (a) Design a circuit for th~ function A+(B+C)(D+E) using CMOS logic. 10 Size all the transistors so that rise and fall time of the output of function is equivalent to standard CMOS inverter with PMOS width is 2 W.and NMOS width is W (b) What do you mean by threshold voltage of MOSFET ? How do we 10 control ?Explainwith the help of relevant mathematical equations. 4. (a) Explain the concept of pass transistor logic useful to implement logic 10 function. Explain limitations of PMOS/NMOS transistors and how it can be taken care.of. (b) Explain the method to design 4: 1 MUX using pass transistor logic. 10 Draw the circuit diagram using NMOS pass transistors. Also draw the stick diagram.

[TURN OVER

Y-Ex-II-08-Scan-D-35

Con. 5711-RC-7244-08.

.>

5. (a)

Explain

constant

field scaling.

10

(b)

Assuming a constant scaling factor of 0.7 for various critical MOSFET parameters, calculate the perfonnance improvement in terms of package density, power dissipation, and speed for ideal CMOS process. Draw the circuit diagram,.stick diagram and layout using A based de- 10 sign rules for the two inputs CMOS NAND gate. Use proper aspect ratio and color coding. . 20

6. CMOS inverter is to be fabricated using n-well process. Discuss various steps involved in fabrication. Sketch the masking steps in cross sectional view giving mask sequence. ~e~tion the number of masks required in complete process.

7.

---"

Write' (i) (ii) (iii) (iv) (v) (vi)

short notes on any four:Custom and Semi custom design methods Short channel effects in MOSFET Design verification methods VHDL in VLSI design Burriedand Butting contacts Comparison of ion implantation and diffusion. s

20 '

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Mosfet Testing With Multi MeterDocument3 pagesMosfet Testing With Multi MeterSalih AnwarNo ratings yet

- Delta6rc FinalDocument2 pagesDelta6rc FinalsarvottamNo ratings yet

- ISDN NotesDocument3 pagesISDN Notesaniket-mhatre-164No ratings yet

- MB Multiplierhdl FpgaDocument10 pagesMB Multiplierhdl Fpgaaniket-mhatre-164No ratings yet

- J09BE7 ETRX BvlsiDocument1 pageJ09BE7 ETRX Bvlsianiket-mhatre-164No ratings yet

- J08BE7 ETRX BvlsiDocument2 pagesJ08BE7 ETRX Bvlsianiket-mhatre-164No ratings yet

- D11be7 Etrx RevDocument11 pagesD11be7 Etrx Revaniket-mhatre-164No ratings yet

- E - C Etj - .::B) : '/' '"Dem09-Dd - (A) Con. T? .14-09. 0As/C3 - O - /JL-S 'Document2 pagesE - C Etj - .::B) : '/' '"Dem09-Dd - (A) Con. T? .14-09. 0As/C3 - O - /JL-S 'aniket-mhatre-164No ratings yet

- TCP UDP: Acronym ForDocument1 pageTCP UDP: Acronym Foraniket-mhatre-164No ratings yet

- Least Cost AlgorithmsDocument6 pagesLeast Cost Algorithmsaniket-mhatre-164No ratings yet

- Inband and Outband SignallingDocument1 pageInband and Outband Signallinganiket-mhatre-164No ratings yet

- TCPDocument2 pagesTCPaniket-mhatre-164No ratings yet

- Oil SpillDocument21 pagesOil Spillmhatre_aniketNo ratings yet

- Troubleshooting For Rb751U-2HndDocument11 pagesTroubleshooting For Rb751U-2Hnddeniwahyud channelNo ratings yet

- IRF150 Power Mosfet For PWM RegulationDocument8 pagesIRF150 Power Mosfet For PWM RegulationOjo RojoNo ratings yet

- IGCTDocument1 pageIGCTapi-3753995No ratings yet

- Bss 145Document7 pagesBss 145Miloud ChouguiNo ratings yet

- Characteristics of Silicon and GermaniumDocument2 pagesCharacteristics of Silicon and GermaniumKanageshwari Rathakrishnan100% (4)

- ECE 305 Homework: Week 10: SolutionsDocument6 pagesECE 305 Homework: Week 10: SolutionsjiosNo ratings yet

- Exercices Transistors Cor PDFDocument5 pagesExercices Transistors Cor PDFAhmed GuetatNo ratings yet

- Semiconductor RevolutionDocument49 pagesSemiconductor RevolutionSubhadip MondalNo ratings yet

- High Breakdown Voltage AlGaN-GaN HEMTs Achieved by Multiple Field PlatesDocument3 pagesHigh Breakdown Voltage AlGaN-GaN HEMTs Achieved by Multiple Field PlatesdaaanuNo ratings yet

- Corner Effect in Double and Triple GateDocument4 pagesCorner Effect in Double and Triple GateIELTS 2021.10No ratings yet

- PIC Microcontrollers ListDocument2 pagesPIC Microcontrollers Listdddddd2013No ratings yet

- Thyristors & SCRs 3Document28 pagesThyristors & SCRs 3Vincent SpadeNo ratings yet

- Isc N-Channel MOSFET Transistor IRFS3607: FeaturesDocument2 pagesIsc N-Channel MOSFET Transistor IRFS3607: FeaturesBarkat HussainNo ratings yet

- DICD Tutorial 5Document5 pagesDICD Tutorial 5Pavika Sharma100% (1)

- EDID632C: Elementary Studies: Transistor FundamentalsDocument87 pagesEDID632C: Elementary Studies: Transistor Fundamentalsakash kumarNo ratings yet

- Sheet 7Document3 pagesSheet 7Mo EidNo ratings yet

- Lab ReportDocument9 pagesLab ReportDadNo ratings yet

- Datasheet Xl1225Document3 pagesDatasheet Xl1225Nicolae CiuraruNo ratings yet

- bcx68 InfineonDocument5 pagesbcx68 InfineonAbdo GrandayzerNo ratings yet

- P 6010 DTFGDocument5 pagesP 6010 DTFGJohnsan DrummerNo ratings yet

- Infineon-Evaluation Board KIT 1EDB AUX SiC-ApplicationNotes-V01 00-EnDocument29 pagesInfineon-Evaluation Board KIT 1EDB AUX SiC-ApplicationNotes-V01 00-EnSergio ImotoNo ratings yet

- EEE 2212 Revision QuestionsDocument9 pagesEEE 2212 Revision QuestionsIAMMARKSNo ratings yet

- Artificial Retina Using Thin Film Transistors: Presented by Y.Mounisha 12W51A04A0Document20 pagesArtificial Retina Using Thin Film Transistors: Presented by Y.Mounisha 12W51A04A0Hemanth KumarNo ratings yet

- Homwork - 1Document15 pagesHomwork - 1TimoNo ratings yet

- Lecture Plan Electronic Dev. ECC 201 MKDDocument1 pageLecture Plan Electronic Dev. ECC 201 MKDrama09092006No ratings yet

- ECN-341 - Lab-01 ReportDocument4 pagesECN-341 - Lab-01 ReportAjinkya YawalkarNo ratings yet

- Stick DiagramDocument24 pagesStick DiagramHasan SadatNo ratings yet