Professional Documents

Culture Documents

Maximum Ratio Combining For A WCDMA Rake Receiver

Uploaded by

tycoonaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Maximum Ratio Combining For A WCDMA Rake Receiver

Uploaded by

tycoonaCopyright:

Available Formats

Freescale Semiconductor Application Note

AN2251 Rev. 2, 11/2004

Maximum Ratio Combining for a WCDMA Rake Receiver

By Kim-Chyan Gan

Wideband CDMA (WCDMA), a widely accepted thirdgeneration interface, is based on direct-sequence (DS) CDMA technology. To minimize distortion of the signals in a DSCDMA system, a rake receiver is used. A signal transmitted through the wireless channel may be severely distorted due to co-channel interference, adjacent channel interference (or multiple access interference), thermal noise, and multipath fading. The most severe distortion comes from fading, which changes the bit error rate (BER) curve from an exponential to a linear curve. One technique the rake receiver employs to combat these distortions is diversity. There are different diversity techniques, including frequency, time, and space. This application note explains how the DS-CDMA rake receiver employs multipath diversity techniques to minimize distortion.

CONTENTS 1 2 3 4

System Model ......................................................... 2 Chip/Symbol Rate Combining ................................3 Implementation in StarCore ....................................5 Results..................................................................... 7

Freescale Semiconductor, Inc., 2004. All rights reserved.

System Model

System Model

Selection diversity (SD). When L multipath signals are received, the combining scheme selects the paths with the higher signal-to-noise ratio (SNR) and discards the L-1 paths. Selection diversity is used in reverse-link of IS-95, where multiple base stations receive the signal from the mobile, but only the basestation that receives the strongest signal is chosen to serve the mobile. Equal gain combining (EGC). The receiver corrects the phase rotation of the received signals caused by the fading channel and combines the received signals of different paths with equal weight. Maximum ratio combining (MRC). The optimum way (in the sense of the least BER) to use information from different paths to achieve decoding in an additive white gaussian channel (AWGN) [1].2 The receiver corrects the phase rotation caused by a fading channel and then combines the received signals of different paths proportionally to the strength of each path. Since each path undergoes different attenuations, combining them with different weights yield an optimum solution under an AWGN channel.

In the diversity scenario are different combining schemes, including the following:1

In a Rayleigh fading channel, the MRC performance is the best, followed by EGC, and then SD. The performance of MRC is the same as that of EGC if signals from each path are of equal strength. In a DS-CDMA communications system, the received signal from the base station to the handset can be expressed as follows:

Equation 1

L

r(p) =

p cl( p ) a

l=1

l ---- + n(p) Tc

Where:

p: discrete time index r(p): the received baseband signal after match filter L: the number of fading paths cl(p): discrete complex channel coefficient of the lth path ak(p): discrete transmitted data l: delay of the lth path Tc: chip period [x]: rounding of x n(p): thermal noise plus inter-channel interference

The path searcher finds the exact delay of each path, and the channel estimation finds the fading channel coefficient.With this information, the received signal, r(p), can be decoded, as follows.

Equation 2

i i - c p + ---- = a ( p ) + r p + --- Tc i Tc

L

l = 1, l i

i i l i i l - c p + ---- a p ---- + ---- + n p + ---- c p + ---- c l p + --- Tc i Tc Tc Tc Tc i Tc

1. See Lee, J. S., Miller, L.E., CDMA Systems Engineering Handbook, Artech House mobile communication library, 1998. See also the TIA/EIA/IS-95-A, Mobile Station-Base Station Compatibility Standard for a Dual-Mode Wideband Spread Spectrum Cellular System. 2. See Stuber, G. L., Principles of Mobile Communication, 1st ed. Kluwer Academic Publishers, 1996

Maximum Ratio Combining for a WCDMA Rake Receiver, Rev. 2 2 Freescale Semiconductor

Chip/Symbol Rate Combining

The first term on the right-hand side (R.H.S.) is the transmitted data weighted by the strength of the fading channel (). The second term is inter-path interference (IPI). The last two terms (second and term term) can be combined and modeled as a single AWGN noise. As the noise from last two terms increases, the probability of error increases. If the fading channel is a Rayleigh distribution, becomes an exponential distribution. If is less than 1, the distance between the symbols in signal constellation shrinks, and the error in decoding becomes more likely than in a normal AWGN channel. In other words, fading shortens the distance in the signal constellation, changing the BER curve to linearly decrease as SNR goes up. To achieve better diversity, the signals from different paths should be totally uncorrelated. If the signals from different paths are correlated, performance deteriorates because duplicate information is extracted from each path. In a real environment, the signals from different paths are almost correlated. The strengths of different paths also affect the probability error curve. If total power is constant, it is desirable to allocate power equally to signals of all the paths to achieve better diversity. In a real-time transmission, the strength of the signal depends on the environment.

Chip/Symbol Rate Combining

There are two ways to achieve combining: at the chip level and at the symbol level. Symbol-level combining, as its name implies, combines the signals of different paths at the symbol level. The descrambling and despreading are performed before combining in order to convert chip-level signals into symbol-level signals. Figure 1 shows the block diagram for combining at the symbol level. Chip-level combining performs combining followed by descrambling and despreading. Figure 2 shows the block diagram for combining at the chip level.

Path Search Descramble/ Despreading

Channel Estimation

g * (t, 1)

1

r (t)

r(t - 1)

dt dt dt dt

X g * (t, 2)

2 3 4

r(t - 2)

X g * (t, 2)

Maximum Ratio Combining (MRC)

I/Q Demapper

r(t - 3)

X g * (t, 4) X

r(t - 4)

Figure 1. Block Diagram Rake Receiver (Symbol-level Combining)

Maximum Ratio Combining for a WCDMA Rake Receiver, Rev. 2 Freescale Semiconductor 3

Chip/Symbol Rate Combining

Path Search

Channel Estimation

g * (t, 1)

1

r (t)

r(t - 1)

X g * (t, 2) Descramble/ Despreading

2 3 4

r(t - 2)

X g * (t, 2)

Maximum Ratio Combining (MRC)

dt

I/Q Demapper

r(t - 3)

X g * (t, 4) X

r(t - 4)

Figure 2. Block Diagram Rake Receiver (Chip-level Combining)

The performance of both combining schemes is the same under perfect channel estimation and path searching, assuming that the fading channel is constant over a symbol period. Table 1 shows the estimation of the computational loads of both combining schemes for one channel. The descrambling and despreading are combined and occur in one step. It is assumed that the scrambling code and the spreading code do not change during the transmission.3

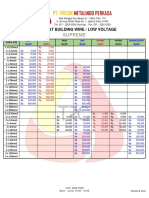

Table 1. Complexity of Chip-Level Versus Symbol-Level Combining in One Channel

Number of Finger(s) Spreading Factor Chip-Level Combining Number of Real MACs in MRC Number of Real MACs in Descramble/ Despread Total MACs Symbol-Level Combining Number of Real MACs in Descramble/ Despread Number of Real MACs in MRC Total MACs

1 1 2 2 3 3 4 4 5

4 512 4 512 4 512 4 512 4

153600 153600 307200 307200 460800 460800 614400 614400 768000

153600 153600 153600 153600 153600 153600 153600 153600 153600

307200 307200 460800 460800 614400 614400 768000 768000 921600

153600 153600 307200 307200 460800 460800 614400 614400 768000

38400 300 76800 600 115200 900 153600 1200 192000

192000 153900 384000 307800 576000 461700 768000 615600 960000

3. If the spreading or the scrambling code changes, the new composite scrambling/spreading code needs to be generated.

Maximum Ratio Combining for a WCDMA Rake Receiver, Rev. 2 4 Freescale Semiconductor

Implementation in StarCore

Table 1. Complexity of Chip-Level Versus Symbol-Level Combining in One Channel (Continued)

Number of Finger(s) Spreading Factor Chip-Level Combining Number of Real MACs in MRC Number of Real MACs in Descramble/ Despread Total MACs Symbol-Level Combining Number of Real MACs in Descramble/ Despread Number of Real MACs in MRC Total MACs

5 6 6

512 4 512

768000 921600 921600

153600 153600 153600

921600 1075200 1075200

768000 921600 921600

1500 230400 1800

769500 1152000 923400

In the rake receiver, symbol-rate combining rather than chip-rate combining is used in the simulation because symbol-rate combining requires fewer computations, especially when the spreading factor goes up. Channel estimation is hard to achieve in chip-level combining. Usually, it is estimated at the symbol level and interpolated to the chip level. Therefore, symbol-level channel estimation requires fewer cycles than chip-level estimation since the interpolation (even the simplest repetition or first-order hold) requires some cycles. The symbol and chip rate combining are compared in term of memory usage. In chip rate combining, one path is stored, but the stored data is in chip-rate, which is as many as 38400 samples. In symbol rate combining, the data of multiple paths is stored. However, each path is in symbol level. The total number of samples is (38400/SF) * L. The discrepancy of memory usage between chip and symbol combining is as follows:

Equation 3

38000 -L = 38400 -------------SF

where L is the number of fingers (ranging from 2 to 8) and SF is the spreading factor (ranging from 4 to 512). If Equation 3 is positive, chip-rate combining requires more memory than symbol-rate combining. Since SF is larger than L most of the time, and Equation 3 is positive, symbol-rate combining uses less memory than chip-rate combining.

Implementation in StarCore

A four-finger rake receiver is considered for implementation. MRC is just a complex multiplication with a channel coefficient in each finger, followed by addition of the results from the different fingers. These steps can be combined using multiply-accumulation (MAC) instructions. Optimization techniques used in an MRC routine are as follows: Software pipelining. Loads both the input and output data. Thus, the first input is executed at the end of the loop while the data output occurs at the beginning of the loop. Scheduling. Allows two combinings to proceed concurrently. In the SC140 core, there are four Data Arithmetic Logic Units (DALUs). One symbol combining occupies two DALUs, one for real and another for imaginary calculation. Thus, two combinings use up all the DALUs. Loop unrolling. The inner kernel is unrolled four times because the outer kernel is executed very frequently. This technique saves the cycles of setting up the loop at the expense of memory size.

Chip-level or symbol-level combining does not affect the MRC implementation. Only the loop counter must be changed. The MRC in this application note is valid for both combining schemes. For chip-level combining, N is 38400, and for symbol-level combining, N is 38400/SF (SF is the spreading factor).

Maximum Ratio Combining for a WCDMA Rake Receiver, Rev. 2 Freescale Semiconductor 5

Implementation in StarCore

Example 1. Maximum Ratio Combining (Four Fingers) move.l #N/2,d0 ; dosetup0 combine4path doen0 d0 [ move.4f (r0)+,d0:d1:d2:d3 ; move.4f (r8)+,d4:d5:d6:d7 ; ] falign loopstart0 combine4path: [ mpy d0,d4,d8 ; mpy d1,d4,d9 ; mpy d2,d6,d10 ; mpy d3,d6,d11 ; moves.4f d8:d9:d10:d11,(r7)+ ; ] [ mac d1,d5,d8 ; mac -d0,d5,d9 ; mac d3,d7,d10 ; mac -d2,d7,d11 ; move.4f (r1)+,d0:d1:d2:d3 ; move.4f (r9)+,d4:d5:d6:d7 ; ] [ mac d0,d4,d8 ; mac d1,d4,d9 ; mac d2,d6,d10 ; mac d3,d6,d11 ; ] [ mac d1,d5,d8 ; mac -d0,d5,d9 ; mac d3,d7,d10 ; mac -d2,d7,d11 ; move.4f (r2)+,d0:d1:d2:d3 ; move.4f (r10)+,d4:d5:d6:d7 ; ] [ mac d0,d4,d8 ; mac d1,d4,d9 ; mac d2,d6,d10 ; mac d3,d6,d11 ; ] [ mac d1,d5,d8 ; mac -d0,d5,d9 ; mac d3,d7,d10 ; mac -d2,d7,d11 ; move.4f (r3)+,d0:d1:d2:d3 ; move.4f (r11)+,d4:d5:d6:d7 ; ] [ mac d0,d4,d8 ; mac d1,d4,d9 ; mac d2,d6,d10 ; mac d3,d6,d11 ; ] [ macr d1,d5,d8 ; macr -d0,d5,d9 ; macr d3,d7,d10 ; macr -d2,d7,d11 ; move.4f (r0)+,d0:d1:d2:d3 ; move.4f (r8)+,d4:d5:d6:d7 ; ] loopend0 moves.4f d8:d9:d10:d11,(r7)+ ; N/2 ri(1,1),rq(1,1),ri(1,2),rq(1,2) gi(1,1),gq(1,1),gi(1,2),gq(1,2)

ri(1,1)*gi(1,1) rq(1,1)*gi(1,1) ri(1,2)*gi(1,2) rq(1,2)*gi(1,2) output, first 4 are dummies rq(1,1)*gq(1,1) ri(1,1)*gq(1,1) rq(1,2)*gq(1,2) ri(1,2)*gq(1,2) ri(2,1),rq(2,1),ri(2,2),rq(2,2) gi(2,1),gq(2,1),gi(2,2),gq(2,2) ri(2,1)*gi(2,1) rq(2,1)*gi(2,1) ri(2,2)*gi(2,2) rq(2,2)*gi(2,2) rq(2,1)*gq(2,1) ri(2,1)*gq(2,1) rq(2,2)*gq(2,2) ri(2,2)*gq(2,2) ri(3,1),rq(3,1),ri(3,2),rq(3,2) gi(3,1),gq(3,1),gi(3,2),gq(3,2) ri(3,1)*gi(3,1) rq(3,1)*gi(3,1) ri(3,2)*gi(3,2) rq(3,2)*gi(3,2) rq(3,1)*gq(3,1) ri(3,1)*gq(3,1) rq(3,2)*gq(3,2) ri(3,2)*gq(3,2) ri(4,1),rq(4,1),ri(4,2),rq(4,2) gi(4,1),gq(4,1),gi(4,2),gq(4,2) ri(4,1)*gi(4,1) rq(4,1)*gi(4,1) ri(4,2)*gi(4,2) rq(4,2)*gi(4,2) rq(4,1)*gq(4,1) ri(4,1)*gq(4,1) rq(4,2)*gq(4,2) ri(4,2)*gq(4,2) ri(1,1),rq(1,1),ri(1,2),rq(1,2) gi(1,1),gq(1,1),gi(1,2),gq(1,2) output, first 4 are dummies

Maximum Ratio Combining for a WCDMA Rake Receiver, Rev. 2 6 Freescale Semiconductor

Results

Results

Table 2 shows the approximate cycles per WCDMA frame for MRC and the code size.

Table 2. Code Size and Approximated Cycle Count

Function Maximum Ratio Combining (four fingers) Cycles/Combining Code Size (Bytes)

212

Maximum Ratio Combining for a WCDMA Rake Receiver, Rev. 2 Freescale Semiconductor 7

How to Reach Us:

Home Page: www.freescale.com E-mail: support@freescale.com USA/Europe or Locations not listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GMBH Technical Information Center Schatzbogen 7 81829 Mnchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064, Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T. Hong Kong +800 2666 8080 For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Typical parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including Typicals must be validated for each customer application by customers technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc. StarCore is a trademark of StarCore LLC. All other product or service names are the property of their respective owners. Freescale Semiconductor, Inc. 2004.

AN2251 Rev. 2 11/2004

You might also like

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- DS/CDMA Systems with Differential M-ary Modulation8932(32,8)51264(64,16)1024128(128,32)2048256(256,64)4096Figure 3. Receiver structures: (a) conventional, (b) DDS M-ary and (c) DM-aryDocument7 pagesDS/CDMA Systems with Differential M-ary Modulation8932(32,8)51264(64,16)1024128(128,32)2048256(256,64)4096Figure 3. Receiver structures: (a) conventional, (b) DDS M-ary and (c) DM-aryCường Sống ThiệnNo ratings yet

- Nokia Double Data Rate For FDD Downlink Through Channel Code Puncturing in MIMO ChannelsDocument4 pagesNokia Double Data Rate For FDD Downlink Through Channel Code Puncturing in MIMO ChannelsPhebeNo ratings yet

- BER of OFDM System Using Concatenated Forward Error Correcting Codes (FEC) Over Nakagami-M Fading ChannelDocument5 pagesBER of OFDM System Using Concatenated Forward Error Correcting Codes (FEC) Over Nakagami-M Fading Channelseventhsensegroup100% (1)

- MIMO-Rake Receiver in WCDMADocument8 pagesMIMO-Rake Receiver in WCDMALê Minh NguyễnNo ratings yet

- PSK Demodulation (Part 1)Document10 pagesPSK Demodulation (Part 1)particlereddyNo ratings yet

- S-38.220 Licentiate Course On Signal Processing in Communications, FALL - 97Document15 pagesS-38.220 Licentiate Course On Signal Processing in Communications, FALL - 97Shabeeb Ali OruvangaraNo ratings yet

- Mimo Generalized Decorrelating Discrete-Time Rake Receiver: Tunc Er Baykas, Mohamed Siala, Abbas Yongac o GluDocument4 pagesMimo Generalized Decorrelating Discrete-Time Rake Receiver: Tunc Er Baykas, Mohamed Siala, Abbas Yongac o Glubavar88No ratings yet

- MIMO Systems: Performance of Antenna Diversity and V-BLASTDocument20 pagesMIMO Systems: Performance of Antenna Diversity and V-BLASTRamakrishnan MahadevanNo ratings yet

- Eigen Value Based (EBB) Beamforming Precoding Design For Downlink Capacity Improvement in Multiuser MIMO ChannelDocument7 pagesEigen Value Based (EBB) Beamforming Precoding Design For Downlink Capacity Improvement in Multiuser MIMO ChannelKrishna Ram BudhathokiNo ratings yet

- Adaptive Beamforming For Ds-Cdma Using Conjugate Gradient Algorithm in Multipath Fading ChannelDocument5 pagesAdaptive Beamforming For Ds-Cdma Using Conjugate Gradient Algorithm in Multipath Fading ChannelV'nod Rathode BNo ratings yet

- DS-CDMA System Analysis in Fading ChannelsDocument5 pagesDS-CDMA System Analysis in Fading ChannelsAnonymous JPbUTto8tqNo ratings yet

- L-3/T-,2/EEE Date: 09/06/2014: To Obtain A PAM Signal, Where, Is The Width of Pulse. What Is TheDocument34 pagesL-3/T-,2/EEE Date: 09/06/2014: To Obtain A PAM Signal, Where, Is The Width of Pulse. What Is TheMahmudNo ratings yet

- Channel Estimation EJSR 70-1-04Document8 pagesChannel Estimation EJSR 70-1-04حاتم الشرڭيNo ratings yet

- Performance Analysis of Multicarrier DS-CDMA System Using BPSK ModulationDocument7 pagesPerformance Analysis of Multicarrier DS-CDMA System Using BPSK ModulationiaetsdiaetsdNo ratings yet

- Edge ModulacijaDocument11 pagesEdge ModulacijakrajstNo ratings yet

- 5.another Format Paper 2Document6 pages5.another Format Paper 2iisteNo ratings yet

- Performance Evaluation of Alamouti Space-Time Block Coded Multi-User W-CDMA Wireless Communication SystemDocument5 pagesPerformance Evaluation of Alamouti Space-Time Block Coded Multi-User W-CDMA Wireless Communication SystemHimanshu ThapliyalNo ratings yet

- UMTS RF FundamentalsDocument60 pagesUMTS RF Fundamentalsericsson3gppNo ratings yet

- MC-CDMA With Quadrature Spreading For Wireless Communication SystemsDocument25 pagesMC-CDMA With Quadrature Spreading For Wireless Communication SystemsNageswara Rao ChallaNo ratings yet

- Unit-3 Diversity Techniques: (1) Repetition Coding and Time DiversityDocument14 pagesUnit-3 Diversity Techniques: (1) Repetition Coding and Time DiversityRakesh DevallaNo ratings yet

- Outage Probability Analysis of Wireless Relay and Cooperative Networks in Rician Fading Channels With Different - FactorsDocument5 pagesOutage Probability Analysis of Wireless Relay and Cooperative Networks in Rician Fading Channels With Different - FactorsballmerNo ratings yet

- Assignment 2Document5 pagesAssignment 2Chuah Chian YeongNo ratings yet

- The Performance Analysis of Non-Primitive Turbo Codes in MIMO System Over Flat Fading ChannelDocument4 pagesThe Performance Analysis of Non-Primitive Turbo Codes in MIMO System Over Flat Fading ChannelTra LeNo ratings yet

- Performance Analysis of Decode-and-Forward Relay Network Under Adaptive M-QAMDocument5 pagesPerformance Analysis of Decode-and-Forward Relay Network Under Adaptive M-QAMballmerNo ratings yet

- Turbo Codes in MIMO System: 0-7803-9335-X/05/$20.00 ©2005 IEEE 281Document3 pagesTurbo Codes in MIMO System: 0-7803-9335-X/05/$20.00 ©2005 IEEE 281Tra LeNo ratings yet

- PAPR Reduction of An MC-CDMA System Using SLM Technique: Gagandeep Kaur, Rajbir KaurDocument5 pagesPAPR Reduction of An MC-CDMA System Using SLM Technique: Gagandeep Kaur, Rajbir KaurIjarcet JournalNo ratings yet

- An Analysis of Pilot Symbol Assisted Modulation Rayleigh Fading ChannelsDocument8 pagesAn Analysis of Pilot Symbol Assisted Modulation Rayleigh Fading ChannelsBrijesh GuptaNo ratings yet

- Performance Analysis by Improving Bit Error Rate (BER) Through Various Diversity Techniques in Wireless CommunicationDocument5 pagesPerformance Analysis by Improving Bit Error Rate (BER) Through Various Diversity Techniques in Wireless CommunicationAdugna BefekaduNo ratings yet

- A Broadband Cmos Multiplier-Based Correlator For Ir-Uwb Transceiver SocDocument4 pagesA Broadband Cmos Multiplier-Based Correlator For Ir-Uwb Transceiver SocmiracuNo ratings yet

- Performance of COFDM Using Turbo Codes: Primary Technical Subject Area: Radio CommunicationDocument11 pagesPerformance of COFDM Using Turbo Codes: Primary Technical Subject Area: Radio Communicationmsachemo1No ratings yet

- Peak-To-Average Power Ratio Reduction of Ofdm SiganlsDocument5 pagesPeak-To-Average Power Ratio Reduction of Ofdm SiganlsInternational Journal of Research in Engineering and TechnologyNo ratings yet

- On The Performance of The Layered-Division-Multiplexing Using Maximal-Ratio CombiningDocument11 pagesOn The Performance of The Layered-Division-Multiplexing Using Maximal-Ratio CombiningsubuhpramonoNo ratings yet

- Alamouti 2x3Document4 pagesAlamouti 2x3Bharghava Sasanka DesuNo ratings yet

- Simulation Study 5G NR PHYDocument8 pagesSimulation Study 5G NR PHYgroupe1 stNo ratings yet

- Ec 2004 (PDC) - CS - End - May - 2023Document24 pagesEc 2004 (PDC) - CS - End - May - 2023223UTKARSH TRIVEDINo ratings yet

- Performance Evaluation of Ds-Cdma System Using MatlabDocument13 pagesPerformance Evaluation of Ds-Cdma System Using MatlabMuhammad FirdausNo ratings yet

- The LabVIEW Simulation of Space-Time Coding Technique in The MIMO-OfDM SystemDocument6 pagesThe LabVIEW Simulation of Space-Time Coding Technique in The MIMO-OfDM Systemivy_publisherNo ratings yet

- Chap 5 Amplitude ModulationDocument80 pagesChap 5 Amplitude ModulationWagner MartinsNo ratings yet

- Zs 2010 19 ChinacomDocument7 pagesZs 2010 19 ChinacomkonenianithaNo ratings yet

- OFDM-MIMO Implementation in Line of Sight Microwave/millimeter Wave LinkDocument52 pagesOFDM-MIMO Implementation in Line of Sight Microwave/millimeter Wave LinkBaruch CyzsNo ratings yet

- DS-CDMA Cellular Systems Performance With Base Station Assignment, Power Control Error and Beamforming Over Multipath FadingDocument18 pagesDS-CDMA Cellular Systems Performance With Base Station Assignment, Power Control Error and Beamforming Over Multipath FadingAIRCC - IJCNCNo ratings yet

- Performance Analysis of MIMO-OFDM Systems On Nakagami-M Fading ChannelsDocument5 pagesPerformance Analysis of MIMO-OFDM Systems On Nakagami-M Fading ChannelsmnoppNo ratings yet

- Rijhun 1Document9 pagesRijhun 1amit kumarNo ratings yet

- Performance Improvement of Mc-Cdma System Through DSTBC Site DiversityDocument8 pagesPerformance Improvement of Mc-Cdma System Through DSTBC Site Diversityمحمد الطراونهNo ratings yet

- A Systematic Approach To Peak-to-Average Power Ratio in OFDMDocument11 pagesA Systematic Approach To Peak-to-Average Power Ratio in OFDMWaled Fouad GaberNo ratings yet

- Of Cdma: Performance Multi-Code in A Multipath Fading ChannelDocument6 pagesOf Cdma: Performance Multi-Code in A Multipath Fading Channelfeku fekuNo ratings yet

- 2 DS-CDMA With MRC: U U I I IDocument5 pages2 DS-CDMA With MRC: U U I I INasir KhanNo ratings yet

- Final Research Paper On Cdma Signalling Technique Using MatlabDocument6 pagesFinal Research Paper On Cdma Signalling Technique Using MatlabArpit AgarwalNo ratings yet

- 4-Evaluate The Effect of Dispersion of Fiber On The Performance of OCDMA System and To Find The Limitations Imposed by Dispersion On The Number of User and Length of Transmission PDFDocument6 pages4-Evaluate The Effect of Dispersion of Fiber On The Performance of OCDMA System and To Find The Limitations Imposed by Dispersion On The Number of User and Length of Transmission PDFRockShayar Irfan Ali KhanNo ratings yet

- Optimum Power Allocation For Fading Relay Channels: Muhammad Mehboob Fareed and Murat UysalDocument5 pagesOptimum Power Allocation For Fading Relay Channels: Muhammad Mehboob Fareed and Murat UysalballmerNo ratings yet

- Performance Analysis of Power Line Communication Using DS-CDMA Technique With Adaptive Laguerre FiltersDocument5 pagesPerformance Analysis of Power Line Communication Using DS-CDMA Technique With Adaptive Laguerre FiltersMasterArvinNo ratings yet

- Simulation of A CDMA Systems Using Linear Prediction and MUD (Matlab)Document44 pagesSimulation of A CDMA Systems Using Linear Prediction and MUD (Matlab)Raj Kumar100% (2)

- Using Log Likelihood Relation For BER Analysis of QAM in Space DiversityDocument9 pagesUsing Log Likelihood Relation For BER Analysis of QAM in Space DiversitySudhashree MutuswamyNo ratings yet

- Rake Receiver: Russian SayingDocument53 pagesRake Receiver: Russian SayingFerzia FirdousiNo ratings yet

- Spatial Diversity in Wireless NetworksDocument42 pagesSpatial Diversity in Wireless NetworksDani StoianNo ratings yet

- Ubicc 200 200Document7 pagesUbicc 200 200Ubiquitous Computing and Communication JournalNo ratings yet

- Second Order Statistics of Selection Macrodiversity System in The Presence of Nakagami-M FadingDocument4 pagesSecond Order Statistics of Selection Macrodiversity System in The Presence of Nakagami-M FadingСтефан ПанићNo ratings yet

- Advanced Multicarrier Technologies for Future Radio Communication: 5G and BeyondFrom EverandAdvanced Multicarrier Technologies for Future Radio Communication: 5G and BeyondNo ratings yet

- How To Analyze Call Drop by DTDocument26 pagesHow To Analyze Call Drop by DTramgi_opNo ratings yet

- Analysis On FFER For CDMADocument12 pagesAnalysis On FFER For CDMASwami Nathan RNo ratings yet

- Code Detection and Acquisition Techniques in The DS CDMA Communications PDFDocument11 pagesCode Detection and Acquisition Techniques in The DS CDMA Communications PDFtycoonaNo ratings yet

- Sip PSTN Call Flow HuDocument7 pagesSip PSTN Call Flow Huaajayagarwal80No ratings yet

- Channel Estimation For A WCDMA Rake ReceiverDocument16 pagesChannel Estimation For A WCDMA Rake ReceiverMuhammad FirdausNo ratings yet

- Comprion Tech Day 2009 Dev App SCWSDocument17 pagesComprion Tech Day 2009 Dev App SCWStycoonaNo ratings yet

- SIM Cards OverviewDocument17 pagesSIM Cards Overviewtycoona100% (1)

- Must Have IP NextGen Network ReferenceDocument57 pagesMust Have IP NextGen Network ReferenceTower_Doc0% (1)

- OpenBinder and D-BusDocument2 pagesOpenBinder and D-BustycoonaNo ratings yet

- Soft and Softer Handover in WCDMADocument37 pagesSoft and Softer Handover in WCDMAriyazahmad7989% (9)

- Technical Specifications For Gprs RoutersDocument9 pagesTechnical Specifications For Gprs RouterstycoonaNo ratings yet

- Recommended System Selection Requirements For 1X and 1xEV-DO-Capable Terminals - 143v1.1Document64 pagesRecommended System Selection Requirements For 1X and 1xEV-DO-Capable Terminals - 143v1.1tycoona100% (1)

- SNR Performance Analysis of Rake Receiver For WCDMADocument5 pagesSNR Performance Analysis of Rake Receiver For WCDMAtycoonaNo ratings yet

- Power Control and Adaptive Resource Allocation in DS-CDMA SystemsDocument195 pagesPower Control and Adaptive Resource Allocation in DS-CDMA SystemstycoonaNo ratings yet

- CDMA Network SecurityDocument33 pagesCDMA Network SecuritytycoonaNo ratings yet

- An Introduction To CDMA Air InterfaceDocument71 pagesAn Introduction To CDMA Air InterfacetycoonaNo ratings yet

- Cdma VLR TrainingDocument1 pageCdma VLR TrainingtycoonaNo ratings yet

- Overview of 3G CDMA and WiMAX v3Document81 pagesOverview of 3G CDMA and WiMAX v3tycoonaNo ratings yet

- Mobile Controlled ROBOT Using DTMF Technology - Report1Document10 pagesMobile Controlled ROBOT Using DTMF Technology - Report1Mukesh Yadav0% (2)

- Wireless Mobile ChargerDocument23 pagesWireless Mobile Chargerdeepsikha malik100% (1)

- Pulsed Load Modulation (PLM)Document19 pagesPulsed Load Modulation (PLM)A. VillaNo ratings yet

- Sap Isu Training CourseDocument5 pagesSap Isu Training Coursetrip2ashishNo ratings yet

- 555 Timer ICDocument8 pages555 Timer ICdirdnangliNo ratings yet

- How To Write Bussiness LetterDocument23 pagesHow To Write Bussiness LetterDedi KurniawanNo ratings yet

- Motor Za Kliznu Kapiju Detaljno Upustvo Za MontažuDocument10 pagesMotor Za Kliznu Kapiju Detaljno Upustvo Za MontažuSrdjanv5No ratings yet

- Analog To Digital and Digital To Analog Converters Engr. Muhmmad Naveed NazDocument11 pagesAnalog To Digital and Digital To Analog Converters Engr. Muhmmad Naveed NazSheraz AliNo ratings yet

- Catalogue Complete MitutoyoDocument666 pagesCatalogue Complete MitutoyoJuan Manuel Barcia Diaz100% (2)

- How To Use NFC Shield With Arduino and Demo CodeDocument8 pagesHow To Use NFC Shield With Arduino and Demo CodeEster KurniantiNo ratings yet

- Hardware Manual ACS800-07 Drives (500 To 2800 KW)Document193 pagesHardware Manual ACS800-07 Drives (500 To 2800 KW)Bhanu Prakash100% (1)

- RS92SGP Datasheet B210358EN F LOW PDFDocument2 pagesRS92SGP Datasheet B210358EN F LOW PDFJesus GonzalezNo ratings yet

- Data SheetDocument8 pagesData SheetFaizatul RosyidahNo ratings yet

- Ce Emc Test ReportDocument61 pagesCe Emc Test ReportBIS RegistrationandNo ratings yet

- 3.5 To 30 MHZ Automatic Antenna Impedance Matching SystemDocument100 pages3.5 To 30 MHZ Automatic Antenna Impedance Matching SystemAlexandru MaiorNo ratings yet

- 2SC2655 Y (F) ToshibaDocument2 pages2SC2655 Y (F) Toshibaalguna54No ratings yet

- AdcDocument3 pagesAdcGopi ChannagiriNo ratings yet

- PWM Atmega328Document30 pagesPWM Atmega328JUNIOR700No ratings yet

- Wavetable Synthesis Basic IntroductionDocument1 pageWavetable Synthesis Basic IntroductionBen GraysonNo ratings yet

- Price List Kabel SupremeDocument5 pagesPrice List Kabel SupremeHappy Kurniawan0% (1)

- CA-DXT99: Compact Component SystemDocument50 pagesCA-DXT99: Compact Component SystemVince M. RondonNo ratings yet

- Induction Balance Metal Detector: Project 549Document6 pagesInduction Balance Metal Detector: Project 549Anonymous D5LmLCabNo ratings yet

- Haier LCD L42v6-A8kDocument21 pagesHaier LCD L42v6-A8kluis_alessandrinNo ratings yet

- Companies ListDocument16 pagesCompanies ListVoipOffNo ratings yet

- Manual Manual Manual Manual SIMRAD EQ42/50/52: EchosounderDocument80 pagesManual Manual Manual Manual SIMRAD EQ42/50/52: EchosounderHen ZebuleNo ratings yet

- Constellation QPSKDocument5 pagesConstellation QPSKVijayanand SNo ratings yet

- Interoperability Between GSM and WCDMA (GBSS14.0 - 04)Document158 pagesInteroperability Between GSM and WCDMA (GBSS14.0 - 04)Saurabh OhriNo ratings yet

- Tssa2015 ProceedingDocument301 pagesTssa2015 ProceedingTeddy ZuganaNo ratings yet

- Sony HCD-N555AV SchematicDocument78 pagesSony HCD-N555AV SchematicAnonymous XVAl0834ykNo ratings yet

- Digital Designs Cenik 2013Document6 pagesDigital Designs Cenik 2013ddaudioNo ratings yet