Professional Documents

Culture Documents

Cronometro Digital

Uploaded by

Josevaldo ArrudaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cronometro Digital

Uploaded by

Josevaldo ArrudaCopyright:

Available Formats

UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITCNICA DEPARTAMENTO DE ENGENHARIA ELTRICA

Cronmetro Digital de Dois Dgitos para Aplicaes no Ensino de Sistemas Digitais

F. L. Santos, I. V. V, Alves, and T. S. Loureno Universidade Federal da Bahia

Abstract This report brings a simple project for implementation of a digital chronometer based-on static logic with logic gates and flip-flops. It will show how it was modeling this system, as well as verifying its consistence and well make some tests to prove its efficient. In the end well show the circuit built in a protoboard. Keywords Digital Chronometer. Digital Circuits. Sequential Circuits. Combinational Circuits.

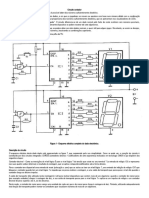

resoluo para que finalmente o sistema seja modelado e projetado. Em seguida, na Seo III, ser feita uma anlise computacional para simulao do funcionamento do circuito com auxlio da ferramenta Multisim. A implementao do projeto numa plataforma fsica de testes (protoboard) ser apresentada na Seo IV. Por fim, na Seo V, apresentaremos os resultados e concluses do trabalho. II. MODELAGEM DO SISTEMA Nesta Seo abordaremos numa viso down-top (de elementos do sistema para o sistema) a modelagem e projeto do circuito. A. O problema do tempo Os circuitos digitais que utilizam lgica sequencial precisam de uma base de tempo para funcionarem adequadamente. Em nosso sistema, a base de tempo servir tambm para a contagem do prprio tempo, uma vez que ele um sistema cronomtrico que contar os segundos. Diversas so as alternativas para se gerar o chamado clock, que um sinal eltrico que servir como base de tempo para o sistema, que vo desde a utilizao de um cristal de quartzo, passando por um astvel ou ainda um outro circuito digital, como um microcontrolador. Devido a praticidade, economia e o no requerimento de extrema preciso, utilizaremos o circuito integrado NE555 na configurao de astvel. O circuito do 555 na configurao astvel pode ser visto na Figura 1.

6V Vs 288.6k R1

RST DIS THR

I. INTRODUO esde o surgimento da eletrnica digital diversos problemas cotidianos puderam ser resolvidos de forma rpida, eficiente e, de certa forma, lgica. Atravs da miniaturizao dos componentes foi possvel integrar muitos elementos em um mesmo chip, denominado circuito integrado. A utilizao dos circuitos integrados permitiu a criao de unidades lgicas e aritmticas facilitando clculos nas reas de engenharia, fsica e computao, por exemplo. Os primeiros circuitos digitais eram formados estritamente por portas lgicas que designam uma lgica combinacional, onde a sada funo exclusiva da entrada e as caractersticas de sequncias temporais de resposta so inexistentes, o que no permitia, por exemplo, o armazenamento de dados. Em 1919, Willian Eccles e F. W. Jordan criaram o menor elemento de memria de um circuito digital, trata-se do flip-flop. A partir de agora, os circuitos no s retornam valores que dependem das entradas, mas tambm de estados anteriores, ou seja, da sequncia temporal. Estes circuitos possuem lgica sequencial. Este trabalho relatar o projeto de concepo de um cronmetro digital de dois dgitos, baseado em lgica fixa1 sequencial e combinacional a fim de aplicar os conhecimentos apreendidos sobre Sistemas Lgicos, o que facilitou desta maneira o processo de ensino e aprendizagem. A organizao do trabalho a segue: na Seo II, apresentaremos o problema inicial, elaborando mecanismos de

VCC OUT

577.2k R2

TRI CON GND

100 Rl 555_VIRTUAL Timer

1uF C

10nF Cf

Um circuito digital dito de lgica fixa quando o seu hardware permite a realizao de uma s tarefa, se quisermos alter-la ou adicionar outra, deveremos construir outro circuito ou readapt-lo.

Figura 1 - Circuito do CI 555 na configurao astvel

UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITCNICA DEPARTAMENTO DE ENGENHARIA ELTRICA

O clculo dos valores a malha R-C (Resistor-Capacitor) responsvel pela gerao da frequncia de oscilao do astvel dada pelas equaes (1) e (2):

TH = 0,69 ( R1 + R2 ) C TL = 0,69 R2 C

(1) (2)

Onde: TH corresponde ao tempo em nvel alto da forma de onda e TL ao tempo em nvel baixo. RA e RB so as resistncias existentes na malha de carga e descarga do capacitor; C a capacitncia do capacitor. A forma de onda no capacitor e a gerada na sada do circuito pode ser vista na Figura 2.

o sistema, necessrio informar ao usurio que o utilizar o resultado da contagem de forma amigvel e intuitiva. Existem diversas formas que incluem desde LEDs e displays de 7 segmentos a displays LCD. Os LEDs informariam uma sada em formato binrio, o que no trivial para o ser humano, ao passo que um display LCD, embora elegante aumentaria muito a complexidade do circuito. Utilizaremos ento dois displays de 7 segmentos. Os displays de 7 segmentos possuem 7 LEDs arranjados em formas de segmentos, nomeados de a (primeiro superior) a g (segmento do meio) seguindo o sentido horrio. Isso permite uma visualizao decimal. A Figura 3 mostra o aspecto fsico de um display de 7 segmentos.

Figura 3 - Display de 7 segmentos Ser necessrio controlar 7 bits (1 para cada segmento do display), no entanto, o contador nos retorna valores digitais em formado de nibble (4 bits). Ser necessria fazer ento a converso entre os sistemas, processo conhecido como decodificao. Convm salientar, que como LEDs, os displays de 7 segmentos possuem polaridade. Um display dito anodo comum, quando todos os anodos dos LEDs esto interligados ou catodo comum, quando todos os catodos esto interligados. Utilizaremos o display catodo comum, o motivo da escolha ficar claro posteriormente. A decodificao pode ser feita como segue na Tabela 1. As entradas QN do decodificador, representam as sadas dos contadores (4 bits, de 0000 a 1001), e as sadas a, b, c, d, e, f e g representam a sada do decodificador. Nvel lgico 1 corresponde a 5V, ao passo que nvel lgico 0, corresponde a 0V. Tabela 1 - Tabela que mostra o processo de decodificao N QD QC QB QA a b c d e f g 0 0 0 0 0 1 1 1 1 1 1 0 1 0 0 0 1 0 1 1 0 0 0 0 2 0 0 1 0 1 1 0 1 1 0 1 3 0 0 1 1 1 1 1 1 0 0 1 4 0 1 0 0 0 1 1 0 0 1 1 5 0 1 0 1 1 0 1 1 0 1 1 6 0 1 1 0 0 0 1 1 1 1 1 7 0 1 1 1 1 1 1 0 0 0 0 8 1 0 0 0 1 1 1 1 1 1 1 9 1 0 0 1 1 1 1 0 0 1 1 Para cada segmento existir um circuito com portas lgicas o

Figura 2 - Forma de onda no capacitor e na sada [2] B. A contagem digital do tempo O segundo problema que apresentamos se refere a como transformar pulsos eltricos em nmeros. Algo que possa ser quantificado e posteriormente transformado em algo legvel ao usurio. Apresentamos agora os circuitos contadores, que so circuitos formados por flip-flops e portas lgicas e que podem apresentar diversas topologias. So divididos em sncronos, quando o sinal de clock atinge simultaneamente todos os flipflops do circuito e assncronos, quando o clock aplicado apenas ao primeiro flip-flop, e o clock dos demais blocos funo dos anteriores. Devido a simplicidade do sistema, o contador assncrono pode ser utilizado, uma vez que o contador sncrono o mais completo contador, ele tem condies de gerar qualquer tipo de seqncia binria, ou seja, um gerador de palavras e consequentemente de cdigos binrios[1]. Os contadores assncronos podem ser ainda classificados como contadores de pulso, de dcada, de 0 a N, crescentes, decrescentes, etc. Utilizaremos o contador de dcada 7490, pois conta de 0 a 9 (0000 a 1001, em binrio). Como o cronmetro exibir de 0 a 99 segundos, sero necessrios dois destes. C. A exibio do tempo Embora possa ficar claro para o projetista o que ocorre com

UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITCNICA DEPARTAMENTO DE ENGENHARIA ELTRICA

que tornaria o circuito final maior, mais complexo e com maior potencialidade de falhas. A fim de simplificar o trabalho, utilizaremos decodificadores prontos vendidos comercialmente, como o circuito integrado 4511 (BCD para 7 Segmentos). D. Sistema de Controle Outro aspecto relevante a ser considerado o de interao com o usurio. Todo cronmetro que se preze possui botes de INICIA/PARA (Start/Stop) e ZERA (Reset). Alguns circuitos integrados possuem estas funcionalidades embutidas, mas o 7490 possui apenas a segunda. Faz-se necessrio, ento, construir um circuito capaz de iniciar e parar o cronmetro a qualquer instante e zer-lo, quando necessrio. Uma tcnica til remover o sinal de clock quando quisermos parar a contagem e reconect-lo quando quisermos iniciar ou reiniciar a contagem. Os botes utilizados so do tipo push button, que fecha o contato apenas quando o pressionamos. Este tipo de chave nos trs um problema: como parar e iniciar o cronmetro (ou seja, ligar e desligar o clock) se a chave no possui estados estveis? Este problema pode ser resolvido com a utilizao de um flipflop tipo D, que funcionar como um biestvel acionado pela chave. O circuito pode ser visto na Figura 4.

VCC 9V J3

6 5 3 SD1 D1 CP1

Seguindo a sua tabela verdade como mostra a Figura 6.

Figura 6 Tabela verdade com funes de reset [5]. E. Viso geral do sistema O diagrama da Figura 7 mostra o sistema em blocos.

U1A

O1 ~O1 1 2

Key = S

R19 4 CD1 1k 7474 R21 10k

Q1

BC547C CLOCK IN R22 1k CLOCK OUT

Figura 4- Parte do Circuito de Controle Neste circuito, o coletor do transistor Q1(BC547) ligado sada Q1 do flip-flop. Quando tivermos nvel lgico 1 na sua sada, o transistor estar polarizado adequadamente e conduzir e cortar segundo o sinal de clock (gerado pelo astvel) na sua base (clock in). O sinal sair no emissor (clock out) que ir para o primeiro contador. Analogamente, ~Q1 estar em nvel 0, que conectado entrada D1 far alternar a sada Q1 para nvel 0, assim que um pulso de clock (ou seja, pressionando a chave) ocorrer. Lembrando-se que a sada Q1 do flip-flop D a prpria entrada, desde que haja transio de subida em seu clock (CP1). O circuito de reset utilizou as funcionalidades do CI 7490.

Figura 7 - Diagrama em Blocos do Sistema. O circuito de controle ativa ou desativa o sinal de clock proveniente do circuito astvel (CI 555). O clock atinge o primeiro contador (A, CI 7490), cuja sada est ligada ao decodificador (CI 4511) do display que exibir a unidade de segundo. Quando o contador chegar a nove (ou seja, tivermos 1001 na sada), uma porta AND (CI 7408) cujas suas entradas esto conectadas ao bit mais significativo (MSB) e menos significativo (LSB) do primeiro contador, tem a sua sada levada ao nvel lgico 1, que gerar o sinal de clock para o segundo contador (B, CI 7490), que possui suas sadas ligadas ao decodificador do display da dezena de segundo. III. VERIFICAO E SIMULAO DO CIRCUITO

Figura 5 Circuito de reset

Aps o

projeto do

circuito

anlise global

do

UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITCNICA DEPARTAMENTO DE ENGENHARIA ELTRICA

comportamento e funcionamento do mesmo, partiu-se para a simulao. O circuito foi reproduzido no Multisim verso 10. De posse do comportamento esperado, verificaram-se as possibilidades de entradas e retorno do sistema, onde o sistema foi ento validado. A Figura 8 mostra o ambiente de simulao.

Figura 9 - Vista do circuito implementado em protoboard. V. CONCLUSO Este trabalho teve o objetivo de mostrar de forma clara e objetiva o processo de concepo e implementao de um cronmetro digital de dois dgitos com circuitos lgicos combinacionais e sequenciais. Atravs deste projeto, foi possvel compreender os passos para criao de um projeto, que vo desde a concepo, passando pela modelagem, verificao, simulao e vo at a etapa de implementao e testes. Foi necessrio o entendimento de uma forma apurada do comportamento dos contadores, gerao de clock e demais assuntos vistos em disciplinas de Sistemas Lgicos e Laboratrio Integrado I do curso de Engenharia Eltrica da UFBA. Aspectos positivos do trabalho envolvem a interao entre alunos componentes da equipe, conhecimento de materiais e reconhecimento de componentes, aplicao dos conhecimentos adquiridos em sala de aula, dentre outros. Aspectos negativos o gasto com os materiais, que alm dos citados na Tabela 2, incluem tambm ferramentas como alicates, protoboard, chaves de fenda, etc, que nem sempre esto acessveis facilmente para estudantes de uma instituio pblica gratuita. VI. APNDICE A Figura 10 mostra o circuito completo do cronmetro.

X2 VCC 9V 2.5 V

Figura 8 - Simulao do circuito no Multisim.

IV. IMPLEMENTAO DO CIRCUITO EM PROTOBOARD Verificada a validade do funcionamento do circuito, avaliou-se a sua viabilidade financeira atravs de um oramento inicial, como segue na Tabela 2. Tabela 2- Oramento dos componentes Preo Qtde. Descrio Unitrio 2 Display 7 seg. C.C. R$ 2,50 2 CI 7490 R$ 4,00 1 CI 7474 R$ 2,00 1 CI 7408 R$ 2,00 2 CI 4511 R$ 2,00 1 CI 555 R$ 1,50 2 Push Button R$ 0,70 1 Resistor 1k R$ 0,20 1 Resistor 100 R$ 0,20 14 Resistor 270 R$ 0,20 4 Resistor 1k2 R$ 0,20 1 Potencimetro 50k R$ 2,50 1 Trimpot de 10k R$ 2,00 Capacitor Eletroltico 1 R$ 0,60 1 x 16V 1 Transistor BC547 R$ 0,50 2 LED 3mm vermelho R$ 0,40 Total

tem 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

Total R$ 5,00 R$ 8,00 R$ 2,00 R$ 2,00 R$ 2,00 R$ 1,50 R$ 1,40 R$ 0,20 R$ 0,20 R$ 2,80 R$ 0,80 R$ 2,50 R$ 2,00 R$ 0,60 R$ 0,50 R$ 0,80 R$ 32,30

X1 9.019k R1

RST DIS THR

U1A

VCC OUT 6 5 3 4 SD1 D1 CP1 CD1 O1 ~O1 1 2

2.5 V R20 100

CK CK

721.5k R2

TRI CON GND

100 Rl 555_VIRTUAL Timer

U10

A B C D E F G A B C D E F G

U3

4013BD_5V

5nF C

10nF Cf

Q1 R21 VCC 9V J3 R22 1k

13 12 11 10 9 15 14

10k

BC547C

R11 270

R12 270

R13 270

R14 R15 270 270

R16 270

R17 270

R1 270

R2 270

R3 270

R4 270

R5 270

R6 270

R7 270

OA OB OC OD OE OF OG

U9 4511BT_5V

OA OB OC OD OE OF OG

Key = S

R19 1k

13 12 11 10 9 15 14

VCC

~EL ~BI ~LT 5 4 3

~EL ~BI ~LT

9V

7 1 2 6 DA DB DC DD

U2 4511BT_5V

J1 Key = Space

7 1 2 6

DA DB DC DD

VCC

5 4 3

Constatada a viabilidade, efetuou-se a compra dos componentes montando o circuito numa placa de prottipos (protoboard), como mostra a Figura 9.

9V J2

14 1 2 3 INA INB R01 R02 R91 R92

U4

QA QB QC QD 12 9 8 11 14 1 2 3 6 7 INA INB R01 R02 R91 R92

U5

QA QB QC QD 12 9 8 11

Key = R R18 1k

6 7

7490N

7490N

U7A 7408J

U6A 7408J

U8A 7408J

Figura 10 Circuito completo do cronmetro digital

UNIVERSIDADE FEDERAL DA BAHIA ESCOLA POLITCNICA DEPARTAMENTO DE ENGENHARIA ELTRICA

REFERNCIAS

[1] Contadores binrios. Disponvel em: <http://pt.wikipedia.org/wiki/Contadores_bin%C3%A1rios>. Acesso em 19 de novembro de 2011. CI 555. Disponvel em: <http://www.eletronica24h.com.br/CURSOAO/aparte3/aulas/Aula555_ 01.html>. Acesso em 27 de novembro de 2011. TOCCI, R.J. & WIDMER,N.S. Sistemas digitais: princpios e aplicaes. 8a ed, Prentice-Hall, 2003 DM7408: Quad 2-Input AND GATES. Disponvel em: <http://www.datasheetcatalog.org/datasheets/166/500074_DS.pdf>. Acesso em: 23 de novembro de 2011. DM7490: Decade and Binary Counter. Disponvel em: <http://www.datasheetcatalog.org/datasheets/50/231825_DS.pdf>. Acesso em: 23 de novembro de 2011. 4511: BCD-to-7 Segment Latch/Decoder/Driver. Disponvel em: <http://www.datasheetcatalog.org/datasheets/320/239110_DS.pdf>. Acesso em: 23 de novembro de 2011. 555: Single timer. Disponvel em: <http://www.datasheetcatalog.org/datasheet/fairchild/LM555.pdf>. Acesso em: 23 de novembro de 2011. 7474: D Flip-Flop. Disponvel em: <http://www.datasheetcatalog.org/datasheets/208/496891_DS.pdf>. Acesso em: 23 de novembro de 2011.

[2]

[3] [4]

[5]

[6]

[7]

[8]

You might also like

- Apostila de Estratigrafia Geral PDFDocument96 pagesApostila de Estratigrafia Geral PDFLu MeloNo ratings yet

- Ra115408 Ra109882 Ra107975Document19 pagesRa115408 Ra109882 Ra107975Gabriel PavanNo ratings yet

- Relatorio Sistemas DigitaisDocument11 pagesRelatorio Sistemas DigitaisRauniNo ratings yet

- Atividade 01 - ProbabilidadeDocument2 pagesAtividade 01 - ProbabilidadeProfessora Sandra Viana75% (12)

- Projeto e Implementação de Um Relógio Digital Utilizando PLDDocument5 pagesProjeto e Implementação de Um Relógio Digital Utilizando PLDWeslley AlmeidaNo ratings yet

- APS-Grupo 7 - Cronometro Digital2 (1) .RevDocument15 pagesAPS-Grupo 7 - Cronometro Digital2 (1) .RevPaulo CordeiroNo ratings yet

- Relógio Digital Com DespertadorDocument4 pagesRelógio Digital Com DespertadormarcelolucasbrNo ratings yet

- Cifras NativistasDocument43 pagesCifras NativistasAlessandro ValentimNo ratings yet

- Teste 01Document7 pagesTeste 01Michele NeriNo ratings yet

- Relatório - Elaboração de Um ContadorDocument13 pagesRelatório - Elaboração de Um ContadorMatheus AraujoNo ratings yet

- Projeto Contador de 0 A 99Document12 pagesProjeto Contador de 0 A 99Diky LukokiNo ratings yet

- Aps Cronometro Regressivo 10SDocument19 pagesAps Cronometro Regressivo 10SLuan BragaNo ratings yet

- Sprint 4Document13 pagesSprint 4Adriano MendesNo ratings yet

- Felipe Dos Santos - Relatório 8 - Relógio DigitalDocument10 pagesFelipe Dos Santos - Relatório 8 - Relógio DigitalFelipe SantosNo ratings yet

- Relatório Técnico Projeto Final Electra 2010Document16 pagesRelatório Técnico Projeto Final Electra 2010Ricardo AkermanNo ratings yet

- Contadores DigitaisDocument5 pagesContadores DigitaisRicardo AkermanNo ratings yet

- Eletronica Digital CTE ParobeDocument13 pagesEletronica Digital CTE ParobeFelipe FigueiróNo ratings yet

- Curso Básico de Eletrônica Digital Parte 10Document8 pagesCurso Básico de Eletrônica Digital Parte 10Thiago_jry100% (2)

- Cronômetro DigitalDocument27 pagesCronômetro DigitalNativomackgiver0% (1)

- Atividade Pratica 8 Contador e FpgaDocument9 pagesAtividade Pratica 8 Contador e FpgaAnderson MartinsNo ratings yet

- Projetos Com Stm8s103f3 Programado Em Arduino - Parte XxvFrom EverandProjetos Com Stm8s103f3 Programado Em Arduino - Parte XxvNo ratings yet

- Relatório Relógio DigitalDocument11 pagesRelatório Relógio DigitalFernanda SantiagoNo ratings yet

- #Pratica 3 - Contaodr Decimal.Document8 pages#Pratica 3 - Contaodr Decimal.Paulo Vinícius B. LimaNo ratings yet

- Desenvolvendo Uma Lombada Eletrônica Para Apresentar A Velocidade Com ArduinoFrom EverandDesenvolvendo Uma Lombada Eletrônica Para Apresentar A Velocidade Com ArduinoNo ratings yet

- SD ApontamentosDocument57 pagesSD Apontamentoslivraria são toméNo ratings yet

- 10 Curso Básico de Eletrônica Digital Parte 10Document8 pages10 Curso Básico de Eletrônica Digital Parte 10SilvaSilvaNo ratings yet

- Relatorio Contador OriginalDocument12 pagesRelatorio Contador OriginalFofuchinho MphiliNo ratings yet

- Relogio Digital Por Oscar Miguel SantacruzDocument15 pagesRelogio Digital Por Oscar Miguel SantacruzsantcruzoscarNo ratings yet

- Capa Padrão RelatórioDocument26 pagesCapa Padrão RelatórioMateus Mendes100% (1)

- Postar Aps7Document43 pagesPostar Aps7Diego CarreiraNo ratings yet

- RELATORIO Eletrônica Digital 5Document14 pagesRELATORIO Eletrônica Digital 5Anna KroviskiNo ratings yet

- Cronômetro DigitalDocument5 pagesCronômetro DigitalDavid Da Silva BorgesNo ratings yet

- Relatorio Do Relogio DigitalDocument7 pagesRelatorio Do Relogio Digitalnilt100% (4)

- LCL 2022 1 D1Document6 pagesLCL 2022 1 D1Alexandre AugustoNo ratings yet

- Cronômetro DigitalDocument6 pagesCronômetro Digitalpaulohss1985No ratings yet

- Analise de Circuitos Utilizando Pspice e MatlabDocument50 pagesAnalise de Circuitos Utilizando Pspice e MatlabRonan PapassoniNo ratings yet

- Mux e DemuxDocument8 pagesMux e DemuxGuilherme Guedes DominguesNo ratings yet

- Desenvolvendo Um Display Indicador De Atendimento Com ArduinoFrom EverandDesenvolvendo Um Display Indicador De Atendimento Com ArduinoNo ratings yet

- Cópia de Circuito ContadorDocument5 pagesCópia de Circuito ContadorRonaldo RochaNo ratings yet

- Relatorio Projeto de Circuitos DigitaisDocument11 pagesRelatorio Projeto de Circuitos DigitaisRosCibelyNo ratings yet

- Cronometro DigitalDocument14 pagesCronometro DigitalWellington Mazoni de AndradeNo ratings yet

- Relatóriofinal InstrumentaçãoeletrônicaDocument29 pagesRelatóriofinal Instrumentaçãoeletrônicaperes.gabriel.gabrielNo ratings yet

- Projetos No Vc# Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IxFrom EverandProjetos No Vc# Para Raspberry Pi 3 Com Windows 10 Iot Core Parte IxNo ratings yet

- Mini Curso Micro Control Ad orDocument42 pagesMini Curso Micro Control Ad orcesarcemNo ratings yet

- Dias Do AnoDocument147 pagesDias Do AnoJosevaldo ArrudaNo ratings yet

- Aula7 PolarizacaoDocument16 pagesAula7 PolarizacaoEdilson MorenoNo ratings yet

- Texto Apoio Mov - Sol-TerraDocument20 pagesTexto Apoio Mov - Sol-TerraJosevaldo ArrudaNo ratings yet

- Smii P22 2013 1 1Document1 pageSmii P22 2013 1 1Josevaldo ArrudaNo ratings yet

- Dias Do AnoDocument90 pagesDias Do AnoJosevaldo ArrudaNo ratings yet

- O OsciloscopioDocument63 pagesO Osciloscopiomarciotdias123No ratings yet

- Relatorio 9 Controle de Velocidade para Motores CADocument4 pagesRelatorio 9 Controle de Velocidade para Motores CAJosevaldo ArrudaNo ratings yet

- 2011 Clagteedesenvolvimento de Uma Plataforma Educacional Interativa Baseada em Foss para Aprendizagem de Motor de PassoDocument5 pages2011 Clagteedesenvolvimento de Uma Plataforma Educacional Interativa Baseada em Foss para Aprendizagem de Motor de PassoJosevaldo ArrudaNo ratings yet

- Relatorio 7 TCA 785Document4 pagesRelatorio 7 TCA 785Josevaldo ArrudaNo ratings yet

- Manutencao Fonte Chaveada2Document4 pagesManutencao Fonte Chaveada2Josevaldo ArrudaNo ratings yet

- Modulação AM e FMDocument12 pagesModulação AM e FMJosevaldo ArrudaNo ratings yet

- FormulasDocument1 pageFormulasJosevaldo ArrudaNo ratings yet

- Aula 16 - CLP (Temporizadores)Document19 pagesAula 16 - CLP (Temporizadores)Josevaldo ArrudaNo ratings yet

- TS EXERCÍCIOS RESOLVIDOS SS TZ TF Discretos 1Document31 pagesTS EXERCÍCIOS RESOLVIDOS SS TZ TF Discretos 1krughor100% (2)

- Lista de Exer Sistema de EquacoesDocument1 pageLista de Exer Sistema de EquacoesAryelly RabeloNo ratings yet

- Aula 15 - CLP (Introducao A Linguagem)Document20 pagesAula 15 - CLP (Introducao A Linguagem)Rafael MarinhoNo ratings yet

- TS EXERCÍCIOS RESOLVIDOS SS TZ TF Discretos 1Document31 pagesTS EXERCÍCIOS RESOLVIDOS SS TZ TF Discretos 1krughor100% (2)

- Algoritmos 01 - Conceitos BásicosDocument42 pagesAlgoritmos 01 - Conceitos BásicosJosevaldo ArrudaNo ratings yet

- TS EXERCÍCIOS RESOLVIDOS SS TZ TF Discretos 1Document31 pagesTS EXERCÍCIOS RESOLVIDOS SS TZ TF Discretos 1krughor100% (2)

- Equações LinearesDocument10 pagesEquações LinearesJosevaldo ArrudaNo ratings yet

- Algoritmos 01 - Conceitos BásicosDocument42 pagesAlgoritmos 01 - Conceitos BásicosJosevaldo ArrudaNo ratings yet

- Maquinas EletricasDocument70 pagesMaquinas EletricasJosevaldo ArrudaNo ratings yet

- TS EXERCÍCIOS RESOLVIDOS SS TZ TF Discretos 1Document31 pagesTS EXERCÍCIOS RESOLVIDOS SS TZ TF Discretos 1krughor100% (2)

- Motor MonoDocument8 pagesMotor MonofabinhocureuNo ratings yet

- Resumo Portugues para Concursos 16 MinDocument4 pagesResumo Portugues para Concursos 16 MinMarcio Victor Lopes AmadoNo ratings yet

- Apostila Ensino Fundamental CEESVO - Matemática 03Document43 pagesApostila Ensino Fundamental CEESVO - Matemática 03Ensino Fundamental95% (20)

- Braga - Roteiro - Turistico - JuvenilDocument19 pagesBraga - Roteiro - Turistico - JuvenilDjoScribdNo ratings yet

- Transtornos Alimentares PDFDocument29 pagesTranstornos Alimentares PDFGilberto de SouzaNo ratings yet

- Resenha-Linguística Textual e ArgumentaçãoDocument6 pagesResenha-Linguística Textual e ArgumentaçãoRose Aparecida Costa Souza OliveiraNo ratings yet

- ComentÁrios de Amoramon Sobre Os Livros de Zecharia SitchinDocument19 pagesComentÁrios de Amoramon Sobre Os Livros de Zecharia SitchinRondinelle Almeida OliveiraNo ratings yet

- Corrimento VaginalDocument4 pagesCorrimento VaginalPAULO VITOR KELMON SILVA DE OLIVEIRANo ratings yet

- André Pichot - Biólogos e RaçasDocument5 pagesAndré Pichot - Biólogos e RaçasLuiz Felipe CandidoNo ratings yet

- O Cânon Do Antigo Testamento Antes Do Concílio de TrentoDocument6 pagesO Cânon Do Antigo Testamento Antes Do Concílio de TrentoConhecereisaVerdadeNo ratings yet

- Tomaz Tadeu - Currículo e Identidade SocialDocument10 pagesTomaz Tadeu - Currículo e Identidade SocialGregBalthazarNo ratings yet

- Planilha para Calcular Traço de ConcretoDocument16 pagesPlanilha para Calcular Traço de ConcretoAllisson DuarteNo ratings yet

- 27 Receitas de Doces, Bolos e Sobremesas LOW CARBDocument42 pages27 Receitas de Doces, Bolos e Sobremesas LOW CARBPaulo SousaNo ratings yet

- Arthur Rimboud - O BARCO ÉBRIO, VOGAIS, MINHA BOÊMIA, AURORADocument5 pagesArthur Rimboud - O BARCO ÉBRIO, VOGAIS, MINHA BOÊMIA, AURORAJonas de Pinho100% (1)

- Psicologia de AprendizagemDocument9 pagesPsicologia de AprendizagemFrancisco Rosario JaimeNo ratings yet

- EBOOK - Atendimento Imobiliário 5.0Document19 pagesEBOOK - Atendimento Imobiliário 5.0Ayrton RodriguesNo ratings yet

- 01-Vidas No LimiteDocument30 pages01-Vidas No LimiteNaira CarmoNo ratings yet

- O Que É Metaficção - Narrativa NarcisistaDocument15 pagesO Que É Metaficção - Narrativa NarcisistaClaudia Regina CamargoNo ratings yet

- As 10 Questões de Genética Mais Importantes Dos Últimos AnosDocument3 pagesAs 10 Questões de Genética Mais Importantes Dos Últimos AnosVital ViliNo ratings yet

- Recurso Ordinário PDFDocument5 pagesRecurso Ordinário PDFSayonara SabinoNo ratings yet

- Análise Orgulho e PreconceitoDocument4 pagesAnálise Orgulho e PreconceitoBia MirandaNo ratings yet

- Fred Malone - O Elevado Mistério Da PredestinaçãoDocument7 pagesFred Malone - O Elevado Mistério Da Predestinaçãoral-nvgtNo ratings yet

- Apostila de Linguagem C - MicrocontroladoresDocument96 pagesApostila de Linguagem C - MicrocontroladorestiagoNo ratings yet

- Padaria Espiritual: Cultura Popular, Memória e "Uns Pilintras" em Fortaleza No Final Do Século XixDocument52 pagesPadaria Espiritual: Cultura Popular, Memória e "Uns Pilintras" em Fortaleza No Final Do Século XixMessias Douglas100% (1)

- 14 As Variáveis Básicas Da NegociaçãoDocument13 pages14 As Variáveis Básicas Da NegociaçãoEduarda SantosNo ratings yet

- 6 Dimensionamento PDFDocument34 pages6 Dimensionamento PDFRodrigoChavesNo ratings yet

- Disc - QuestionárioDocument5 pagesDisc - QuestionárioElenNo ratings yet